PLL回路

【課題】感度関数と相補感度関数の両方が低減されたPLL回路を提供する。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

【解決手段】本発明のPLL回路10は、一般的なPLL回路の構成を備えた第1ループ50と、相補感度関数を低減するための第2ループ52とを備えて構成されている。第1ループ50では、周波数が高い基準クロック34を用いて比較部14にて位相比較を行うことにより、感度関数を下げている。そして、第2ループ52からの出力により電流補償部16にて電流値を補完することにより、相補感度関数を下げている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、感度関数と相補感度関数とを低減させたPLL回路に関する。

【背景技術】

【0002】

一般的なPLL回路(フェーズ・ロックド・ループ回路)を、図5を参照して説明する。

【0003】

この図に示すPLL回路100は位相比較回路101と、ローパスフィルタ回路102と、VCO回路(電圧制御型発振回路)103と、分周回路104とを備えている。そして、外部リファレンスクロック信号に基づいてVCO回路103の発振周波数を制御して、この外部リファレンスクロック信号に同期した所定周波数のクロック信号を生成し、これを外部に出力する。更に、位相比較回路101は外部リファレンスクロック信号と、帰還信号とが供給されたとき、これら外部リファレンスクロック信号と、帰還信号との位相差に応じた信号を生成してこれをローパスフィルタ回路102に供給する。ローパスフィルタ回路102は、位相比較回路101から出力される信号を平滑化して周波数制御信号を生成し、これをVCO回路103に供給する。

【0004】

VCO回路103は、ローパスフィルタ回路102から出力される周波数制御信号に応じた周波数で発振してクロック信号を生成し、これを外部に出力するとともに、分周回路104に供給する。分周回路104は予め設定されている分周比でVCO回路103から出力されるクロック信号を分周して帰還信号を生成し、これを位相比較回路101に供給する。

【0005】

このように、一般的なPLL回路では、VCO回路103から出力されるクロック信号を分周して得られた帰還信号の位相と、外部リファレンスクロック信号の位相とを比較している。そして、両者の位相が一致するようにVCO回路103の発振周波数が制御され、この制御動作によって決定した周波数および位相のクロック信号が外部に出力される。

【0006】

例えば、従来から使用されているPLL回路は、下記特許文献1に記載されている。

【特許文献1】特開平01−232828号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

上記した構成のPLL回路では、PLL回路に供給される外部リファレンス信号の周波数を高めて更に高安定とすることにより、感度関数を下げることが可能となり、電源変動等の外乱が出力に与える悪影響が小さくされる。

【0008】

しかしながら、この方法により感度関数を低くすると、感度関数と加算して1となる性質を備えた相補感度関数の値が大きくなり、結果的に入力信号に含まれる雑音が出力に大きく悪影響を与えてしまう問題がある。

【0009】

本発明は上述した問題点を鑑みて成されたものである。本発明の主な目的は、感度関数と相補感度関数の両方を低減させたPLL回路を提供することにある。

【課題を解決するための手段】

【0010】

本発明のPLL回路は、外部参照クロックが逓倍された発振クロックを出力するPLL回路であり、分周比の時間平均値が小数点以下を含む値または整数である第1分周比にて、フィードバックされた前記発振クロックを分周する累算部と、分周された前記発振クロックと基準クロックとを比較して、両者の位相差を示す位相誤差信号を出力する第1位相比較部と、前記累算部からの出力に基づいて、前記位相誤差信号を補正して補正信号を発生させる電流補償部と、前記補正信号を平滑化するループフィルタと、前記ループフィルタの出力に基づいて制御されて前記発振クロックを発振する出力発振部と、フィードバックされた前記発振クロックを、第2分周比により分周する分周部と、分周された前記発振クロックと、前記第1基準クロックよりも周波数が低い外部参照クロックとを比較して両者の位相誤差信号を出力する第2位相比較部と、前記第2位相比較部の出力を基に、前記累算部が備えるべき前記第1分周比を算出するフィルタと、を備えることを特徴とする。

【発明の効果】

【0011】

本発明によれば、高い周波数を備えた基準クロックと発振クロックとを同期させることにより位相誤差信号を生成することで感度関数を小さくしている。更に、周波数が低い外部参照クロックと発振クロックとの差に基づいて、この位相誤差信号を補間することで相補感度関数を小さくしている。

【発明を実施するための最良の形態】

【0012】

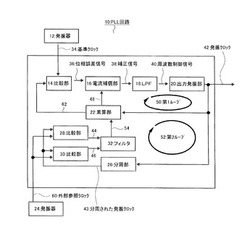

図1を参照して、本実施形態のPLL回路10の全体的な構成を説明する。PLL回路10は、比較部14と、電流補償部16と、LPF18(ローパスフィルタ)と、出力発振部20と、累算部22と、分周部26と、比較部30、28と、フィルタ32とを主要に備えて構成されている。更に、PLL回路10には、発振器12から基準クロック34が入力されると共に、発振器24から外部参照クロック60が入力される。

【0013】

PLL回路10を構成する各部位を以下にて説明する。

【0014】

出力発振部20は、電圧制御発振器(VCO:voltage controlled oscillator)であり、LPF18から供給される周波数制御信号40の電圧により、出力される発振クロック42の周波数が制御される発振器である。本実施形態では、発振クロック42の周波数は、発振器24から入力される外部参照クロック60が逓倍されたものである。具体的には、発振クロック42の周波数は、例えば400MHz〜1GHz程度である。

【0015】

累算部22(アキュムレータ)は、分周を行う所定の設定値である逓倍値54(ΔT)に基づいて、発振クロック42を分周する機能を備えており、分周された発振クロック62は比較部14に入力される。更に、累算部22は、逓倍値54に基づいて、補正信号38を補間するための補正信号48を電流補償部16に供給している。

【0016】

比較部14は、累算部22にて分周された発振クロック62の位相と、発振器12から入力される基準クロック34の位相とを比較し、両者の差に基づく位相誤差信号36を発生する。

【0017】

電流補償部16は、後述するように例えばチャージポンプを含んで構成され、比較部14から供給される位相誤差信号36に基づいてLPF18に供給される補正信号38を生成している。更に電流補償部16では、累算部22から供給された補正信号48により電流補償部16から出力される補正信号38の電流値が調整されている。

【0018】

LPF18は、補正信号38を平坦化して周波数制御信号40を生成する回路である。LPF18としては、2次ローパスフィルタ、3次ローパスフィルタ、ラグリード型フィルタが採用され、所定の周波数帯の信号が除去される。

【0019】

分周部26は、設定された分周比により、発振クロック42を分周する回路である。

【0020】

比較部28には、分周部にて分周された発振クロック43が入力されると共に、発振器24から発振された外部参照クロック60が入力される。そして、両者の位相が比較されて、位相差に基づく補正信号44がフィルタ32に入力される。

【0021】

比較部30は、比較部28と同様に、分周された発振クロック43と外部参照クロック60との位相を比較し、両者の位相差に応じた補正信号46をフィルタ32に対して出力する。

【0022】

ここで、比較部28はデジタル回路で構成され、比較部30はアナログ回路で構成される。比較部28はロックアップするまでの間に於いて用いられ、ロックアップした後は比較部30が用いられる。ロックアップするまでの間は高速性が重視され、比較的にラフな情報でよいので、デジタル回路から成る比較部28が用いられる。一方、ロックアップした後は、高精度に位相比較を行う必要があるので、デジタルクロック間の高精度比較を実施するために、アナログ回路からなる比較部30が用いられる。

【0023】

フィルタ32は、比較部30と比較部28とから入力された補正信号44および補正信号46を元に、逓倍値54(ΔT)を算出する。ここでは、逓倍値54としては、整数値のみならず、時間平均値が小数点以下の値でも良い。算出された逓倍値54は、累算部22に入力される。また、フィルタ32は、相補感度関数を下げるためのフィルタであり、第1ループ50の周波数特性には影響を及ぼさないので、入力される外部参照クロック60に含まれる高周波外乱を抑制することができる。

【0024】

更に、フィルタ32は、カットオフ周波数が可変であるアダプティブフィルタとすることができる。すなわち、分周部26に於ける分周比または外部参照クロック60が変化して、発振クロック42がロックアップするまでの期間と、ロックアップした後の期間で、カットオフ周波数を変化させている。

【0025】

具体的には、ロックアップするまでの間はカットオフ周波数を高くして、発振クロック42を高速にロックアップさせている。一方、発振クロック42がロックアップした後は、カットオフ周波数を下げて、外部参照クロック60に含まれる外乱成分を抑圧する効果を高めている。

【0026】

発振器12としては、PLL回路10全体の安定性を向上させるために、高い周波数の基準クロック34を高安定に発振する発振器が採用される。具体的には、クリスタルオシレータやSAWオシレータ等が発振器12として採用される。発振器12から発振される基準クロック34の周波数は、例えば10MHz〜100MHz程度である。尚、本実施の形態では、外部に位置する発振器24から発振される外部参照クロック60の周波数や、フィルタ32により算出される逓倍値54が変化しても、発振器12から発振される基準クロック34の周波数には影響しない。また、発振器12が発振する基準クロック34は、外部に位置する発振器24が発振する外部参照クロック60よりも高い周波数である。このことにより、比較部14にて発振クロック62の位相と基準クロック34の位相とを比較する頻度を高くして、電源変動などの外乱が抑制されて、感度関数を下げることができる。

【0027】

発振器24は、外部参照クロック60を発振して、比較部28および比較部30に入力する機能を有する。本実施形態のPLL回路10は、外部参照クロック60と分周部26の分周比に基づく周波数を、発振クロック42が備えている。

【0028】

本実施の形態のPLL回路10は、2つのループ(第1ループ50および第2ループ52)を備えた回路であると見なすことができる。具体的には、第1ループ50は、累算部22、比較部14、電流補償部16、LPF18および出力発振部20から成る。そして、第2ループ52は、分周部26、比較部28および比較部30、フィルタ32から成る。

【0029】

第1ループ50を構成する比較部14、電流補償部16、LPF18および出力発振部20はアナログ回路から構成され、累算部22はデジタル回路により構成されている。累算部22は、時間的に分周比を変化させると共に、分周比が小数点以下の値を含むように調整するので、第1ループ50はフラクショナルN方式のPLL回路として機能する。

【0030】

第2ループ52を構成する分周部26、比較部28およびフィルタ32はデジタル回路から構成され、比較部30はアナログ回路から構成されている。

【0031】

本実施の形態では、上記した第1ループ50と第2ループ52とを組みあわせてPLL回路10を構成することにより、PLL回路10全体の感度関数を相補感度関数とを、両者の値を小さくして両立させることができる。

【0032】

具体的には、上記したように、第1ループ50では、発振器12から発振される高周波且つ安定した基準クロック34を用いて、比較部14にて位相比較を行っている。このことにより、感度関数を小さくして外乱を抑制することができる。しかしながら、感度関数を小さくしたままであると、感度関数と加算して1となる相補感度関数の値が大きくなってしまい、入力雑音を抑制することが困難になってしまう。即ち、外部参照クロックに含まれる変動成分がジッタとして出力に筒抜けになってしまう。

【0033】

この様な不具合を回避するために、本実施形態では第2ループ52を設けている。この第2ループでは、基準クロック34よりも周波数が低い外部参照クロック60の位相と、分周された発振クロック43そのものの位相とを比較することにより、逓倍値54を算出している。更に、累算部22では、逓倍値54に基づいて補正信号48を算出し、この補正信号48により電流補償部16を流れる電流を微調整することにより、補正信号38の電流を補間している。

【0034】

ここで、上記したPLL回路10に入力される基準クロック34、外部参照クロック60および発振クロック42等の一例を説明する。先ず、発振器24から入力される外部参照クロック60の周波数を44.1KHzとし、発振器12から入力される基準クロック34の周波数を100MHzとし、分周部26の分周比を1/22674とする。この様な場合、出力発振部20から出力される発振クロック42の周波数は999.9234MHzとなる必要がある。そして、この様な状態となるためには、累算部22に於ける逓倍値54が9.999234と設定される。

【0035】

次に、分周部26に於ける分周値および基準クロック34の周波数はそのままの状態で、外部参照クロック60の周波数が44.2KHzに変化したと仮定する。そうなると、この変化が比較部28および比較部30により検出され、フィルタ32において逓倍値54の値が大きくされて10.021908とされる。更に、この逓倍値54を参照して累算部22により発振クロック42が分周されるので、出力発振部20から発振される発振クロック42の周波数は1002.1908MHzとされる。即ち、本実施の形態では、外部参照クロックの周波数および分周部26の何れか(または両方)が変化したら、フィードバックされる、分周された発振クロック43と外部参照クロック60との差を基に、フィルタ32により逓倍値54が計算される。そして、外部参照クロック60の周波数を分周部26の分周比で除算した値と、逓倍値54と基準クロック34とを乗算した値とが等しくなるように、逓倍値54が算出される。

【0036】

図2を参照して、上記した累算部22の動作を説明する。図2(A)はΔT(逓倍値54)および累積値Accが記録されるレジスタを示している。図2(B)では、基準クロック34、発振クロック42、分周された発振クロック43、比較部14により検出されるフェーズエラーおよび電流補償部16により加えられる補償電流を示すタイミングチャートである。またここでは、説明の簡単のために、分周部26の分周数が3.25の場合の例を示している。図2(C)はレジスタに入力される値を示す表である。

【0037】

従来型の整数型PLL回路を考えてみると小数点以下の値である0.25が加算されて整数になる4倍の周期、即ち、分周数13でないと同期をとることができない。このため、位相を比較する回数が減り、感度関数を下げることができない欠点があった。

【0038】

一方、フラクショナルN型PLLにおいては、全ての基準クロック34のタイミングで、基準クロック34と、分周された発振クロック43とを位相比較することが可能となる。しかしながら、単に位相比較を行うと、図2(B)に示すように、0.25、0.50、0.75、0.00と周期的に位相誤差を発生し続ける欠点がある。結果的に、位相誤差を含む信号をLPF18にて平滑化するために、LPF18のカットオフ周波数を上げることが困難になる。

【0039】

本実施形態では、この周期的な誤差(外乱)を予めアナログ的に除去している。具体的には、ΔTのレジスタには3.25を入力しておき、AccのレジスタにはΔTを累積加算していく。ただし、Accの整数部Nには、そのサイクルに於けるディバイダ値(逓値)が計算されるが、Accはこの整数部Nが参照された後は、Accからその整数値Nを引く。このときの計算例を図2(C)に示す。

【0040】

図2(C)を参照して、Accの整数部NにはフラクショナルN方式でダイナミックに制御される分周数が計算され、参照後のAccには予想される位相誤差が計算される。そして、電流補償部16では、参照後のAccの内容に基づいて電流補正を行う。

【0041】

ここで、Accの周波数計算の有効桁全てで電流の補正を行っても良いが、許容されるジッタ性能に応じてビット数を選択することが好適である。例えば、出力発振部20から出力される発振クロック42の周波数が1GHzである場合、発振クロック42の周期は1nsとなる。本実施形態のPLL回路で発生する位相誤差は発振クロック42を動作クロックとしているため、この誤差は最大でも発振クロック42の周期の1クロック分である。従って、予想されるジッタとしては最悪で±500psである。これを実際のPLLの性能と比較した場合、誤差の実用値としては15ps程度であればよいとすると、補正値としては15/500=1/32で良い。

【0042】

図3を参照して、この補正を行う電流補償部16を説明する。図3(A)は電流補償部16の構成を示す回路図であり、図3(B)は動作を示すタイミングチャートである。

【0043】

図3(A)を参照して、電流補償部16は、チャージポンプ56と、電流補償用の4つのトランジスタ58C、58D、58E、58Fとから構成されている。チャージポンプ56は、電源と接地電位との間に直列に接続された2つのトランジスタ58A、58Bから成り、これらのトランジスタの制御電極は比較部14に接続されている。そして、比較部14から供給された補正信号によりトランジスタ58Aがオン動作する間は、電源からLPF18に電流が供給される。ここで、トランジスタ58Aがオンすることにより、LPF18に供給される電流値を1とする。

【0044】

また、電流補償用の4つのトランジスタ58C、58D、58E、58Fは、チャージポンプ56を構成するトランジスタ58Aと並列に接続されており、累算部22の出力信号が各々の制御電極に印加される。ここで、トランジスタ58Aと比較すると、トランジスタ58Cを通過する電流は1/4であり、トランジスタ58Dを通過する電流は1/8であり、トランジスタ58Eを通過する電流は1/16であり、トランジスタ58Fを通過する電流は1/32である。またここでは、トランジスタ58A−58FとしてMOSFETが示されているが、これらのトランジスタとしてバイポーラトランジスタ等が採用されても良い。

【0045】

またここで、図3(A)に示す電流補償部16の構成を変更しても良い。即ち、この図に示す電流補償部16では、トランジスタ58C−58Fを、電源とLPF18への出力との間に並列に接続しているが、この接続を変更しても良い。変更される場合は、これらのトランジスタ58C−58Fが、接地電位とLPF18への出力との間に並列に接続される。この様にすることで、トランジスタ58C−58Fが適宜駆動することにより、LPF18に供給される電流が所定の値に減算されて補正される。

【0046】

更にまた、電源と上記出力との間にトランジスタ58C−58Fを設けると共に、それに加えて、上記出力と接地電位との間に同様の構成のトランジスタ58C−58Fを設けても良い。この場合は、これらのトランジスタが適宜駆動することにより、LPF18に供給される電流の加算および減算が行われる。

【0047】

図3(B)を参照して、フェーズエラーが発生した場合、トランジスタ58Cが、発振クロック42の2サイクルに渡りオン動作する。即ち、発振クロック42の1サイクルが1nsの場合は、2nsに渡りトランジスタ58Cがオンする。このことにより、電流値が1/2であるトランジスタが1サイクルに渡りオンしたことと等価となる。ここでは、トランジスタ58Cに加えて、トランジスタ58D、58Eおよび58Fも2サイクルに渡りオン動作している。このことにより、合計で、30/32の電流が補償電流(補正パルス)としてLPF18に供給される。

【0048】

ここで、一般的には、5ビットの分解能を備えた電流制御回路を構成する場合、電流が流れる経路に対して並列に接続された5つのトランジスタが用いられる。この場合は、主電極を流れる電流値が1/2、1/4、1/8、1/16および1/32のトランジスタが用いられる。

【0049】

本実施の形態では、各トランジスタを流れる電流値を制御すると共に、各トランジスタをオン動作させる時間を制御している。即ち、流れる電流値が1/4のトランジスタ58Cを、発振クロック42の2サイクルに渡り連続してオンさせることで、電流値が1/2であるトランジスタの役割をトランジスタ58Cが担っている。この様にすることで、電流補償部に必要とされる回路規模を小さくできる。換言すると、本実施の形態では、4つのトランジスタ58C−58Fで、5ビットの分解能を実現している。

【0050】

更にまた、トランジスタ58C−58Fは必ずしも同じタイミングにてオン動作する必要はなく、タイミングチャートの右端に示すように、異なるタイミングにて動作しても良い(同図右側)。ここでは、フェーズエラーが発生した際に、トランジスタ58Cとトランジスタ58Eが2サイクルに渡りオン動作し、その後に1サイクルに渡りトランジスタ58Fがオン動作することにより、電流補償を行っている。

【0051】

図4のタイミングチャートを参照して、電流補償部16の動作を説明する。ここでは、基準クロック34が発振クロック42に対して位相遅れが生じている。本実施の形態では、比較部14から発生される補正信号(フェーズエラー)に先行して電流補正を行い、更に、この電流補正は補正信号が収束した後も行われている。

【0052】

具体的には、比較部14にて検出されたフェーズエラーが0.65625nsの場合を説明すると、電流補償部16では、フェーズエラーが発生する直前のサイクルから電流補償を行っている。ここでは、トランジスタ58Cおよびトランジスタ58Eを、フェーズエラーが発生する1サイクル前から発生させ、フェーズエラーが含まれるサイクルの終端まで連続して発生させている。ここで、上記したように、トランジスタ58Cの電流量は1/4であり、トランジスタ58Eの電流量は1/16である。そして、トランジスタ58Cおよびトランジスタ58Eがオフした次のサイクルでは、電流量が1/32のトランジスタ58Fが1サイクルに渡りオンして補正電流を供給している。

【0053】

図の最下段に、VCOに供給される電流値(VCO−in)の変動を示す。先ず、トランジスタ58C、58Eがオンするサイクルでは電流値(VCO−in)が増加する。そして、次サイクルに於いてフェーズエラーが発生する期間では、トランジスタ58C、58Eによる電流値よりも、フェーズエラーのマイナスの補正量の方が大きいので、電流値(VCO−in)は減少する。また、このサイクルの他の期間では、トランジスタ58C、58Eを通過する補正電流により、電流値(VCO−in)は増加する。そして、トランジスタ58C、58Eによる電流補正が終了した次のサイクルでは、電流量が1/32であるトランジスタ58Fがオンすることにより、更なる電流補正が行われ、結果的に電流値(VCO−in)は、以前と同様の値となる。

【0054】

本実施の形態では、上記したように、トランジスタ58C−58Fによる電流補正を、フェーズエラーと同期して、あるいは時間的に非常に近くして行っている。従って、フェーズエラーにより誤差が発生している時間を短くして、ジッタの発生を抑制している。また、図4のフェーズエラーを示すチャートを参照すると、フェーズエラーのパルス幅は、VCOから発振される発振クロック42の周波数分解能である。従って、フェーズエラーを示す信号の幅は、発振クロックの1サイクルの幅以下であるので、同期が高速に行われる。

【0055】

更に、上記した電流補償部を、CMOSトランジスタを含むカレントミラー回路で構成すると、LSIの上面に形成されるトランジスタの面積比で、フェーズエラーを示す信号と、補正電流との比を規定することができる。従って、本実施のPLL回路を具現化するLSIでの調整が不要となる。

【0056】

尚、本発明は上記した本実施形態に限定されることはなく、例えば次のように変更することが可能である。

【0057】

図1を参照して、第2ループ52を動作させずに第1ループ50のみを動作させることで、PLL回路10を通常のフラクショナルNPLL回路として使用することができる。この場合は、基準クロック34が逓倍された発振クロック42が出力される。

【0058】

更に、累算部22に入力される逓倍値54の値として整数を設定することにより、PLL回路10を整数PLLとして用いることができる。

【0059】

更にまた、電流補償部16に入力する補正信号として、乱数に基づく信号を採用すると、PLL回路10がスペクトラム拡散PLLとして機能し、発生する副射ノイズを低減することができる。

【図面の簡単な説明】

【0060】

【図1】本発明のPLL回路の構成を示すブロック図である。

【図2】本発明のPLL回路を示す図であり、(A)はレジスタを示す図であり、(B)は基準クロック等を示すタイミングチャートであり、(C)はレジスタに入力される数値を示す表である。

【図3】本発明のPLL回路を示す図であり、(A)は電流補償部16の構成を示す図であり、(B)はタイミングチャートである。

【図4】本発明のPLL回路に含まれる電流補償部の動作を示すタイミングチャートである。

【図5】背景技術のPLL回路を説明するためのブロック図である。

【符号の説明】

【0061】

10 PLL回路

12 発振器

14 比較部

16 電流補償部

18 LPF

20 出力発振部

22 累算部

24 発振器

26 分周部

28 比較部

30 比較部

32 フィルタ

34 基準クロック

36 位相誤差信号

38 補正信号

40 周波数制御信号

42 発振クロック

43 発振クロック

44 補正信号

46 補正信号

48 補正信号

50 第1ループ

52 第2ループ

54 逓倍値

56 チャージポンプ

58A、58B、58C、58D、58E、58F トランジスタ

60 外部参照クロック

62 発振クロック

【技術分野】

【0001】

本発明は、感度関数と相補感度関数とを低減させたPLL回路に関する。

【背景技術】

【0002】

一般的なPLL回路(フェーズ・ロックド・ループ回路)を、図5を参照して説明する。

【0003】

この図に示すPLL回路100は位相比較回路101と、ローパスフィルタ回路102と、VCO回路(電圧制御型発振回路)103と、分周回路104とを備えている。そして、外部リファレンスクロック信号に基づいてVCO回路103の発振周波数を制御して、この外部リファレンスクロック信号に同期した所定周波数のクロック信号を生成し、これを外部に出力する。更に、位相比較回路101は外部リファレンスクロック信号と、帰還信号とが供給されたとき、これら外部リファレンスクロック信号と、帰還信号との位相差に応じた信号を生成してこれをローパスフィルタ回路102に供給する。ローパスフィルタ回路102は、位相比較回路101から出力される信号を平滑化して周波数制御信号を生成し、これをVCO回路103に供給する。

【0004】

VCO回路103は、ローパスフィルタ回路102から出力される周波数制御信号に応じた周波数で発振してクロック信号を生成し、これを外部に出力するとともに、分周回路104に供給する。分周回路104は予め設定されている分周比でVCO回路103から出力されるクロック信号を分周して帰還信号を生成し、これを位相比較回路101に供給する。

【0005】

このように、一般的なPLL回路では、VCO回路103から出力されるクロック信号を分周して得られた帰還信号の位相と、外部リファレンスクロック信号の位相とを比較している。そして、両者の位相が一致するようにVCO回路103の発振周波数が制御され、この制御動作によって決定した周波数および位相のクロック信号が外部に出力される。

【0006】

例えば、従来から使用されているPLL回路は、下記特許文献1に記載されている。

【特許文献1】特開平01−232828号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

上記した構成のPLL回路では、PLL回路に供給される外部リファレンス信号の周波数を高めて更に高安定とすることにより、感度関数を下げることが可能となり、電源変動等の外乱が出力に与える悪影響が小さくされる。

【0008】

しかしながら、この方法により感度関数を低くすると、感度関数と加算して1となる性質を備えた相補感度関数の値が大きくなり、結果的に入力信号に含まれる雑音が出力に大きく悪影響を与えてしまう問題がある。

【0009】

本発明は上述した問題点を鑑みて成されたものである。本発明の主な目的は、感度関数と相補感度関数の両方を低減させたPLL回路を提供することにある。

【課題を解決するための手段】

【0010】

本発明のPLL回路は、外部参照クロックが逓倍された発振クロックを出力するPLL回路であり、分周比の時間平均値が小数点以下を含む値または整数である第1分周比にて、フィードバックされた前記発振クロックを分周する累算部と、分周された前記発振クロックと基準クロックとを比較して、両者の位相差を示す位相誤差信号を出力する第1位相比較部と、前記累算部からの出力に基づいて、前記位相誤差信号を補正して補正信号を発生させる電流補償部と、前記補正信号を平滑化するループフィルタと、前記ループフィルタの出力に基づいて制御されて前記発振クロックを発振する出力発振部と、フィードバックされた前記発振クロックを、第2分周比により分周する分周部と、分周された前記発振クロックと、前記第1基準クロックよりも周波数が低い外部参照クロックとを比較して両者の位相誤差信号を出力する第2位相比較部と、前記第2位相比較部の出力を基に、前記累算部が備えるべき前記第1分周比を算出するフィルタと、を備えることを特徴とする。

【発明の効果】

【0011】

本発明によれば、高い周波数を備えた基準クロックと発振クロックとを同期させることにより位相誤差信号を生成することで感度関数を小さくしている。更に、周波数が低い外部参照クロックと発振クロックとの差に基づいて、この位相誤差信号を補間することで相補感度関数を小さくしている。

【発明を実施するための最良の形態】

【0012】

図1を参照して、本実施形態のPLL回路10の全体的な構成を説明する。PLL回路10は、比較部14と、電流補償部16と、LPF18(ローパスフィルタ)と、出力発振部20と、累算部22と、分周部26と、比較部30、28と、フィルタ32とを主要に備えて構成されている。更に、PLL回路10には、発振器12から基準クロック34が入力されると共に、発振器24から外部参照クロック60が入力される。

【0013】

PLL回路10を構成する各部位を以下にて説明する。

【0014】

出力発振部20は、電圧制御発振器(VCO:voltage controlled oscillator)であり、LPF18から供給される周波数制御信号40の電圧により、出力される発振クロック42の周波数が制御される発振器である。本実施形態では、発振クロック42の周波数は、発振器24から入力される外部参照クロック60が逓倍されたものである。具体的には、発振クロック42の周波数は、例えば400MHz〜1GHz程度である。

【0015】

累算部22(アキュムレータ)は、分周を行う所定の設定値である逓倍値54(ΔT)に基づいて、発振クロック42を分周する機能を備えており、分周された発振クロック62は比較部14に入力される。更に、累算部22は、逓倍値54に基づいて、補正信号38を補間するための補正信号48を電流補償部16に供給している。

【0016】

比較部14は、累算部22にて分周された発振クロック62の位相と、発振器12から入力される基準クロック34の位相とを比較し、両者の差に基づく位相誤差信号36を発生する。

【0017】

電流補償部16は、後述するように例えばチャージポンプを含んで構成され、比較部14から供給される位相誤差信号36に基づいてLPF18に供給される補正信号38を生成している。更に電流補償部16では、累算部22から供給された補正信号48により電流補償部16から出力される補正信号38の電流値が調整されている。

【0018】

LPF18は、補正信号38を平坦化して周波数制御信号40を生成する回路である。LPF18としては、2次ローパスフィルタ、3次ローパスフィルタ、ラグリード型フィルタが採用され、所定の周波数帯の信号が除去される。

【0019】

分周部26は、設定された分周比により、発振クロック42を分周する回路である。

【0020】

比較部28には、分周部にて分周された発振クロック43が入力されると共に、発振器24から発振された外部参照クロック60が入力される。そして、両者の位相が比較されて、位相差に基づく補正信号44がフィルタ32に入力される。

【0021】

比較部30は、比較部28と同様に、分周された発振クロック43と外部参照クロック60との位相を比較し、両者の位相差に応じた補正信号46をフィルタ32に対して出力する。

【0022】

ここで、比較部28はデジタル回路で構成され、比較部30はアナログ回路で構成される。比較部28はロックアップするまでの間に於いて用いられ、ロックアップした後は比較部30が用いられる。ロックアップするまでの間は高速性が重視され、比較的にラフな情報でよいので、デジタル回路から成る比較部28が用いられる。一方、ロックアップした後は、高精度に位相比較を行う必要があるので、デジタルクロック間の高精度比較を実施するために、アナログ回路からなる比較部30が用いられる。

【0023】

フィルタ32は、比較部30と比較部28とから入力された補正信号44および補正信号46を元に、逓倍値54(ΔT)を算出する。ここでは、逓倍値54としては、整数値のみならず、時間平均値が小数点以下の値でも良い。算出された逓倍値54は、累算部22に入力される。また、フィルタ32は、相補感度関数を下げるためのフィルタであり、第1ループ50の周波数特性には影響を及ぼさないので、入力される外部参照クロック60に含まれる高周波外乱を抑制することができる。

【0024】

更に、フィルタ32は、カットオフ周波数が可変であるアダプティブフィルタとすることができる。すなわち、分周部26に於ける分周比または外部参照クロック60が変化して、発振クロック42がロックアップするまでの期間と、ロックアップした後の期間で、カットオフ周波数を変化させている。

【0025】

具体的には、ロックアップするまでの間はカットオフ周波数を高くして、発振クロック42を高速にロックアップさせている。一方、発振クロック42がロックアップした後は、カットオフ周波数を下げて、外部参照クロック60に含まれる外乱成分を抑圧する効果を高めている。

【0026】

発振器12としては、PLL回路10全体の安定性を向上させるために、高い周波数の基準クロック34を高安定に発振する発振器が採用される。具体的には、クリスタルオシレータやSAWオシレータ等が発振器12として採用される。発振器12から発振される基準クロック34の周波数は、例えば10MHz〜100MHz程度である。尚、本実施の形態では、外部に位置する発振器24から発振される外部参照クロック60の周波数や、フィルタ32により算出される逓倍値54が変化しても、発振器12から発振される基準クロック34の周波数には影響しない。また、発振器12が発振する基準クロック34は、外部に位置する発振器24が発振する外部参照クロック60よりも高い周波数である。このことにより、比較部14にて発振クロック62の位相と基準クロック34の位相とを比較する頻度を高くして、電源変動などの外乱が抑制されて、感度関数を下げることができる。

【0027】

発振器24は、外部参照クロック60を発振して、比較部28および比較部30に入力する機能を有する。本実施形態のPLL回路10は、外部参照クロック60と分周部26の分周比に基づく周波数を、発振クロック42が備えている。

【0028】

本実施の形態のPLL回路10は、2つのループ(第1ループ50および第2ループ52)を備えた回路であると見なすことができる。具体的には、第1ループ50は、累算部22、比較部14、電流補償部16、LPF18および出力発振部20から成る。そして、第2ループ52は、分周部26、比較部28および比較部30、フィルタ32から成る。

【0029】

第1ループ50を構成する比較部14、電流補償部16、LPF18および出力発振部20はアナログ回路から構成され、累算部22はデジタル回路により構成されている。累算部22は、時間的に分周比を変化させると共に、分周比が小数点以下の値を含むように調整するので、第1ループ50はフラクショナルN方式のPLL回路として機能する。

【0030】

第2ループ52を構成する分周部26、比較部28およびフィルタ32はデジタル回路から構成され、比較部30はアナログ回路から構成されている。

【0031】

本実施の形態では、上記した第1ループ50と第2ループ52とを組みあわせてPLL回路10を構成することにより、PLL回路10全体の感度関数を相補感度関数とを、両者の値を小さくして両立させることができる。

【0032】

具体的には、上記したように、第1ループ50では、発振器12から発振される高周波且つ安定した基準クロック34を用いて、比較部14にて位相比較を行っている。このことにより、感度関数を小さくして外乱を抑制することができる。しかしながら、感度関数を小さくしたままであると、感度関数と加算して1となる相補感度関数の値が大きくなってしまい、入力雑音を抑制することが困難になってしまう。即ち、外部参照クロックに含まれる変動成分がジッタとして出力に筒抜けになってしまう。

【0033】

この様な不具合を回避するために、本実施形態では第2ループ52を設けている。この第2ループでは、基準クロック34よりも周波数が低い外部参照クロック60の位相と、分周された発振クロック43そのものの位相とを比較することにより、逓倍値54を算出している。更に、累算部22では、逓倍値54に基づいて補正信号48を算出し、この補正信号48により電流補償部16を流れる電流を微調整することにより、補正信号38の電流を補間している。

【0034】

ここで、上記したPLL回路10に入力される基準クロック34、外部参照クロック60および発振クロック42等の一例を説明する。先ず、発振器24から入力される外部参照クロック60の周波数を44.1KHzとし、発振器12から入力される基準クロック34の周波数を100MHzとし、分周部26の分周比を1/22674とする。この様な場合、出力発振部20から出力される発振クロック42の周波数は999.9234MHzとなる必要がある。そして、この様な状態となるためには、累算部22に於ける逓倍値54が9.999234と設定される。

【0035】

次に、分周部26に於ける分周値および基準クロック34の周波数はそのままの状態で、外部参照クロック60の周波数が44.2KHzに変化したと仮定する。そうなると、この変化が比較部28および比較部30により検出され、フィルタ32において逓倍値54の値が大きくされて10.021908とされる。更に、この逓倍値54を参照して累算部22により発振クロック42が分周されるので、出力発振部20から発振される発振クロック42の周波数は1002.1908MHzとされる。即ち、本実施の形態では、外部参照クロックの周波数および分周部26の何れか(または両方)が変化したら、フィードバックされる、分周された発振クロック43と外部参照クロック60との差を基に、フィルタ32により逓倍値54が計算される。そして、外部参照クロック60の周波数を分周部26の分周比で除算した値と、逓倍値54と基準クロック34とを乗算した値とが等しくなるように、逓倍値54が算出される。

【0036】

図2を参照して、上記した累算部22の動作を説明する。図2(A)はΔT(逓倍値54)および累積値Accが記録されるレジスタを示している。図2(B)では、基準クロック34、発振クロック42、分周された発振クロック43、比較部14により検出されるフェーズエラーおよび電流補償部16により加えられる補償電流を示すタイミングチャートである。またここでは、説明の簡単のために、分周部26の分周数が3.25の場合の例を示している。図2(C)はレジスタに入力される値を示す表である。

【0037】

従来型の整数型PLL回路を考えてみると小数点以下の値である0.25が加算されて整数になる4倍の周期、即ち、分周数13でないと同期をとることができない。このため、位相を比較する回数が減り、感度関数を下げることができない欠点があった。

【0038】

一方、フラクショナルN型PLLにおいては、全ての基準クロック34のタイミングで、基準クロック34と、分周された発振クロック43とを位相比較することが可能となる。しかしながら、単に位相比較を行うと、図2(B)に示すように、0.25、0.50、0.75、0.00と周期的に位相誤差を発生し続ける欠点がある。結果的に、位相誤差を含む信号をLPF18にて平滑化するために、LPF18のカットオフ周波数を上げることが困難になる。

【0039】

本実施形態では、この周期的な誤差(外乱)を予めアナログ的に除去している。具体的には、ΔTのレジスタには3.25を入力しておき、AccのレジスタにはΔTを累積加算していく。ただし、Accの整数部Nには、そのサイクルに於けるディバイダ値(逓値)が計算されるが、Accはこの整数部Nが参照された後は、Accからその整数値Nを引く。このときの計算例を図2(C)に示す。

【0040】

図2(C)を参照して、Accの整数部NにはフラクショナルN方式でダイナミックに制御される分周数が計算され、参照後のAccには予想される位相誤差が計算される。そして、電流補償部16では、参照後のAccの内容に基づいて電流補正を行う。

【0041】

ここで、Accの周波数計算の有効桁全てで電流の補正を行っても良いが、許容されるジッタ性能に応じてビット数を選択することが好適である。例えば、出力発振部20から出力される発振クロック42の周波数が1GHzである場合、発振クロック42の周期は1nsとなる。本実施形態のPLL回路で発生する位相誤差は発振クロック42を動作クロックとしているため、この誤差は最大でも発振クロック42の周期の1クロック分である。従って、予想されるジッタとしては最悪で±500psである。これを実際のPLLの性能と比較した場合、誤差の実用値としては15ps程度であればよいとすると、補正値としては15/500=1/32で良い。

【0042】

図3を参照して、この補正を行う電流補償部16を説明する。図3(A)は電流補償部16の構成を示す回路図であり、図3(B)は動作を示すタイミングチャートである。

【0043】

図3(A)を参照して、電流補償部16は、チャージポンプ56と、電流補償用の4つのトランジスタ58C、58D、58E、58Fとから構成されている。チャージポンプ56は、電源と接地電位との間に直列に接続された2つのトランジスタ58A、58Bから成り、これらのトランジスタの制御電極は比較部14に接続されている。そして、比較部14から供給された補正信号によりトランジスタ58Aがオン動作する間は、電源からLPF18に電流が供給される。ここで、トランジスタ58Aがオンすることにより、LPF18に供給される電流値を1とする。

【0044】

また、電流補償用の4つのトランジスタ58C、58D、58E、58Fは、チャージポンプ56を構成するトランジスタ58Aと並列に接続されており、累算部22の出力信号が各々の制御電極に印加される。ここで、トランジスタ58Aと比較すると、トランジスタ58Cを通過する電流は1/4であり、トランジスタ58Dを通過する電流は1/8であり、トランジスタ58Eを通過する電流は1/16であり、トランジスタ58Fを通過する電流は1/32である。またここでは、トランジスタ58A−58FとしてMOSFETが示されているが、これらのトランジスタとしてバイポーラトランジスタ等が採用されても良い。

【0045】

またここで、図3(A)に示す電流補償部16の構成を変更しても良い。即ち、この図に示す電流補償部16では、トランジスタ58C−58Fを、電源とLPF18への出力との間に並列に接続しているが、この接続を変更しても良い。変更される場合は、これらのトランジスタ58C−58Fが、接地電位とLPF18への出力との間に並列に接続される。この様にすることで、トランジスタ58C−58Fが適宜駆動することにより、LPF18に供給される電流が所定の値に減算されて補正される。

【0046】

更にまた、電源と上記出力との間にトランジスタ58C−58Fを設けると共に、それに加えて、上記出力と接地電位との間に同様の構成のトランジスタ58C−58Fを設けても良い。この場合は、これらのトランジスタが適宜駆動することにより、LPF18に供給される電流の加算および減算が行われる。

【0047】

図3(B)を参照して、フェーズエラーが発生した場合、トランジスタ58Cが、発振クロック42の2サイクルに渡りオン動作する。即ち、発振クロック42の1サイクルが1nsの場合は、2nsに渡りトランジスタ58Cがオンする。このことにより、電流値が1/2であるトランジスタが1サイクルに渡りオンしたことと等価となる。ここでは、トランジスタ58Cに加えて、トランジスタ58D、58Eおよび58Fも2サイクルに渡りオン動作している。このことにより、合計で、30/32の電流が補償電流(補正パルス)としてLPF18に供給される。

【0048】

ここで、一般的には、5ビットの分解能を備えた電流制御回路を構成する場合、電流が流れる経路に対して並列に接続された5つのトランジスタが用いられる。この場合は、主電極を流れる電流値が1/2、1/4、1/8、1/16および1/32のトランジスタが用いられる。

【0049】

本実施の形態では、各トランジスタを流れる電流値を制御すると共に、各トランジスタをオン動作させる時間を制御している。即ち、流れる電流値が1/4のトランジスタ58Cを、発振クロック42の2サイクルに渡り連続してオンさせることで、電流値が1/2であるトランジスタの役割をトランジスタ58Cが担っている。この様にすることで、電流補償部に必要とされる回路規模を小さくできる。換言すると、本実施の形態では、4つのトランジスタ58C−58Fで、5ビットの分解能を実現している。

【0050】

更にまた、トランジスタ58C−58Fは必ずしも同じタイミングにてオン動作する必要はなく、タイミングチャートの右端に示すように、異なるタイミングにて動作しても良い(同図右側)。ここでは、フェーズエラーが発生した際に、トランジスタ58Cとトランジスタ58Eが2サイクルに渡りオン動作し、その後に1サイクルに渡りトランジスタ58Fがオン動作することにより、電流補償を行っている。

【0051】

図4のタイミングチャートを参照して、電流補償部16の動作を説明する。ここでは、基準クロック34が発振クロック42に対して位相遅れが生じている。本実施の形態では、比較部14から発生される補正信号(フェーズエラー)に先行して電流補正を行い、更に、この電流補正は補正信号が収束した後も行われている。

【0052】

具体的には、比較部14にて検出されたフェーズエラーが0.65625nsの場合を説明すると、電流補償部16では、フェーズエラーが発生する直前のサイクルから電流補償を行っている。ここでは、トランジスタ58Cおよびトランジスタ58Eを、フェーズエラーが発生する1サイクル前から発生させ、フェーズエラーが含まれるサイクルの終端まで連続して発生させている。ここで、上記したように、トランジスタ58Cの電流量は1/4であり、トランジスタ58Eの電流量は1/16である。そして、トランジスタ58Cおよびトランジスタ58Eがオフした次のサイクルでは、電流量が1/32のトランジスタ58Fが1サイクルに渡りオンして補正電流を供給している。

【0053】

図の最下段に、VCOに供給される電流値(VCO−in)の変動を示す。先ず、トランジスタ58C、58Eがオンするサイクルでは電流値(VCO−in)が増加する。そして、次サイクルに於いてフェーズエラーが発生する期間では、トランジスタ58C、58Eによる電流値よりも、フェーズエラーのマイナスの補正量の方が大きいので、電流値(VCO−in)は減少する。また、このサイクルの他の期間では、トランジスタ58C、58Eを通過する補正電流により、電流値(VCO−in)は増加する。そして、トランジスタ58C、58Eによる電流補正が終了した次のサイクルでは、電流量が1/32であるトランジスタ58Fがオンすることにより、更なる電流補正が行われ、結果的に電流値(VCO−in)は、以前と同様の値となる。

【0054】

本実施の形態では、上記したように、トランジスタ58C−58Fによる電流補正を、フェーズエラーと同期して、あるいは時間的に非常に近くして行っている。従って、フェーズエラーにより誤差が発生している時間を短くして、ジッタの発生を抑制している。また、図4のフェーズエラーを示すチャートを参照すると、フェーズエラーのパルス幅は、VCOから発振される発振クロック42の周波数分解能である。従って、フェーズエラーを示す信号の幅は、発振クロックの1サイクルの幅以下であるので、同期が高速に行われる。

【0055】

更に、上記した電流補償部を、CMOSトランジスタを含むカレントミラー回路で構成すると、LSIの上面に形成されるトランジスタの面積比で、フェーズエラーを示す信号と、補正電流との比を規定することができる。従って、本実施のPLL回路を具現化するLSIでの調整が不要となる。

【0056】

尚、本発明は上記した本実施形態に限定されることはなく、例えば次のように変更することが可能である。

【0057】

図1を参照して、第2ループ52を動作させずに第1ループ50のみを動作させることで、PLL回路10を通常のフラクショナルNPLL回路として使用することができる。この場合は、基準クロック34が逓倍された発振クロック42が出力される。

【0058】

更に、累算部22に入力される逓倍値54の値として整数を設定することにより、PLL回路10を整数PLLとして用いることができる。

【0059】

更にまた、電流補償部16に入力する補正信号として、乱数に基づく信号を採用すると、PLL回路10がスペクトラム拡散PLLとして機能し、発生する副射ノイズを低減することができる。

【図面の簡単な説明】

【0060】

【図1】本発明のPLL回路の構成を示すブロック図である。

【図2】本発明のPLL回路を示す図であり、(A)はレジスタを示す図であり、(B)は基準クロック等を示すタイミングチャートであり、(C)はレジスタに入力される数値を示す表である。

【図3】本発明のPLL回路を示す図であり、(A)は電流補償部16の構成を示す図であり、(B)はタイミングチャートである。

【図4】本発明のPLL回路に含まれる電流補償部の動作を示すタイミングチャートである。

【図5】背景技術のPLL回路を説明するためのブロック図である。

【符号の説明】

【0061】

10 PLL回路

12 発振器

14 比較部

16 電流補償部

18 LPF

20 出力発振部

22 累算部

24 発振器

26 分周部

28 比較部

30 比較部

32 フィルタ

34 基準クロック

36 位相誤差信号

38 補正信号

40 周波数制御信号

42 発振クロック

43 発振クロック

44 補正信号

46 補正信号

48 補正信号

50 第1ループ

52 第2ループ

54 逓倍値

56 チャージポンプ

58A、58B、58C、58D、58E、58F トランジスタ

60 外部参照クロック

62 発振クロック

【特許請求の範囲】

【請求項1】

外部参照クロックが逓倍された発振クロックを出力するPLL回路であり、

分周比の時間平均値が小数点以下を含む値または整数である第1分周比にて、フィードバックされた前記発振クロックを分周する累算部と、

分周された前記発振クロックと基準クロックとを比較して、両者の位相差を示す第1位相誤差信号を出力する第1位相比較部と、

前記累算部からの出力に基づいて、前記第1位相誤差信号を補正して補正信号を発生させる電流補償部と、

前記補正信号を平滑化するループフィルタと、

前記ループフィルタの出力に基づいて制御されて前記発振クロックを発振する出力発振部と、

フィードバックされた前記発振クロックを、第2分周比により分周する分周部と、

分周された前記発振クロックと、前記第1基準クロックよりも周波数が低い前記外部参照クロックとを比較して第2位相誤差信号を出力する第2位相比較部と、

前記第2位相誤差信号を基に、前記累算部が備えるべき前記第1分周比を算出するフィルタと、

を備えることを特徴とするPLL回路。

【請求項2】

前記フィルタでは、

前記分周部の第2分周比と前記外部参照クロックの周波数とから算出される周波数と、

前記累算部の前記第1分周比と前記基準クロックの周波数とから算出される周波数とが、同一となるように前記第1分周比を算出して前記累算部に出力する、

ことを特徴とする請求項1記載のPLL回路。

【請求項3】

前記電流補償部は、電源に接続されたチャージポンプと、前記チャージポンプを構成するトランジスタに並列に接続された複数のトランジスタとを備え、

前記チャージポンプは、前記第1位相比較部から出力される第1位相誤差信号に基づいて動作し、

周期的に発生する位相誤差信号に応じた電流を、前記トランジスタを経由して前記チャージポンプの出力に加えることを特徴とする請求項2記載のPLL回路。

【請求項4】

前記複数のトランジスタは、

主電極を流れる電流値が制御されると共に、

前記発振クロックの1サイクルよりも長くオン動作を保持することを特徴とする請求項3記載のPLL回路。

【請求項5】

前記複数のトランジスタは、

前記位相誤差信号が発生する以前の、前記発振クロックのサイクルから、このサイクルの次サイクルに渡って連続的にオン動作を保持することを特徴とする請求項4記載のPLL回路。

【請求項6】

前記第2比較部は、デジタル回路から構成されるデジタル比較部と、アナログ回路から構成されるアナログ比較部とを含み、

発振クロックの周波数がロックアップするまでの間は前記デジタル比較部が用いられ、前記発振クロックがロックアップした後は、前記アナログ比較部が用いられることを特徴とする請求項6記載のPLL回路。

【請求項1】

外部参照クロックが逓倍された発振クロックを出力するPLL回路であり、

分周比の時間平均値が小数点以下を含む値または整数である第1分周比にて、フィードバックされた前記発振クロックを分周する累算部と、

分周された前記発振クロックと基準クロックとを比較して、両者の位相差を示す第1位相誤差信号を出力する第1位相比較部と、

前記累算部からの出力に基づいて、前記第1位相誤差信号を補正して補正信号を発生させる電流補償部と、

前記補正信号を平滑化するループフィルタと、

前記ループフィルタの出力に基づいて制御されて前記発振クロックを発振する出力発振部と、

フィードバックされた前記発振クロックを、第2分周比により分周する分周部と、

分周された前記発振クロックと、前記第1基準クロックよりも周波数が低い前記外部参照クロックとを比較して第2位相誤差信号を出力する第2位相比較部と、

前記第2位相誤差信号を基に、前記累算部が備えるべき前記第1分周比を算出するフィルタと、

を備えることを特徴とするPLL回路。

【請求項2】

前記フィルタでは、

前記分周部の第2分周比と前記外部参照クロックの周波数とから算出される周波数と、

前記累算部の前記第1分周比と前記基準クロックの周波数とから算出される周波数とが、同一となるように前記第1分周比を算出して前記累算部に出力する、

ことを特徴とする請求項1記載のPLL回路。

【請求項3】

前記電流補償部は、電源に接続されたチャージポンプと、前記チャージポンプを構成するトランジスタに並列に接続された複数のトランジスタとを備え、

前記チャージポンプは、前記第1位相比較部から出力される第1位相誤差信号に基づいて動作し、

周期的に発生する位相誤差信号に応じた電流を、前記トランジスタを経由して前記チャージポンプの出力に加えることを特徴とする請求項2記載のPLL回路。

【請求項4】

前記複数のトランジスタは、

主電極を流れる電流値が制御されると共に、

前記発振クロックの1サイクルよりも長くオン動作を保持することを特徴とする請求項3記載のPLL回路。

【請求項5】

前記複数のトランジスタは、

前記位相誤差信号が発生する以前の、前記発振クロックのサイクルから、このサイクルの次サイクルに渡って連続的にオン動作を保持することを特徴とする請求項4記載のPLL回路。

【請求項6】

前記第2比較部は、デジタル回路から構成されるデジタル比較部と、アナログ回路から構成されるアナログ比較部とを含み、

発振クロックの周波数がロックアップするまでの間は前記デジタル比較部が用いられ、前記発振クロックがロックアップした後は、前記アナログ比較部が用いられることを特徴とする請求項6記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2010−154058(P2010−154058A)

【公開日】平成22年7月8日(2010.7.8)

【国際特許分類】

【出願番号】特願2008−328045(P2008−328045)

【出願日】平成20年12月24日(2008.12.24)

【出願人】(301016159)システムエルエスアイ株式会社 (5)

【Fターム(参考)】

【公開日】平成22年7月8日(2010.7.8)

【国際特許分類】

【出願日】平成20年12月24日(2008.12.24)

【出願人】(301016159)システムエルエスアイ株式会社 (5)

【Fターム(参考)】

[ Back to top ]