PLL回路

【課題】ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路を提供する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

【解決手段】PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、信号遅延に応じて第3のクロック信号を発振する発振回路とを含み、フィルタ回路は、第1の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、第2の遅延回路により第1のクロック信号をフィルタ処理して第2のクロック信号を生成する。

【発明の詳細な説明】

【技術分野】

【0001】

本願開示は、一般に電子回路に関し、詳しくは位相の自動制御を行なう回路に関する。

【背景技術】

【0002】

PLL(Phase Locked Loop)回路は基準クロック信号を受け取り、この基準クロック信号に位相の同期した発振信号を出力する。位相同期がとれている状態で、基準クロック信号にノイズが混入すると、このノイズが原因でPLLのロックがはずれる(位相の同期がはずれる)という不具合が発生する場合がある。このような不具合が発生しないように、一般的には、基準クロック信号をノイズフィルタ回路に通過させてノイズを除去してから、PLLの位相比較回路に入力する。

【0003】

上記のようなノイズフィルタ回路はローパスフィルタ特性を有する。一般に、ノイズを除去する目的においては、フィルタのカットオフ周波数をできるだけ低くすることが好ましい。しかしながら、PLL回路の入力部分においてカットオフ周波数を低くしすぎると、基準クロック信号自身が検出可能な信号としてフィルタを通過できなくなってしまう。従って、動作周波数などの動作条件等を含むPLL回路の用途に合わせて、適切な特性を有するフィルタを設計してやらなければならないという問題があった。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平4−101577号公報

【特許文献2】特開2000−269947号公報

【特許文献3】特開2001−267914号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以上を鑑みると、ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路が望まれる。

【課題を解決するための手段】

【0006】

PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記第3のクロック信号を発振する発振回路とを含み、前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とする。

【発明の効果】

【0007】

本願開示の少なくとも1つの実施例によれば、フィルタ回路は、発振回路中の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす遅延回路を含む。これにより、発振周波数に応じたフィルタ処理が可能となる。また発振ループの遅延回路とフィルタ処理の遅延回路とに同一の回路構成の回路を用いることにより、発振周期の変化量に対するフィルタ処理特性の変化量を、発振周波数の値に関わらず略一定として、安定した制御を実現することができる。またプロセス変動や温度変化などにより発振ループの遅延回路の特性が変動しても、フィルタ処理用の遅延回路の特性も同様に変動するので、種々の条件下で安定した制御を実現することができる。

【図面の簡単な説明】

【0008】

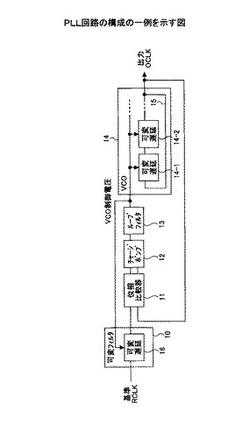

【図1】PLL回路の構成の一例を示す図である。

【図2】電圧制御発振器の構成の一例を示す図である。

【図3】可変フィルタ回路の構成の一例を示す図である。

【図4】PLL回路の構成の別の一例を示す図である。

【図5】V/I変換器の構成の一例を示す図である。

【図6】電流制御発振器の構成の一例を示す図である。

【図7】可変フィルタ回路の構成の一例を示す図である。

【図8】PLL回路の構成の更に別の一例を示す図である。

【図9】電圧変換器の構成の一例を示す図である。

【図10】PLL回路の構成の更に別の一例を示す図である。

【図11】電流変換器の構成の一例を示す図である。

【図12】PLL回路の構成の更に別の一例を示す図である。

【図13】PLL回路の構成の更に別の一例を示す図である。

【図14】図13のPLL回路の構成の変形例を示す図である。

【図15】図13のPLL回路の構成の別の変形例を示す図である。

【図16】位相比較器の回路構成の一例を示す図である。

【図17】図13のPLL回路の構成の更に別の変形例を示す図である。

【図18】ロック検出回路の構成の一例を示す図である。

【図19】図18のロック検出回路の動作を説明するための図である。

【図20】PLL回路を内蔵するシステムの構成の一例を示す図である。

【発明を実施するための形態】

【0009】

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

【0010】

図1は、PLL回路の構成の一例を示す図である。図1に示すPLL回路は、可変フィルタ回路10、位相比較器11、チャージポンプ12、ループフィルタ13、及び電圧制御発振器(VCO:Voltage Controlled Oscillator)14を含む。可変フィルタ回路10は、基準クロック信号RCLKをフィルタ処理して、フィルタ処理後のクロック信号を生成する。位相比較器11は、フィルタ処理後のクロック信号と出力クロック信号OCLKとの位相比較を行い、位相比較結果を示す信号を生成する。チャージポンプ12は、位相比較器11からの位相比較結果を示す信号に基づいて、位相比較結果に応じた電圧信号を生成する。ループフィルタ13は、チャージポンプ12からの電圧信号をローパスフィルタ処理して実効的に積分処理することにより、不必要な細かい変動を除去し、位相比較結果に応じた制御信号を生成する。電圧制御発振器14は、入力電圧値に応じた発振周波数で発振する発振器であり、少なくとも1つ又は複数の可変遅延回路14−1、14−2、・・・により構成される発振ループ15を有する。電圧制御発振器14は、ループフィルタ13からの制御信号の電圧値に応じた信号遅延をもたらす遅延回路(例えば14−1)を少なくとも含み、この信号遅延に応じて出力クロック信号OCLKを発振する。ここで各可変遅延回路14−1、14−2、・・・は、互いに同一の構成である。例えば、電圧制御発振器14の複数の可変遅延回路の個数が3つであり、発振周波数が100MHzの場合、可変遅延回路の遅延は1/100÷6≒1.6nsとなる。なおここで、各可変遅延回路は入力の論理値に対して出力の論理値を反転させるインバータ形式の回路であるとして、除算の除数を3の2倍の6としている。

【0011】

図1の構成において、可変フィルタ回路10は、前記遅延回路(例えば14−1)と同一構成であり前記制御信号の電圧値に応じた信号遅延をもたらす可変遅延回路16を含む。可変フィルタ回路10は、可変遅延回路16により基準クロック信号RCLKをフィルタ処理することにより、フィルタ処理後のクロック信号を生成する。このように、出力クロック信号OCLKの発振周波数を制御する制御信号の電圧に応じて、可変遅延回路16によりフィルタ処理することにより、発振周波数に応じたフィルタ処理が可能となる。また発振ループの可変遅延回路とフィルタ処理の可変遅延回路とに、同一の回路構成の回路を用いている。これにより、発振周期の変化量に対するフィルタ処理特性の変化量を、発振周波数の値に関わらず略一定として、安定した制御を実現することができる。またプロセス変動や温度変化などにより発振ループの可変遅延回路の特性が変動しても、フィルタ処理用の可変遅延回路の特性も同様に変動するので、種々の条件下で安定した制御を実現することができる。

【0012】

図2は、電圧制御発振器14の構成の一例を示す図である。図2に示す電圧制御発振器14は、PMOSトランジスタ20及び21、NMOSトランジスタ22及び23、及び抵抗24を含む。電圧制御発振器14は更に、PMOSトランジスタ25−1乃至25−3、NMOSトランジスタ26−1乃至26−3、インバータ27−1乃至27−3、及び容量素子28−1乃至28−3を含む。PMOSトランジスタ25−1、NMOSトランジスタ26−1、インバータ27−1、及び容量素子28−1が、第1の可変遅延回路14−1を構成する。PMOSトランジスタ25−2、NMOSトランジスタ26−2、インバータ27−2、及び容量素子28−2が、第2の可変遅延回路14−2を構成する。PMOSトランジスタ25−3、NMOSトランジスタ26−3、インバータ27−3、及び容量素子28−3が、第3の可変遅延回路14−3を構成する。第1乃至第3の可変遅延回路14−1乃至14−3は縦続接続され、第3の可変遅延回路14−3の出力が第1の可変遅延回路14−1の入力に接続されて、発振ループ15を形成している。

【0013】

図1に示すループフィルタ13からの制御信号電圧がNMOSトランジスタ22のゲートに印加される。これにより、NMOSトランジスタ22には制御信号電圧に応じた電流量Idのドレイン電流が流れる。この時、NMOSトランジスタ22に直列に接続されるPMOSトランジスタ20にも同一の電流量Idの電流が流れる。PMOSトランジスタ20と21とはカレントミラー回路を形成しており、PMOSトランジスタ21にも上記と同一の電流量Idの電流が流れる。更に、PMOSトランジスタ21に直列に接続されるNMOSトランジスタ23にも同一の電流量Idの電流が流れる。この電流量Idの電流を流すPMOSトランジスタ20及び21のゲート電圧が、遅延制御信号Pとして、PMOSトランジスタ25−1乃至25−3のゲートに印加される。また、電流量Idの電流を流すNMOSトランジスタ23のゲート電圧が、遅延制御信号Nとして、NMOSトランジスタ26−1乃至26−3のゲートに印加される。従って、図1に示すループフィルタ13からの制御信号電圧に応じて、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値(電流量)が変化する。

【0014】

ループフィルタ13からの制御信号電圧が低くなり、上記抵抗値が増大(電流量が減少)すると、容量素子28−1乃至28−3の充放電速度が低下して信号波形の遷移が緩やかになる。その結果、インバータ27−1乃至27−3の出力信号の遷移タイミングが遅くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が長くなる。このようにして、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値が増大すると、第1乃至第3の可変遅延回路14−1乃至14−3の各々の遅延時間が長くなる。即ち、ループフィルタ13からの制御信号電圧が低くなると、発振ループ15の発振周波数が低くなる。

【0015】

逆にループフィルタ13からの制御信号電圧が高くなり、抵抗値が減少(電流量が増大)すると、容量素子28−1乃至28−3の充放電速度が上昇して信号波形の遷移が急峻になる。その結果、インバータ27−1乃至27−3の出力信号の遷移タイミングが早くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が短くなる。このようにして、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値が減少すると、第1乃至第3の可変遅延回路14−1乃至14−3の各々の遅延時間が短くなる。即ち、ループフィルタ13からの制御信号電圧が高くなると、発振ループ15の発振周波数が高くなる。

【0016】

図3は、可変フィルタ回路10の構成の一例を示す図である。図3に示す可変フィルタ回路10は、PMOSトランジスタ30及び31、NMOSトランジスタ32及び33、及び抵抗34を含む。可変フィルタ回路10は更に、PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38を含む。PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38が、可変遅延回路16(図1参照)を構成する。

【0017】

図1に示すループフィルタ13からの制御信号電圧がNMOSトランジスタ32のゲートに印加される。これにより、NMOSトランジスタ32には制御信号電圧に応じた電流量Idのドレイン電流が流れる。この時、NMOSトランジスタ32に直列に接続されるPMOSトランジスタ30にも同一の電流量Idの電流が流れる。PMOSトランジスタ30と31とはカレントミラー回路を形成しており、PMOSトランジスタ31にも上記と同一の電流量Idの電流が流れる。更に、PMOSトランジスタ31に直列に接続されるNMOSトランジスタ33にも同一の電流量Idの電流が流れる。この電流量Idの電流を流すPMOSトランジスタ30及び31のゲート電圧が、遅延制御信号Pとして、PMOSトランジスタ35のゲートに印加される。また、電流量Idの電流を流すNMOSトランジスタ33のゲート電圧が、遅延制御信号Nとして、NMOSトランジスタ36のゲートに印加される。従って、図1に示すループフィルタ13からの制御信号電圧に応じて、PMOSトランジスタ35及びNMOSトランジスタ36の抵抗値が変化する。

【0018】

ループフィルタ13からの制御信号電圧が低くなり、上記抵抗値が増大(電流量が減少)すると、容量素子38の充放電速度が低下して信号波形の遷移が緩やかになる。その結果、インバータ37の出力信号の遷移タイミングが遅くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が長くなる。またその際、フィルタ入力信号にノイズが含まれる場合に、フィルタ出力信号にノイズが現れるために最低限必要なノイズの幅及び高さが大きくなる。即ち、ループフィルタ13からの制御信号電圧が低くなると、より大きなノイズを除去することができるようになる。

【0019】

逆にループフィルタ13からの制御信号電圧が高くなり、抵抗値が減少(電流量が増大)すると、容量素子38の充放電速度が上昇して信号波形の遷移が急峻になる。その結果、インバータ37の出力信号の遷移タイミングが早くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が短くなる。またその際、フィルタ入力信号にノイズが含まれる場合に、フィルタ出力信号にノイズが現れるために最低限必要なノイズの幅及び高さが小さくなる。即ち、ループフィルタ13からの制御信号電圧が高くなると、除去可能なノイズがより小さくなる。

【0020】

図4は、PLL回路の構成の別の一例を示す図である。図4において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。図4に示すPLL回路は、図1に示すPLL回路と比較して、V/I変換器17が設けられ、発振周波数を電圧制御ではなく電流制御する点が異なる。またこれに伴い、電圧制御発振器14の代りに電流制御発振器(ICO)14Aが設けられ、また可変フィルタ回路10の代りに可変フィルタ回路10Aが設けられる。電圧制御の代りに電流制御する点を除けば、図4のPLL回路の動作は図1のPLL回路の動作と同一である。

【0021】

V/I変換器17は、ループフィルタ13からの制御信号の電圧値を電流値に変換する。電流制御発振器14Aは、入力電流値に応じた発振周波数で発振する発振器であり、少なくとも1つ又は複数の可変遅延回路14A−1、14A−2、・・・により構成される発振ループ15Aを有する。電流制御発振器14Aは、V/I変換器17からの制御信号の電流値に応じた信号遅延をもたらす遅延回路(例えば14−1)を少なくとも含み、この信号遅延に応じて出力クロック信号OCLKを発振する。可変フィルタ回路10Aは、前記遅延回路(例えば14−1)と同一構成であり前記制御信号の電流値に応じた信号遅延をもたらす可変遅延回路16Aを含む。可変フィルタ回路10Aは、可変遅延回路16Aにより基準クロック信号RCLKをフィルタ処理することにより、フィルタ処理後のクロック信号を生成する。

【0022】

図5は、V/I変換器17の構成の一例を示す図である。図5に示すV/I変換器17は、PMOSトランジスタ40乃至42、NMOSトランジスタ43、及び抵抗44を含む。図4に示すループフィルタ13からの制御信号電圧がNMOSトランジスタ43のゲートに印加される。これにより、NMOSトランジスタ43には制御信号電圧に応じた電流量Idのドレイン電流が流れる。この時、NMOSトランジスタ43に直列に接続されるPMOSトランジスタ40にも同一の電流量Idの電流が流れる。PMOSトランジスタ40,41,42はカレントミラー回路を形成しており、PMOSトランジスタ41及び42にも上記と同一の電流量Idの電流が流れる。これらPMOSトランジスタ41及び42に流れる電流のうち、一方が電流制御発振器14Aに供給され、他方が可変フィルタ回路10Aに供給される。

【0023】

図6は、電流制御発振器14Aの構成の一例を示す図である。図6において、図2と同一の構成要素は同一の番号で参照し、その説明は省略する。図6に示す電流制御発振器14Aは、PMOSトランジスタ50、及びNMOSトランジスタ51及び52を含む。電流制御発振器14Aは更に、PMOSトランジスタ25−1乃至25−3、NMOSトランジスタ26−1乃至26−3、インバータ27−1乃至27−3、及び容量素子28−1乃至28−3を含む。第1乃至第3の可変遅延回路14A−1乃至14A−3は縦続接続され、第3の可変遅延回路14A−3の出力が第1の可変遅延回路14A−1の入力に接続されて、発振ループ15Aを形成している。

【0024】

図4に示すV/I変換器17からの制御信号電流がNMOSトランジスタ51に流される。NMOSトランジスタ51と52とはカレントミラー回路を形成しており、NMOSトランジスタ52にも上記と同一の電流量の電流が流れる。更に、NMOSトランジスタ52に直列に接続されるPMOSトランジスタ50にも同一の電流量の電流が流れる。この電流量の電流を流すPMOSトランジスタ50のゲート電圧が、PMOSトランジスタ25−1乃至25−3のゲートに印加される。また上記の電流量の電流を流すNMOSトランジスタ52のゲート電圧が、NMOSトランジスタ26−1乃至26−3のゲートに印加される。従って、図4に示すV/I変換器17からの制御信号電流に応じて、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値(電流量)が変化し、発振ループ15Aの発振周波数が変化する。

【0025】

図7は、可変フィルタ回路10Aの構成の一例を示す図である。図7において、図3と同一の構成要素は同一の番号で参照し、その説明は省略する。図7に示す可変フィルタ回路10Aは、PMOSトランジスタ60、及びNMOSトランジスタ61及び62を含む。可変フィルタ回路10Aは更に、PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38を含む。PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38が、可変遅延回路16A(図4参照)を構成する。

【0026】

図4に示すV/I変換器17からの制御信号電流がNMOSトランジスタ61に流される。NMOSトランジスタ61と62とはカレントミラー回路を形成しており、NMOSトランジスタ62にも上記と同一の電流量の電流が流れる。更に、NMOSトランジスタ62に直列に接続されるPMOSトランジスタ60にも同一の電流量の電流が流れる。この電流量の電流を流すPMOSトランジスタ60のゲート電圧が、PMOSトランジスタ35のゲートに印加される。また上記の電流量の電流を流すNMOSトランジスタ62のゲート電圧が、NMOSトランジスタ36のゲートに印加される。従って、図4に示すV/I変換器17からの制御信号電流に応じて、可変フィルタ回路10Aにより除去可能なノイズの大きさが変化する。

【0027】

図8は、PLL回路の構成の更に別の一例を示す図である。図8において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。図8に示すPLL回路は、図1に示すPLL回路と比較して、制御信号の電圧値を変換する電圧変換器18が設けられている点が異なる。電圧変換器18により電圧値を変換した後の制御信号の電圧値に応じて、可変フィルタ回路10の可変遅延回路16が動作する。電圧変換器18は、CPU等の外部からのフィルタ特性制御信号に応じて、変換前の電圧値と変換後の電圧値との関係を調整する。

【0028】

図9は、電圧変換器18の構成の一例を示す図である。図9に示す電圧変換器18は、オペアンプ70、複数の直列接続された抵抗素子71、及び複数のスイッチ回路72を含む。オペアンプ70は、電圧変換器18への入力電圧を非反転入力端に受け取る。オペアンプ70の出力は、複数の抵抗素子71の列の一端に接続される。複数の抵抗素子71の列の他端はグランドに接続される。複数の抵抗素子71の列で分圧された中間点の電圧が、オペアンプ70の反転入力端にフィードバックされる。複数の抵抗素子71の列により分圧され生成された複数の電圧は、複数のスイッチ回路72のうちの導通した1つにより選択され、電圧変換器18の出力電圧となる。複数のスイッチ回路72のうちの何れを導通させるかは、外部から供給される出力電圧選択信号(フィルタ特性制御信号)により決定される。これにより、出力電圧(ループフィルタ13の出力電圧)よりも高い電圧或いは低い電圧を自由に生成して、可変遅延回路16に供給することができる。

【0029】

図10は、PLL回路の構成の更に別の一例を示す図である。図10において、図4と同一の構成要素は同一の番号で参照し、その説明は省略する。図10に示すPLL回路は、図4に示すPLL回路と比較して、制御信号の電流値を変換する電流変換器18Aが設けられている点が異なる。電流変換器18Aにより電流値を変換した後の制御信号の電流値に応じて、可変フィルタ回路10Aの可変遅延回路16Aが動作する。電流変換器18Aは、CPU等の外部からのフィルタ特性制御信号に応じて、変換前の電流値と変換後の電流値との関係を調整する。

【0030】

図11は、電流変換器18Aの構成の一例を示す図である。図11に示す電流変換器18Aは、PMOSトランジスタ80、NMOSトランジスタ81及び82、複数のPMOSトランジスタ83、及び複数のスイッチ回路84を含む。図10に示すV/I変換器17からの制御信号電流がNMOSトランジスタ81に流される。NMOSトランジスタ81と82とはカレントミラー回路を形成しており、NMOSトランジスタ82にも上記と同一の電流量の電流が流れる。更に、NMOSトランジスタ82に直列に接続されるPMOSトランジスタ80にも同一の電流量の電流が流れる。この電流量の電流を流すPMOSトランジスタ80のゲート電圧が、複数のPMOSトランジスタ83のゲートに印加されており、カレントミラー回路を構成している。複数のPMOSトランジスタ83により生成される複数の電流は、複数のスイッチ回路84のうちの導通した1つ又は複数のスイッチ回路を介して、電流変換器18の出力電流として送出される。複数のスイッチ回路72のうちの幾つを導通させるかは、外部から供給される出力電流選択信号(フィルタ特性制御信号)により決定される。これにより、出力電流(V/I変換器17の出力電流)よりも大きい電流を自由に生成して、可変遅延回路16Aに供給することができる。なおNMOSトランジスタ81と82とのゲート幅を異ならせ、NMOSトランジスタ82に流れるドレイン電流をNMOSトランジスタ81に流れるドレイン電流の1/n(n:自然数)としてもよい。この場合、出力電流(V/I変換器17の出力電流)よりも小さい電流或いは大きい電流を自由に生成して、可変遅延回路16Aに供給することができる。

【0031】

図12は、PLL回路の構成の更に別の一例を示す図である。図12において、図8と同一の構成要素は同一の番号で参照し、その説明は省略する。図12に示すPLL回路は、図8に示すPLL回路と比較して、N分周器90、M分周器91、及びデコーダ92が追加で設けられている点が異なる。N分周器90は、分周設定信号に応じた分周率Nにより、可変フィルタ回路10の出力するフィルタ処理後のクロック信号を分周する。M分周器91は、分周設定信号に応じた分周率Mにより、電圧制御発振器14の出力する出力クロック信号OCLKを分周する。これら分周器90及び91による分周後のクロック信号を位相比較対象の信号として位相比較器11に入力する。デコーダ92は、N分周を指定する分周設定信号とM分周を指定する分周設定信号とをデコードして、フィルタ特性制御信号を生成する。電圧変換器18は、このフィルタ特性制御信号に応じて、変換前の電圧値と変換後の電圧値との関係を調整する。なお図12の構成では、N分周器90とM分周器91との2つの分周器を設けているが、何れか一方のみを設けた構成としてもよい。

【0032】

電圧変換器18が設けられていない図1の構成において、適切なノイズ除去が実現されているとする。そのままの条件で、図8に示すようにN分周器90とM分周器91との2つの分周器を設けた場合を考える。この場合、位相同期がとれた状態では、基準クロック信号RCLKのN分の1が出力クロック信号OCLKのM分の1に等しくなるので、基準クロック信号RCLKの周波数は出力周波数のN/Mとなる。分周器が設けられていない状態(即ちN=M=1)において可変遅延回路16の制御電圧が適正値であったのだから、図8に示す構成の場合、電圧変換器18から可変遅延回路16に印加される制御電圧を、上記適正値の例えばN/M倍とすればよい。即ち、電圧変換器18により入力電圧のN/M倍の電圧を生成するような信号を、デコーダ92により生成すればよい。

【0033】

図13は、PLL回路の構成の更に別の一例を示す図である。図13において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。図13に示すPLL回路は、図1に示すPLL回路と比較して、スイッチ回路19が設けられている点が異なる。スイッチ回路19は、図示下側のノードに接続されると、基準クロック信号RCLKを可変フィルタ回路10を介することなく位相比較対象の信号として位相比較器11に供給する第1の経路を選択する。またスイッチ回路19は、図示上側のノードに接続されると、基準クロック信号RCLKから可変フィルタ回路10を介して得られるフィルタ処理後のクロック信号を、位相比較対象の信号として位相比較器11に供給する第2の経路を選択する。スイッチ回路19は、上記第1の経路と第2の経路との何れか一方を選択して切り替え可能な構成となっている。

【0034】

スイッチ回路19は、CPU等の外部からのフィルタバイパス制御信号に応じて、切り替え動作を実行してよい。例えば、PLL回路が位相同期を確立するまでの初期動作時(ロック前)には基準クロック信号RCLKを直接に位相比較器11に供給し、PLL回路が位相同期を確立した後(ロック後)においてはフィルタ処理後のクロック信号を位相比較器11に供給してよい。仮に位相をロックするための初期動作時において、位相同期確立に必要なクロックのパルス信号までも可変フィルタ回路10を通過できないような初期状態に可変フィルタ回路10が設定されているとすると、PLL回路が全く所望の動作を実行できないことになる。上記のように、位相をロックするための初期動作時において、基準クロック信号RCLKを直接に位相比較器11に供給するようにすれば、可変フィルタ回路10の初期状態に関わらず、確実に位相同期を確立することができる。また位相同期の確立後は、フィルタ処理後のクロック信号を位相比較器11に供給することで、確実にノイズの影響を除去することができる。

【0035】

図14は、図13のPLL回路の構成の変形例を示す図である。図14において、図13と同一の構成要素は同一の番号で参照し、その説明は省略する。図14に示すPLL回路は、図13に示すPLL回路と比較して、カウンタ100が設けられている点が異なる。カウンタ100は、基準クロック信号RCLKのパルス数を計数し、計数値が所定値になると出力をアサートする。カウンタ100の出力のアサートに応じてスイッチ回路19が前記第1の経路から前記第2の経路に切り替える。上記所定値として、位相同期を確立させる動作(位相ロック動作)が終了するのに必要なパルス数を設定すればよい。

【0036】

図15は、図13のPLL回路の構成の別の変形例を示す図である。図15において、図13と同一の構成要素は同一の番号で参照し、その説明は省略する。図15に示すPLL回路は、図13に示すPLL回路と比較して、ロック検出回路101が設けられている点が異なる。ロック検出回路101は、位相比較器11の出力する制御信号に基づいて位相が同期した状態を検出すると出力をアサートする。このロック検出回路101の出力のアサートに応じて、スイッチ回路19が、前記第1の経路から前記第2の経路に切り替える。

【0037】

図16は、位相比較器11の回路構成の一例を示す図である。図16の位相比較器11は、NAND回路111乃至118、インバータ119乃至121、及びAND回路122を含む。位相比較器11は、NAND回路118の出力である周波数アップ信号出力がHIGHであり、AND回路122の出力である周波数ダウン信号出力がLOWである状態で、入力の変化を待ち受ける。周波数アップ信号出力のHIGH及び周波数ダウン信号出力のLOWは、それぞれの信号のネゲート状態である。周波数アップ信号出力は次段のチャージポンプ12のPMOSトランジスタのゲートに印加され、周波数ダウン信号出力は次段のチャージポンプ12のNMOSトランジスタのゲートに印加される。これらのPMOSトランジスタ及びNMOSトランジスタにより、チャージポンプ12の容量素子への充放電が行なわれる。

【0038】

上記の待ち受け状態で、例えば基準クロック信号が比較クロック信号よりも先にHIGHからLOWに変化すると、NAND回路111の出力がHIGHに変化し、NAND回路118の周波数アップ信号出力がLOWに変化する。即ち周波数アップ信号出力がアサート状態(LOW)となる。その後、比較クロック信号がHIGHからLOWに変化すると、NAND回路116の出力がHIGHに変化し、AND回路122の周波数ダウン信号出力がHIGHに変化する。即ち周波数ダウン信号出力がアサート状態(HIGH)となる。またNAND回路116の出力のHIGHへの変化により、NAND回路117の入力が全てHIGHとなり、NAND回路117の出力がHIGHからLOWへと変化する。これにより、周波数アップ信号出力及び周波数ダウン信号出力がそれぞれHIGH及びLOWへと同時に変化すると共に、位相比較器11がリセットされる。その後、基準クロック信号と比較クロック信号とがHIGHに戻ると、位相比較器11は上記の待ち受け状態に戻る。

【0039】

また上記の待ち受け状態で、基準クロック信号と比較クロック信号とが同時にHIGHからLOWに変化すると、周波数アップ信号出力のLOWへの変化及び周波数ダウン信号出力のHIGHへの変化が同時に起こる。更に、その直後に、位相比較器11のリセットとともに周波数アップ信号出力のHIGHへの変化及び周波数ダウン信号出力のLOWへの変化が同時に起こる。

【0040】

このように、クロックの位相同期がとれている状態では、周波数アップ信号出力のアサート状態と周波数ダウン信号出力のアサート状態とが同一期間に発生する。またクロック間に位相差がある状態では、位相差に等しい期間だけ一方の信号出力のアサート状態が他方の信号のアサート状態よりも長く発生する。このような位相比較結果信号を出力する位相比較器11に対しては、図15に示すロック検出回路101にはXOR回路(排他的論理和回路)を用いることができる。クロックの位相同期がとれている状態では、周波数アップ信号出力の論理値と周波数ダウン信号出力の論理値とは常に逆になっているので、XOR回路の出力はHIGHに固定される。またクロック間に位相差がある状態では、位相差に等しい期間だけ両方の信号出力が同一論理値となるので、XOR回路の出力は位相差に等しい期間LOWとなる。ロック検出回路101は、XOR回路の出力がHIGH固定であることを検出すると、スイッチ回路19を前記第1の経路から前記第2の経路に切り替えてよい。

【0041】

図17は、図13のPLL回路の構成の更に別の変形例を示す図である。図17において、図13と同一の構成要素は同一の番号で参照し、その説明は省略する。図17に示すPLL回路は、図13に示すPLL回路と比較して、ロック検出回路102が設けられている点が異なる。ロック検出回路102は、位相比較器11の位相比較結果に応じてループフィルタ13が出力する制御信号に基づいて、位相が同期した状態を検出すると出力をアサートする。このロック検出回路102の出力のアサートに応じて、スイッチ回路19が、前記第1の経路から前記第2の経路に切り替える。

【0042】

図18は、ロック検出回路102の構成の一例を示す図である。図18に示すロック検出回路102は、容量素子131、抵抗素子132、及びコンパレータ133を含む。容量素子131と抵抗素子132とが微分回路を構成し、入力されるVCO制御電圧波形の微分に相当する電圧を生成する。コンパレータ133は、微分電圧と基準電圧とを比較して、微分電圧が基準電圧よりも低くなると出力をHIGHにする。

【0043】

図19は、図18のロック検出回路102の動作を説明するための図である。図19において、ループフィルタ13から電圧制御発振器14に印加されるVCO制御電圧は、例えば電圧波形140のような波形となる。即ち、PLL回路の動作が開始すると、フィードバック制御に基づいて、位相比較器11による位相比較結果に応じてVCO制御電圧が調整される。クロック間の位相が同期するVCO制御電圧が得られると(即ちロック状態となると)、その後VCO制御電圧は略一定値で推移する。

【0044】

電圧波形141は、電圧波形140を微分した波形であり、図18に示すコンパレータ133の反転入力端に入力される電圧波形である。また電圧波形142は、基準電圧であり、コンパレータ133の非反転入力端に入力される電圧波形である。コンパレータ133は、微分電圧と基準電圧とを比較して、その大小関係に応じて電圧波形143として示す出力電圧を生成する。コンパレータ133の出力電圧は、PLL回路の動作開始タイミングT0から暫くの期間LOWとなり、位相同期が確立されたタイミングT1においてHIGHとなる。ロック検出回路102は、コンパレータ133の出力によりスイッチ回路19を制御し、コンパレータ133の出力がHIGHになるとスイッチ回路19を前記第1の経路から前記第2の経路に切り替えてよい。

【0045】

図20は、PLL回路を内蔵するシステムの構成の一例を示す図である。例えば半導体装置として単一のチップとして構成されるシステム150は、CPU151、フラッシュメモリ152、RAM153、クロック制御回路154、各種リソース156、及びバス157を含む。CPU151、フラッシュメモリ152、RAM153、クロック制御回路154、及び各種リソース156は、バス157を介して、互いに信号をやり取りする。クロック制御回路154は、前述の例えば図8又は図9に示すPLL回路155を含み、基準クロック信号に応じて出力クロック信号を生成する。クロック制御回路154が生成した出力クロック信号は、システム150内の各ユニットに供給されて、システムのクロック同期した動作を実現する。PLL回路155は、CPU151からの信号に応じて制御信号の値を変換する変換回路18又は18A(図8及び図9参照)を含む。

【0046】

このクロック制御回路154のPLL回路155は、CPU151からの分周設定信号に応じた分周率により基準クロック信号及び出力クロック信号の少なくとも一方を分周する分周器(例えば図12のN分周器90又はM分周器91)を更に含んでもよい。この場合、変換回路18は分周設定信号に応じて制御信号の値を変換する。またPLL回路155は、前述のスイッチ回路19(図13,14,15,17参照)を含んでもよい。

【0047】

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

【0048】

なお本願は以下の内容を含むものである。

(付記1)

第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、

前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記第3のクロック信号を発振する発振回路と

を含み、

前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とするPLL回路。

(付記2)

前記制御信号の値を変換する変換回路を更に含み、前記値を変換した後の前記制御信号の値に応じて前記第2の遅延回路は動作することを特徴とする付記1記載のPLL回路。

(付記3)

分周設定信号に応じた分周率により前記第2のクロック信号及び前記第3のクロック信号の少なくとも一方を分周する分周器を更に含み、前記分周器による分周後のクロック信号を位相比較対象の信号として前記位相比較回路に入力し、前記変換回路は前記分周設定信号に応じて前記制御信号の値を変換することを特徴とする付記2記載のPLL回路。

(付記4)

前記第1のクロック信号を前記フィルタ回路を介することなく位相比較対象の信号として前記位相比較回路に供給する第1の経路と、前記第1のクロック信号から前記フィルタ回路を介して得られる前記第2のクロック信号を位相比較対象の信号として前記位相比較回路に供給する第2の経路と、を選択して切り替え可能なスイッチ回路を更に含むことを特徴とする付記1乃至3何れか一項記載のPLL回路。

(付記5)

前記第1のクロック信号のパルス数を計数し、計数値が所定値になると出力をアサートするカウンタを更に含み、前記カウンタの出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記4記載のPLL回路。

(付記6)

前記位相比較回路の出力する前記制御信号に基づいて前記第2のクロック信号と前記第3のクロック信号との位相が同期した状態を検出すると出力をアサートする検出回路を更に含み、前記検出回路の出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記4記載のPLL回路。

(付記7)

基準クロック信号に応じて出力クロック信号を生成するクロック制御回路と、

処理ユニットと

を含み、前記クロック制御回路は、

前記基準クロック信号をフィルタ処理して第1のクロック信号を生成するフィルタ回路と、

前記第1のクロック信号と前記出力クロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記出力クロック信号を発振する発振回路と、

前記処理ユニットからの信号に応じて前記制御信号の値を変換する変換回路と

を含み、

前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記値を変換した後の前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記基準クロック信号をフィルタ処理して前記第1のクロック信号を生成することを特徴とするシステム。

(付記8)

前記クロック制御回路は、前記処理ユニットからの分周設定信号に応じた分周率により前記第1のクロック信号及び前記出力クロック信号の少なくとも一方を分周する分周器を更に含み、前記分周器による分周後のクロック信号を位相比較対象の信号として前記位相比較回路に入力し、前記変換回路は前記分周設定信号に応じて前記制御信号の値を変換することを特徴とする付記7記載のシステム。

(付記9)

前記クロック制御回路は、前記基準クロック信号を前記フィルタ回路を介することなく位相比較対象の信号として前記位相比較回路に供給する第1の経路と、前記第1のクロック信号から前記フィルタ回路を介して得られる前記第2のクロック信号を位相比較対象の信号として前記位相比較回路に供給する第2の経路と、を選択して切り替え可能なスイッチ回路を更に含むことを特徴とする付記7又は8記載のシステム。

(付記10)

前記クロック制御回路は、前記基準クロック信号のパルス数を計数し、計数値が所定値になると出力をアサートするカウンタを更に含み、前記カウンタの出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記9記載のシステム。

(付記11)

前記位相比較回路の出力する前記制御信号に基づいて前記第1のクロック信号と前記出力クロック信号との位相が同期した状態を検出すると出力をアサートする検出回路を更に含み、前記検出回路の出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記9記載のシステム。

(付記12)

第1のクロック信号をフィルタ処理して第2のクロック信号を生成し、

前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成し、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を利用して、前記信号遅延に応じた前記第3のクロック信号を発振する

各段階を含み、

前記フィルタ処理は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を利用し、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とするPLL回路のノイズ除去方法。

【符号の説明】

【0049】

10 可変フィルタ回路

11 位相比較器

12 チャージポンプ

13 ループフィルタ

14 電圧制御発振器

【技術分野】

【0001】

本願開示は、一般に電子回路に関し、詳しくは位相の自動制御を行なう回路に関する。

【背景技術】

【0002】

PLL(Phase Locked Loop)回路は基準クロック信号を受け取り、この基準クロック信号に位相の同期した発振信号を出力する。位相同期がとれている状態で、基準クロック信号にノイズが混入すると、このノイズが原因でPLLのロックがはずれる(位相の同期がはずれる)という不具合が発生する場合がある。このような不具合が発生しないように、一般的には、基準クロック信号をノイズフィルタ回路に通過させてノイズを除去してから、PLLの位相比較回路に入力する。

【0003】

上記のようなノイズフィルタ回路はローパスフィルタ特性を有する。一般に、ノイズを除去する目的においては、フィルタのカットオフ周波数をできるだけ低くすることが好ましい。しかしながら、PLL回路の入力部分においてカットオフ周波数を低くしすぎると、基準クロック信号自身が検出可能な信号としてフィルタを通過できなくなってしまう。従って、動作周波数などの動作条件等を含むPLL回路の用途に合わせて、適切な特性を有するフィルタを設計してやらなければならないという問題があった。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開平4−101577号公報

【特許文献2】特開2000−269947号公報

【特許文献3】特開2001−267914号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

以上を鑑みると、ノイズフィルタ回路の特定を適切に自動設定可能なPLL回路が望まれる。

【課題を解決するための手段】

【0006】

PLL回路は、第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記第3のクロック信号を発振する発振回路とを含み、前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とする。

【発明の効果】

【0007】

本願開示の少なくとも1つの実施例によれば、フィルタ回路は、発振回路中の遅延回路と同一構成であり制御信号の値に応じた信号遅延をもたらす遅延回路を含む。これにより、発振周波数に応じたフィルタ処理が可能となる。また発振ループの遅延回路とフィルタ処理の遅延回路とに同一の回路構成の回路を用いることにより、発振周期の変化量に対するフィルタ処理特性の変化量を、発振周波数の値に関わらず略一定として、安定した制御を実現することができる。またプロセス変動や温度変化などにより発振ループの遅延回路の特性が変動しても、フィルタ処理用の遅延回路の特性も同様に変動するので、種々の条件下で安定した制御を実現することができる。

【図面の簡単な説明】

【0008】

【図1】PLL回路の構成の一例を示す図である。

【図2】電圧制御発振器の構成の一例を示す図である。

【図3】可変フィルタ回路の構成の一例を示す図である。

【図4】PLL回路の構成の別の一例を示す図である。

【図5】V/I変換器の構成の一例を示す図である。

【図6】電流制御発振器の構成の一例を示す図である。

【図7】可変フィルタ回路の構成の一例を示す図である。

【図8】PLL回路の構成の更に別の一例を示す図である。

【図9】電圧変換器の構成の一例を示す図である。

【図10】PLL回路の構成の更に別の一例を示す図である。

【図11】電流変換器の構成の一例を示す図である。

【図12】PLL回路の構成の更に別の一例を示す図である。

【図13】PLL回路の構成の更に別の一例を示す図である。

【図14】図13のPLL回路の構成の変形例を示す図である。

【図15】図13のPLL回路の構成の別の変形例を示す図である。

【図16】位相比較器の回路構成の一例を示す図である。

【図17】図13のPLL回路の構成の更に別の変形例を示す図である。

【図18】ロック検出回路の構成の一例を示す図である。

【図19】図18のロック検出回路の動作を説明するための図である。

【図20】PLL回路を内蔵するシステムの構成の一例を示す図である。

【発明を実施するための形態】

【0009】

以下に、本発明の実施例を添付の図面を用いて詳細に説明する。

【0010】

図1は、PLL回路の構成の一例を示す図である。図1に示すPLL回路は、可変フィルタ回路10、位相比較器11、チャージポンプ12、ループフィルタ13、及び電圧制御発振器(VCO:Voltage Controlled Oscillator)14を含む。可変フィルタ回路10は、基準クロック信号RCLKをフィルタ処理して、フィルタ処理後のクロック信号を生成する。位相比較器11は、フィルタ処理後のクロック信号と出力クロック信号OCLKとの位相比較を行い、位相比較結果を示す信号を生成する。チャージポンプ12は、位相比較器11からの位相比較結果を示す信号に基づいて、位相比較結果に応じた電圧信号を生成する。ループフィルタ13は、チャージポンプ12からの電圧信号をローパスフィルタ処理して実効的に積分処理することにより、不必要な細かい変動を除去し、位相比較結果に応じた制御信号を生成する。電圧制御発振器14は、入力電圧値に応じた発振周波数で発振する発振器であり、少なくとも1つ又は複数の可変遅延回路14−1、14−2、・・・により構成される発振ループ15を有する。電圧制御発振器14は、ループフィルタ13からの制御信号の電圧値に応じた信号遅延をもたらす遅延回路(例えば14−1)を少なくとも含み、この信号遅延に応じて出力クロック信号OCLKを発振する。ここで各可変遅延回路14−1、14−2、・・・は、互いに同一の構成である。例えば、電圧制御発振器14の複数の可変遅延回路の個数が3つであり、発振周波数が100MHzの場合、可変遅延回路の遅延は1/100÷6≒1.6nsとなる。なおここで、各可変遅延回路は入力の論理値に対して出力の論理値を反転させるインバータ形式の回路であるとして、除算の除数を3の2倍の6としている。

【0011】

図1の構成において、可変フィルタ回路10は、前記遅延回路(例えば14−1)と同一構成であり前記制御信号の電圧値に応じた信号遅延をもたらす可変遅延回路16を含む。可変フィルタ回路10は、可変遅延回路16により基準クロック信号RCLKをフィルタ処理することにより、フィルタ処理後のクロック信号を生成する。このように、出力クロック信号OCLKの発振周波数を制御する制御信号の電圧に応じて、可変遅延回路16によりフィルタ処理することにより、発振周波数に応じたフィルタ処理が可能となる。また発振ループの可変遅延回路とフィルタ処理の可変遅延回路とに、同一の回路構成の回路を用いている。これにより、発振周期の変化量に対するフィルタ処理特性の変化量を、発振周波数の値に関わらず略一定として、安定した制御を実現することができる。またプロセス変動や温度変化などにより発振ループの可変遅延回路の特性が変動しても、フィルタ処理用の可変遅延回路の特性も同様に変動するので、種々の条件下で安定した制御を実現することができる。

【0012】

図2は、電圧制御発振器14の構成の一例を示す図である。図2に示す電圧制御発振器14は、PMOSトランジスタ20及び21、NMOSトランジスタ22及び23、及び抵抗24を含む。電圧制御発振器14は更に、PMOSトランジスタ25−1乃至25−3、NMOSトランジスタ26−1乃至26−3、インバータ27−1乃至27−3、及び容量素子28−1乃至28−3を含む。PMOSトランジスタ25−1、NMOSトランジスタ26−1、インバータ27−1、及び容量素子28−1が、第1の可変遅延回路14−1を構成する。PMOSトランジスタ25−2、NMOSトランジスタ26−2、インバータ27−2、及び容量素子28−2が、第2の可変遅延回路14−2を構成する。PMOSトランジスタ25−3、NMOSトランジスタ26−3、インバータ27−3、及び容量素子28−3が、第3の可変遅延回路14−3を構成する。第1乃至第3の可変遅延回路14−1乃至14−3は縦続接続され、第3の可変遅延回路14−3の出力が第1の可変遅延回路14−1の入力に接続されて、発振ループ15を形成している。

【0013】

図1に示すループフィルタ13からの制御信号電圧がNMOSトランジスタ22のゲートに印加される。これにより、NMOSトランジスタ22には制御信号電圧に応じた電流量Idのドレイン電流が流れる。この時、NMOSトランジスタ22に直列に接続されるPMOSトランジスタ20にも同一の電流量Idの電流が流れる。PMOSトランジスタ20と21とはカレントミラー回路を形成しており、PMOSトランジスタ21にも上記と同一の電流量Idの電流が流れる。更に、PMOSトランジスタ21に直列に接続されるNMOSトランジスタ23にも同一の電流量Idの電流が流れる。この電流量Idの電流を流すPMOSトランジスタ20及び21のゲート電圧が、遅延制御信号Pとして、PMOSトランジスタ25−1乃至25−3のゲートに印加される。また、電流量Idの電流を流すNMOSトランジスタ23のゲート電圧が、遅延制御信号Nとして、NMOSトランジスタ26−1乃至26−3のゲートに印加される。従って、図1に示すループフィルタ13からの制御信号電圧に応じて、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値(電流量)が変化する。

【0014】

ループフィルタ13からの制御信号電圧が低くなり、上記抵抗値が増大(電流量が減少)すると、容量素子28−1乃至28−3の充放電速度が低下して信号波形の遷移が緩やかになる。その結果、インバータ27−1乃至27−3の出力信号の遷移タイミングが遅くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が長くなる。このようにして、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値が増大すると、第1乃至第3の可変遅延回路14−1乃至14−3の各々の遅延時間が長くなる。即ち、ループフィルタ13からの制御信号電圧が低くなると、発振ループ15の発振周波数が低くなる。

【0015】

逆にループフィルタ13からの制御信号電圧が高くなり、抵抗値が減少(電流量が増大)すると、容量素子28−1乃至28−3の充放電速度が上昇して信号波形の遷移が急峻になる。その結果、インバータ27−1乃至27−3の出力信号の遷移タイミングが早くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が短くなる。このようにして、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値が減少すると、第1乃至第3の可変遅延回路14−1乃至14−3の各々の遅延時間が短くなる。即ち、ループフィルタ13からの制御信号電圧が高くなると、発振ループ15の発振周波数が高くなる。

【0016】

図3は、可変フィルタ回路10の構成の一例を示す図である。図3に示す可変フィルタ回路10は、PMOSトランジスタ30及び31、NMOSトランジスタ32及び33、及び抵抗34を含む。可変フィルタ回路10は更に、PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38を含む。PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38が、可変遅延回路16(図1参照)を構成する。

【0017】

図1に示すループフィルタ13からの制御信号電圧がNMOSトランジスタ32のゲートに印加される。これにより、NMOSトランジスタ32には制御信号電圧に応じた電流量Idのドレイン電流が流れる。この時、NMOSトランジスタ32に直列に接続されるPMOSトランジスタ30にも同一の電流量Idの電流が流れる。PMOSトランジスタ30と31とはカレントミラー回路を形成しており、PMOSトランジスタ31にも上記と同一の電流量Idの電流が流れる。更に、PMOSトランジスタ31に直列に接続されるNMOSトランジスタ33にも同一の電流量Idの電流が流れる。この電流量Idの電流を流すPMOSトランジスタ30及び31のゲート電圧が、遅延制御信号Pとして、PMOSトランジスタ35のゲートに印加される。また、電流量Idの電流を流すNMOSトランジスタ33のゲート電圧が、遅延制御信号Nとして、NMOSトランジスタ36のゲートに印加される。従って、図1に示すループフィルタ13からの制御信号電圧に応じて、PMOSトランジスタ35及びNMOSトランジスタ36の抵抗値が変化する。

【0018】

ループフィルタ13からの制御信号電圧が低くなり、上記抵抗値が増大(電流量が減少)すると、容量素子38の充放電速度が低下して信号波形の遷移が緩やかになる。その結果、インバータ37の出力信号の遷移タイミングが遅くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が長くなる。またその際、フィルタ入力信号にノイズが含まれる場合に、フィルタ出力信号にノイズが現れるために最低限必要なノイズの幅及び高さが大きくなる。即ち、ループフィルタ13からの制御信号電圧が低くなると、より大きなノイズを除去することができるようになる。

【0019】

逆にループフィルタ13からの制御信号電圧が高くなり、抵抗値が減少(電流量が増大)すると、容量素子38の充放電速度が上昇して信号波形の遷移が急峻になる。その結果、インバータ37の出力信号の遷移タイミングが早くなる。即ち、入力信号の遷移に応答して出力信号が遷移する際の入力信号の遷移開始から出力信号が遷移するまでの時間が短くなる。またその際、フィルタ入力信号にノイズが含まれる場合に、フィルタ出力信号にノイズが現れるために最低限必要なノイズの幅及び高さが小さくなる。即ち、ループフィルタ13からの制御信号電圧が高くなると、除去可能なノイズがより小さくなる。

【0020】

図4は、PLL回路の構成の別の一例を示す図である。図4において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。図4に示すPLL回路は、図1に示すPLL回路と比較して、V/I変換器17が設けられ、発振周波数を電圧制御ではなく電流制御する点が異なる。またこれに伴い、電圧制御発振器14の代りに電流制御発振器(ICO)14Aが設けられ、また可変フィルタ回路10の代りに可変フィルタ回路10Aが設けられる。電圧制御の代りに電流制御する点を除けば、図4のPLL回路の動作は図1のPLL回路の動作と同一である。

【0021】

V/I変換器17は、ループフィルタ13からの制御信号の電圧値を電流値に変換する。電流制御発振器14Aは、入力電流値に応じた発振周波数で発振する発振器であり、少なくとも1つ又は複数の可変遅延回路14A−1、14A−2、・・・により構成される発振ループ15Aを有する。電流制御発振器14Aは、V/I変換器17からの制御信号の電流値に応じた信号遅延をもたらす遅延回路(例えば14−1)を少なくとも含み、この信号遅延に応じて出力クロック信号OCLKを発振する。可変フィルタ回路10Aは、前記遅延回路(例えば14−1)と同一構成であり前記制御信号の電流値に応じた信号遅延をもたらす可変遅延回路16Aを含む。可変フィルタ回路10Aは、可変遅延回路16Aにより基準クロック信号RCLKをフィルタ処理することにより、フィルタ処理後のクロック信号を生成する。

【0022】

図5は、V/I変換器17の構成の一例を示す図である。図5に示すV/I変換器17は、PMOSトランジスタ40乃至42、NMOSトランジスタ43、及び抵抗44を含む。図4に示すループフィルタ13からの制御信号電圧がNMOSトランジスタ43のゲートに印加される。これにより、NMOSトランジスタ43には制御信号電圧に応じた電流量Idのドレイン電流が流れる。この時、NMOSトランジスタ43に直列に接続されるPMOSトランジスタ40にも同一の電流量Idの電流が流れる。PMOSトランジスタ40,41,42はカレントミラー回路を形成しており、PMOSトランジスタ41及び42にも上記と同一の電流量Idの電流が流れる。これらPMOSトランジスタ41及び42に流れる電流のうち、一方が電流制御発振器14Aに供給され、他方が可変フィルタ回路10Aに供給される。

【0023】

図6は、電流制御発振器14Aの構成の一例を示す図である。図6において、図2と同一の構成要素は同一の番号で参照し、その説明は省略する。図6に示す電流制御発振器14Aは、PMOSトランジスタ50、及びNMOSトランジスタ51及び52を含む。電流制御発振器14Aは更に、PMOSトランジスタ25−1乃至25−3、NMOSトランジスタ26−1乃至26−3、インバータ27−1乃至27−3、及び容量素子28−1乃至28−3を含む。第1乃至第3の可変遅延回路14A−1乃至14A−3は縦続接続され、第3の可変遅延回路14A−3の出力が第1の可変遅延回路14A−1の入力に接続されて、発振ループ15Aを形成している。

【0024】

図4に示すV/I変換器17からの制御信号電流がNMOSトランジスタ51に流される。NMOSトランジスタ51と52とはカレントミラー回路を形成しており、NMOSトランジスタ52にも上記と同一の電流量の電流が流れる。更に、NMOSトランジスタ52に直列に接続されるPMOSトランジスタ50にも同一の電流量の電流が流れる。この電流量の電流を流すPMOSトランジスタ50のゲート電圧が、PMOSトランジスタ25−1乃至25−3のゲートに印加される。また上記の電流量の電流を流すNMOSトランジスタ52のゲート電圧が、NMOSトランジスタ26−1乃至26−3のゲートに印加される。従って、図4に示すV/I変換器17からの制御信号電流に応じて、PMOSトランジスタ25−1乃至25−3及びNMOSトランジスタ26−1乃至26−3の抵抗値(電流量)が変化し、発振ループ15Aの発振周波数が変化する。

【0025】

図7は、可変フィルタ回路10Aの構成の一例を示す図である。図7において、図3と同一の構成要素は同一の番号で参照し、その説明は省略する。図7に示す可変フィルタ回路10Aは、PMOSトランジスタ60、及びNMOSトランジスタ61及び62を含む。可変フィルタ回路10Aは更に、PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38を含む。PMOSトランジスタ35、NMOSトランジスタ36、インバータ37、及び容量素子38が、可変遅延回路16A(図4参照)を構成する。

【0026】

図4に示すV/I変換器17からの制御信号電流がNMOSトランジスタ61に流される。NMOSトランジスタ61と62とはカレントミラー回路を形成しており、NMOSトランジスタ62にも上記と同一の電流量の電流が流れる。更に、NMOSトランジスタ62に直列に接続されるPMOSトランジスタ60にも同一の電流量の電流が流れる。この電流量の電流を流すPMOSトランジスタ60のゲート電圧が、PMOSトランジスタ35のゲートに印加される。また上記の電流量の電流を流すNMOSトランジスタ62のゲート電圧が、NMOSトランジスタ36のゲートに印加される。従って、図4に示すV/I変換器17からの制御信号電流に応じて、可変フィルタ回路10Aにより除去可能なノイズの大きさが変化する。

【0027】

図8は、PLL回路の構成の更に別の一例を示す図である。図8において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。図8に示すPLL回路は、図1に示すPLL回路と比較して、制御信号の電圧値を変換する電圧変換器18が設けられている点が異なる。電圧変換器18により電圧値を変換した後の制御信号の電圧値に応じて、可変フィルタ回路10の可変遅延回路16が動作する。電圧変換器18は、CPU等の外部からのフィルタ特性制御信号に応じて、変換前の電圧値と変換後の電圧値との関係を調整する。

【0028】

図9は、電圧変換器18の構成の一例を示す図である。図9に示す電圧変換器18は、オペアンプ70、複数の直列接続された抵抗素子71、及び複数のスイッチ回路72を含む。オペアンプ70は、電圧変換器18への入力電圧を非反転入力端に受け取る。オペアンプ70の出力は、複数の抵抗素子71の列の一端に接続される。複数の抵抗素子71の列の他端はグランドに接続される。複数の抵抗素子71の列で分圧された中間点の電圧が、オペアンプ70の反転入力端にフィードバックされる。複数の抵抗素子71の列により分圧され生成された複数の電圧は、複数のスイッチ回路72のうちの導通した1つにより選択され、電圧変換器18の出力電圧となる。複数のスイッチ回路72のうちの何れを導通させるかは、外部から供給される出力電圧選択信号(フィルタ特性制御信号)により決定される。これにより、出力電圧(ループフィルタ13の出力電圧)よりも高い電圧或いは低い電圧を自由に生成して、可変遅延回路16に供給することができる。

【0029】

図10は、PLL回路の構成の更に別の一例を示す図である。図10において、図4と同一の構成要素は同一の番号で参照し、その説明は省略する。図10に示すPLL回路は、図4に示すPLL回路と比較して、制御信号の電流値を変換する電流変換器18Aが設けられている点が異なる。電流変換器18Aにより電流値を変換した後の制御信号の電流値に応じて、可変フィルタ回路10Aの可変遅延回路16Aが動作する。電流変換器18Aは、CPU等の外部からのフィルタ特性制御信号に応じて、変換前の電流値と変換後の電流値との関係を調整する。

【0030】

図11は、電流変換器18Aの構成の一例を示す図である。図11に示す電流変換器18Aは、PMOSトランジスタ80、NMOSトランジスタ81及び82、複数のPMOSトランジスタ83、及び複数のスイッチ回路84を含む。図10に示すV/I変換器17からの制御信号電流がNMOSトランジスタ81に流される。NMOSトランジスタ81と82とはカレントミラー回路を形成しており、NMOSトランジスタ82にも上記と同一の電流量の電流が流れる。更に、NMOSトランジスタ82に直列に接続されるPMOSトランジスタ80にも同一の電流量の電流が流れる。この電流量の電流を流すPMOSトランジスタ80のゲート電圧が、複数のPMOSトランジスタ83のゲートに印加されており、カレントミラー回路を構成している。複数のPMOSトランジスタ83により生成される複数の電流は、複数のスイッチ回路84のうちの導通した1つ又は複数のスイッチ回路を介して、電流変換器18の出力電流として送出される。複数のスイッチ回路72のうちの幾つを導通させるかは、外部から供給される出力電流選択信号(フィルタ特性制御信号)により決定される。これにより、出力電流(V/I変換器17の出力電流)よりも大きい電流を自由に生成して、可変遅延回路16Aに供給することができる。なおNMOSトランジスタ81と82とのゲート幅を異ならせ、NMOSトランジスタ82に流れるドレイン電流をNMOSトランジスタ81に流れるドレイン電流の1/n(n:自然数)としてもよい。この場合、出力電流(V/I変換器17の出力電流)よりも小さい電流或いは大きい電流を自由に生成して、可変遅延回路16Aに供給することができる。

【0031】

図12は、PLL回路の構成の更に別の一例を示す図である。図12において、図8と同一の構成要素は同一の番号で参照し、その説明は省略する。図12に示すPLL回路は、図8に示すPLL回路と比較して、N分周器90、M分周器91、及びデコーダ92が追加で設けられている点が異なる。N分周器90は、分周設定信号に応じた分周率Nにより、可変フィルタ回路10の出力するフィルタ処理後のクロック信号を分周する。M分周器91は、分周設定信号に応じた分周率Mにより、電圧制御発振器14の出力する出力クロック信号OCLKを分周する。これら分周器90及び91による分周後のクロック信号を位相比較対象の信号として位相比較器11に入力する。デコーダ92は、N分周を指定する分周設定信号とM分周を指定する分周設定信号とをデコードして、フィルタ特性制御信号を生成する。電圧変換器18は、このフィルタ特性制御信号に応じて、変換前の電圧値と変換後の電圧値との関係を調整する。なお図12の構成では、N分周器90とM分周器91との2つの分周器を設けているが、何れか一方のみを設けた構成としてもよい。

【0032】

電圧変換器18が設けられていない図1の構成において、適切なノイズ除去が実現されているとする。そのままの条件で、図8に示すようにN分周器90とM分周器91との2つの分周器を設けた場合を考える。この場合、位相同期がとれた状態では、基準クロック信号RCLKのN分の1が出力クロック信号OCLKのM分の1に等しくなるので、基準クロック信号RCLKの周波数は出力周波数のN/Mとなる。分周器が設けられていない状態(即ちN=M=1)において可変遅延回路16の制御電圧が適正値であったのだから、図8に示す構成の場合、電圧変換器18から可変遅延回路16に印加される制御電圧を、上記適正値の例えばN/M倍とすればよい。即ち、電圧変換器18により入力電圧のN/M倍の電圧を生成するような信号を、デコーダ92により生成すればよい。

【0033】

図13は、PLL回路の構成の更に別の一例を示す図である。図13において、図1と同一の構成要素は同一の番号で参照し、その説明は省略する。図13に示すPLL回路は、図1に示すPLL回路と比較して、スイッチ回路19が設けられている点が異なる。スイッチ回路19は、図示下側のノードに接続されると、基準クロック信号RCLKを可変フィルタ回路10を介することなく位相比較対象の信号として位相比較器11に供給する第1の経路を選択する。またスイッチ回路19は、図示上側のノードに接続されると、基準クロック信号RCLKから可変フィルタ回路10を介して得られるフィルタ処理後のクロック信号を、位相比較対象の信号として位相比較器11に供給する第2の経路を選択する。スイッチ回路19は、上記第1の経路と第2の経路との何れか一方を選択して切り替え可能な構成となっている。

【0034】

スイッチ回路19は、CPU等の外部からのフィルタバイパス制御信号に応じて、切り替え動作を実行してよい。例えば、PLL回路が位相同期を確立するまでの初期動作時(ロック前)には基準クロック信号RCLKを直接に位相比較器11に供給し、PLL回路が位相同期を確立した後(ロック後)においてはフィルタ処理後のクロック信号を位相比較器11に供給してよい。仮に位相をロックするための初期動作時において、位相同期確立に必要なクロックのパルス信号までも可変フィルタ回路10を通過できないような初期状態に可変フィルタ回路10が設定されているとすると、PLL回路が全く所望の動作を実行できないことになる。上記のように、位相をロックするための初期動作時において、基準クロック信号RCLKを直接に位相比較器11に供給するようにすれば、可変フィルタ回路10の初期状態に関わらず、確実に位相同期を確立することができる。また位相同期の確立後は、フィルタ処理後のクロック信号を位相比較器11に供給することで、確実にノイズの影響を除去することができる。

【0035】

図14は、図13のPLL回路の構成の変形例を示す図である。図14において、図13と同一の構成要素は同一の番号で参照し、その説明は省略する。図14に示すPLL回路は、図13に示すPLL回路と比較して、カウンタ100が設けられている点が異なる。カウンタ100は、基準クロック信号RCLKのパルス数を計数し、計数値が所定値になると出力をアサートする。カウンタ100の出力のアサートに応じてスイッチ回路19が前記第1の経路から前記第2の経路に切り替える。上記所定値として、位相同期を確立させる動作(位相ロック動作)が終了するのに必要なパルス数を設定すればよい。

【0036】

図15は、図13のPLL回路の構成の別の変形例を示す図である。図15において、図13と同一の構成要素は同一の番号で参照し、その説明は省略する。図15に示すPLL回路は、図13に示すPLL回路と比較して、ロック検出回路101が設けられている点が異なる。ロック検出回路101は、位相比較器11の出力する制御信号に基づいて位相が同期した状態を検出すると出力をアサートする。このロック検出回路101の出力のアサートに応じて、スイッチ回路19が、前記第1の経路から前記第2の経路に切り替える。

【0037】

図16は、位相比較器11の回路構成の一例を示す図である。図16の位相比較器11は、NAND回路111乃至118、インバータ119乃至121、及びAND回路122を含む。位相比較器11は、NAND回路118の出力である周波数アップ信号出力がHIGHであり、AND回路122の出力である周波数ダウン信号出力がLOWである状態で、入力の変化を待ち受ける。周波数アップ信号出力のHIGH及び周波数ダウン信号出力のLOWは、それぞれの信号のネゲート状態である。周波数アップ信号出力は次段のチャージポンプ12のPMOSトランジスタのゲートに印加され、周波数ダウン信号出力は次段のチャージポンプ12のNMOSトランジスタのゲートに印加される。これらのPMOSトランジスタ及びNMOSトランジスタにより、チャージポンプ12の容量素子への充放電が行なわれる。

【0038】

上記の待ち受け状態で、例えば基準クロック信号が比較クロック信号よりも先にHIGHからLOWに変化すると、NAND回路111の出力がHIGHに変化し、NAND回路118の周波数アップ信号出力がLOWに変化する。即ち周波数アップ信号出力がアサート状態(LOW)となる。その後、比較クロック信号がHIGHからLOWに変化すると、NAND回路116の出力がHIGHに変化し、AND回路122の周波数ダウン信号出力がHIGHに変化する。即ち周波数ダウン信号出力がアサート状態(HIGH)となる。またNAND回路116の出力のHIGHへの変化により、NAND回路117の入力が全てHIGHとなり、NAND回路117の出力がHIGHからLOWへと変化する。これにより、周波数アップ信号出力及び周波数ダウン信号出力がそれぞれHIGH及びLOWへと同時に変化すると共に、位相比較器11がリセットされる。その後、基準クロック信号と比較クロック信号とがHIGHに戻ると、位相比較器11は上記の待ち受け状態に戻る。

【0039】

また上記の待ち受け状態で、基準クロック信号と比較クロック信号とが同時にHIGHからLOWに変化すると、周波数アップ信号出力のLOWへの変化及び周波数ダウン信号出力のHIGHへの変化が同時に起こる。更に、その直後に、位相比較器11のリセットとともに周波数アップ信号出力のHIGHへの変化及び周波数ダウン信号出力のLOWへの変化が同時に起こる。

【0040】

このように、クロックの位相同期がとれている状態では、周波数アップ信号出力のアサート状態と周波数ダウン信号出力のアサート状態とが同一期間に発生する。またクロック間に位相差がある状態では、位相差に等しい期間だけ一方の信号出力のアサート状態が他方の信号のアサート状態よりも長く発生する。このような位相比較結果信号を出力する位相比較器11に対しては、図15に示すロック検出回路101にはXOR回路(排他的論理和回路)を用いることができる。クロックの位相同期がとれている状態では、周波数アップ信号出力の論理値と周波数ダウン信号出力の論理値とは常に逆になっているので、XOR回路の出力はHIGHに固定される。またクロック間に位相差がある状態では、位相差に等しい期間だけ両方の信号出力が同一論理値となるので、XOR回路の出力は位相差に等しい期間LOWとなる。ロック検出回路101は、XOR回路の出力がHIGH固定であることを検出すると、スイッチ回路19を前記第1の経路から前記第2の経路に切り替えてよい。

【0041】

図17は、図13のPLL回路の構成の更に別の変形例を示す図である。図17において、図13と同一の構成要素は同一の番号で参照し、その説明は省略する。図17に示すPLL回路は、図13に示すPLL回路と比較して、ロック検出回路102が設けられている点が異なる。ロック検出回路102は、位相比較器11の位相比較結果に応じてループフィルタ13が出力する制御信号に基づいて、位相が同期した状態を検出すると出力をアサートする。このロック検出回路102の出力のアサートに応じて、スイッチ回路19が、前記第1の経路から前記第2の経路に切り替える。

【0042】

図18は、ロック検出回路102の構成の一例を示す図である。図18に示すロック検出回路102は、容量素子131、抵抗素子132、及びコンパレータ133を含む。容量素子131と抵抗素子132とが微分回路を構成し、入力されるVCO制御電圧波形の微分に相当する電圧を生成する。コンパレータ133は、微分電圧と基準電圧とを比較して、微分電圧が基準電圧よりも低くなると出力をHIGHにする。

【0043】

図19は、図18のロック検出回路102の動作を説明するための図である。図19において、ループフィルタ13から電圧制御発振器14に印加されるVCO制御電圧は、例えば電圧波形140のような波形となる。即ち、PLL回路の動作が開始すると、フィードバック制御に基づいて、位相比較器11による位相比較結果に応じてVCO制御電圧が調整される。クロック間の位相が同期するVCO制御電圧が得られると(即ちロック状態となると)、その後VCO制御電圧は略一定値で推移する。

【0044】

電圧波形141は、電圧波形140を微分した波形であり、図18に示すコンパレータ133の反転入力端に入力される電圧波形である。また電圧波形142は、基準電圧であり、コンパレータ133の非反転入力端に入力される電圧波形である。コンパレータ133は、微分電圧と基準電圧とを比較して、その大小関係に応じて電圧波形143として示す出力電圧を生成する。コンパレータ133の出力電圧は、PLL回路の動作開始タイミングT0から暫くの期間LOWとなり、位相同期が確立されたタイミングT1においてHIGHとなる。ロック検出回路102は、コンパレータ133の出力によりスイッチ回路19を制御し、コンパレータ133の出力がHIGHになるとスイッチ回路19を前記第1の経路から前記第2の経路に切り替えてよい。

【0045】

図20は、PLL回路を内蔵するシステムの構成の一例を示す図である。例えば半導体装置として単一のチップとして構成されるシステム150は、CPU151、フラッシュメモリ152、RAM153、クロック制御回路154、各種リソース156、及びバス157を含む。CPU151、フラッシュメモリ152、RAM153、クロック制御回路154、及び各種リソース156は、バス157を介して、互いに信号をやり取りする。クロック制御回路154は、前述の例えば図8又は図9に示すPLL回路155を含み、基準クロック信号に応じて出力クロック信号を生成する。クロック制御回路154が生成した出力クロック信号は、システム150内の各ユニットに供給されて、システムのクロック同期した動作を実現する。PLL回路155は、CPU151からの信号に応じて制御信号の値を変換する変換回路18又は18A(図8及び図9参照)を含む。

【0046】

このクロック制御回路154のPLL回路155は、CPU151からの分周設定信号に応じた分周率により基準クロック信号及び出力クロック信号の少なくとも一方を分周する分周器(例えば図12のN分周器90又はM分周器91)を更に含んでもよい。この場合、変換回路18は分周設定信号に応じて制御信号の値を変換する。またPLL回路155は、前述のスイッチ回路19(図13,14,15,17参照)を含んでもよい。

【0047】

以上、本発明を実施例に基づいて説明したが、本発明は上記実施例に限定されるものではなく、特許請求の範囲に記載の範囲内で様々な変形が可能である。

【0048】

なお本願は以下の内容を含むものである。

(付記1)

第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、

前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記第3のクロック信号を発振する発振回路と

を含み、

前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とするPLL回路。

(付記2)

前記制御信号の値を変換する変換回路を更に含み、前記値を変換した後の前記制御信号の値に応じて前記第2の遅延回路は動作することを特徴とする付記1記載のPLL回路。

(付記3)

分周設定信号に応じた分周率により前記第2のクロック信号及び前記第3のクロック信号の少なくとも一方を分周する分周器を更に含み、前記分周器による分周後のクロック信号を位相比較対象の信号として前記位相比較回路に入力し、前記変換回路は前記分周設定信号に応じて前記制御信号の値を変換することを特徴とする付記2記載のPLL回路。

(付記4)

前記第1のクロック信号を前記フィルタ回路を介することなく位相比較対象の信号として前記位相比較回路に供給する第1の経路と、前記第1のクロック信号から前記フィルタ回路を介して得られる前記第2のクロック信号を位相比較対象の信号として前記位相比較回路に供給する第2の経路と、を選択して切り替え可能なスイッチ回路を更に含むことを特徴とする付記1乃至3何れか一項記載のPLL回路。

(付記5)

前記第1のクロック信号のパルス数を計数し、計数値が所定値になると出力をアサートするカウンタを更に含み、前記カウンタの出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記4記載のPLL回路。

(付記6)

前記位相比較回路の出力する前記制御信号に基づいて前記第2のクロック信号と前記第3のクロック信号との位相が同期した状態を検出すると出力をアサートする検出回路を更に含み、前記検出回路の出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記4記載のPLL回路。

(付記7)

基準クロック信号に応じて出力クロック信号を生成するクロック制御回路と、

処理ユニットと

を含み、前記クロック制御回路は、

前記基準クロック信号をフィルタ処理して第1のクロック信号を生成するフィルタ回路と、

前記第1のクロック信号と前記出力クロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記出力クロック信号を発振する発振回路と、

前記処理ユニットからの信号に応じて前記制御信号の値を変換する変換回路と

を含み、

前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記値を変換した後の前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記基準クロック信号をフィルタ処理して前記第1のクロック信号を生成することを特徴とするシステム。

(付記8)

前記クロック制御回路は、前記処理ユニットからの分周設定信号に応じた分周率により前記第1のクロック信号及び前記出力クロック信号の少なくとも一方を分周する分周器を更に含み、前記分周器による分周後のクロック信号を位相比較対象の信号として前記位相比較回路に入力し、前記変換回路は前記分周設定信号に応じて前記制御信号の値を変換することを特徴とする付記7記載のシステム。

(付記9)

前記クロック制御回路は、前記基準クロック信号を前記フィルタ回路を介することなく位相比較対象の信号として前記位相比較回路に供給する第1の経路と、前記第1のクロック信号から前記フィルタ回路を介して得られる前記第2のクロック信号を位相比較対象の信号として前記位相比較回路に供給する第2の経路と、を選択して切り替え可能なスイッチ回路を更に含むことを特徴とする付記7又は8記載のシステム。

(付記10)

前記クロック制御回路は、前記基準クロック信号のパルス数を計数し、計数値が所定値になると出力をアサートするカウンタを更に含み、前記カウンタの出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記9記載のシステム。

(付記11)

前記位相比較回路の出力する前記制御信号に基づいて前記第1のクロック信号と前記出力クロック信号との位相が同期した状態を検出すると出力をアサートする検出回路を更に含み、前記検出回路の出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする付記9記載のシステム。

(付記12)

第1のクロック信号をフィルタ処理して第2のクロック信号を生成し、

前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成し、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を利用して、前記信号遅延に応じた前記第3のクロック信号を発振する

各段階を含み、

前記フィルタ処理は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を利用し、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とするPLL回路のノイズ除去方法。

【符号の説明】

【0049】

10 可変フィルタ回路

11 位相比較器

12 チャージポンプ

13 ループフィルタ

14 電圧制御発振器

【特許請求の範囲】

【請求項1】

第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、

前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記第3のクロック信号を発振する発振回路と

を含み、

前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とするPLL回路。

【請求項2】

前記制御信号の値を変換する変換回路を更に含み、前記値を変換した後の前記制御信号の値に応じて前記第2の遅延回路は動作することを特徴とする請求項1記載のPLL回路。

【請求項3】

分周設定信号に応じた分周率により前記第2のクロック信号及び前記第3のクロック信号の少なくとも一方を分周する分周器を更に含み、前記分周器による分周後のクロック信号を位相比較対象の信号として前記位相比較回路に入力し、前記変換回路は前記分周設定信号に応じて前記制御信号の値を変換することを特徴とする請求項2記載のPLL回路。

【請求項4】

前記第1のクロック信号を前記フィルタ回路を介することなく位相比較対象の信号として前記位相比較回路に供給する第1の経路と、前記第1のクロック信号から前記フィルタ回路を介して得られる前記第2のクロック信号を位相比較対象の信号として前記位相比較回路に供給する第2の経路と、を選択して切り替え可能なスイッチ回路を更に含むことを特徴とする請求項1乃至3何れか一項記載のPLL回路。

【請求項5】

前記位相比較回路の出力する前記制御信号に基づいて前記第2のクロック信号と前記第3のクロック信号との位相が同期した状態を検出すると出力をアサートする検出回路を更に含み、前記検出回路の出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする請求項4記載のPLL回路。

【請求項1】

第1のクロック信号をフィルタ処理して第2のクロック信号を生成するフィルタ回路と、

前記第2のクロック信号と第3のクロック信号との位相比較結果に応じた制御信号を生成する位相比較回路と、

前記制御信号の値に応じた信号遅延をもたらす第1の遅延回路を少なくとも含み、前記信号遅延に応じて前記第3のクロック信号を発振する発振回路と

を含み、

前記フィルタ回路は、前記第1の遅延回路と同一構成であり前記制御信号の値に応じた信号遅延をもたらす第2の遅延回路を含み、前記第2の遅延回路により前記第1のクロック信号をフィルタ処理して前記第2のクロック信号を生成することを特徴とするPLL回路。

【請求項2】

前記制御信号の値を変換する変換回路を更に含み、前記値を変換した後の前記制御信号の値に応じて前記第2の遅延回路は動作することを特徴とする請求項1記載のPLL回路。

【請求項3】

分周設定信号に応じた分周率により前記第2のクロック信号及び前記第3のクロック信号の少なくとも一方を分周する分周器を更に含み、前記分周器による分周後のクロック信号を位相比較対象の信号として前記位相比較回路に入力し、前記変換回路は前記分周設定信号に応じて前記制御信号の値を変換することを特徴とする請求項2記載のPLL回路。

【請求項4】

前記第1のクロック信号を前記フィルタ回路を介することなく位相比較対象の信号として前記位相比較回路に供給する第1の経路と、前記第1のクロック信号から前記フィルタ回路を介して得られる前記第2のクロック信号を位相比較対象の信号として前記位相比較回路に供給する第2の経路と、を選択して切り替え可能なスイッチ回路を更に含むことを特徴とする請求項1乃至3何れか一項記載のPLL回路。

【請求項5】

前記位相比較回路の出力する前記制御信号に基づいて前記第2のクロック信号と前記第3のクロック信号との位相が同期した状態を検出すると出力をアサートする検出回路を更に含み、前記検出回路の出力のアサートに応じて前記スイッチ回路が前記第1の経路から前記第2の経路に切り替えることを特徴とする請求項4記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2011−182178(P2011−182178A)

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願番号】特願2010−44211(P2010−44211)

【出願日】平成22年3月1日(2010.3.1)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成23年9月15日(2011.9.15)

【国際特許分類】

【出願日】平成22年3月1日(2010.3.1)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]