PLL回路

【課題】サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

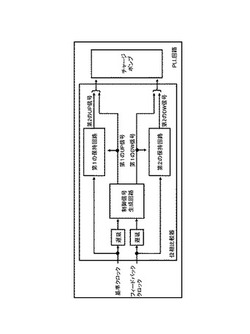

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

【解決手段】図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL回路(位相同期回路)に関する。特に、位相比較器を備えるPLL回路に関する。

【背景技術】

【0002】

PLL回路が様々な電子機器の回路に用いられている。図2は、PLL回路1の内部構成の一例を示す図である。図2に示すPLL回路1は、位相比較器(PFD)10と、チャージポンプ(CP)20と、ループフィルタ(LP)30と、電圧制御発振器(VCO)40と、分周回路50から構成されている。PLL回路1では、位相比較器10において基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差を検出し、チャージポンプ20により昇圧した後にループフィルタ30によりDC電圧に変換する。

【0003】

図3は、位相比較器10の内部構成の一例を示す図である。位相比較器10は、フリップフロップFF01及びFF02と、否定論理積回路NAND01から構成されている。位相比較器10では、基準クロックREF_CLKとフィードバッククロックFB_CLKを比較することで、チャージポンプ20に対する制御信号(UP信号及びDW信号)を生成する。電圧制御発振器40では、DC電圧に比例した周波数の出力を行なう。電圧制御発振器40の出力は、分周回路50により分周されてフィードバッククロックFB_CLKとして使用される。

【0004】

ここで、特許文献1において、電圧制御発振器の出力周波数(フィードバッククロック)と基準クロックとの間の位相差を検出し、位相差が360度以上の場合に誤差信号を出力する位相周波数検出器(PFD)を備えるPLL回路が開示されている。特許文献1で開示された技術では、誤差信号に基づいて電圧制御発振器のフリーランニング周波数を調整し、PLL回路の周波数可変範囲を維持している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特表2006−518151号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

なお、上記先行技術文献の各開示を、本書に引用をもって繰り込むものとする。以下の分析は、本発明の観点からなされたものである。

【0007】

図2に示すPLL回路1では、ロックを開始(引き込みを開始)する際にサイクルスリップが生じるという問題がある。PLL回路1の周波数可変範囲が広い場合には、位相比較器10における位相差が±360度を越えることが考えられる。位相差が±360度を越えた場合に、基準クロックREF_CLKとフィードバッククロックFB_CLKの周波数が一致していないにも関わらず、位相が一致したと判断されてしまうため、PLL回路1のロックが遅れてしまう。これがサイクルスリップである。

【0008】

図4は、PLL回路1の引き込み過程のシミュレーション結果の一例を示す図である。図4では、PLL回路1の出力とチャージポンプ20の出力電圧Vcntを示す。Vcntが一定値になるとPLL回路1はロック状態にあるといえる。図4から、時刻t1に引き込みを開始して、時刻t2でロックするまでの間にVcntが上下に大きく変動(ギザギザ部分)しているのが分かる。この大きく変動している期間にサイクルスリップが発生しており、PLL回路1のロックが遅れる要因となる。

【0009】

上述のように、PLL回路は様々な電子機器において使用されており、特に近年では、SerDes(Serializer/Deserializer)マクロにおけるクロック生成モジュールとして使用されることが多い。図5は、SerDesマクロの内部構成の一例を示す図である。SerDesマクロにおいては、PLL回路から、データの送受信を行なうTx部及びRx部に対して基準クロックを供給する。SerDesマクロは、SATA(Serial ATA)、PCIe(PCI express)、USB(Universal Serial Bus)3.0、HDMI(High−Definition Multimedia Interface)等のバス規格を実現する製品に使用される。

【0010】

これらのバス規格の中でSATA規格に対応したSerDesマクロには、Partialモードと呼ばれるPLL回路をオフ(非活性)にするモードが存在する。Partialモードに遷移させることによって、SerDesマクロでの消費電力を低減する。一方、PartialモードからActiveモード(PLL回路を活性化)に遷移する際にSerDesマクロ全体での復帰時間に関する仕様が定められている。この復帰時間は非常に短く、PLL回路自体も高速でロックを行なわないとSerDesマクロに求められる仕様を満足することができない。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【課題を解決するための手段】

【0011】

本発明の一視点によれば、位相比較器と、前記位相比較器と接続されるチャージポンプと、を備えるPLL回路であって、前記位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、前記チャージポンプの出力電圧を上昇させる第1のUP信号及び前記チャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、前記基準クロックに同期させ、前記第1のUP信号に基づき前記チャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、前記フィードバッククロックに同期させ、前記第1のDW信号に基づき前記チャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含むPLL回路が提供される。

【発明の効果】

【0012】

本発明の一視点によれば、サイクルスリップを低減し、高速にロックを行なうPLL回路が提供される。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態の概要を説明するための図である。

【図2】PLL回路の内部構成の一例を示す図である。

【図3】図2に示す位相比較器の内部構成の一例を示す図である。

【図4】図2に示すPLL回路の引き込み過程のシミュレーション結果の一例を示す図である。

【図5】SerDesマクロの内部構成の一例を示す図である。

【図6】本発明の第1の実施形態に係るPLL回路の内部構成の一例を示す図である。

【図7】図6に示す位相比較器の内部構成の一例を示す図である。

【図8】図3に示す位相比較器の入出力波形の一例を示すタイミングチャートである。

【図9】図7に示す位相比較器の入出力波形の一例を示すタイミングチャートである。

【図10】PLL回路がロックする過程をシミュレーションした結果の一例である。

【図11】図6に示す位相比較器の別の内部構成の一例を示す図である。

【図12】第2の実施形態に係る位相比較器の内部構成の一例を示す図である。

【図13】位相比較器のシミュレーション結果の一例を示す図である。

【図14】第3の実施形態に係るPLL回路の内部構成の一例を示す図である。

【図15】図14に示す位相比較器の内部構成の一例を示す図である。

【図16】図15に示す位相比較器の入出力波形の一例を示すタイミングチャートである。

【図17】第4の実施形態に係る位相比較器の内部構成の一例を示す図である。

【図18】位相比較器のシミュレーション結果の一例を示す図である。

【図19】ループフィルタの内部構成の一例を示す図である。

【発明を実施するための形態】

【0014】

初めに、図1を用いて実施形態の概要について説明する。なお、この概要に付記した図面参照符号は、理解を助けるための一例として各要素に便宜上付記したものであり、本発明を図示の態様に限定することを意図するものではない。

【0015】

上述のように、サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。PLL回路を搭載する回路の仕様によっては、PLL回路が引き込みを完了するまでに許容される時間は極めて短い場合も多い。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【0016】

そこで、図1に示すPLL回路を提供する。図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

【0017】

フィードバッククロックの論理レベルの変化が基準クロックの論理レベルの変化よりも遅れることによって、制御信号生成回路が出力する第1のUP信号又は第2のDW信号にサイクルスリップが発生する場合がある。制御信号生成回路は基準クロックとフィードバッククロックを遅延させたクロックによって動作しているが、第1の保持回路及び第2の保持回路は遅延させていない基準クロック及びフィードバッククロックで動作している。そのため、第1のUP信号又は第1のDW信号にサイクルスリップが発生したとしても、サイクルスリップが発生する前の第1のUP信号又は第1のDW信号を第1の保持回路又は第2の保持回路で基準クロック又はフィードバッククロックに同期させて出力可能である。すると、第1のUP信号又は第1のDW信号が、サイクルスリップの発生によりサイクルスリップ発生前の論理レベルから反転してしまったとしても、第2のUP信号又は第2のDW信号はサイクルスリップ発生前の論理レベルを維持できる。その結果、第1のUP信号又は第2のUP信号(第1のDW信号又は第2のDW信号)で、チャージポンプを動作させることでサイクルスリップが低減し、PLL回路のロック時間が短縮できる。

【0018】

[第1の実施形態]

次に、本発明の第1の実施形態について、図面を用いてより詳細に説明する。図6に本実施形態に係るPLL回路2の内部構成の一例を示す。図6において、図2と同一の構成要素には同一の符号を付し、その説明を省略する。図2に示すPLL回路1とPLL回路2の相違点は、位相比較器10に代えて位相比較器11を使用することと、位相差判定ブロック60及びカウンタ70を追加する点である。位相差判定ブロック60では、UP信号及びDW信号により基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差を判定する。その際に、位相差がある一定値より小さい値となると判定信号LDRTを出力する。カウンタ70では、判定信号LDRTが一定時間変動しないことを確認するとPLL回路1がロック状態に遷移したと判断し、ロック信号を出力する。

【0019】

図7は、位相比較器11の内部構成の一例を示す図である。位相比較器11は、フリップフロップFF03乃至FF06と、否定論理積回路NAND02と、論理和回路OR01及びOR02と、遅延素子D01及びD02から構成されている。フリップフロップFF03及びFF04と、否定論理積回路NAND02で上述の制御信号生成回路を形成している。

【0020】

フリップフロップFF03のデータ端子には電源電圧VDD(Hレベル)を入力し、基準クロックREF_CLKを遅延素子D01により遅延させて、クロック端子に入力する。フリップフロップFF03のデータ出力は、否定論理積回路NAND02と論理和回路OR01に入力される。同様に、フリップフロップFF04のデータ端子には電源電圧VDD(Hレベル)を入力し、フィードバッククロックFB_CLKを遅延素子D02により遅延させて、クロック端子に入力する。フリップフロップFF04のデータ出力は、否定論理積回路NAND02と論理和回路OR02に入力される。また、フリップフロップFF03及びFF04のリセット端子には否定論理積回路NAND02の出力が入力される。

【0021】

フリップフロップFF05のデータ端子にはフリップフロップFF03のデータ出力を入力し、基準クロックREF_CLKをクロック端子に入力する。フリップフロップFF05のデータ出力を論理和回路OR01に入力する。フリップフロップFF06のデータ端子にはフリップフロップFF04のデータ出力を入力し、フィードバッククロックFB_CLKをクロック端子に入力する。フリップフロップFF06のデータ出力は論理和回路OR02に入力する。

【0022】

また、フリップフロップFF05及びFF06のリセット端子には動作許可信号ENが入力される。動作許可信号ENをLレベルに設定することでフリップフロップFF05及びFF06のデータ出力を初期化することができる。論理和回路OR01の出力をUP信号、論理和回路OR02の出力をDW信号とする。なお、フリップフロップFF03のデータ出力端子をノードS1、フリップフロップFF05のデータ出力端子をノードS2とする。

【0023】

次に、位相比較器11の動作を図3に示す位相比較器10の動作と対比して説明する。初めに、位相比較器10の動作について説明する。図8は、位相比較器10の入出力波形の一例を示すタイミングチャートである。図8には、位相比較器10に入力する基準クロックREF_CLKと、フィードバッククロックFB_CLKと、UP信号を示している。

【0024】

図8の時刻t3〜t4の期間(位相比較1)では、フリップフロップFF01の出力は、HレベルであるからUP信号もHレベルが出力される。時刻t4において、フィードバッククロックFB_CLKの立ち上りエッジがフリップフロップFF02に入力されると、フリップフロップFF02の出力もHレベルとなり、否定論理積回路NAND01の出力はLレベルとなる。その結果、フリップフロップFF01の出力は初期化(Lレベルと)となりUP信号もLレベルとなる。時刻t3〜t4と同様に、時刻t5〜t6の期間(位相比較2)及び時刻t7〜t8の期間(位相比較3)もUP信号はHレベルである。

【0025】

一方、時刻t8〜t11の期間(位相比較4及び5)においては、UP信号の動作は本来期待される動作と逆になってしまう。つまり、時刻t8における基準クロックREF_CLKの立ち上りエッジよりも、時刻t9におけるフィードバッククロックFB_CLKの立ち上りエッジが遅いため、時刻t9において否定論理積回路NAND01の出力はHレベルとなりフリップフロップFF01の出力(UP信号)はLレベルとなってしまう。その後、時刻t10で基準クロックREF_CLKの立ち上りエッジが入力され、時刻t11でフィードバッククロックFB_CLKの立ち上りエッジが入力されるまでUP信号はHレベルとなる。この時刻t8〜t11の期間に発生している現象がサイクルスリップであり、PLL回路1のロック動作の妨げになっている。

【0026】

続いて、位相比較器11の動作について説明する。図9は、位相比較器11の入出力波形の一例を示すタイミングチャートである。図9には、遅延素子D01の出力(基準クロックREF_CLKが遅延した波形)と、遅延素子D02の出力(フィードバッククロックFB_CLKが遅延した波形)と、ノードS1のレベルと、基準クロックREF_CLKと、ノードS2のレベルと、UP信号を示している。ノードS1のレベルは、位相比較器10におけるUP信号と同等である。

【0027】

時刻t14〜t15の期間(位相比較1)では、フリップフロップFF03のデータ出力(ノードS1)はHレベルであるため、UP信号もHレベルとなる。同様に、時刻t17〜t18の期間(位相比較2)でも、UP信号はHレベルとなる。時刻t22における遅延素子D01の出力の立ち上りエッジと時刻t23における遅延素子D02の出力の立ち上りエッジの関係のように、遅延素子D02の立ち上りエッジが遅れる場合が存在する。このような場合には、フリップフロップFF03のデータ出力(ノードS1)はLレベルとなる。しかし、基準クロックREF_CLKをクロック端子で受け付けているフリップフロップFF05のデータ出力(ノードS2)はノードS1がLレベルに遷移する前に、Hレベルとなっている(時刻t21)。そのため、ノードS1のレベルとノードS2のレベルの論理和がUP信号であるため、UP信号はHレベルを維持する。従って、位相比較器10でサイクルスリップが起きていた期間(時刻t22〜t26)であっても、位相比較器11ではサイクルスリップが発生しない。その結果、位相比較器11を使用するPLL回路2は高速にロック状態に遷移することが可能である。

【0028】

なお、時刻t26と時刻t28の期間ではサイクルスリップが発生している。時刻t23〜t25の期間におけるノードS1はLレベルである。また、フリップフロップFF05はこのノードS1をデータ入力としており、基準クロックREF_CLKの立ち上りエッジが入力された際(時刻t24)にはノードS1はLレベルとなっているためである。

【0029】

図10は、PLL回路1及びPLL回路2がロックする過程をシミュレーションした結果の一例である。図10の上段は、位相比較器10を使用した場合のシミュレーション結果であり、下段が位相比較器11を使用した場合のシミュレーション結果である。上述のように、Vcntはチャージポンプ20が出力する電圧制御発振器40の制御電圧であり、Vcntが一定になるとPLL発振周波数は安定していると判断することができる。なお、図10に示すVcnt1はループフィルタ30の内部ノードである。さらに、判定信号LDRTは、基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差が予め定めた閾値よりも小さくなるとHレベルからLレベルに変化する信号である。従って、判定信号LDRTがLレベルに変化した時刻から、PLL回路のロック状態を判断することができる。図10のシミュレーションから、位相比較器11を使用するPLL回路2がロックに要する時間はPLL回路1と比較して176ns早いことが分かる。

【0030】

なお、動作許可信号ENによって、フリップフロップFF03及びFF04のデータ出力を初期化することも可能である。図11は、位相比較器12の内部構成の一例を示す図である。位相比較器12は、位相比較器11に否定論理積回路NAND03とインバータ回路INV01を追加している。否定論理積回路NAND03において、否定論理積回路NAND02の出力と動作許可信号ENを受け付ける。否定論理積回路NAND03の出力をインバータ回路INV01に入力し、インバータ回路INV01の出力をフリップフロップFF03及びFF04のリセット端子に入力する。動作許可信号ENをHレベルに設定すると、位相比較器12は活性化し、Lレベルに設定するとフリップフロップFF03乃至FF06のデータ出力(UP信号及びDW信号)は全てLレベルとなる(非活性状態となる)。以下の実施形態においても同様に動作許可信号ENによって、UP信号及びDW信号をLレベルにすることが可能である。

【0031】

[第2の実施形態]

続いて、第2の実施形態について図面を参照して詳細に説明する。図12は本実施形態に係る位相比較器13の内部構成の一例を示す図である。図12において図7と同一構成要素には、同一の符号を表し、その説明を省略する。図12に示す位相比較器13と図7に示す位相比較器11の相違点は、フリップフロップFF07乃至FF14を追加し、論理和回路OR01及びOR02を論理和回路OR03及びOR04に変更している点である。

【0032】

フリップフロップFF07のデータ端子にフリップフロップFF05のデータ出力を入力し、クロック端子には基準クロックREF_CLKを入力する。さらに、データ出力端子は次段のフリップフロップFF09のデータ端子が接続されると共に、論理和回路OR03の入力端子に接続される。フリップフロップFF07のリセット端子には動作許可信号ENが入力される。フリップフロップFF08乃至FF14も同様に、前段のフリップフロップのデータ出力をデータ端子で受け付け、データ出力を次段のフリップフロップ及び論理和回路(OR03及びOR04)に出力する。

【0033】

位相比較器13を図12に示す構成とすることで、フリップフロップFF03又はフリップフロップFF04が出力するレベルは順次、次段のフリップフロップで保持される。その結果、サイクルスリップの発生するタイミングを遅らせることが可能になる。

【0034】

図13は、図3に示す位相比較器10と、第1の実施形態に係る位相比較器11と、本実施形態に係る位相比較器13のシミュレーション結果の一例を示す図である。時刻t30は、位相比較器13を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t31は、位相比較器11を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t32は、位相比較器10を用いた場合の判定信号LDRTがLレベルになる時間である。図13から、本実施形態に係る位相比較器13を用いた場合が最もPLL回路のロックが早いことが分かる。

【0035】

次に、PLL回路が理想的なロックを行なう場合と各位相比較器(10、11、13)の結果を検討する。図13の上段(位相比較器10の出力波形)に示す点線が、PLL回路において理想的にロックが行なわれた場合のVcntの波形を示している。このように理想的にロックが行なわれる場合であっても、2.2μsの時間(時刻t29)はロックに必要であることが分かる。

【0036】

なお、判定信号LDRTがLレベルになる時間をPLL回路がロックした時間とみなすと、位相比較器10を用いた場合のロック時間は4.55μs(時刻t32)であり、理想的なロックが行なわれた場合との差分は、4.55μs−2.2μs=2.35μsとなる。次に、位相比較器11を用いた場合のロック時間は、4.38μs(時刻t31)であり、理想的なロックとの差分は、4.38μs−2.2μs=2.18μsである。その結果、位相比較器11では、位相比較器10を用いた場合と比較して、(1−2.18/2.35)×100=7.2%の改善が行なえる。

【0037】

さらに、位相比較器13を用いた場合のロック時間は、4.15μs(時刻t30)であり、理想的なロックとの差分は、4.15μs−2.2μs=1.95である。その結果、位相比較器10を用いた場合と比較して、(1−1.95/2.35)×100=17.0%の改善が行なわれる。

【0038】

次に、上述のSATA規格対応のSerDesマクロにおいて、PartialモードからActiveモードに復帰する際のPLL回路のロック時間について考える。SerDesマクロ全体にて、PartialモードからActiveモードへの復帰に要する時間は、10μsまで許容される。その内部ブロックであるPLLは、より早く復帰する必要がある。ここでは、10μsの半分の5μs内で、PLLをロックさせることを考える。5μsを基準にして、各位相比較器(10、11、13)を用いた場合にPLL回路がロックする時間の改善率を検証する。

【0039】

位相比較器10と位相比較器11を用いた場合を考えると、ロックに要する時間は4.55μs−4.38μs=0.17μs短縮されている。従って、5μsを基準にすると0.17/5×100=3.4%の改善が実現できている。同様に、位相比較器10と位相比較器13を用いた場合を考えると、ロックに要する時間は4.55μs−4.15μs=0.4μs短縮されている。従って、5μsを基準にすると0.4/5×100=8%の改善が実現できている。

【0040】

[第3の実施形態]

続いて、第3の実施形態について図面を参照して詳細に説明する。図14に本実施形態に係るPLL回路3の内部構成の一例を示す。図14において図6と同一構成要素には、同一の符号を表し、その説明を省略する。図6に示すPLL回路2とPLL回路3の相違点は、位相比較器11を位相比較器14に変更し、位相差判定ブロック60の出力する判定信号LDRTを位相比較器14に入力する点である。

【0041】

図15は、位相比較器14の内部構成の一例を示す図である。図15に示す位相比較器14は、位相比較器12a及び12bと、2分周回路100及び101と、論理和回路OR05及びOR06から構成されている。位相比較器12a及び12bは、図11に示す位相比較器12と同一の回路である。2分周回路100は、フリップフロップFF15とインバータ回路INV02から構成されている。基準クロックREF_CLKをフリップフロップFF15のクロック端子に入力し、フリップフロップFF15のデータ出力をインバータ回路INV02で反転し、データ端子に入力している。同時に、フリップフロップFF15のデータ出力を位相比較器12bの基準クロックREF_CLKとして使用する。2分周回路101の構成は2分周回路100と同様のため、説明を省略する。

【0042】

2分周回路101により2分周したフィードバッククロックFB_CLKを位相比較器12bのフィードバッククロックFB_CLKとして使用する。位相比較器12a及び12bのUP信号を論理和回路OR05に入力し、論理和回路OR05の出力を新たなUP信号とする。同様に、位相比較器12a及び12bのDW信号を論理和回路OR06に入力し、論理和回路OR06の出力を新たなDW信号とする。

【0043】

さらに、動作許可信号ENを位相比較器12aに入力し、判定信号LDRTを位相比較器12bに入力する。上述のように、判定信号LDRTは基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差がある一定値より小さくなるとHレベルからLレベルに変化する信号である。判定信号LDRTを用いてPLL回路のロック状態の有無を判定している。PLL回路がロックする過程において、判定信号LDRTの初期状態はHレベルである。そのため、PLL回路3のロック開始直後は、図15に示す位相比較器12a及び12bは共に活性状態である。

【0044】

なお、位相比較器12aのUP信号を出力するノードをノードS3、2分周回路100の出力ノードをノードS4、2分周回路101の出力ノードをノードS5、位相比較器12bのUP信号を出力するノードをノードS6とする。

【0045】

次に、位相比較器14の動作を説明する。図16は、位相比較器14の入出力波形の一例を示すタイミングチャートである。位相比較器14は、内部に位相比較器12aと12bを含む構成であって、位相比較器12aの動作は図7の位相比較器11の動作と同一である。一方、位相比較器12bの動作についても基準クロックREF_CLKとフィードバッククロックFB_CLKが2分周となる他は動作に相違はない。位相比較器14では、位相比較器12aと位相比較器12bが独立して動作し、それぞれの出力するUP信号又はDW信号の論理和を位相比較器14の出力信号(UP信号及びDW信号)としている。

【0046】

図9の時刻t25〜t28の期間において、位相比較器11はサイクルスリップを起こしていた。位相比較器11のUP信号とノードS3のレベル変化は一致するため、時刻t40〜t42の期間にサイクルスリップの発生が認められる。

【0047】

しかし、位相比較器12bに入力するクロックは、基準クロックREF_CLKとフィードバッククロックFB_CLKを2分周したクロックであるので、時刻t40において、位相比較器12bに入力される基準クロックREF_CLK(ノードS4)の立ち上りエッジが入力後、フィードバッククロックFB_CLK(ノードS5)の立ち上りエッジが入力(時刻t43)されるまでの間は位相比較器12bが出力するUP信号はHレベルとなる(ノードS6)。そのため、位相比較器14自体のUP信号はHレベルを維持することができる(時刻t40〜t43)。

【0048】

即ち、2分周されたクロックを位相比較器12bに入力することで、位相比較器12aだけでは回避できなかったサイクルスリップを回避することができる。その結果、PLL回路3は高速に所定の周波数に引き込みが可能となる。なお、基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差が一定値より小さくなると判定信号LDRTはLレベルとなり、位相比較器12bは非活性状態となる。位相比較器12bが非活性状態となった後は、位相比較器12aによりPLL回路3のロック動作が継続されることになる。

【0049】

[第4の実施形態]

続いて、第4の実施形態について図面を参照して詳細に説明する。図17は、本実施形態に係る位相比較器15の内部構成の一例を示す図である。図17において図15と同一構成要素には、同一の符号を表し、その説明を省略する。図15に示す位相比較器14と位相比較器15の相違点は、位相比較器14に位相比較器12c及び12dと、2分周回路102乃至105と、論理和回路OR07乃至OR10を追加する点である。位相比較器12c及び12dは、位相比較器12と同一のため説明を省略する。2分周回路102乃至105についても、2分周回路100と同一構成のため説明を省略する。

【0050】

位相比較器12cは2分周回路102及び103が供給するクロックを受け付ける。2分周回路102は、2分周回路100の出力を2分周するものなので、基準クロックREF_CLKを4分周したクロックが位相比較器12cに入力される。同様に、フィードバッククロックFB_CLKを4分周したクロックが位相比較器12cに入力される。位相比較器12dについても、基準クロックREF_CLKを8分周したクロックとフィードバッククロックFB_CLKを8分周したクロックを入力する。

【0051】

位相比較器15においても、位相比較器12a乃至12dが独立して動作し、各位相比較器の出力するUP信号又はDW信号の論理和を位相比較器15のUP信号又はDW信号として出力する。位相比較器15では、位相比較器14と比較してサイクルスリップの発生を遅らせることが可能になるのでよりPLLのロック時間を短縮することができる。

【0052】

図18は、図3に示す位相比較器10と、第3の実施形態に係る位相比較器14と、本実施形態に係る位相比較器15のシミュレーション結果の一例を示す図である。時刻t44は位相比較器15を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t45は位相比較器14を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t46は位相比較器10を用いた場合の判定信号LDRTがLレベルになる時間である。

【0053】

次に、位相比較器14及び15を使用したPLL回路の引き込み時間の改善率を検証する。位相比較器10を用いた場合のロック時間は4.55μs(時刻t46)であり、理想的なロックが行なわれた場合との差分は、4.55μs−2.2μs=2.35μsとなる。位相比較器14を用いた場合のロック時間は、3.05μs(時刻t45)であり、理想的なロックとの差分は、3.05μs−2.2μs=0.85μsである。その結果、位相比較器10を用いた場合と比較して、(1−0.85/2.35)×100=63.8%の改善が行なえる。さらに、位相比較器15を用いた場合のロック時間は、2.60μs(時刻t44)であり、理想的なロックとの差分は、2.60μs−2.2μs=0.4である。その結果、位相比較器10を用いた場合と比較して、(1−0.4/2.35)×100=83.0%の改善が行なわれる。

【0054】

次に、SATA規格対応のSerDesマクロにおけるPartialモードからActiveモードに復帰する際に、PLLのロック時間の目標としている5μsを基準にして改善率を検証する。位相比較器10と位相比較器14を用いた場合を考えると、ロックに要する時間は4.55μs−3.05μs=1.5μs短縮されている。従って、5μsを基準にすると1.5/5×100=30%の改善が実現できている。同様に、位相比較器10と位相比較器15を用いた場合を考えると、ロックに要する時間は4.55μs−2.60μs=1.95μs短縮されている。従って、5μsを基準にすると1.95/5×100=39%の改善が実現できている。

【0055】

以上のように、2分周回路を追加し、分周数を増加させた位相比較器15のPLL回路の引き込み時間に対する改善効果は非常に大きい。ただし、無条件に2分周回路を増やすことは適切ではない。分周回路やフリップフロップ等を追加する必要があるため、分周数が大きくなればなるほど、レイアウト面積が増加するためである。

【0056】

さらに、PLL回路の安定性も考慮する必要がある。初めに、図2に示すPLL回路1の安定性を考える。その際に、ループフィルタ30は容量C1及びC2と、抵抗R1から構成されるものとする(図19参照)。

【0057】

PLL回路1のオープンループゲインA1(s)は、式(1)から求めることができる。

A1(s)=Icp×F(s)×(Kvco/s)×(1/N) ・・・(1)

なお、チャージポンプ電流をIcp[uA/2π]、ループフィルタ30の伝達関数をF(s)、電圧制御発振器40のゲインをKvco[GHz/V]、分周回路50の分周比をNとする。

【0058】

基準クロックREF_CLKの周波数としてFref=40[MHz]、電圧制御発振器40の発振周波数としてFvco=6[GHz]、Kvco=3[GHz/V]、Icp=25[uA/2π]、N=150、C1=1[pF]、C2=160[pF]、R1=7000[Ω]として、式(1)のボード線図からPLL回路1の位相余裕を求めると74.8度となる。位相余裕は、回路の安定性の判断基準であり45度〜60度以上であれば安定な回路であるといえる。

【0059】

次に、第3及び第4の実施形態に係る位相比較器14及び15を用いたPLL回路の安定性について考える。PLLの引き込みが完了した後は、第1の実施形態に係るPLL回路2と同様の動作になる。PLL回路2の位相余裕もPLL回路1と同様に74.8度である。従って、定常状態における位相比較器14及び15を用いたPLL回路の安定性は維持できている。

【0060】

続いて、位相比較器14及び15を用いたPLL回路の引き込み時について考える。位相比較器14を用いたPLL回路の引き込み時のオープンループゲインA2(s)は式(2)表せる。

A2(s)=Icp×F(s)×(Kvco/s)×(1/N)×(1/2) ・・・(2)

位相比較器14は、2分周回路を含むため、式(1)に対して分周数2で除算することで、式(2)を導き出すことができる。式(2)を用いて位相余裕を求めると64.6度となる。同様に、位相比較器15を用いたPLL回路のPLL引き込み時のオープンループゲインA3(s)は式(3)で表せる。

A3(s)=Icp×F(s)×(Kvco/s)×(1/N)×(1/8) ・・・(3)

位相比較器15では、8分周回路が追加されているため、分周数8で除算する。式(3)を用いて位相余裕を求めると39.9度となる。このように、分周数を増やすとPLL回路の安定性が低下することが分かる。位相比較器15を用いたPLL回路のシミュレーション結果では、PLLの引き込みは完了しているが、実際の回路の設計時においては安定性も考慮する必要がある。そのため、サイクルスリップを回避することによるPLL回路のロック時間の短縮とPLL回路の安定性の適切なバランスを考えることが必要となる。

【0061】

なお、引用した上記の特許文献等の各開示は、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0062】

1、2、3 PLL回路

10、11、12、12a〜12d、13、14、15 位相比較器

20 チャージポンプ

30 ループフィルタ

40 電圧制御発振器

50 分周回路

60 位相差判定ブロック

70 カウンタ

100〜105 2分周回路

C1、C2 容量

D01、D02 遅延素子

FF01〜FF27 フリップフロップ

INV01〜INV07 インバータ回路

NAND01〜NAND03 否定論理積回路

OR01〜OR10 論理和回路

R1 抵抗

【技術分野】

【0001】

本発明は、PLL回路(位相同期回路)に関する。特に、位相比較器を備えるPLL回路に関する。

【背景技術】

【0002】

PLL回路が様々な電子機器の回路に用いられている。図2は、PLL回路1の内部構成の一例を示す図である。図2に示すPLL回路1は、位相比較器(PFD)10と、チャージポンプ(CP)20と、ループフィルタ(LP)30と、電圧制御発振器(VCO)40と、分周回路50から構成されている。PLL回路1では、位相比較器10において基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差を検出し、チャージポンプ20により昇圧した後にループフィルタ30によりDC電圧に変換する。

【0003】

図3は、位相比較器10の内部構成の一例を示す図である。位相比較器10は、フリップフロップFF01及びFF02と、否定論理積回路NAND01から構成されている。位相比較器10では、基準クロックREF_CLKとフィードバッククロックFB_CLKを比較することで、チャージポンプ20に対する制御信号(UP信号及びDW信号)を生成する。電圧制御発振器40では、DC電圧に比例した周波数の出力を行なう。電圧制御発振器40の出力は、分周回路50により分周されてフィードバッククロックFB_CLKとして使用される。

【0004】

ここで、特許文献1において、電圧制御発振器の出力周波数(フィードバッククロック)と基準クロックとの間の位相差を検出し、位相差が360度以上の場合に誤差信号を出力する位相周波数検出器(PFD)を備えるPLL回路が開示されている。特許文献1で開示された技術では、誤差信号に基づいて電圧制御発振器のフリーランニング周波数を調整し、PLL回路の周波数可変範囲を維持している。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特表2006−518151号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

なお、上記先行技術文献の各開示を、本書に引用をもって繰り込むものとする。以下の分析は、本発明の観点からなされたものである。

【0007】

図2に示すPLL回路1では、ロックを開始(引き込みを開始)する際にサイクルスリップが生じるという問題がある。PLL回路1の周波数可変範囲が広い場合には、位相比較器10における位相差が±360度を越えることが考えられる。位相差が±360度を越えた場合に、基準クロックREF_CLKとフィードバッククロックFB_CLKの周波数が一致していないにも関わらず、位相が一致したと判断されてしまうため、PLL回路1のロックが遅れてしまう。これがサイクルスリップである。

【0008】

図4は、PLL回路1の引き込み過程のシミュレーション結果の一例を示す図である。図4では、PLL回路1の出力とチャージポンプ20の出力電圧Vcntを示す。Vcntが一定値になるとPLL回路1はロック状態にあるといえる。図4から、時刻t1に引き込みを開始して、時刻t2でロックするまでの間にVcntが上下に大きく変動(ギザギザ部分)しているのが分かる。この大きく変動している期間にサイクルスリップが発生しており、PLL回路1のロックが遅れる要因となる。

【0009】

上述のように、PLL回路は様々な電子機器において使用されており、特に近年では、SerDes(Serializer/Deserializer)マクロにおけるクロック生成モジュールとして使用されることが多い。図5は、SerDesマクロの内部構成の一例を示す図である。SerDesマクロにおいては、PLL回路から、データの送受信を行なうTx部及びRx部に対して基準クロックを供給する。SerDesマクロは、SATA(Serial ATA)、PCIe(PCI express)、USB(Universal Serial Bus)3.0、HDMI(High−Definition Multimedia Interface)等のバス規格を実現する製品に使用される。

【0010】

これらのバス規格の中でSATA規格に対応したSerDesマクロには、Partialモードと呼ばれるPLL回路をオフ(非活性)にするモードが存在する。Partialモードに遷移させることによって、SerDesマクロでの消費電力を低減する。一方、PartialモードからActiveモード(PLL回路を活性化)に遷移する際にSerDesマクロ全体での復帰時間に関する仕様が定められている。この復帰時間は非常に短く、PLL回路自体も高速でロックを行なわないとSerDesマクロに求められる仕様を満足することができない。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【課題を解決するための手段】

【0011】

本発明の一視点によれば、位相比較器と、前記位相比較器と接続されるチャージポンプと、を備えるPLL回路であって、前記位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、前記チャージポンプの出力電圧を上昇させる第1のUP信号及び前記チャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、前記基準クロックに同期させ、前記第1のUP信号に基づき前記チャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、前記フィードバッククロックに同期させ、前記第1のDW信号に基づき前記チャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含むPLL回路が提供される。

【発明の効果】

【0012】

本発明の一視点によれば、サイクルスリップを低減し、高速にロックを行なうPLL回路が提供される。

【図面の簡単な説明】

【0013】

【図1】本発明の実施形態の概要を説明するための図である。

【図2】PLL回路の内部構成の一例を示す図である。

【図3】図2に示す位相比較器の内部構成の一例を示す図である。

【図4】図2に示すPLL回路の引き込み過程のシミュレーション結果の一例を示す図である。

【図5】SerDesマクロの内部構成の一例を示す図である。

【図6】本発明の第1の実施形態に係るPLL回路の内部構成の一例を示す図である。

【図7】図6に示す位相比較器の内部構成の一例を示す図である。

【図8】図3に示す位相比較器の入出力波形の一例を示すタイミングチャートである。

【図9】図7に示す位相比較器の入出力波形の一例を示すタイミングチャートである。

【図10】PLL回路がロックする過程をシミュレーションした結果の一例である。

【図11】図6に示す位相比較器の別の内部構成の一例を示す図である。

【図12】第2の実施形態に係る位相比較器の内部構成の一例を示す図である。

【図13】位相比較器のシミュレーション結果の一例を示す図である。

【図14】第3の実施形態に係るPLL回路の内部構成の一例を示す図である。

【図15】図14に示す位相比較器の内部構成の一例を示す図である。

【図16】図15に示す位相比較器の入出力波形の一例を示すタイミングチャートである。

【図17】第4の実施形態に係る位相比較器の内部構成の一例を示す図である。

【図18】位相比較器のシミュレーション結果の一例を示す図である。

【図19】ループフィルタの内部構成の一例を示す図である。

【発明を実施するための形態】

【0014】

初めに、図1を用いて実施形態の概要について説明する。なお、この概要に付記した図面参照符号は、理解を助けるための一例として各要素に便宜上付記したものであり、本発明を図示の態様に限定することを意図するものではない。

【0015】

上述のように、サイクルスリップが発生することでPLL回路の引き込み時間が遅れるという問題がある。PLL回路を搭載する回路の仕様によっては、PLL回路が引き込みを完了するまでに許容される時間は極めて短い場合も多い。そのため、サイクルスリップを低減し、高速にロックを行なうPLL回路の提供が望まれる。

【0016】

そこで、図1に示すPLL回路を提供する。図1に示すPLL回路は、位相比較器と、位相比較器と接続されるチャージポンプと、を備えている。さらに、位相比較器は、基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、チャージポンプの出力電圧を上昇させる第1のUP信号及びチャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、基準クロックに同期させ、第1のUP信号に基づきチャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、フィードバッククロックに同期させ、第1のDW信号に基づきチャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、を含んでいる。

【0017】

フィードバッククロックの論理レベルの変化が基準クロックの論理レベルの変化よりも遅れることによって、制御信号生成回路が出力する第1のUP信号又は第2のDW信号にサイクルスリップが発生する場合がある。制御信号生成回路は基準クロックとフィードバッククロックを遅延させたクロックによって動作しているが、第1の保持回路及び第2の保持回路は遅延させていない基準クロック及びフィードバッククロックで動作している。そのため、第1のUP信号又は第1のDW信号にサイクルスリップが発生したとしても、サイクルスリップが発生する前の第1のUP信号又は第1のDW信号を第1の保持回路又は第2の保持回路で基準クロック又はフィードバッククロックに同期させて出力可能である。すると、第1のUP信号又は第1のDW信号が、サイクルスリップの発生によりサイクルスリップ発生前の論理レベルから反転してしまったとしても、第2のUP信号又は第2のDW信号はサイクルスリップ発生前の論理レベルを維持できる。その結果、第1のUP信号又は第2のUP信号(第1のDW信号又は第2のDW信号)で、チャージポンプを動作させることでサイクルスリップが低減し、PLL回路のロック時間が短縮できる。

【0018】

[第1の実施形態]

次に、本発明の第1の実施形態について、図面を用いてより詳細に説明する。図6に本実施形態に係るPLL回路2の内部構成の一例を示す。図6において、図2と同一の構成要素には同一の符号を付し、その説明を省略する。図2に示すPLL回路1とPLL回路2の相違点は、位相比較器10に代えて位相比較器11を使用することと、位相差判定ブロック60及びカウンタ70を追加する点である。位相差判定ブロック60では、UP信号及びDW信号により基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差を判定する。その際に、位相差がある一定値より小さい値となると判定信号LDRTを出力する。カウンタ70では、判定信号LDRTが一定時間変動しないことを確認するとPLL回路1がロック状態に遷移したと判断し、ロック信号を出力する。

【0019】

図7は、位相比較器11の内部構成の一例を示す図である。位相比較器11は、フリップフロップFF03乃至FF06と、否定論理積回路NAND02と、論理和回路OR01及びOR02と、遅延素子D01及びD02から構成されている。フリップフロップFF03及びFF04と、否定論理積回路NAND02で上述の制御信号生成回路を形成している。

【0020】

フリップフロップFF03のデータ端子には電源電圧VDD(Hレベル)を入力し、基準クロックREF_CLKを遅延素子D01により遅延させて、クロック端子に入力する。フリップフロップFF03のデータ出力は、否定論理積回路NAND02と論理和回路OR01に入力される。同様に、フリップフロップFF04のデータ端子には電源電圧VDD(Hレベル)を入力し、フィードバッククロックFB_CLKを遅延素子D02により遅延させて、クロック端子に入力する。フリップフロップFF04のデータ出力は、否定論理積回路NAND02と論理和回路OR02に入力される。また、フリップフロップFF03及びFF04のリセット端子には否定論理積回路NAND02の出力が入力される。

【0021】

フリップフロップFF05のデータ端子にはフリップフロップFF03のデータ出力を入力し、基準クロックREF_CLKをクロック端子に入力する。フリップフロップFF05のデータ出力を論理和回路OR01に入力する。フリップフロップFF06のデータ端子にはフリップフロップFF04のデータ出力を入力し、フィードバッククロックFB_CLKをクロック端子に入力する。フリップフロップFF06のデータ出力は論理和回路OR02に入力する。

【0022】

また、フリップフロップFF05及びFF06のリセット端子には動作許可信号ENが入力される。動作許可信号ENをLレベルに設定することでフリップフロップFF05及びFF06のデータ出力を初期化することができる。論理和回路OR01の出力をUP信号、論理和回路OR02の出力をDW信号とする。なお、フリップフロップFF03のデータ出力端子をノードS1、フリップフロップFF05のデータ出力端子をノードS2とする。

【0023】

次に、位相比較器11の動作を図3に示す位相比較器10の動作と対比して説明する。初めに、位相比較器10の動作について説明する。図8は、位相比較器10の入出力波形の一例を示すタイミングチャートである。図8には、位相比較器10に入力する基準クロックREF_CLKと、フィードバッククロックFB_CLKと、UP信号を示している。

【0024】

図8の時刻t3〜t4の期間(位相比較1)では、フリップフロップFF01の出力は、HレベルであるからUP信号もHレベルが出力される。時刻t4において、フィードバッククロックFB_CLKの立ち上りエッジがフリップフロップFF02に入力されると、フリップフロップFF02の出力もHレベルとなり、否定論理積回路NAND01の出力はLレベルとなる。その結果、フリップフロップFF01の出力は初期化(Lレベルと)となりUP信号もLレベルとなる。時刻t3〜t4と同様に、時刻t5〜t6の期間(位相比較2)及び時刻t7〜t8の期間(位相比較3)もUP信号はHレベルである。

【0025】

一方、時刻t8〜t11の期間(位相比較4及び5)においては、UP信号の動作は本来期待される動作と逆になってしまう。つまり、時刻t8における基準クロックREF_CLKの立ち上りエッジよりも、時刻t9におけるフィードバッククロックFB_CLKの立ち上りエッジが遅いため、時刻t9において否定論理積回路NAND01の出力はHレベルとなりフリップフロップFF01の出力(UP信号)はLレベルとなってしまう。その後、時刻t10で基準クロックREF_CLKの立ち上りエッジが入力され、時刻t11でフィードバッククロックFB_CLKの立ち上りエッジが入力されるまでUP信号はHレベルとなる。この時刻t8〜t11の期間に発生している現象がサイクルスリップであり、PLL回路1のロック動作の妨げになっている。

【0026】

続いて、位相比較器11の動作について説明する。図9は、位相比較器11の入出力波形の一例を示すタイミングチャートである。図9には、遅延素子D01の出力(基準クロックREF_CLKが遅延した波形)と、遅延素子D02の出力(フィードバッククロックFB_CLKが遅延した波形)と、ノードS1のレベルと、基準クロックREF_CLKと、ノードS2のレベルと、UP信号を示している。ノードS1のレベルは、位相比較器10におけるUP信号と同等である。

【0027】

時刻t14〜t15の期間(位相比較1)では、フリップフロップFF03のデータ出力(ノードS1)はHレベルであるため、UP信号もHレベルとなる。同様に、時刻t17〜t18の期間(位相比較2)でも、UP信号はHレベルとなる。時刻t22における遅延素子D01の出力の立ち上りエッジと時刻t23における遅延素子D02の出力の立ち上りエッジの関係のように、遅延素子D02の立ち上りエッジが遅れる場合が存在する。このような場合には、フリップフロップFF03のデータ出力(ノードS1)はLレベルとなる。しかし、基準クロックREF_CLKをクロック端子で受け付けているフリップフロップFF05のデータ出力(ノードS2)はノードS1がLレベルに遷移する前に、Hレベルとなっている(時刻t21)。そのため、ノードS1のレベルとノードS2のレベルの論理和がUP信号であるため、UP信号はHレベルを維持する。従って、位相比較器10でサイクルスリップが起きていた期間(時刻t22〜t26)であっても、位相比較器11ではサイクルスリップが発生しない。その結果、位相比較器11を使用するPLL回路2は高速にロック状態に遷移することが可能である。

【0028】

なお、時刻t26と時刻t28の期間ではサイクルスリップが発生している。時刻t23〜t25の期間におけるノードS1はLレベルである。また、フリップフロップFF05はこのノードS1をデータ入力としており、基準クロックREF_CLKの立ち上りエッジが入力された際(時刻t24)にはノードS1はLレベルとなっているためである。

【0029】

図10は、PLL回路1及びPLL回路2がロックする過程をシミュレーションした結果の一例である。図10の上段は、位相比較器10を使用した場合のシミュレーション結果であり、下段が位相比較器11を使用した場合のシミュレーション結果である。上述のように、Vcntはチャージポンプ20が出力する電圧制御発振器40の制御電圧であり、Vcntが一定になるとPLL発振周波数は安定していると判断することができる。なお、図10に示すVcnt1はループフィルタ30の内部ノードである。さらに、判定信号LDRTは、基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差が予め定めた閾値よりも小さくなるとHレベルからLレベルに変化する信号である。従って、判定信号LDRTがLレベルに変化した時刻から、PLL回路のロック状態を判断することができる。図10のシミュレーションから、位相比較器11を使用するPLL回路2がロックに要する時間はPLL回路1と比較して176ns早いことが分かる。

【0030】

なお、動作許可信号ENによって、フリップフロップFF03及びFF04のデータ出力を初期化することも可能である。図11は、位相比較器12の内部構成の一例を示す図である。位相比較器12は、位相比較器11に否定論理積回路NAND03とインバータ回路INV01を追加している。否定論理積回路NAND03において、否定論理積回路NAND02の出力と動作許可信号ENを受け付ける。否定論理積回路NAND03の出力をインバータ回路INV01に入力し、インバータ回路INV01の出力をフリップフロップFF03及びFF04のリセット端子に入力する。動作許可信号ENをHレベルに設定すると、位相比較器12は活性化し、Lレベルに設定するとフリップフロップFF03乃至FF06のデータ出力(UP信号及びDW信号)は全てLレベルとなる(非活性状態となる)。以下の実施形態においても同様に動作許可信号ENによって、UP信号及びDW信号をLレベルにすることが可能である。

【0031】

[第2の実施形態]

続いて、第2の実施形態について図面を参照して詳細に説明する。図12は本実施形態に係る位相比較器13の内部構成の一例を示す図である。図12において図7と同一構成要素には、同一の符号を表し、その説明を省略する。図12に示す位相比較器13と図7に示す位相比較器11の相違点は、フリップフロップFF07乃至FF14を追加し、論理和回路OR01及びOR02を論理和回路OR03及びOR04に変更している点である。

【0032】

フリップフロップFF07のデータ端子にフリップフロップFF05のデータ出力を入力し、クロック端子には基準クロックREF_CLKを入力する。さらに、データ出力端子は次段のフリップフロップFF09のデータ端子が接続されると共に、論理和回路OR03の入力端子に接続される。フリップフロップFF07のリセット端子には動作許可信号ENが入力される。フリップフロップFF08乃至FF14も同様に、前段のフリップフロップのデータ出力をデータ端子で受け付け、データ出力を次段のフリップフロップ及び論理和回路(OR03及びOR04)に出力する。

【0033】

位相比較器13を図12に示す構成とすることで、フリップフロップFF03又はフリップフロップFF04が出力するレベルは順次、次段のフリップフロップで保持される。その結果、サイクルスリップの発生するタイミングを遅らせることが可能になる。

【0034】

図13は、図3に示す位相比較器10と、第1の実施形態に係る位相比較器11と、本実施形態に係る位相比較器13のシミュレーション結果の一例を示す図である。時刻t30は、位相比較器13を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t31は、位相比較器11を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t32は、位相比較器10を用いた場合の判定信号LDRTがLレベルになる時間である。図13から、本実施形態に係る位相比較器13を用いた場合が最もPLL回路のロックが早いことが分かる。

【0035】

次に、PLL回路が理想的なロックを行なう場合と各位相比較器(10、11、13)の結果を検討する。図13の上段(位相比較器10の出力波形)に示す点線が、PLL回路において理想的にロックが行なわれた場合のVcntの波形を示している。このように理想的にロックが行なわれる場合であっても、2.2μsの時間(時刻t29)はロックに必要であることが分かる。

【0036】

なお、判定信号LDRTがLレベルになる時間をPLL回路がロックした時間とみなすと、位相比較器10を用いた場合のロック時間は4.55μs(時刻t32)であり、理想的なロックが行なわれた場合との差分は、4.55μs−2.2μs=2.35μsとなる。次に、位相比較器11を用いた場合のロック時間は、4.38μs(時刻t31)であり、理想的なロックとの差分は、4.38μs−2.2μs=2.18μsである。その結果、位相比較器11では、位相比較器10を用いた場合と比較して、(1−2.18/2.35)×100=7.2%の改善が行なえる。

【0037】

さらに、位相比較器13を用いた場合のロック時間は、4.15μs(時刻t30)であり、理想的なロックとの差分は、4.15μs−2.2μs=1.95である。その結果、位相比較器10を用いた場合と比較して、(1−1.95/2.35)×100=17.0%の改善が行なわれる。

【0038】

次に、上述のSATA規格対応のSerDesマクロにおいて、PartialモードからActiveモードに復帰する際のPLL回路のロック時間について考える。SerDesマクロ全体にて、PartialモードからActiveモードへの復帰に要する時間は、10μsまで許容される。その内部ブロックであるPLLは、より早く復帰する必要がある。ここでは、10μsの半分の5μs内で、PLLをロックさせることを考える。5μsを基準にして、各位相比較器(10、11、13)を用いた場合にPLL回路がロックする時間の改善率を検証する。

【0039】

位相比較器10と位相比較器11を用いた場合を考えると、ロックに要する時間は4.55μs−4.38μs=0.17μs短縮されている。従って、5μsを基準にすると0.17/5×100=3.4%の改善が実現できている。同様に、位相比較器10と位相比較器13を用いた場合を考えると、ロックに要する時間は4.55μs−4.15μs=0.4μs短縮されている。従って、5μsを基準にすると0.4/5×100=8%の改善が実現できている。

【0040】

[第3の実施形態]

続いて、第3の実施形態について図面を参照して詳細に説明する。図14に本実施形態に係るPLL回路3の内部構成の一例を示す。図14において図6と同一構成要素には、同一の符号を表し、その説明を省略する。図6に示すPLL回路2とPLL回路3の相違点は、位相比較器11を位相比較器14に変更し、位相差判定ブロック60の出力する判定信号LDRTを位相比較器14に入力する点である。

【0041】

図15は、位相比較器14の内部構成の一例を示す図である。図15に示す位相比較器14は、位相比較器12a及び12bと、2分周回路100及び101と、論理和回路OR05及びOR06から構成されている。位相比較器12a及び12bは、図11に示す位相比較器12と同一の回路である。2分周回路100は、フリップフロップFF15とインバータ回路INV02から構成されている。基準クロックREF_CLKをフリップフロップFF15のクロック端子に入力し、フリップフロップFF15のデータ出力をインバータ回路INV02で反転し、データ端子に入力している。同時に、フリップフロップFF15のデータ出力を位相比較器12bの基準クロックREF_CLKとして使用する。2分周回路101の構成は2分周回路100と同様のため、説明を省略する。

【0042】

2分周回路101により2分周したフィードバッククロックFB_CLKを位相比較器12bのフィードバッククロックFB_CLKとして使用する。位相比較器12a及び12bのUP信号を論理和回路OR05に入力し、論理和回路OR05の出力を新たなUP信号とする。同様に、位相比較器12a及び12bのDW信号を論理和回路OR06に入力し、論理和回路OR06の出力を新たなDW信号とする。

【0043】

さらに、動作許可信号ENを位相比較器12aに入力し、判定信号LDRTを位相比較器12bに入力する。上述のように、判定信号LDRTは基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差がある一定値より小さくなるとHレベルからLレベルに変化する信号である。判定信号LDRTを用いてPLL回路のロック状態の有無を判定している。PLL回路がロックする過程において、判定信号LDRTの初期状態はHレベルである。そのため、PLL回路3のロック開始直後は、図15に示す位相比較器12a及び12bは共に活性状態である。

【0044】

なお、位相比較器12aのUP信号を出力するノードをノードS3、2分周回路100の出力ノードをノードS4、2分周回路101の出力ノードをノードS5、位相比較器12bのUP信号を出力するノードをノードS6とする。

【0045】

次に、位相比較器14の動作を説明する。図16は、位相比較器14の入出力波形の一例を示すタイミングチャートである。位相比較器14は、内部に位相比較器12aと12bを含む構成であって、位相比較器12aの動作は図7の位相比較器11の動作と同一である。一方、位相比較器12bの動作についても基準クロックREF_CLKとフィードバッククロックFB_CLKが2分周となる他は動作に相違はない。位相比較器14では、位相比較器12aと位相比較器12bが独立して動作し、それぞれの出力するUP信号又はDW信号の論理和を位相比較器14の出力信号(UP信号及びDW信号)としている。

【0046】

図9の時刻t25〜t28の期間において、位相比較器11はサイクルスリップを起こしていた。位相比較器11のUP信号とノードS3のレベル変化は一致するため、時刻t40〜t42の期間にサイクルスリップの発生が認められる。

【0047】

しかし、位相比較器12bに入力するクロックは、基準クロックREF_CLKとフィードバッククロックFB_CLKを2分周したクロックであるので、時刻t40において、位相比較器12bに入力される基準クロックREF_CLK(ノードS4)の立ち上りエッジが入力後、フィードバッククロックFB_CLK(ノードS5)の立ち上りエッジが入力(時刻t43)されるまでの間は位相比較器12bが出力するUP信号はHレベルとなる(ノードS6)。そのため、位相比較器14自体のUP信号はHレベルを維持することができる(時刻t40〜t43)。

【0048】

即ち、2分周されたクロックを位相比較器12bに入力することで、位相比較器12aだけでは回避できなかったサイクルスリップを回避することができる。その結果、PLL回路3は高速に所定の周波数に引き込みが可能となる。なお、基準クロックREF_CLKとフィードバッククロックFB_CLKの位相差が一定値より小さくなると判定信号LDRTはLレベルとなり、位相比較器12bは非活性状態となる。位相比較器12bが非活性状態となった後は、位相比較器12aによりPLL回路3のロック動作が継続されることになる。

【0049】

[第4の実施形態]

続いて、第4の実施形態について図面を参照して詳細に説明する。図17は、本実施形態に係る位相比較器15の内部構成の一例を示す図である。図17において図15と同一構成要素には、同一の符号を表し、その説明を省略する。図15に示す位相比較器14と位相比較器15の相違点は、位相比較器14に位相比較器12c及び12dと、2分周回路102乃至105と、論理和回路OR07乃至OR10を追加する点である。位相比較器12c及び12dは、位相比較器12と同一のため説明を省略する。2分周回路102乃至105についても、2分周回路100と同一構成のため説明を省略する。

【0050】

位相比較器12cは2分周回路102及び103が供給するクロックを受け付ける。2分周回路102は、2分周回路100の出力を2分周するものなので、基準クロックREF_CLKを4分周したクロックが位相比較器12cに入力される。同様に、フィードバッククロックFB_CLKを4分周したクロックが位相比較器12cに入力される。位相比較器12dについても、基準クロックREF_CLKを8分周したクロックとフィードバッククロックFB_CLKを8分周したクロックを入力する。

【0051】

位相比較器15においても、位相比較器12a乃至12dが独立して動作し、各位相比較器の出力するUP信号又はDW信号の論理和を位相比較器15のUP信号又はDW信号として出力する。位相比較器15では、位相比較器14と比較してサイクルスリップの発生を遅らせることが可能になるのでよりPLLのロック時間を短縮することができる。

【0052】

図18は、図3に示す位相比較器10と、第3の実施形態に係る位相比較器14と、本実施形態に係る位相比較器15のシミュレーション結果の一例を示す図である。時刻t44は位相比較器15を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t45は位相比較器14を用いた場合の判定信号LDRTがLレベルになる時間であり、時刻t46は位相比較器10を用いた場合の判定信号LDRTがLレベルになる時間である。

【0053】

次に、位相比較器14及び15を使用したPLL回路の引き込み時間の改善率を検証する。位相比較器10を用いた場合のロック時間は4.55μs(時刻t46)であり、理想的なロックが行なわれた場合との差分は、4.55μs−2.2μs=2.35μsとなる。位相比較器14を用いた場合のロック時間は、3.05μs(時刻t45)であり、理想的なロックとの差分は、3.05μs−2.2μs=0.85μsである。その結果、位相比較器10を用いた場合と比較して、(1−0.85/2.35)×100=63.8%の改善が行なえる。さらに、位相比較器15を用いた場合のロック時間は、2.60μs(時刻t44)であり、理想的なロックとの差分は、2.60μs−2.2μs=0.4である。その結果、位相比較器10を用いた場合と比較して、(1−0.4/2.35)×100=83.0%の改善が行なわれる。

【0054】

次に、SATA規格対応のSerDesマクロにおけるPartialモードからActiveモードに復帰する際に、PLLのロック時間の目標としている5μsを基準にして改善率を検証する。位相比較器10と位相比較器14を用いた場合を考えると、ロックに要する時間は4.55μs−3.05μs=1.5μs短縮されている。従って、5μsを基準にすると1.5/5×100=30%の改善が実現できている。同様に、位相比較器10と位相比較器15を用いた場合を考えると、ロックに要する時間は4.55μs−2.60μs=1.95μs短縮されている。従って、5μsを基準にすると1.95/5×100=39%の改善が実現できている。

【0055】

以上のように、2分周回路を追加し、分周数を増加させた位相比較器15のPLL回路の引き込み時間に対する改善効果は非常に大きい。ただし、無条件に2分周回路を増やすことは適切ではない。分周回路やフリップフロップ等を追加する必要があるため、分周数が大きくなればなるほど、レイアウト面積が増加するためである。

【0056】

さらに、PLL回路の安定性も考慮する必要がある。初めに、図2に示すPLL回路1の安定性を考える。その際に、ループフィルタ30は容量C1及びC2と、抵抗R1から構成されるものとする(図19参照)。

【0057】

PLL回路1のオープンループゲインA1(s)は、式(1)から求めることができる。

A1(s)=Icp×F(s)×(Kvco/s)×(1/N) ・・・(1)

なお、チャージポンプ電流をIcp[uA/2π]、ループフィルタ30の伝達関数をF(s)、電圧制御発振器40のゲインをKvco[GHz/V]、分周回路50の分周比をNとする。

【0058】

基準クロックREF_CLKの周波数としてFref=40[MHz]、電圧制御発振器40の発振周波数としてFvco=6[GHz]、Kvco=3[GHz/V]、Icp=25[uA/2π]、N=150、C1=1[pF]、C2=160[pF]、R1=7000[Ω]として、式(1)のボード線図からPLL回路1の位相余裕を求めると74.8度となる。位相余裕は、回路の安定性の判断基準であり45度〜60度以上であれば安定な回路であるといえる。

【0059】

次に、第3及び第4の実施形態に係る位相比較器14及び15を用いたPLL回路の安定性について考える。PLLの引き込みが完了した後は、第1の実施形態に係るPLL回路2と同様の動作になる。PLL回路2の位相余裕もPLL回路1と同様に74.8度である。従って、定常状態における位相比較器14及び15を用いたPLL回路の安定性は維持できている。

【0060】

続いて、位相比較器14及び15を用いたPLL回路の引き込み時について考える。位相比較器14を用いたPLL回路の引き込み時のオープンループゲインA2(s)は式(2)表せる。

A2(s)=Icp×F(s)×(Kvco/s)×(1/N)×(1/2) ・・・(2)

位相比較器14は、2分周回路を含むため、式(1)に対して分周数2で除算することで、式(2)を導き出すことができる。式(2)を用いて位相余裕を求めると64.6度となる。同様に、位相比較器15を用いたPLL回路のPLL引き込み時のオープンループゲインA3(s)は式(3)で表せる。

A3(s)=Icp×F(s)×(Kvco/s)×(1/N)×(1/8) ・・・(3)

位相比較器15では、8分周回路が追加されているため、分周数8で除算する。式(3)を用いて位相余裕を求めると39.9度となる。このように、分周数を増やすとPLL回路の安定性が低下することが分かる。位相比較器15を用いたPLL回路のシミュレーション結果では、PLLの引き込みは完了しているが、実際の回路の設計時においては安定性も考慮する必要がある。そのため、サイクルスリップを回避することによるPLL回路のロック時間の短縮とPLL回路の安定性の適切なバランスを考えることが必要となる。

【0061】

なお、引用した上記の特許文献等の各開示は、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素の多様な組み合わせないし選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

【符号の説明】

【0062】

1、2、3 PLL回路

10、11、12、12a〜12d、13、14、15 位相比較器

20 チャージポンプ

30 ループフィルタ

40 電圧制御発振器

50 分周回路

60 位相差判定ブロック

70 カウンタ

100〜105 2分周回路

C1、C2 容量

D01、D02 遅延素子

FF01〜FF27 フリップフロップ

INV01〜INV07 インバータ回路

NAND01〜NAND03 否定論理積回路

OR01〜OR10 論理和回路

R1 抵抗

【特許請求の範囲】

【請求項1】

位相比較器と、

前記位相比較器と接続されるチャージポンプと、を備えるPLL回路であって、

前記位相比較器は、

基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、前記チャージポンプの出力電圧を上昇させる第1のUP信号及び前記チャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、

前記基準クロックに同期させ、前記第1のUP信号に基づき前記チャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、

前記フィードバッククロックに同期させ、前記第1のDW信号に基づき前記チャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、

を含むことを特徴とするPLL回路。

【請求項2】

前記位相比較器は、動作許可信号を受け付け、前記動作許可信号に基づいて活性状態又は非活性状態が定まる請求項1のPLL回路。

【請求項3】

前記第1及び第2の保持回路は、フリップフロップにより構成される請求項1又は2のPLL回路。

【請求項4】

さらに、前記第1及び第2の保持回路は、n(但し、nは2以上の整数)段縦続接続されたフリップフロップを含み、n個の前記フリップフロップの各データ出力を前記チャージポンプの出力電圧を上昇させる第nのUP信号、又は、前記チャージポンプの出力電圧を下降させる第nのDW信号として出力する請求項1乃至3のいずれか一に記載のPLL回路。

【請求項5】

さらに、前記第1乃至第nのUP信号からいずれかを選択し、前記チャージポンプに出力する第1の選択回路と、前記第1乃至第nのDW信号からいずれかを選択し、前記チャージポンプに出力する第2の選択回路と、を含む請求項4のPLL回路。

【請求項6】

さらに、前記位相比較器をm(但し、mは2以上の整数)個含み、前記第1の位相比較器は、前記基準クロック及び前記フィードバッククロックを受け付け、前記第mの位相比較器は、前記基準クロックを2のm−1乗に分周したクロック及び前記フィードバッククロックを2のm−1乗に分周したクロックを受け付ける請求項1乃至5のいずれか一に記載のPLL回路。

【請求項7】

前記第1の位相比較器は、前記動作許可信号を受け付け、前記第2乃至第mの位相比較器は、基準クロックとフィードバッククロックの位相差が予め定めた閾値よりも小さくなると論理レベルが変化する信号に基づいて非活性状態となる請求項6のPLL回路。

【請求項8】

前記第1乃至第mの位相比較器の出力するUP信号からいずれかを選択し、前記チャージポンプに出力する第3の選択回路と、

前記第1乃至第mの位相比較器の出力するDW信号からいずれかを選択し、前記チャージポンプに出力する第4の選択回路と、

を備える請求項6又は7のPLL回路。

【請求項1】

位相比較器と、

前記位相比較器と接続されるチャージポンプと、を備えるPLL回路であって、

前記位相比較器は、

基準クロックを遅延させたクロック及びフィードバッククロックを遅延させたクロックに基づき、前記チャージポンプの出力電圧を上昇させる第1のUP信号及び前記チャージポンプの出力電圧を下降させる第1のDW信号を生成する制御信号生成回路と、

前記基準クロックに同期させ、前記第1のUP信号に基づき前記チャージポンプの出力電圧を上昇させる第2のUP信号を出力する第1の保持回路と、

前記フィードバッククロックに同期させ、前記第1のDW信号に基づき前記チャージポンプの出力電圧を下降させる第2のDW信号を出力する第2の保持回路と、

を含むことを特徴とするPLL回路。

【請求項2】

前記位相比較器は、動作許可信号を受け付け、前記動作許可信号に基づいて活性状態又は非活性状態が定まる請求項1のPLL回路。

【請求項3】

前記第1及び第2の保持回路は、フリップフロップにより構成される請求項1又は2のPLL回路。

【請求項4】

さらに、前記第1及び第2の保持回路は、n(但し、nは2以上の整数)段縦続接続されたフリップフロップを含み、n個の前記フリップフロップの各データ出力を前記チャージポンプの出力電圧を上昇させる第nのUP信号、又は、前記チャージポンプの出力電圧を下降させる第nのDW信号として出力する請求項1乃至3のいずれか一に記載のPLL回路。

【請求項5】

さらに、前記第1乃至第nのUP信号からいずれかを選択し、前記チャージポンプに出力する第1の選択回路と、前記第1乃至第nのDW信号からいずれかを選択し、前記チャージポンプに出力する第2の選択回路と、を含む請求項4のPLL回路。

【請求項6】

さらに、前記位相比較器をm(但し、mは2以上の整数)個含み、前記第1の位相比較器は、前記基準クロック及び前記フィードバッククロックを受け付け、前記第mの位相比較器は、前記基準クロックを2のm−1乗に分周したクロック及び前記フィードバッククロックを2のm−1乗に分周したクロックを受け付ける請求項1乃至5のいずれか一に記載のPLL回路。

【請求項7】

前記第1の位相比較器は、前記動作許可信号を受け付け、前記第2乃至第mの位相比較器は、基準クロックとフィードバッククロックの位相差が予め定めた閾値よりも小さくなると論理レベルが変化する信号に基づいて非活性状態となる請求項6のPLL回路。

【請求項8】

前記第1乃至第mの位相比較器の出力するUP信号からいずれかを選択し、前記チャージポンプに出力する第3の選択回路と、

前記第1乃至第mの位相比較器の出力するDW信号からいずれかを選択し、前記チャージポンプに出力する第4の選択回路と、

を備える請求項6又は7のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2012−217077(P2012−217077A)

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願番号】特願2011−81740(P2011−81740)

【出願日】平成23年4月1日(2011.4.1)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成24年11月8日(2012.11.8)

【国際特許分類】

【出願日】平成23年4月1日(2011.4.1)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]