PLL回路

【課題】低消費電力のPLL回路を提供する。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

【解決手段】位相比較回路11は、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(UP信号とDN信号)をチャージポンプ12に供給し、バイアス回路16は、チャージポンプ12にバイアス電流を供給し、制御回路17は、2種の位相差信号のうち一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、2種の位相差信号の両方が非活性化状態のときに、バイアス回路16を停止させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PLL(Phase-locked loop)回路に関する。

【背景技術】

【0002】

携帯機器の電池寿命を延ばすことなどを目的として、半導体集積回路の低消費電力化の要求が高まっている。PLL回路は、周波数シンセサイザとして用いられ、大部分のSOC(System-On-a-Chip)製品に搭載されている。

【0003】

PLL回路は、チャージポンプなどに対しバイアス電流を供給するバイアス回路を含み、その消費電流を削減することが求められている。

消費電流削減のため、フィードバック信号と基準信号の同期を検出(ロック検出)するロック検出回路を設け、ロック検出後に、バイアス回路を、位相を比較するタイミングにおいてイネーブルさせ、それ以外はディスイネーブルさせるPLL回路が知られている。

【0004】

なお、バイアス回路(基準電圧回路・基準電流回路)を間欠的に動作させる際に、起動を速める方法として、基準電圧を容量素子に保持させる技術が知られている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特表2003−529246号

【特許文献2】特開2011−8683号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、従来のPLL回路では、製造条件のばらつきなどで、ロック検出回路がロック検出を正しく行えないと、不要なタイミングでバイアス回路をイネーブルさせてしまい、十分な低消費電力化が図れない場合があった。

【課題を解決するための手段】

【0007】

発明の一観点によれば、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号をチャージポンプに供給する位相比較回路と、前記チャージポンプにバイアス電流を供給するバイアス回路と、前記2種の位相差信号のうち一方または両方が活性化状態のときに前記バイアス回路の動作を行わせ、前記2種の位相差信号の両方が非活性化状態のときに、前記バイアス回路を停止させる制御回路と、を備えたPLL回路が提供される。

【発明の効果】

【0008】

開示のPLL回路によれば、チャージポンプが動作するタイミング以外でのバイアス電流の供給を抑制でき、効率的に消費電力の削減が可能となる。

【図面の簡単な説明】

【0009】

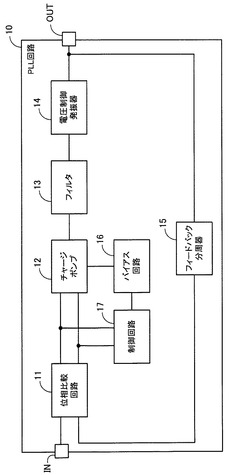

【図1】第1の実施の形態のPLL回路の一例を示す図である。

【図2】バイアス回路及び制御回路の一例を示す図である。

【図3】バイアス回路の他の例を示す図である。

【図4】第1の実施の形態のPLL回路の動作例を示すタイミングチャートである。

【図5】バイアス電流の立ち上がり期間を考慮したPLL回路の一部を示す図である。

【図6】図5の回路の動作例を示すタイミングチャートである。

【図7】チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。

【図8】図7の回路の動作例を示すタイミングチャートである。

【図9】バイアス電流の立ち上がり期間と、チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。

【図10】図9の回路の動作例を示すタイミングチャートである。

【図11】第2の実施の形態のPLL回路の一例を示す図である。

【図12】バイアス回路の一例を示す図である。

【図13】バイアス回路の他の例を示す図である。

【図14】第3の実施の形態のPLL回路の一例を示す図である。

【図15】第4の実施の形態のPLL回路の一例を示す図である。

【図16】第4の実施の形態のPLL回路の動作の一例を示すタイミングチャートである。

【図17】バイアス回路の他の例を示す図である。

【図18】バイアス回路の他の例を示す図である。

【図19】第5の実施の形態のPLL回路の一例を示す図である。

【図20】PLL回路の動作開始時の動作の一例を示すタイミングチャートである。

【図21】PLL回路の動作中に基準電圧に異常が生じた場合の動作例を示すタイミングチャートである。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態を、図面を参照しつつ説明する。

(第1の実施の形態)

図1は、第1の実施の形態のPLL回路の一例を示す図である。

【0011】

PLL回路10は、位相比較回路11、チャージポンプ12、フィルタ13、電圧制御発振器14、フィードバック分周器15、バイアス回路16、制御回路17を有している。

【0012】

位相比較回路11は、入力端子INから入力される基準信号と、フィードバック分周器15から出力されるフィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(以下UP信号とDN信号と呼ぶ)をチャージポンプ12に供給する。位相比較回路11は、基準信号の遷移がフィードバック信号の遷移よりも前に起こる場合には、UP信号を活性状態とし、基準信号の遷移がフィードバック信号の遷移よりも後に起こる場合には、DN信号を活性状態とする。

【0013】

チャージポンプ12は、UP信号とDN信号に応じて、チャージポンプ電流を生成する。

フィルタ13は、チャージポンプ電流をフィルタリングして、制御電圧を生成し電圧制御発振器14に供給する。

【0014】

電圧制御発振器14は、制御電圧に応じて出力信号の発振周波数を調整し、調整した出力信号を出力端子OUTから出力するとともに、フィードバック分周器15に供給する。

フィードバック分周器15は、電圧制御発振器14の出力信号の周波数を任意の整数比で分周する。なお、周波数の逓倍が不要な場合には、フィードバック分周器15はなくてもよい。

【0015】

バイアス回路16は、チャージポンプ12に対して、チャージポンプ電流を生成させるためのバイアス電流を供給する。

制御回路17は、UP信号とDN信号のうち、一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、UP信号とDN信号の両方が非活性化状態のときに、バイアス回路16を停止させる。なお、以下に示す例では、信号レベルが“1”(またはH(High)レベル)の場合を活性化状態、“0”(またはL(Low)レベル)の場合を非活性化状態として説明するが、“0”の場合を活性化状態、“1”の場合を非活性化状態としてもよい。

【0016】

図2は、バイアス回路及び制御回路の一例を示す図である。

バイアス回路16は、電流源20、スイッチ21,22、nチャネル型MOSFET(Metal-Oxide Semiconductor Field Effect Transistor)(以下nMOSと略す)23,24を有する。

【0017】

nMOS23のドレインはスイッチ21を介して、チャージポンプ12に接続されており、ソースは接地されている。また、nMOS23のゲートはnMOS24のゲートに接続されている。nMOS24のゲートはさらに、nMOS24のドレインに接続されている。nMOS24のドレインはスイッチ22を介して電流源20に接続されており、ソースは接地されている。スイッチ21,22は制御回路17からの制御信号によりオンまたはオフする。

【0018】

このようなバイアス回路16は、カレントミラーの機能を有し、スイッチ21,22のオン時には、電流源20で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0019】

制御回路17は、OR回路25を有している。位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が“1”の場合に、“1”を出力し、UP信号とDN信号の両方が“0”の場合に、“0”を出力する。すなわち、OR回路25は、UP信号とDN信号のうち、一方または両方が活性化状態のときに“1”を出力し、UP信号とDN信号の両方が非活性化状態のときに、“0”を出力する。

【0020】

図2のバイアス回路16及び制御回路17の例では、スイッチ21,22は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0021】

これにより、バイアス回路16は、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12にバイアス電流を供給する。そして、バイアス回路16は、UP信号とDN信号の両方が非活性化状態の場合には、動作を停止する。これにより、チャージポンプ12へのバイアス電流の供給が遮断される。

【0022】

なお、図2のバイアス回路16では、nMOS23,24が用いられているが、これに限定されず、pチャネル型MOSFET(以下pMOSと略す)を用いるようにしてもよい。

【0023】

図3は、バイアス回路の他の例を示す図である。

図3に示されるバイアス回路16aは、pMOS26,27、スイッチ28,29、電流源30を有している。

【0024】

pMOS26のドレインはスイッチ28を介して、チャージポンプ12に接続されており、ソースは電源に接続されている。また、pMOS26のゲートは、pMOS27のゲートに接続されている。pMOS27のゲートはさらにpMOS27のドレインに接続されている。pMOS27のドレインはスイッチ29を介して電流源30に接続されており、ソースは電源と接続されている。スイッチ28,29は制御回路17からの制御信号によりオンまたはオフする。

【0025】

このようなバイアス回路16aも、図2のバイアス回路16と同様に、カレントミラーの機能を有し、スイッチ28,29のオン時には、電流源30で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0026】

図3のバイアス回路16a及び制御回路17の例でも、スイッチ28,29は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0027】

これにより、バイアス回路16aは、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12にバイアス電流を供給する。そして、バイアス回路16aは、UP信号とDN信号の両方が非活性化状態の場合には、動作を停止する。これにより、チャージポンプ12へのバイアス電流の供給が遮断される。

【0028】

以下、第1の実施の形態のPLL回路10の動作の一例を、タイミングチャートを用いて説明する。

図4は、第1の実施の形態のPLL回路の動作例を示すタイミングチャートである。

【0029】

図4では、上から、基準信号である入力クロック(CK)、フィードバック信号(FB)、UP信号(UP)、DN信号(DN)が示されている。また、制御回路17から出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。

【0030】

CKがHレベルに立ち上がる時刻t1では、FBはLレベルのままであり、時刻t2になって、FBは、Hレベルに立ち上がる。すなわち、FBの位相は、基準信号であるCKの位相と比べて遅れている。

【0031】

そのため、位相比較回路11は、時刻t1において、UPをHレベルに立ち上げ、活性化状態とする。これにより、バイアスイネーブルもHレベルに立ち上がり、Ibiasが流れ、チャージポンプ12は、Icpを流し始める。

【0032】

時刻t2でFBがHレベルに立ち上がると、位相比較回路11は、時刻t3まではUPとDNの両方とも活性化状態とする。これは、位相比較回路11の「UP/DN信号のパルス幅 対 位相差」特性において、位相差が0付近に不感帯が生じるのを防ぐためであり、わずかな時間、UPとDNが両方、活性化状態とするようにしている。時刻t2と時刻t3の間は、UPとDNによって生じた電流が、チャージポンプ12内部で相殺されるので、図4に示されているように、この時間のIcpは0となっている。

【0033】

次に、時刻t4では、FBが立ち上がり、その後、時刻t5にてCKが立ち上がっている。すなわち、FBの位相は、基準信号であるCKの位相と比べて進んでいる。

そのため、位相比較回路11は、時刻t4において、DNをHレベルに立ち上げ、活性化状態とする。これにより、バイアスイネーブルも立ち上がり、Ibiasが流れ、チャージポンプ12は、負のIcpを流し始める。

【0034】

なお、時刻t5から時刻t6までは、上述と同様の理由で、UPとDNが両方活性化状態となっており、このときIcpは0となっている。

以上のように、UPまたはDNが活性化状態になっているタイミングで、チャージポンプ12が動作してIcpが流れる。

【0035】

本実施の形態のPLL回路10では、UP信号またはDN信号の一方または両方が活性化状態のときに、バイアス回路を動作させ、それ以外では停止させバイアス電流を遮断する。これにより、チャージポンプ12が動作するタイミング以外でのバイアス電流の供給を抑制でき、効率的に消費電力の削減が可能となる。

【0036】

ところで、制御回路17からの制御信号によって、バイアス回路16が動作を開始してからバイアス電流が立ち上がるまでに時間がかかる場合や、バイアス電流が立ち上がるときにノイズが発生すると、チャージポンプ12の動作に影響を与える可能性がある。それを抑制するために、たとえば、以下のような回路をさらに設けるようにしてもよい。

【0037】

図5は、バイアス電流の立ち上がり期間を考慮したPLL回路の一部を示す図である。図1と同様の要素については同一符号を付している。

図5に示されているように、位相比較回路11とチャージポンプ12の間に、遅延素子(バッファ)41,42を有する遅延回路40が設けられている。たとえば、遅延素子41は、位相比較回路11が出力するUP信号を遅延させてチャージポンプ12に供給し、遅延素子42は、位相比較回路11が出力するDN信号を遅延させてチャージポンプ12に供給する。遅延回路40の遅延量は、たとえば、バイアス電流の立ち上がり時に、バイアス電流が、一定の電流に安定するまでの時間、UP信号及びDN信号を遅延させるように設定される。

【0038】

制御回路17aのOR回路25aは、遅延前後のUP信号及びDN信号を入力して、それらの信号の論理和を制御信号(バイアスイネーブル)として、バイアス回路16に出力する。

【0039】

図6は、図5の回路の動作例を示すタイミングチャートである。

図6では、上から、遅延前のUP信号(UP1)、遅延後のUP信号(UP2)、制御回路17aから出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。なお、図6では、説明を簡単にするため、UP信号だけが活性化状態となる場合が示されている。

【0040】

時刻t1でUP1が立ち上がると、制御回路17aは、バイアスイネーブルをHレベルとし、バイアス回路16の動作を開始させる。これにより、Ibiasが立ち上がり始める。このとき、UP2は、Lレベルのままであるので、チャージポンプ12は、Icpを流さない。

【0041】

Ibiasが一定の電流値に立ち上がり、時刻t2で、UP2がHレベルに立ち上がると、チャージポンプ12は、Icpを流し始める。

時刻t3において、UP1がLレベルに立ち下がると、制御回路17aは、UP2がHレベルのままであるので、Hレベルのバイアスイネーブルをバイアス回路16に供給し続ける。

【0042】

時刻t4において、UP2がLレベルに立ち下がると、制御回路17aは、バイアスイネーブルをLレベルに立ち下げる。これにより、バイアス回路16から出力されるIbiasは0に下がっていく。また、チャージポンプ12はIcpを立ち下げる。

【0043】

以上のように、図5に示したPLL回路では、遅延回路40を設け、チャージポンプ12に入力されるUP信号及びDN信号を遅らせ、制御回路17aは、チャージポンプ12がチャージポンプ電流を流し始める前に、バイアス回路の動作を開始させている。

【0044】

これにより、PLL回路は、前述したような効率的に消費電力の削減が可能となるという効果のほかに、立ち上がり時の不安定なバイアス電流によるチャージポンプ12の誤作動を抑制できる、という効果をさらに有する。

【0045】

ところで、チャージポンプ12内の遅延により、UP信号及びDN信号が両方とも非活性化状態となっても、チャージポンプ電流が直ちに立ち下がらない場合がある。チャージポンプ電流の精度を保つため、バイアス電流は、チャージポンプ電流が流れている間は、チャージポンプ12に供給されていることが望ましい。

【0046】

図7は、チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。図1と同様の要素については同一符号を付している。

制御回路17bは、UP信号とDN信号を遅延する遅延回路43を有し、OR回路25bは、遅延前後のUP信号及びDN信号を入力し、その論理和をバイアス回路16に制御信号(バイアスイネーブル)として出力する。

【0047】

遅延回路43は、遅延素子(バッファ)43a,43bを有し、たとえば、遅延素子43aは、位相比較回路11が出力するUP信号を遅延させ、遅延素子43bは、位相比較回路11が出力するDN信号を遅延させる。遅延回路43の遅延量は、たとえば、UP信号及びDN信号の遅延時間が、チャージポンプ12の内部の遅延時間と同程度、もしくはそれ以上になるように設定される。

【0048】

なお、図7の例では、遅延回路43を制御回路17bに含めているが、制御回路17bとは別の回路ブロックとしてもよい。

図8は、図7の回路の動作例を示すタイミングチャートである。

【0049】

図8では、上から、遅延前のUP信号(UP1)、遅延後のUP信号(UP2)、制御回路17bから出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。なお、図8では、説明を簡単にするため、UP信号だけが活性化状態となる場合が示されている。

【0050】

時刻t1でUP1が立ち上がると、制御回路17bは、バイアスイネーブルをHレベルとし、バイアス回路16の動作を開始させる。これにより、Ibiasが立ち上がり始める。ただし、チャージポンプ12は、内部の遅延により、時刻t2になるまでは、Icpを流し始めない。図8の例の場合、時刻t1から時刻t2までの時間が、チャージポンプ12の遅延時間となる。

【0051】

時刻t2になると、チャージポンプ12は、Ibiasに基づいてIcpを出力し始める。UP2は、時刻t1から、遅延回路43による遅延時間経過後の時刻t3でHレベルに立ち上がる。

【0052】

時刻t4において、UP1がLレベルになっても、UP2がHレベルのままであるので、制御回路17bは、Hレベルのバイアスイネーブルをバイアス回路16に供給し続ける。また、UP1がLレベルに立ち下がっても、チャージポンプ12は、内部の遅延により、時刻t5になるまでは、Icpの出力を続ける。図8の例の場合、時刻t4から時刻t5までの時間が、Icpを立ち下げる際のチャージポンプ12の遅延時間となる。

【0053】

時刻t6で、UP2がLレベルに立ち下がると、バイアスイネーブルはLレベルに立ち下がり、Ibiasは下がり始める。

以上のように図7に示すようなPLL回路によれば、前述したように効率的に消費電力の削減が可能となるとともに、遅延により、チャージポンプ電流が直ちに立ち下がらない場合でも、チャージポンプ12に一定期間バイアス電流を供給し続けられる。これにより、チャージポンプ12の誤動作を抑制できる。

【0054】

なお、図5に示したPLL回路と、図7に示したPLL回路とを以下のように組み合わせることもできる。

図9は、バイアス電流の立ち上がり期間と、チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。図5と図7に示したものと同様の要素については同一符号を付している。

【0055】

図9に示されるPLL回路では、図5に示した遅延回路40と、図7に示した制御回路17bとが組み合わされている。遅延回路40で遅延されたUP信号とDN信号が、制御回路17bの遅延回路43で、さらに遅延されてOR回路25bに入力されるような回路となっている。

【0056】

図10は、図9の回路の動作例を示すタイミングチャートである。

図10では、上から、遅延前のUP信号(UP1)、遅延回路40で遅延後のUP信号(UP2)、遅延回路43で遅延後のUP信号(UP3)が示されている。さらに、制御回路17bから出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。なお、図10では、説明の簡略化のため、UP信号だけが活性化状態となる場合が示されている。

【0057】

時刻t1でUP1が立ち上がると、制御回路17bは、バイアスイネーブルをHレベルとし、バイアス回路16の動作を開始させる。これにより、Ibiasが立ち上がり始める。このとき、UP2は、Lレベルのままであるので、チャージポンプ12は、Icpを流さない。

【0058】

Ibiasが一定の電流値に立ち上がり、時刻t2で、UP2がHレベルに立ち上がると、チャージポンプ12は、チャージポンプ12内による遅延時間経過後の時刻t3にて、Icpを流し始める。

【0059】

UP3は、時刻t2から遅延回路43による遅延時間経過後の時刻t4で、Hレベルに立ち上がる。

時刻t5において、UP1がLレベルに立ち下がると、制御回路17bは、UP3がHレベルのままであるので、Hレベルのバイアスイネーブルをバイアス回路16に供給し続ける。

【0060】

時刻t6において、UP2がLレベルに立ち下がると、チャージポンプ12は、内部の遅延により、時刻t7になるとIcpを遮断し始める。

時刻t8において、UP3がLレベルに立ち下がると、制御回路17bは、バイアスイネーブルをLレベルに立ち下げる。これにより、バイアス回路16から出力されるIbiasは0に下がっていく。

【0061】

図9に示したPLL回路によれば、前述したように効率的に消費電力の削減が可能になるとともに、立ち上がり時の不安定なバイアス電流や、遅延によりチャージポンプ電流が直ちに立ち下がらないことによるチャージポンプ12の誤動作を抑制できる。

【0062】

なお、図6、図8、図10では、UP信号だけが活性化状態となる場合について説明したが、DN信号だけが活性化状態となる場合、またはUP信号とDN信号が両方活性化状態となる場合についても同様の動作が行われる。

【0063】

(第2の実施の形態)

図11は、第2の実施の形態のPLL回路の一例を示す図である。図1に示した第1の実施の形態のPLL回路10と同様の要素については同一符号を付し、説明を省略する。

【0064】

第2の実施の形態のPLL回路10aは、電圧制御発振器14が、バイアス回路50で生成されるバイアス電流を用いる回路ブロックである場合に対応したものである。

すなわち、PLL回路10aは、図1に示したPLL回路10と異なり、チャージポンプ12のみならず、電圧制御発振器14にもバイアス電流を供給するバイアス回路50を有している。

【0065】

バイアス回路50は、基準電圧・バイアス電流生成部51、スイッチ52、容量素子53、バイアス電流生成部54を有している。

基準電圧・バイアス電流生成部51は、バイアス電流を生成するための基準電圧を生成するとともに、チャージポンプ12に供給するバイアス電流を生成する。

【0066】

スイッチ52は、制御回路17からの制御信号によってオンオフが制御される。

容量素子53は、基準電圧・バイアス電流生成部51で生成された基準電圧を保持する。

【0067】

バイアス電流生成部54は、容量素子53に保持される基準電圧に基づいて、バイアス電流を生成し、電圧制御発振器14に供給する。

図12は、バイアス回路の一例を示す図である。

【0068】

バイアス回路50において、基準電圧・バイアス電流生成部51は、電流源60、スイッチ61,62、nMOS63,64を有する。

nMOS63のドレインはスイッチ61を介して、チャージポンプ12に接続されており、ソースは接地されている。また、nMOS63のゲートはnMOS64のゲートに接続されている。nMOS64のゲートはさらに、nMOS64のドレインに接続されている。nMOS64のドレインはスイッチ62を介して電流源60に接続されており、ソースは接地されている。スイッチ61,62は制御回路17からの制御信号によりオンまたはオフする。

【0069】

このような基準電圧・バイアス電流生成部51は、カレントミラーの機能を有し、スイッチ61,62のオン時には、電流源60で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0070】

また、スイッチ52の一方の端子は、nMOS63,64のゲートに接続されており、スイッチ52のオン時には、nMOS63,64のゲート電圧が基準電圧として、容量素子53に保持される。

【0071】

バイアス電流生成部54は、nMOS65を有している。nMOS65のゲートは、スイッチ52の他方の端子及び容量素子53の一方の端子に接続されている。nMOS65のドレインは、電圧制御発振器14に接続されており、ソースは接地されている。

【0072】

バイアス電流生成部54は、スイッチ52がオン時には、基準電圧・バイアス電流生成部51との間でカレントミラーとして機能し、チャージポンプ12に供給されるバイアス電流と同じ電流を、電圧制御発振器14に供給する。スイッチ52がオフ時には、バイアス電流生成部54は、容量素子53に保持された基準電圧によりnMOS65はオン状態を保ち、電圧制御発振器14にバイアス電流を供給し続ける。

【0073】

図12のバイアス回路50の例では、スイッチ52,61,62は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0074】

これにより、バイアス回路50は、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12及び電圧制御発振器14にバイアス電流を供給する。そして、バイアス回路50は、UP信号とDN信号の両方が非活性化状態の場合には、チャージポンプ12へのバイアス電流の供給を停止する。しかし、バイアス回路50は、電圧制御発振器14に対しては、バイアス電流の供給を引き続き行うことができる。

【0075】

上記のようなバイアス回路50の代わりに、以下に示すようなpMOSを用いたバイアス回路を適用してもよい。

図13は、バイアス回路の他の例を示す図である。

【0076】

図13に示されるバイアス回路50aにおいて、基準電圧・バイアス電流生成部51aは、pMOS70,71、スイッチ72,73、電流源74を有している。

pMOS70のドレインはスイッチ72を介して、チャージポンプ12に接続されており、ソースは電源に接続されている。また、pMOS70のゲートは、pMOS71のゲートに接続されている。pMOS71のゲートはさらにpMOS71のドレインに接続されている。pMOS71のドレインはスイッチ73を介して電流源74に接続されており、ソースは電源と接続されている。スイッチ72,73は制御回路17からの制御信号によりオンまたはオフする。

【0077】

このような基準電圧・バイアス電流生成部51aは、カレントミラーの機能を有し、スイッチ72,73のオン時には、電流源74で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0078】

また、スイッチ52の一方の端子は、pMOS70,71のゲートに接続されており、スイッチ52のオン時には、pMOS70,71のゲート電圧が基準電圧として、容量素子53に保持される。なお、容量素子53は、一方の端子をスイッチ52とバイアス電流生成部54a間のノードに接続し、他方の端子を電源に接続している。

【0079】

バイアス電流生成部54aは、pMOS75を有している。pMOS75のゲートは、スイッチ52の他方の端子及び容量素子53の一方の端子に接続されている。pMOS75のドレインは、電圧制御発振器14に接続されており、ソースは電源に接続されている。

【0080】

バイアス電流生成部54aは、スイッチ52がオン時には、基準電圧・バイアス電流生成部51aとの間でカレントミラーとして機能し、チャージポンプ12に供給されるバイアス電流と同じ電流を、電圧制御発振器14に供給する。スイッチ52がオフ時には、バイアス電流生成部54aは、容量素子53に保持された基準電圧によりpMOS75はオン状態を保ち、電圧制御発振器14にバイアス電流を供給し続ける。

【0081】

図13のバイアス回路50aの例でも、スイッチ52,72,73は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0082】

これにより、バイアス回路50aは、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12及び電圧制御発振器14にバイアス電流を供給する。そして、バイアス回路50aは、UP信号とDN信号の両方が非活性化状態の場合には、チャージポンプ12へのバイアス電流の供給を停止する。しかし、バイアス回路50aは、電圧制御発振器14に対しては、バイアス電流の供給を引き続き行うことができる。

【0083】

なお、図12、図13のバイアス回路50,50aにおいて、容量素子53で保持された基準電圧は、スイッチ52がオフの場合には、リークによって変動する。しかし、前述したように、位相比較回路11は、入力される基準信号(入力クロック)とフィードバック信号の位相差が0であっても、わずかな期間、UP信号とDN信号を両方、活性化状態とするので、入力クロックの周期で、スイッチ52はオンする。これにより、容量素子53で保持される基準電圧は、入力クロックの周期で補正される。

【0084】

ただし、容量素子53で保持される基準電圧の変動が、UP信号またはDN信号のパルス幅の時間で補正できるように設計をすることが望ましい。

基準電圧の変動をΔVとすると、スイッチ52を閉じることで、nMOS64のゲート電位も、ΔV変化する(説明を簡単にするため、nMOS63〜65のゲート容量と、スイッチ52のON抵抗は無視する)。このとき、nMOS64のトランスコンダクタンスをgmとすると、nMOS64のドレイン電流はgmΔV減少する。nMOS64のドレイン電流が減少する代わりに、容量素子53には、gmΔVの大きさの電流が流入する。以上の原理から、容量素子53を充電する際の時定数C/gmが、UP信号またはDN信号の最小のパルス幅の時間より充分小さく(たとえば、1/3以下)になるように、容量値Cを決定することが望ましい。

【0085】

なお、外乱などの要因で、あるタイミングにおけるUP信号またはDN信号のパルス幅の時間では補正できないほど、基準電圧が変動したとする。その場合、基準電圧の変動によって出力クロックが変動し、入力クロックとフィードバック信号の位相差が広がることで、UP信号またはDN信号のパルス差が広くなり、容量素子53で保持される基準電圧は補正される。つまり、基準電圧が外乱などの影響で変動したとしても、PLL回路10aのフィードバックの効果によって、基準電圧は補正される。

【0086】

以上のような第2の実施の形態のPLL回路10aによれば、第1の実施の形態のPLL回路10と同様に効率的に消費電力の削減が行えるとともに、バイアス電流を常に用いる回路ブロックには、バイアス電流を供給し続けることができる。

【0087】

なお、バイアス電流を常に用いる回路ブロックとして、上記の例では、電圧制御発振器14を挙げたがこれに限定されない。回路構成によって、バイアス電流を常時使用する回路ブロックがPLL回路内にある場合には、その回路ブロックに対して本実施のバイアス回路から、容量素子に保持された基準電圧に基づくバイアス電流を供給すればよい。

【0088】

なお、第2の実施の形態のPLL回路10aに対して、図5〜図10に示したように、遅延回路40,43を設けて、各信号の立ち上がりや立ち下がりタイミングを調整するようにしてもよい。

【0089】

(第3の実施の形態)

図14は、第3の実施の形態のPLL回路の一例を示す図である。図11に示した第2の実施の形態のPLL回路10aと同様の要素については同一符号を付し、説明を省略する。

【0090】

第3の実施の形態のPLL回路10bでは、バイアス回路80が、第2の実施の形態のPLL回路10aと異なっている。

バイアス回路80は、基準電圧生成部81、スイッチ82、容量素子83、バイアス電流生成部84を有している。

【0091】

基準電圧生成部81は、たとえば、図12に示したような電流源60やスイッチ62などを有しており、UP信号とDN信号の一方または両方が活性化状態の際に、バイアス電流を生成するための基準電圧を出力する。

【0092】

スイッチ82は、制御回路17からの制御信号によってオンオフが制御される。UP信号とDN信号の一方または両方が活性化状態の際には、スイッチ82はオンし、UP信号とDN信号の両方が非活性化状態の際には、スイッチ82はオフする。

【0093】

容量素子83は、基準電圧生成部81で生成された基準電圧を保持する。

バイアス電流生成部84は、容量素子83に保持される基準電圧に基づいて、バイアス電流を生成し、チャージポンプ12と電圧制御発振器14に供給する。また、バイアス電流生成部84は、チャージポンプ12に対して、バイアス電流を供給するか否かを切り替えるスイッチを有している。そのスイッチは、制御回路17からの制御信号によってオンオフが制御される。UP信号とDN信号の一方または両方が活性化状態の際には、そのスイッチはオンしてチャージポンプ12にバイアス電流を供給する。UP信号とDN信号の両方が非活性化状態の際には、そのスイッチはオフして、チャージポンプ12へのバイアス電流の供給を遮断する。

【0094】

このようなPLL回路10bでも、第2の実施の形態のPLL回路10aと同様の効果が得られる。

なお、第3の実施の形態のPLL回路10bに対して、図5〜図10に示したように、遅延回路40,43を設けて、各信号の立ち上がりや立ち下がりタイミングを調整するようにしてもよい。

【0095】

さらに、チャージポンプ12に高精度のバイアス電流を供給し、かつ、電圧制御発振器14にもノイズの少ないバイアス電流を供給するために、以下のようなPLL回路を適用することもできる。

【0096】

(第4の実施の形態)

図15は、第4の実施の形態のPLL回路の一例を示す図である。

図15では、PLL回路10cの一部を示している。図示を省略した部分は、前述のPLL回路10,10a,10bと同様である。なお、PLL回路10,10a,10bと同様の要素については同一符号を付し、説明を省略する。

【0097】

第4の実施の形態のPLL回路10cは、位相比較回路11とチャージポンプ12の間に設けられた遅延回路90を有している。

遅延回路90は、位相比較回路11から出力されるUP信号を遅延させる遅延素子91,92,93と、DN信号を遅延させる遅延素子94,95,96を有している。

【0098】

制御回路100は、OR回路101,102,103と遅延回路110を有している。遅延回路110は、遅延素子93で遅延されたUP信号をさらに遅延させてOR回路103に入力する遅延素子111と、遅延素子96で遅延されたDN信号をさらに遅延させてOR回路103に入力する遅延素子112を有している。

【0099】

なお、図15の例では、遅延回路110を制御回路100に含めているが、制御回路100とは別の回路ブロックとしてもよい。

OR回路101は、遅延回路90による遅延前のUP信号とDN信号と、OR回路102の出力信号を入力し、これらの信号の論理和を出力する。OR回路102は、遅延素子91,94で遅延されたUP信号とDN信号と、OR回路103の出力信号を入力し、これらの信号の論理和を出力する。OR回路103は、遅延素子92,95で遅延されたUP信号とDN信号と、遅延素子111,112で遅延されたUP信号とDN信号とを入力し、これらの信号の論理和を出力する。

【0100】

バイアス回路120は、第2及び第3の実施の形態のPLL回路10a,10bのバイアス回路50,80と同様に、チャージポンプ12と電圧制御発振器14にバイアス電流を供給する機能を有しているが、以下のような各要素を有する。

【0101】

すなわち、バイアス回路120は、電流源121、スイッチ122,123,124,125、nMOS126,127,128、容量素子129,130を有する。

スイッチ122,123は、制御回路100から出力される制御信号のうち、OR回路101の出力信号によりオンオフ制御される。スイッチ124は、制御回路100から出力される制御信号のうち、OR回路102の出力信号によりオンオフ制御される。また、スイッチ125は、制御回路100から出力される制御信号のうち、OR回路103の出力信号によりオンオフ制御される。スイッチ122〜125は、たとえば、nMOSであり、そのゲートにOR回路101〜103から“1”が入力されるとオン状態となり、“0”が入力されるとオフ状態となる。

【0102】

スイッチ122は、電流源121とnMOS126のドレインとの間に設けられている。スイッチ123は、nMOS127のドレインとチャージポンプ12との間に設けられている。スイッチ124は、nMOS126のドレイン−ゲート間に接続されている。スイッチ125は、nMOS126とnMOS127のゲートの間に接続されている。

【0103】

また、nMOS127のゲートはnMOS128のゲートに接続されており、nMOS128のドレインは、電圧制御発振器14に接続されている。nMOS126〜128のソースは接地されている。

【0104】

また、容量素子129の一方の端子は、nMOS126のゲートとスイッチ125間に接続されている。容量素子130の一方の端子は、nMOS127のゲートとスイッチ125間に接続されている。容量素子129,130の他方の端子は接地されている。

【0105】

このようなバイアス回路120では、電流源121を含む基準電圧を発生する回路部と、容量素子129がスイッチ124を介して接続されており、スイッチ122がオン状態のとき、スイッチ124がオン状態となると、容量素子129が充電され、基準電圧が保持される。その後、スイッチ125がオン状態となると、容量素子130が充電されることになる。

【0106】

図16は、第4の実施の形態のPLL回路の動作の一例を示すタイミングチャートである。

遅延前のUP信号(UP1)、遅延素子91で遅延後のUP信号(UP2)、遅延素子92でさらに遅延されたUP信号(UP3)、遅延素子93でさらに遅延されたUP信号(UP4)、遅延素子111でさらに遅延されたUP信号(UP5)が示されている。また、OR回路101の出力信号(バイアスイネーブル1)、OR回路102の出力信号(バイアスイネーブル2)、OR回路103の出力信号(バイアスイネーブル3)が示されている。また、nMOS126のドレイン電圧(V1)、nMOS126のソース電流(I1)、nMOS126のゲート電圧(V2)、nMOS127のゲート電圧(V3)が示されている。さらに、電圧制御発振器14に供給されるバイアス電流(Ibias1)、チャージポンプ12に供給されるバイアス電流(Ibias2)、チャージポンプ電流(Icp)が示されている。

【0107】

なお、図16では、説明の簡略化のため、UP信号だけが活性化状態となる場合が示されている。

時刻t0では、UP1〜UP5、バイアスイネーブル1〜3はLレベルであるものとする。また、V2,V3は、容量素子129,130に保持されている電圧による0以上の一定値(Hレベル)を示しているものとする。

【0108】

これにより、スイッチ122〜125は全てオフ状態で、nMOS126はオン状態であるため、V1もLレベル、I1、Ibias2、Icpも0となっている。また、V3がHレベルであることにより、nMOS128がオンしており、Ibias1が電圧制御発振器14に供給されている。

【0109】

時刻t1でUP1が立ち上がると、OR回路101による遅延後の時刻t2においてバイアスイネーブル1がHレベルに立ち上がる。これにより、スイッチ122がオンし、V1、I1が立ち上がり始め、その後、一定値となる。また、スイッチ123もオンし、容量素子130に保持されている基準電圧によってIbias2も立ち上がる。基準電圧を保持する容量素子130を設けていることによって、Ibias2は素早く立ち上がる。

【0110】

時刻t3でUP2が立ち上がると、OR回路102による遅延後の時刻t4においてバイアスイネーブル2がHレベルに立ち上がる。これにより、スイッチ124がオンし、電流源121の電流により容量素子129に保持されている電荷のリーク分が補填され、V2が補正される。

【0111】

時刻t5でUP3が立ち上がると、OR回路103による遅延後の時刻t6においてバイアスイネーブル3がHレベルに立ち上がる。これにより、スイッチ125がオンし、電流源121の電流により容量素子130に保持されている電荷のリーク分が補填され、V3が補正される。これにより、電圧制御発振器14に供給されるバイアス電流であるIbias1、チャージポンプ12に供給されるバイアス電流であるIbias2も補正される。

【0112】

このとき、容量素子129に基準電圧が保持されているため、電圧の変動を抑えることができる。

時刻t7でUP4が立ち上がると、チャージポンプ12は、Icpを流し始める。その後、時刻t8でUP5が立ち上がるが、バイアスイネーブル3は、Hレベルのままである。

【0113】

その後、UP1〜UP3が順にLレベルに立ち下がり、時刻t9でUP4がLレベルに立ち下がると、Icpは立ち下がるが、UP5はHレベルのままであるので、OR回路103の出力信号であるバイアスイネーブル3はHレベルのままとなる。これにより、OR回路103の出力信号を入力するOR回路102の出力信号であるバイアスイネーブル2もHレベルを維持し、OR回路102の出力信号を入力するOR回路101の出力信号であるバイアスイネーブル1もHレベルを維持する。そのため、スイッチ122〜125もオン状態のままであり、チャージポンプ12及び電圧制御発振器14に対して、バイアス電流(Ibias2,Ibias1)が供給され続ける。

【0114】

時刻t10でUP5が立ち下がると、OR回路103による遅延後の時刻t11においてバイアスイネーブル3がLレベルに立ち下がり、これを受けてバイアスイネーブル2、バイアスイネーブル1が順にLレベルに立ち下がる。これにより、スイッチ125、スイッチ124が順にオフ状態となり、最後にスイッチ122,123がオフ状態となる。

【0115】

このような順序でスイッチ122〜125をオフ状態にしていくことで、容量素子130に保持される基準電圧が大きく変動することを抑えられる。

時刻t12でバイアスイネーブル1がLレベルに立ち下がると、スイッチ123はオフ状態となるので、Ibias2は立ち下がる。Ibias1は、容量素子130に保持される電圧によって、電圧制御発振器14に供給され続ける。

【0116】

以上のように、遅延回路90を設け、チャージポンプ12に入力されるUP信号及びDN信号を遅らせ、制御回路100は、チャージポンプ12がチャージポンプ電流を流し始める前に、バイアス回路の動作を開始させている。

【0117】

これにより、PLL回路10cは、効率的に消費電力の削減が可能となるという効果のほかに、立ち上がり時の不安定なバイアス電流によるチャージポンプ12の誤作動を抑制できる、という効果をさらに有する。

【0118】

また、遅延回路110により、チャージポンプ電流が直ちに立ち下がらない場合でも、チャージポンプ12にバイアスを供給し続けられる。これにより、チャージポンプ12の誤動作を抑制できる。

【0119】

このように、遅延回路90,110を設けることで、チャージポンプ12がチャージポンプ電流を流している期間中、安定なバイアス電流をチャージポンプ12に供給できる。

また、PLL回路10cは、バイアス回路120にスイッチ122〜125と容量素子129,130を設け、バイアスイネーブル1〜3による制御によって、容量素子129,130のリーク分を補填する。これにより、バイアス電流の変動を抑えられ、精度のよいバイアス電流を、チャージポンプ12及び電圧制御発振器14に供給できる。

【0120】

図16では、UP信号だけが活性化状態となる場合について説明したが、DN信号だけが活性化状態となる場合、またはUP信号とDN信号が両方活性化状態となる場合についても同様の動作が行われる。

【0121】

なお、バイアス回路120は、図15のような回路に限定されず、以下のような回路としてもよい。

図17は、バイアス回路の他の例を示す図である。

【0122】

バイアス回路120aは、図15に示したバイアス回路120のnMOS126〜128の代わりにpMOSを用いている。すなわち、バイアス回路120aは、電流源131、スイッチ132,133,134,135、pMOS136,137,138、容量素子139,140を有する。

【0123】

スイッチ132,133は、OR回路101の出力信号によりオンオフ制御される。スイッチ134は、OR回路102の出力信号によりオンオフ制御される。また、スイッチ135は、OR回路103の出力信号によりオンオフ制御される。スイッチ132〜135は、たとえば、nMOSであり、そのゲートにOR回路101〜103から“1”が入力されるとオン状態となり、“0”が入力されるとオフ状態となる。

【0124】

スイッチ132は、電流源131とpMOS136のドレインとの間に設けられている。スイッチ133は、pMOS137のドレインとチャージポンプ12との間に設けられている。スイッチ134は、pMOS136のドレイン−ゲート間に接続されている。スイッチ135は、pMOS136とpMOS137のゲートの間に接続されている。

【0125】

また、pMOS137のゲートはpMOS138のゲートに接続されており、pMOS138のドレインは、電圧制御発振器14に接続されている。pMOS136〜138のソースは電源に接続されている。

【0126】

また、容量素子139の一方の端子は、pMOS136のゲートとスイッチ135間に接続されている。容量素子140の一方の端子は、pMOS137のゲートとスイッチ135間に接続されている。容量素子139,140の他方の端子は電源に接続されている。

【0127】

このようなバイアス回路120aを用いても同様な効果が得られる。また、基準電圧を発生させる回路部として、電流源の代わりに、抵抗を用いても、同様な効果が得られる。

図18は、バイアス回路の他の例を示す図である。図15に示したバイアス回路120と同様の要素については、同一符号を付している。

【0128】

バイアス回路120bは、図15に示したバイアス回路120の電流源121の代わりに、電源に接続された抵抗141を有しており、この抵抗により基準電圧を生成している。

【0129】

なお、図17に示したようなバイアス回路120aにおいても同様に、電流源131の代わりに抵抗を用いてもよい。

以上のような第4の実施の形態のPLL回路10cでは、バイアス回路120の消費電流(たとえば、数十〜数百μA)に比べて、制御回路100の消費電流は小さい(たとえば、数μA)。そのため、図15に示すようなOR回路101〜103を設けたとしても、UP信号とDN信号が非活性化状態の際に、バイアス回路120のチャージポンプ12へのバイアス電流を遮断するように制御することによる節電効果は高い。

【0130】

また、OR回路101〜103の面積は、PLL回路10c全体の1%程度にできるため、面積の増加は少ない。また、図18に示したような抵抗141を用いるようなバイアス回路120bを適用した場合でも、抵抗値を増やす(抵抗の面積も増える)ことなく、消費電流を削減できる。

【0131】

本実施の形態のような制御回路100を用いないPLL回路(電圧制御発振器はバイアス電流を必要としない回路構成とする)の通常動作状態で、たとえば、PLL回路全体の消費電流が150μA、バイアス回路の消費電流が80μAだったとする。バイアス抵抗を大きくすることで電流を削減することもできるが、バイアス電流に反比例して抵抗の面積が増えてしまう。これに対し、制御回路100を適用し、チャージポンプ12へバイアス電流を流す時間を、流さない時間に対して1%とし、制御回路100の消費電流を4μAとする。すると、バイアス抵抗の面積増加なしに、PLL回路全体の消費電流を、制御回路100を用いないPLL回路よりも、半分の75μA程度まで削減できる。

【0132】

(第5の実施の形態)

図19は、第5の実施の形態のPLL回路の一例を示す図である。図11に示したPLL回路10aと同様の要素については、同一符号を付している。

【0133】

第5の実施の形態のPLL回路10dは、容量素子53に保持される基準電圧を監視する電圧監視回路150を有している。

電圧監視回路150は、たとえば、コンパレータを有している。電圧監視回路150は、容量素子53に保持される基準電圧の変動量がある閾値を超えた場合に、基準電圧に異常が発生している旨を示す信号(以下異常検知信号と呼ぶ)を、制御回路160に通知する。たとえば、電圧監視回路150は、ある閾値電圧と容量素子53の電圧とを比較し、容量素子53の電圧が閾値電圧以下の場合、異常検知信号を制御回路160に通知する。

【0134】

制御回路160は、図11に示したPLL回路10aの、制御回路17と同様の機能を有している。制御回路160は、さらに、異常検知信号を受けると、所定期間バイアスイネーブルを活性化状態にして、バイアス回路50を動作させ、容量素子53を充電させる機能を有する。

【0135】

バイアスイネーブルを活性化状態に保持しておく期間としては、たとえば、電圧監視回路150が異常検知信号を出力している間、もしくは、電圧監視回路150が異常検知信号を出力している間と、異常検知信号を出力し終えた後の所定期間とする。たとえば、制御回路160は、カウンタを有し、異常検知信号が通知されると、基準信号である入力クロックが所定数入力されるまで、バイアスイネーブルを活性化状態にしておく。

【0136】

以下では、電圧監視回路150が異常検知信号を出力し終えた後に、制御回路160が入力クロックの立ち上がりを2回カウントするまで、バイアスイネーブルを活性化状態とする場合を例にして、第5の実施の形態のPLL回路10dの動作を説明する。

【0137】

図20は、PLL回路の動作開始時の動作の一例を示すタイミングチャートである。

図20では、上から、基準信号である入力クロック(CK)、フィードバック信号(FB)、UP信号(UP)、DN信号(DN)が示されている。また、電圧監視回路150から出力される異常検知信号(OVF)、制御回路160から出力される制御信号(バイアスイネーブル)、容量素子53に保持される基準電圧、チャージポンプ電流(Icp)が示されている。

【0138】

PLL回路10dの動作開示時刻である時刻t0では、容量素子53に保持されている基準電圧は低く、所定の閾値電圧Vth以下となっているので、OVFは活性化状態(Hレベル)となる。これにより、バイアスイネーブルもHレベルとなり、バイアス回路50におけるスイッチ52はオンし、容量素子53が充電される。

【0139】

時刻t1で、容量素子53に保持される基準電圧が閾値電圧Vthを超えると、電圧監視回路150は、OVFを非活性化状態(Lレベル)に立ち下げる。しかし、制御回路160は、OVFがLレベルに立ち下がってから、入力クロックの2つの目の立ち上がりを検出する時刻t2まで、バイアスイネーブルをHレベルに保持しておく。

【0140】

ただ、図20の例では、時刻t2において、UPがHレベルに立ち上がるため、UPとDNが両方Lレベルに立ち下がる時刻t3まで、バイアスイネーブルはHレベルのままとなる。

【0141】

時刻t3以降では、基準電圧がVthを上回っている間、UPまたはDNの一方または両方がHレベルのときには、チャージポンプ12にバイアス電流を供給し、UPとDNの両方がLレベルのときには、バイアス電流の供給を遮断する、前述の動作が行われる。

【0142】

このように、PLL回路10dの動作開始時に、一定期間、バイアスイネーブルを活性化状態に保持して、容量素子53を充電することで、基準電圧が一定のレベルになる時間を早められ、PLL回路10dの動作に不具合が生じることを抑制できる。

【0143】

図21は、PLL回路の動作中に基準電圧に異常が生じた場合の動作例を示すタイミングチャートである。

図21では、上から、基準信号である入力クロック(CK)、フィードバック信号(FB)、UP信号(UP)、DN信号(DN)が示されている。また、容量素子53に保持される基準電圧、電圧監視回路150から出力される異常検知信号(OVF)、制御回路160から出力される制御信号(バイアスイネーブル)、チャージポンプ電流(Icp)が示されている。

【0144】

時刻t1において、外乱などにより、容量素子53に保持されている基準電圧が閾値電圧Vth以下となると、OVFがHレベルに立ち上がり、バイアスイネーブルもHレベルに立ち上がる。これにより、スイッチ52がオン状態となり、容量素子53が充電される。時刻t2において、基準電圧が閾値電圧Vthを超えると、OVFはLレベルに立ち下がるが、制御回路17は、入力クロックの2つの目の立ち上がりを検出する時刻t3まで、バイアスイネーブルをHレベルに保持しておく。ただ、図21の例では、時刻t3において、UP及びDNがHレベルに立ち上がるため、UPとDNが両方Lレベルに立ち下がる時刻t4まで、バイアスイネーブルはHレベルのままとなる。

【0145】

このように、外乱など、何らかの要因で、基準電圧が大きく変動した場合、一定期間、バイアスイネーブルを活性化状態に保持して、容量素子53を充電することで、基準電圧が一定のレベルになる時間を早められる。これにより、PLL回路10dの動作に不具合が生じることを抑制できる。

【0146】

なお、以上説明した図19のPLL回路10dの例では、第2の実施の形態のPLL回路10aに電圧監視回路150を適用しているが、図14に示した第3の実施の形態のPLL回路10b、図15に示した第4の実施の形態のPLL回路10cにも適用できる。

【0147】

図14に示したPLL回路10bに適用する場合には、電圧監視回路150は、容量素子83の電圧を監視するようにすればよい。

図15に示したPLL回路10cに適用する場合には、電圧監視回路150は、たとえば、容量素子130の電圧を監視するようにすればよい。

【0148】

以上、実施の形態に基づき、本発明のPLL回路の一観点について説明してきたが、これらは一例にすぎず、上記の記載に限定されるものではない。

【符号の説明】

【0149】

10 PLL回路

11 位相比較回路

12 チャージポンプ

13 フィルタ

14 電圧制御発振器

15 フィードバック分周器

16 バイアス回路

17 制御回路

IN 入力端子

OUT 出力端子

【技術分野】

【0001】

本発明は、PLL(Phase-locked loop)回路に関する。

【背景技術】

【0002】

携帯機器の電池寿命を延ばすことなどを目的として、半導体集積回路の低消費電力化の要求が高まっている。PLL回路は、周波数シンセサイザとして用いられ、大部分のSOC(System-On-a-Chip)製品に搭載されている。

【0003】

PLL回路は、チャージポンプなどに対しバイアス電流を供給するバイアス回路を含み、その消費電流を削減することが求められている。

消費電流削減のため、フィードバック信号と基準信号の同期を検出(ロック検出)するロック検出回路を設け、ロック検出後に、バイアス回路を、位相を比較するタイミングにおいてイネーブルさせ、それ以外はディスイネーブルさせるPLL回路が知られている。

【0004】

なお、バイアス回路(基準電圧回路・基準電流回路)を間欠的に動作させる際に、起動を速める方法として、基準電圧を容量素子に保持させる技術が知られている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特表2003−529246号

【特許文献2】特開2011−8683号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかし、従来のPLL回路では、製造条件のばらつきなどで、ロック検出回路がロック検出を正しく行えないと、不要なタイミングでバイアス回路をイネーブルさせてしまい、十分な低消費電力化が図れない場合があった。

【課題を解決するための手段】

【0007】

発明の一観点によれば、基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号をチャージポンプに供給する位相比較回路と、前記チャージポンプにバイアス電流を供給するバイアス回路と、前記2種の位相差信号のうち一方または両方が活性化状態のときに前記バイアス回路の動作を行わせ、前記2種の位相差信号の両方が非活性化状態のときに、前記バイアス回路を停止させる制御回路と、を備えたPLL回路が提供される。

【発明の効果】

【0008】

開示のPLL回路によれば、チャージポンプが動作するタイミング以外でのバイアス電流の供給を抑制でき、効率的に消費電力の削減が可能となる。

【図面の簡単な説明】

【0009】

【図1】第1の実施の形態のPLL回路の一例を示す図である。

【図2】バイアス回路及び制御回路の一例を示す図である。

【図3】バイアス回路の他の例を示す図である。

【図4】第1の実施の形態のPLL回路の動作例を示すタイミングチャートである。

【図5】バイアス電流の立ち上がり期間を考慮したPLL回路の一部を示す図である。

【図6】図5の回路の動作例を示すタイミングチャートである。

【図7】チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。

【図8】図7の回路の動作例を示すタイミングチャートである。

【図9】バイアス電流の立ち上がり期間と、チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。

【図10】図9の回路の動作例を示すタイミングチャートである。

【図11】第2の実施の形態のPLL回路の一例を示す図である。

【図12】バイアス回路の一例を示す図である。

【図13】バイアス回路の他の例を示す図である。

【図14】第3の実施の形態のPLL回路の一例を示す図である。

【図15】第4の実施の形態のPLL回路の一例を示す図である。

【図16】第4の実施の形態のPLL回路の動作の一例を示すタイミングチャートである。

【図17】バイアス回路の他の例を示す図である。

【図18】バイアス回路の他の例を示す図である。

【図19】第5の実施の形態のPLL回路の一例を示す図である。

【図20】PLL回路の動作開始時の動作の一例を示すタイミングチャートである。

【図21】PLL回路の動作中に基準電圧に異常が生じた場合の動作例を示すタイミングチャートである。

【発明を実施するための形態】

【0010】

以下、本発明の実施の形態を、図面を参照しつつ説明する。

(第1の実施の形態)

図1は、第1の実施の形態のPLL回路の一例を示す図である。

【0011】

PLL回路10は、位相比較回路11、チャージポンプ12、フィルタ13、電圧制御発振器14、フィードバック分周器15、バイアス回路16、制御回路17を有している。

【0012】

位相比較回路11は、入力端子INから入力される基準信号と、フィードバック分周器15から出力されるフィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号(以下UP信号とDN信号と呼ぶ)をチャージポンプ12に供給する。位相比較回路11は、基準信号の遷移がフィードバック信号の遷移よりも前に起こる場合には、UP信号を活性状態とし、基準信号の遷移がフィードバック信号の遷移よりも後に起こる場合には、DN信号を活性状態とする。

【0013】

チャージポンプ12は、UP信号とDN信号に応じて、チャージポンプ電流を生成する。

フィルタ13は、チャージポンプ電流をフィルタリングして、制御電圧を生成し電圧制御発振器14に供給する。

【0014】

電圧制御発振器14は、制御電圧に応じて出力信号の発振周波数を調整し、調整した出力信号を出力端子OUTから出力するとともに、フィードバック分周器15に供給する。

フィードバック分周器15は、電圧制御発振器14の出力信号の周波数を任意の整数比で分周する。なお、周波数の逓倍が不要な場合には、フィードバック分周器15はなくてもよい。

【0015】

バイアス回路16は、チャージポンプ12に対して、チャージポンプ電流を生成させるためのバイアス電流を供給する。

制御回路17は、UP信号とDN信号のうち、一方または両方が活性化状態のときにバイアス回路16の動作を行わせ、UP信号とDN信号の両方が非活性化状態のときに、バイアス回路16を停止させる。なお、以下に示す例では、信号レベルが“1”(またはH(High)レベル)の場合を活性化状態、“0”(またはL(Low)レベル)の場合を非活性化状態として説明するが、“0”の場合を活性化状態、“1”の場合を非活性化状態としてもよい。

【0016】

図2は、バイアス回路及び制御回路の一例を示す図である。

バイアス回路16は、電流源20、スイッチ21,22、nチャネル型MOSFET(Metal-Oxide Semiconductor Field Effect Transistor)(以下nMOSと略す)23,24を有する。

【0017】

nMOS23のドレインはスイッチ21を介して、チャージポンプ12に接続されており、ソースは接地されている。また、nMOS23のゲートはnMOS24のゲートに接続されている。nMOS24のゲートはさらに、nMOS24のドレインに接続されている。nMOS24のドレインはスイッチ22を介して電流源20に接続されており、ソースは接地されている。スイッチ21,22は制御回路17からの制御信号によりオンまたはオフする。

【0018】

このようなバイアス回路16は、カレントミラーの機能を有し、スイッチ21,22のオン時には、電流源20で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0019】

制御回路17は、OR回路25を有している。位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が“1”の場合に、“1”を出力し、UP信号とDN信号の両方が“0”の場合に、“0”を出力する。すなわち、OR回路25は、UP信号とDN信号のうち、一方または両方が活性化状態のときに“1”を出力し、UP信号とDN信号の両方が非活性化状態のときに、“0”を出力する。

【0020】

図2のバイアス回路16及び制御回路17の例では、スイッチ21,22は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0021】

これにより、バイアス回路16は、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12にバイアス電流を供給する。そして、バイアス回路16は、UP信号とDN信号の両方が非活性化状態の場合には、動作を停止する。これにより、チャージポンプ12へのバイアス電流の供給が遮断される。

【0022】

なお、図2のバイアス回路16では、nMOS23,24が用いられているが、これに限定されず、pチャネル型MOSFET(以下pMOSと略す)を用いるようにしてもよい。

【0023】

図3は、バイアス回路の他の例を示す図である。

図3に示されるバイアス回路16aは、pMOS26,27、スイッチ28,29、電流源30を有している。

【0024】

pMOS26のドレインはスイッチ28を介して、チャージポンプ12に接続されており、ソースは電源に接続されている。また、pMOS26のゲートは、pMOS27のゲートに接続されている。pMOS27のゲートはさらにpMOS27のドレインに接続されている。pMOS27のドレインはスイッチ29を介して電流源30に接続されており、ソースは電源と接続されている。スイッチ28,29は制御回路17からの制御信号によりオンまたはオフする。

【0025】

このようなバイアス回路16aも、図2のバイアス回路16と同様に、カレントミラーの機能を有し、スイッチ28,29のオン時には、電流源30で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0026】

図3のバイアス回路16a及び制御回路17の例でも、スイッチ28,29は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0027】

これにより、バイアス回路16aは、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12にバイアス電流を供給する。そして、バイアス回路16aは、UP信号とDN信号の両方が非活性化状態の場合には、動作を停止する。これにより、チャージポンプ12へのバイアス電流の供給が遮断される。

【0028】

以下、第1の実施の形態のPLL回路10の動作の一例を、タイミングチャートを用いて説明する。

図4は、第1の実施の形態のPLL回路の動作例を示すタイミングチャートである。

【0029】

図4では、上から、基準信号である入力クロック(CK)、フィードバック信号(FB)、UP信号(UP)、DN信号(DN)が示されている。また、制御回路17から出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。

【0030】

CKがHレベルに立ち上がる時刻t1では、FBはLレベルのままであり、時刻t2になって、FBは、Hレベルに立ち上がる。すなわち、FBの位相は、基準信号であるCKの位相と比べて遅れている。

【0031】

そのため、位相比較回路11は、時刻t1において、UPをHレベルに立ち上げ、活性化状態とする。これにより、バイアスイネーブルもHレベルに立ち上がり、Ibiasが流れ、チャージポンプ12は、Icpを流し始める。

【0032】

時刻t2でFBがHレベルに立ち上がると、位相比較回路11は、時刻t3まではUPとDNの両方とも活性化状態とする。これは、位相比較回路11の「UP/DN信号のパルス幅 対 位相差」特性において、位相差が0付近に不感帯が生じるのを防ぐためであり、わずかな時間、UPとDNが両方、活性化状態とするようにしている。時刻t2と時刻t3の間は、UPとDNによって生じた電流が、チャージポンプ12内部で相殺されるので、図4に示されているように、この時間のIcpは0となっている。

【0033】

次に、時刻t4では、FBが立ち上がり、その後、時刻t5にてCKが立ち上がっている。すなわち、FBの位相は、基準信号であるCKの位相と比べて進んでいる。

そのため、位相比較回路11は、時刻t4において、DNをHレベルに立ち上げ、活性化状態とする。これにより、バイアスイネーブルも立ち上がり、Ibiasが流れ、チャージポンプ12は、負のIcpを流し始める。

【0034】

なお、時刻t5から時刻t6までは、上述と同様の理由で、UPとDNが両方活性化状態となっており、このときIcpは0となっている。

以上のように、UPまたはDNが活性化状態になっているタイミングで、チャージポンプ12が動作してIcpが流れる。

【0035】

本実施の形態のPLL回路10では、UP信号またはDN信号の一方または両方が活性化状態のときに、バイアス回路を動作させ、それ以外では停止させバイアス電流を遮断する。これにより、チャージポンプ12が動作するタイミング以外でのバイアス電流の供給を抑制でき、効率的に消費電力の削減が可能となる。

【0036】

ところで、制御回路17からの制御信号によって、バイアス回路16が動作を開始してからバイアス電流が立ち上がるまでに時間がかかる場合や、バイアス電流が立ち上がるときにノイズが発生すると、チャージポンプ12の動作に影響を与える可能性がある。それを抑制するために、たとえば、以下のような回路をさらに設けるようにしてもよい。

【0037】

図5は、バイアス電流の立ち上がり期間を考慮したPLL回路の一部を示す図である。図1と同様の要素については同一符号を付している。

図5に示されているように、位相比較回路11とチャージポンプ12の間に、遅延素子(バッファ)41,42を有する遅延回路40が設けられている。たとえば、遅延素子41は、位相比較回路11が出力するUP信号を遅延させてチャージポンプ12に供給し、遅延素子42は、位相比較回路11が出力するDN信号を遅延させてチャージポンプ12に供給する。遅延回路40の遅延量は、たとえば、バイアス電流の立ち上がり時に、バイアス電流が、一定の電流に安定するまでの時間、UP信号及びDN信号を遅延させるように設定される。

【0038】

制御回路17aのOR回路25aは、遅延前後のUP信号及びDN信号を入力して、それらの信号の論理和を制御信号(バイアスイネーブル)として、バイアス回路16に出力する。

【0039】

図6は、図5の回路の動作例を示すタイミングチャートである。

図6では、上から、遅延前のUP信号(UP1)、遅延後のUP信号(UP2)、制御回路17aから出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。なお、図6では、説明を簡単にするため、UP信号だけが活性化状態となる場合が示されている。

【0040】

時刻t1でUP1が立ち上がると、制御回路17aは、バイアスイネーブルをHレベルとし、バイアス回路16の動作を開始させる。これにより、Ibiasが立ち上がり始める。このとき、UP2は、Lレベルのままであるので、チャージポンプ12は、Icpを流さない。

【0041】

Ibiasが一定の電流値に立ち上がり、時刻t2で、UP2がHレベルに立ち上がると、チャージポンプ12は、Icpを流し始める。

時刻t3において、UP1がLレベルに立ち下がると、制御回路17aは、UP2がHレベルのままであるので、Hレベルのバイアスイネーブルをバイアス回路16に供給し続ける。

【0042】

時刻t4において、UP2がLレベルに立ち下がると、制御回路17aは、バイアスイネーブルをLレベルに立ち下げる。これにより、バイアス回路16から出力されるIbiasは0に下がっていく。また、チャージポンプ12はIcpを立ち下げる。

【0043】

以上のように、図5に示したPLL回路では、遅延回路40を設け、チャージポンプ12に入力されるUP信号及びDN信号を遅らせ、制御回路17aは、チャージポンプ12がチャージポンプ電流を流し始める前に、バイアス回路の動作を開始させている。

【0044】

これにより、PLL回路は、前述したような効率的に消費電力の削減が可能となるという効果のほかに、立ち上がり時の不安定なバイアス電流によるチャージポンプ12の誤作動を抑制できる、という効果をさらに有する。

【0045】

ところで、チャージポンプ12内の遅延により、UP信号及びDN信号が両方とも非活性化状態となっても、チャージポンプ電流が直ちに立ち下がらない場合がある。チャージポンプ電流の精度を保つため、バイアス電流は、チャージポンプ電流が流れている間は、チャージポンプ12に供給されていることが望ましい。

【0046】

図7は、チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。図1と同様の要素については同一符号を付している。

制御回路17bは、UP信号とDN信号を遅延する遅延回路43を有し、OR回路25bは、遅延前後のUP信号及びDN信号を入力し、その論理和をバイアス回路16に制御信号(バイアスイネーブル)として出力する。

【0047】

遅延回路43は、遅延素子(バッファ)43a,43bを有し、たとえば、遅延素子43aは、位相比較回路11が出力するUP信号を遅延させ、遅延素子43bは、位相比較回路11が出力するDN信号を遅延させる。遅延回路43の遅延量は、たとえば、UP信号及びDN信号の遅延時間が、チャージポンプ12の内部の遅延時間と同程度、もしくはそれ以上になるように設定される。

【0048】

なお、図7の例では、遅延回路43を制御回路17bに含めているが、制御回路17bとは別の回路ブロックとしてもよい。

図8は、図7の回路の動作例を示すタイミングチャートである。

【0049】

図8では、上から、遅延前のUP信号(UP1)、遅延後のUP信号(UP2)、制御回路17bから出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。なお、図8では、説明を簡単にするため、UP信号だけが活性化状態となる場合が示されている。

【0050】

時刻t1でUP1が立ち上がると、制御回路17bは、バイアスイネーブルをHレベルとし、バイアス回路16の動作を開始させる。これにより、Ibiasが立ち上がり始める。ただし、チャージポンプ12は、内部の遅延により、時刻t2になるまでは、Icpを流し始めない。図8の例の場合、時刻t1から時刻t2までの時間が、チャージポンプ12の遅延時間となる。

【0051】

時刻t2になると、チャージポンプ12は、Ibiasに基づいてIcpを出力し始める。UP2は、時刻t1から、遅延回路43による遅延時間経過後の時刻t3でHレベルに立ち上がる。

【0052】

時刻t4において、UP1がLレベルになっても、UP2がHレベルのままであるので、制御回路17bは、Hレベルのバイアスイネーブルをバイアス回路16に供給し続ける。また、UP1がLレベルに立ち下がっても、チャージポンプ12は、内部の遅延により、時刻t5になるまでは、Icpの出力を続ける。図8の例の場合、時刻t4から時刻t5までの時間が、Icpを立ち下げる際のチャージポンプ12の遅延時間となる。

【0053】

時刻t6で、UP2がLレベルに立ち下がると、バイアスイネーブルはLレベルに立ち下がり、Ibiasは下がり始める。

以上のように図7に示すようなPLL回路によれば、前述したように効率的に消費電力の削減が可能となるとともに、遅延により、チャージポンプ電流が直ちに立ち下がらない場合でも、チャージポンプ12に一定期間バイアス電流を供給し続けられる。これにより、チャージポンプ12の誤動作を抑制できる。

【0054】

なお、図5に示したPLL回路と、図7に示したPLL回路とを以下のように組み合わせることもできる。

図9は、バイアス電流の立ち上がり期間と、チャージポンプ電流の立ち下がり時の遅延を考慮したPLL回路の一部を示す図である。図5と図7に示したものと同様の要素については同一符号を付している。

【0055】

図9に示されるPLL回路では、図5に示した遅延回路40と、図7に示した制御回路17bとが組み合わされている。遅延回路40で遅延されたUP信号とDN信号が、制御回路17bの遅延回路43で、さらに遅延されてOR回路25bに入力されるような回路となっている。

【0056】

図10は、図9の回路の動作例を示すタイミングチャートである。

図10では、上から、遅延前のUP信号(UP1)、遅延回路40で遅延後のUP信号(UP2)、遅延回路43で遅延後のUP信号(UP3)が示されている。さらに、制御回路17bから出力される制御信号(バイアスイネーブル)、チャージポンプ12へ供給されるバイアス電流(Ibias)、チャージポンプ電流(Icp)が示されている。なお、図10では、説明の簡略化のため、UP信号だけが活性化状態となる場合が示されている。

【0057】

時刻t1でUP1が立ち上がると、制御回路17bは、バイアスイネーブルをHレベルとし、バイアス回路16の動作を開始させる。これにより、Ibiasが立ち上がり始める。このとき、UP2は、Lレベルのままであるので、チャージポンプ12は、Icpを流さない。

【0058】

Ibiasが一定の電流値に立ち上がり、時刻t2で、UP2がHレベルに立ち上がると、チャージポンプ12は、チャージポンプ12内による遅延時間経過後の時刻t3にて、Icpを流し始める。

【0059】

UP3は、時刻t2から遅延回路43による遅延時間経過後の時刻t4で、Hレベルに立ち上がる。

時刻t5において、UP1がLレベルに立ち下がると、制御回路17bは、UP3がHレベルのままであるので、Hレベルのバイアスイネーブルをバイアス回路16に供給し続ける。

【0060】

時刻t6において、UP2がLレベルに立ち下がると、チャージポンプ12は、内部の遅延により、時刻t7になるとIcpを遮断し始める。

時刻t8において、UP3がLレベルに立ち下がると、制御回路17bは、バイアスイネーブルをLレベルに立ち下げる。これにより、バイアス回路16から出力されるIbiasは0に下がっていく。

【0061】

図9に示したPLL回路によれば、前述したように効率的に消費電力の削減が可能になるとともに、立ち上がり時の不安定なバイアス電流や、遅延によりチャージポンプ電流が直ちに立ち下がらないことによるチャージポンプ12の誤動作を抑制できる。

【0062】

なお、図6、図8、図10では、UP信号だけが活性化状態となる場合について説明したが、DN信号だけが活性化状態となる場合、またはUP信号とDN信号が両方活性化状態となる場合についても同様の動作が行われる。

【0063】

(第2の実施の形態)

図11は、第2の実施の形態のPLL回路の一例を示す図である。図1に示した第1の実施の形態のPLL回路10と同様の要素については同一符号を付し、説明を省略する。

【0064】

第2の実施の形態のPLL回路10aは、電圧制御発振器14が、バイアス回路50で生成されるバイアス電流を用いる回路ブロックである場合に対応したものである。

すなわち、PLL回路10aは、図1に示したPLL回路10と異なり、チャージポンプ12のみならず、電圧制御発振器14にもバイアス電流を供給するバイアス回路50を有している。

【0065】

バイアス回路50は、基準電圧・バイアス電流生成部51、スイッチ52、容量素子53、バイアス電流生成部54を有している。

基準電圧・バイアス電流生成部51は、バイアス電流を生成するための基準電圧を生成するとともに、チャージポンプ12に供給するバイアス電流を生成する。

【0066】

スイッチ52は、制御回路17からの制御信号によってオンオフが制御される。

容量素子53は、基準電圧・バイアス電流生成部51で生成された基準電圧を保持する。

【0067】

バイアス電流生成部54は、容量素子53に保持される基準電圧に基づいて、バイアス電流を生成し、電圧制御発振器14に供給する。

図12は、バイアス回路の一例を示す図である。

【0068】

バイアス回路50において、基準電圧・バイアス電流生成部51は、電流源60、スイッチ61,62、nMOS63,64を有する。

nMOS63のドレインはスイッチ61を介して、チャージポンプ12に接続されており、ソースは接地されている。また、nMOS63のゲートはnMOS64のゲートに接続されている。nMOS64のゲートはさらに、nMOS64のドレインに接続されている。nMOS64のドレインはスイッチ62を介して電流源60に接続されており、ソースは接地されている。スイッチ61,62は制御回路17からの制御信号によりオンまたはオフする。

【0069】

このような基準電圧・バイアス電流生成部51は、カレントミラーの機能を有し、スイッチ61,62のオン時には、電流源60で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0070】

また、スイッチ52の一方の端子は、nMOS63,64のゲートに接続されており、スイッチ52のオン時には、nMOS63,64のゲート電圧が基準電圧として、容量素子53に保持される。

【0071】

バイアス電流生成部54は、nMOS65を有している。nMOS65のゲートは、スイッチ52の他方の端子及び容量素子53の一方の端子に接続されている。nMOS65のドレインは、電圧制御発振器14に接続されており、ソースは接地されている。

【0072】

バイアス電流生成部54は、スイッチ52がオン時には、基準電圧・バイアス電流生成部51との間でカレントミラーとして機能し、チャージポンプ12に供給されるバイアス電流と同じ電流を、電圧制御発振器14に供給する。スイッチ52がオフ時には、バイアス電流生成部54は、容量素子53に保持された基準電圧によりnMOS65はオン状態を保ち、電圧制御発振器14にバイアス電流を供給し続ける。

【0073】

図12のバイアス回路50の例では、スイッチ52,61,62は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0074】

これにより、バイアス回路50は、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12及び電圧制御発振器14にバイアス電流を供給する。そして、バイアス回路50は、UP信号とDN信号の両方が非活性化状態の場合には、チャージポンプ12へのバイアス電流の供給を停止する。しかし、バイアス回路50は、電圧制御発振器14に対しては、バイアス電流の供給を引き続き行うことができる。

【0075】

上記のようなバイアス回路50の代わりに、以下に示すようなpMOSを用いたバイアス回路を適用してもよい。

図13は、バイアス回路の他の例を示す図である。

【0076】

図13に示されるバイアス回路50aにおいて、基準電圧・バイアス電流生成部51aは、pMOS70,71、スイッチ72,73、電流源74を有している。

pMOS70のドレインはスイッチ72を介して、チャージポンプ12に接続されており、ソースは電源に接続されている。また、pMOS70のゲートは、pMOS71のゲートに接続されている。pMOS71のゲートはさらにpMOS71のドレインに接続されている。pMOS71のドレインはスイッチ73を介して電流源74に接続されており、ソースは電源と接続されている。スイッチ72,73は制御回路17からの制御信号によりオンまたはオフする。

【0077】

このような基準電圧・バイアス電流生成部51aは、カレントミラーの機能を有し、スイッチ72,73のオン時には、電流源74で生成された電流が、バイアス電流としてチャージポンプ12に供給される。

【0078】

また、スイッチ52の一方の端子は、pMOS70,71のゲートに接続されており、スイッチ52のオン時には、pMOS70,71のゲート電圧が基準電圧として、容量素子53に保持される。なお、容量素子53は、一方の端子をスイッチ52とバイアス電流生成部54a間のノードに接続し、他方の端子を電源に接続している。

【0079】

バイアス電流生成部54aは、pMOS75を有している。pMOS75のゲートは、スイッチ52の他方の端子及び容量素子53の一方の端子に接続されている。pMOS75のドレインは、電圧制御発振器14に接続されており、ソースは電源に接続されている。

【0080】

バイアス電流生成部54aは、スイッチ52がオン時には、基準電圧・バイアス電流生成部51aとの間でカレントミラーとして機能し、チャージポンプ12に供給されるバイアス電流と同じ電流を、電圧制御発振器14に供給する。スイッチ52がオフ時には、バイアス電流生成部54aは、容量素子53に保持された基準電圧によりpMOS75はオン状態を保ち、電圧制御発振器14にバイアス電流を供給し続ける。

【0081】

図13のバイアス回路50aの例でも、スイッチ52,72,73は、たとえば、nMOSであり、制御回路17のOR回路25から“1”が供給された場合にオンし、“0”が供給された場合にオフする。

【0082】

これにより、バイアス回路50aは、位相比較回路11から出力されるUP信号とDN信号のうち、一方または両方が活性化状態の場合に、カレントミラーとして動作し、チャージポンプ12及び電圧制御発振器14にバイアス電流を供給する。そして、バイアス回路50aは、UP信号とDN信号の両方が非活性化状態の場合には、チャージポンプ12へのバイアス電流の供給を停止する。しかし、バイアス回路50aは、電圧制御発振器14に対しては、バイアス電流の供給を引き続き行うことができる。

【0083】

なお、図12、図13のバイアス回路50,50aにおいて、容量素子53で保持された基準電圧は、スイッチ52がオフの場合には、リークによって変動する。しかし、前述したように、位相比較回路11は、入力される基準信号(入力クロック)とフィードバック信号の位相差が0であっても、わずかな期間、UP信号とDN信号を両方、活性化状態とするので、入力クロックの周期で、スイッチ52はオンする。これにより、容量素子53で保持される基準電圧は、入力クロックの周期で補正される。

【0084】

ただし、容量素子53で保持される基準電圧の変動が、UP信号またはDN信号のパルス幅の時間で補正できるように設計をすることが望ましい。

基準電圧の変動をΔVとすると、スイッチ52を閉じることで、nMOS64のゲート電位も、ΔV変化する(説明を簡単にするため、nMOS63〜65のゲート容量と、スイッチ52のON抵抗は無視する)。このとき、nMOS64のトランスコンダクタンスをgmとすると、nMOS64のドレイン電流はgmΔV減少する。nMOS64のドレイン電流が減少する代わりに、容量素子53には、gmΔVの大きさの電流が流入する。以上の原理から、容量素子53を充電する際の時定数C/gmが、UP信号またはDN信号の最小のパルス幅の時間より充分小さく(たとえば、1/3以下)になるように、容量値Cを決定することが望ましい。

【0085】

なお、外乱などの要因で、あるタイミングにおけるUP信号またはDN信号のパルス幅の時間では補正できないほど、基準電圧が変動したとする。その場合、基準電圧の変動によって出力クロックが変動し、入力クロックとフィードバック信号の位相差が広がることで、UP信号またはDN信号のパルス差が広くなり、容量素子53で保持される基準電圧は補正される。つまり、基準電圧が外乱などの影響で変動したとしても、PLL回路10aのフィードバックの効果によって、基準電圧は補正される。

【0086】

以上のような第2の実施の形態のPLL回路10aによれば、第1の実施の形態のPLL回路10と同様に効率的に消費電力の削減が行えるとともに、バイアス電流を常に用いる回路ブロックには、バイアス電流を供給し続けることができる。

【0087】

なお、バイアス電流を常に用いる回路ブロックとして、上記の例では、電圧制御発振器14を挙げたがこれに限定されない。回路構成によって、バイアス電流を常時使用する回路ブロックがPLL回路内にある場合には、その回路ブロックに対して本実施のバイアス回路から、容量素子に保持された基準電圧に基づくバイアス電流を供給すればよい。

【0088】

なお、第2の実施の形態のPLL回路10aに対して、図5〜図10に示したように、遅延回路40,43を設けて、各信号の立ち上がりや立ち下がりタイミングを調整するようにしてもよい。

【0089】

(第3の実施の形態)

図14は、第3の実施の形態のPLL回路の一例を示す図である。図11に示した第2の実施の形態のPLL回路10aと同様の要素については同一符号を付し、説明を省略する。

【0090】

第3の実施の形態のPLL回路10bでは、バイアス回路80が、第2の実施の形態のPLL回路10aと異なっている。

バイアス回路80は、基準電圧生成部81、スイッチ82、容量素子83、バイアス電流生成部84を有している。

【0091】

基準電圧生成部81は、たとえば、図12に示したような電流源60やスイッチ62などを有しており、UP信号とDN信号の一方または両方が活性化状態の際に、バイアス電流を生成するための基準電圧を出力する。

【0092】

スイッチ82は、制御回路17からの制御信号によってオンオフが制御される。UP信号とDN信号の一方または両方が活性化状態の際には、スイッチ82はオンし、UP信号とDN信号の両方が非活性化状態の際には、スイッチ82はオフする。

【0093】

容量素子83は、基準電圧生成部81で生成された基準電圧を保持する。

バイアス電流生成部84は、容量素子83に保持される基準電圧に基づいて、バイアス電流を生成し、チャージポンプ12と電圧制御発振器14に供給する。また、バイアス電流生成部84は、チャージポンプ12に対して、バイアス電流を供給するか否かを切り替えるスイッチを有している。そのスイッチは、制御回路17からの制御信号によってオンオフが制御される。UP信号とDN信号の一方または両方が活性化状態の際には、そのスイッチはオンしてチャージポンプ12にバイアス電流を供給する。UP信号とDN信号の両方が非活性化状態の際には、そのスイッチはオフして、チャージポンプ12へのバイアス電流の供給を遮断する。

【0094】

このようなPLL回路10bでも、第2の実施の形態のPLL回路10aと同様の効果が得られる。

なお、第3の実施の形態のPLL回路10bに対して、図5〜図10に示したように、遅延回路40,43を設けて、各信号の立ち上がりや立ち下がりタイミングを調整するようにしてもよい。

【0095】

さらに、チャージポンプ12に高精度のバイアス電流を供給し、かつ、電圧制御発振器14にもノイズの少ないバイアス電流を供給するために、以下のようなPLL回路を適用することもできる。

【0096】

(第4の実施の形態)

図15は、第4の実施の形態のPLL回路の一例を示す図である。

図15では、PLL回路10cの一部を示している。図示を省略した部分は、前述のPLL回路10,10a,10bと同様である。なお、PLL回路10,10a,10bと同様の要素については同一符号を付し、説明を省略する。

【0097】

第4の実施の形態のPLL回路10cは、位相比較回路11とチャージポンプ12の間に設けられた遅延回路90を有している。

遅延回路90は、位相比較回路11から出力されるUP信号を遅延させる遅延素子91,92,93と、DN信号を遅延させる遅延素子94,95,96を有している。

【0098】

制御回路100は、OR回路101,102,103と遅延回路110を有している。遅延回路110は、遅延素子93で遅延されたUP信号をさらに遅延させてOR回路103に入力する遅延素子111と、遅延素子96で遅延されたDN信号をさらに遅延させてOR回路103に入力する遅延素子112を有している。

【0099】

なお、図15の例では、遅延回路110を制御回路100に含めているが、制御回路100とは別の回路ブロックとしてもよい。

OR回路101は、遅延回路90による遅延前のUP信号とDN信号と、OR回路102の出力信号を入力し、これらの信号の論理和を出力する。OR回路102は、遅延素子91,94で遅延されたUP信号とDN信号と、OR回路103の出力信号を入力し、これらの信号の論理和を出力する。OR回路103は、遅延素子92,95で遅延されたUP信号とDN信号と、遅延素子111,112で遅延されたUP信号とDN信号とを入力し、これらの信号の論理和を出力する。

【0100】

バイアス回路120は、第2及び第3の実施の形態のPLL回路10a,10bのバイアス回路50,80と同様に、チャージポンプ12と電圧制御発振器14にバイアス電流を供給する機能を有しているが、以下のような各要素を有する。

【0101】

すなわち、バイアス回路120は、電流源121、スイッチ122,123,124,125、nMOS126,127,128、容量素子129,130を有する。

スイッチ122,123は、制御回路100から出力される制御信号のうち、OR回路101の出力信号によりオンオフ制御される。スイッチ124は、制御回路100から出力される制御信号のうち、OR回路102の出力信号によりオンオフ制御される。また、スイッチ125は、制御回路100から出力される制御信号のうち、OR回路103の出力信号によりオンオフ制御される。スイッチ122〜125は、たとえば、nMOSであり、そのゲートにOR回路101〜103から“1”が入力されるとオン状態となり、“0”が入力されるとオフ状態となる。

【0102】

スイッチ122は、電流源121とnMOS126のドレインとの間に設けられている。スイッチ123は、nMOS127のドレインとチャージポンプ12との間に設けられている。スイッチ124は、nMOS126のドレイン−ゲート間に接続されている。スイッチ125は、nMOS126とnMOS127のゲートの間に接続されている。

【0103】

また、nMOS127のゲートはnMOS128のゲートに接続されており、nMOS128のドレインは、電圧制御発振器14に接続されている。nMOS126〜128のソースは接地されている。

【0104】

また、容量素子129の一方の端子は、nMOS126のゲートとスイッチ125間に接続されている。容量素子130の一方の端子は、nMOS127のゲートとスイッチ125間に接続されている。容量素子129,130の他方の端子は接地されている。

【0105】

このようなバイアス回路120では、電流源121を含む基準電圧を発生する回路部と、容量素子129がスイッチ124を介して接続されており、スイッチ122がオン状態のとき、スイッチ124がオン状態となると、容量素子129が充電され、基準電圧が保持される。その後、スイッチ125がオン状態となると、容量素子130が充電されることになる。

【0106】

図16は、第4の実施の形態のPLL回路の動作の一例を示すタイミングチャートである。

遅延前のUP信号(UP1)、遅延素子91で遅延後のUP信号(UP2)、遅延素子92でさらに遅延されたUP信号(UP3)、遅延素子93でさらに遅延されたUP信号(UP4)、遅延素子111でさらに遅延されたUP信号(UP5)が示されている。また、OR回路101の出力信号(バイアスイネーブル1)、OR回路102の出力信号(バイアスイネーブル2)、OR回路103の出力信号(バイアスイネーブル3)が示されている。また、nMOS126のドレイン電圧(V1)、nMOS126のソース電流(I1)、nMOS126のゲート電圧(V2)、nMOS127のゲート電圧(V3)が示されている。さらに、電圧制御発振器14に供給されるバイアス電流(Ibias1)、チャージポンプ12に供給されるバイアス電流(Ibias2)、チャージポンプ電流(Icp)が示されている。

【0107】

なお、図16では、説明の簡略化のため、UP信号だけが活性化状態となる場合が示されている。

時刻t0では、UP1〜UP5、バイアスイネーブル1〜3はLレベルであるものとする。また、V2,V3は、容量素子129,130に保持されている電圧による0以上の一定値(Hレベル)を示しているものとする。

【0108】

これにより、スイッチ122〜125は全てオフ状態で、nMOS126はオン状態であるため、V1もLレベル、I1、Ibias2、Icpも0となっている。また、V3がHレベルであることにより、nMOS128がオンしており、Ibias1が電圧制御発振器14に供給されている。

【0109】

時刻t1でUP1が立ち上がると、OR回路101による遅延後の時刻t2においてバイアスイネーブル1がHレベルに立ち上がる。これにより、スイッチ122がオンし、V1、I1が立ち上がり始め、その後、一定値となる。また、スイッチ123もオンし、容量素子130に保持されている基準電圧によってIbias2も立ち上がる。基準電圧を保持する容量素子130を設けていることによって、Ibias2は素早く立ち上がる。

【0110】

時刻t3でUP2が立ち上がると、OR回路102による遅延後の時刻t4においてバイアスイネーブル2がHレベルに立ち上がる。これにより、スイッチ124がオンし、電流源121の電流により容量素子129に保持されている電荷のリーク分が補填され、V2が補正される。

【0111】

時刻t5でUP3が立ち上がると、OR回路103による遅延後の時刻t6においてバイアスイネーブル3がHレベルに立ち上がる。これにより、スイッチ125がオンし、電流源121の電流により容量素子130に保持されている電荷のリーク分が補填され、V3が補正される。これにより、電圧制御発振器14に供給されるバイアス電流であるIbias1、チャージポンプ12に供給されるバイアス電流であるIbias2も補正される。

【0112】

このとき、容量素子129に基準電圧が保持されているため、電圧の変動を抑えることができる。

時刻t7でUP4が立ち上がると、チャージポンプ12は、Icpを流し始める。その後、時刻t8でUP5が立ち上がるが、バイアスイネーブル3は、Hレベルのままである。

【0113】

その後、UP1〜UP3が順にLレベルに立ち下がり、時刻t9でUP4がLレベルに立ち下がると、Icpは立ち下がるが、UP5はHレベルのままであるので、OR回路103の出力信号であるバイアスイネーブル3はHレベルのままとなる。これにより、OR回路103の出力信号を入力するOR回路102の出力信号であるバイアスイネーブル2もHレベルを維持し、OR回路102の出力信号を入力するOR回路101の出力信号であるバイアスイネーブル1もHレベルを維持する。そのため、スイッチ122〜125もオン状態のままであり、チャージポンプ12及び電圧制御発振器14に対して、バイアス電流(Ibias2,Ibias1)が供給され続ける。

【0114】

時刻t10でUP5が立ち下がると、OR回路103による遅延後の時刻t11においてバイアスイネーブル3がLレベルに立ち下がり、これを受けてバイアスイネーブル2、バイアスイネーブル1が順にLレベルに立ち下がる。これにより、スイッチ125、スイッチ124が順にオフ状態となり、最後にスイッチ122,123がオフ状態となる。

【0115】

このような順序でスイッチ122〜125をオフ状態にしていくことで、容量素子130に保持される基準電圧が大きく変動することを抑えられる。

時刻t12でバイアスイネーブル1がLレベルに立ち下がると、スイッチ123はオフ状態となるので、Ibias2は立ち下がる。Ibias1は、容量素子130に保持される電圧によって、電圧制御発振器14に供給され続ける。

【0116】

以上のように、遅延回路90を設け、チャージポンプ12に入力されるUP信号及びDN信号を遅らせ、制御回路100は、チャージポンプ12がチャージポンプ電流を流し始める前に、バイアス回路の動作を開始させている。

【0117】

これにより、PLL回路10cは、効率的に消費電力の削減が可能となるという効果のほかに、立ち上がり時の不安定なバイアス電流によるチャージポンプ12の誤作動を抑制できる、という効果をさらに有する。

【0118】

また、遅延回路110により、チャージポンプ電流が直ちに立ち下がらない場合でも、チャージポンプ12にバイアスを供給し続けられる。これにより、チャージポンプ12の誤動作を抑制できる。

【0119】

このように、遅延回路90,110を設けることで、チャージポンプ12がチャージポンプ電流を流している期間中、安定なバイアス電流をチャージポンプ12に供給できる。

また、PLL回路10cは、バイアス回路120にスイッチ122〜125と容量素子129,130を設け、バイアスイネーブル1〜3による制御によって、容量素子129,130のリーク分を補填する。これにより、バイアス電流の変動を抑えられ、精度のよいバイアス電流を、チャージポンプ12及び電圧制御発振器14に供給できる。

【0120】

図16では、UP信号だけが活性化状態となる場合について説明したが、DN信号だけが活性化状態となる場合、またはUP信号とDN信号が両方活性化状態となる場合についても同様の動作が行われる。

【0121】

なお、バイアス回路120は、図15のような回路に限定されず、以下のような回路としてもよい。

図17は、バイアス回路の他の例を示す図である。

【0122】

バイアス回路120aは、図15に示したバイアス回路120のnMOS126〜128の代わりにpMOSを用いている。すなわち、バイアス回路120aは、電流源131、スイッチ132,133,134,135、pMOS136,137,138、容量素子139,140を有する。

【0123】

スイッチ132,133は、OR回路101の出力信号によりオンオフ制御される。スイッチ134は、OR回路102の出力信号によりオンオフ制御される。また、スイッチ135は、OR回路103の出力信号によりオンオフ制御される。スイッチ132〜135は、たとえば、nMOSであり、そのゲートにOR回路101〜103から“1”が入力されるとオン状態となり、“0”が入力されるとオフ状態となる。

【0124】

スイッチ132は、電流源131とpMOS136のドレインとの間に設けられている。スイッチ133は、pMOS137のドレインとチャージポンプ12との間に設けられている。スイッチ134は、pMOS136のドレイン−ゲート間に接続されている。スイッチ135は、pMOS136とpMOS137のゲートの間に接続されている。

【0125】

また、pMOS137のゲートはpMOS138のゲートに接続されており、pMOS138のドレインは、電圧制御発振器14に接続されている。pMOS136〜138のソースは電源に接続されている。

【0126】

また、容量素子139の一方の端子は、pMOS136のゲートとスイッチ135間に接続されている。容量素子140の一方の端子は、pMOS137のゲートとスイッチ135間に接続されている。容量素子139,140の他方の端子は電源に接続されている。

【0127】

このようなバイアス回路120aを用いても同様な効果が得られる。また、基準電圧を発生させる回路部として、電流源の代わりに、抵抗を用いても、同様な効果が得られる。

図18は、バイアス回路の他の例を示す図である。図15に示したバイアス回路120と同様の要素については、同一符号を付している。

【0128】

バイアス回路120bは、図15に示したバイアス回路120の電流源121の代わりに、電源に接続された抵抗141を有しており、この抵抗により基準電圧を生成している。

【0129】

なお、図17に示したようなバイアス回路120aにおいても同様に、電流源131の代わりに抵抗を用いてもよい。

以上のような第4の実施の形態のPLL回路10cでは、バイアス回路120の消費電流(たとえば、数十〜数百μA)に比べて、制御回路100の消費電流は小さい(たとえば、数μA)。そのため、図15に示すようなOR回路101〜103を設けたとしても、UP信号とDN信号が非活性化状態の際に、バイアス回路120のチャージポンプ12へのバイアス電流を遮断するように制御することによる節電効果は高い。

【0130】

また、OR回路101〜103の面積は、PLL回路10c全体の1%程度にできるため、面積の増加は少ない。また、図18に示したような抵抗141を用いるようなバイアス回路120bを適用した場合でも、抵抗値を増やす(抵抗の面積も増える)ことなく、消費電流を削減できる。

【0131】

本実施の形態のような制御回路100を用いないPLL回路(電圧制御発振器はバイアス電流を必要としない回路構成とする)の通常動作状態で、たとえば、PLL回路全体の消費電流が150μA、バイアス回路の消費電流が80μAだったとする。バイアス抵抗を大きくすることで電流を削減することもできるが、バイアス電流に反比例して抵抗の面積が増えてしまう。これに対し、制御回路100を適用し、チャージポンプ12へバイアス電流を流す時間を、流さない時間に対して1%とし、制御回路100の消費電流を4μAとする。すると、バイアス抵抗の面積増加なしに、PLL回路全体の消費電流を、制御回路100を用いないPLL回路よりも、半分の75μA程度まで削減できる。

【0132】

(第5の実施の形態)

図19は、第5の実施の形態のPLL回路の一例を示す図である。図11に示したPLL回路10aと同様の要素については、同一符号を付している。

【0133】

第5の実施の形態のPLL回路10dは、容量素子53に保持される基準電圧を監視する電圧監視回路150を有している。

電圧監視回路150は、たとえば、コンパレータを有している。電圧監視回路150は、容量素子53に保持される基準電圧の変動量がある閾値を超えた場合に、基準電圧に異常が発生している旨を示す信号(以下異常検知信号と呼ぶ)を、制御回路160に通知する。たとえば、電圧監視回路150は、ある閾値電圧と容量素子53の電圧とを比較し、容量素子53の電圧が閾値電圧以下の場合、異常検知信号を制御回路160に通知する。

【0134】

制御回路160は、図11に示したPLL回路10aの、制御回路17と同様の機能を有している。制御回路160は、さらに、異常検知信号を受けると、所定期間バイアスイネーブルを活性化状態にして、バイアス回路50を動作させ、容量素子53を充電させる機能を有する。

【0135】

バイアスイネーブルを活性化状態に保持しておく期間としては、たとえば、電圧監視回路150が異常検知信号を出力している間、もしくは、電圧監視回路150が異常検知信号を出力している間と、異常検知信号を出力し終えた後の所定期間とする。たとえば、制御回路160は、カウンタを有し、異常検知信号が通知されると、基準信号である入力クロックが所定数入力されるまで、バイアスイネーブルを活性化状態にしておく。

【0136】

以下では、電圧監視回路150が異常検知信号を出力し終えた後に、制御回路160が入力クロックの立ち上がりを2回カウントするまで、バイアスイネーブルを活性化状態とする場合を例にして、第5の実施の形態のPLL回路10dの動作を説明する。

【0137】

図20は、PLL回路の動作開始時の動作の一例を示すタイミングチャートである。

図20では、上から、基準信号である入力クロック(CK)、フィードバック信号(FB)、UP信号(UP)、DN信号(DN)が示されている。また、電圧監視回路150から出力される異常検知信号(OVF)、制御回路160から出力される制御信号(バイアスイネーブル)、容量素子53に保持される基準電圧、チャージポンプ電流(Icp)が示されている。

【0138】

PLL回路10dの動作開示時刻である時刻t0では、容量素子53に保持されている基準電圧は低く、所定の閾値電圧Vth以下となっているので、OVFは活性化状態(Hレベル)となる。これにより、バイアスイネーブルもHレベルとなり、バイアス回路50におけるスイッチ52はオンし、容量素子53が充電される。

【0139】

時刻t1で、容量素子53に保持される基準電圧が閾値電圧Vthを超えると、電圧監視回路150は、OVFを非活性化状態(Lレベル)に立ち下げる。しかし、制御回路160は、OVFがLレベルに立ち下がってから、入力クロックの2つの目の立ち上がりを検出する時刻t2まで、バイアスイネーブルをHレベルに保持しておく。

【0140】

ただ、図20の例では、時刻t2において、UPがHレベルに立ち上がるため、UPとDNが両方Lレベルに立ち下がる時刻t3まで、バイアスイネーブルはHレベルのままとなる。

【0141】

時刻t3以降では、基準電圧がVthを上回っている間、UPまたはDNの一方または両方がHレベルのときには、チャージポンプ12にバイアス電流を供給し、UPとDNの両方がLレベルのときには、バイアス電流の供給を遮断する、前述の動作が行われる。

【0142】

このように、PLL回路10dの動作開始時に、一定期間、バイアスイネーブルを活性化状態に保持して、容量素子53を充電することで、基準電圧が一定のレベルになる時間を早められ、PLL回路10dの動作に不具合が生じることを抑制できる。

【0143】

図21は、PLL回路の動作中に基準電圧に異常が生じた場合の動作例を示すタイミングチャートである。

図21では、上から、基準信号である入力クロック(CK)、フィードバック信号(FB)、UP信号(UP)、DN信号(DN)が示されている。また、容量素子53に保持される基準電圧、電圧監視回路150から出力される異常検知信号(OVF)、制御回路160から出力される制御信号(バイアスイネーブル)、チャージポンプ電流(Icp)が示されている。

【0144】

時刻t1において、外乱などにより、容量素子53に保持されている基準電圧が閾値電圧Vth以下となると、OVFがHレベルに立ち上がり、バイアスイネーブルもHレベルに立ち上がる。これにより、スイッチ52がオン状態となり、容量素子53が充電される。時刻t2において、基準電圧が閾値電圧Vthを超えると、OVFはLレベルに立ち下がるが、制御回路17は、入力クロックの2つの目の立ち上がりを検出する時刻t3まで、バイアスイネーブルをHレベルに保持しておく。ただ、図21の例では、時刻t3において、UP及びDNがHレベルに立ち上がるため、UPとDNが両方Lレベルに立ち下がる時刻t4まで、バイアスイネーブルはHレベルのままとなる。

【0145】

このように、外乱など、何らかの要因で、基準電圧が大きく変動した場合、一定期間、バイアスイネーブルを活性化状態に保持して、容量素子53を充電することで、基準電圧が一定のレベルになる時間を早められる。これにより、PLL回路10dの動作に不具合が生じることを抑制できる。

【0146】

なお、以上説明した図19のPLL回路10dの例では、第2の実施の形態のPLL回路10aに電圧監視回路150を適用しているが、図14に示した第3の実施の形態のPLL回路10b、図15に示した第4の実施の形態のPLL回路10cにも適用できる。

【0147】

図14に示したPLL回路10bに適用する場合には、電圧監視回路150は、容量素子83の電圧を監視するようにすればよい。

図15に示したPLL回路10cに適用する場合には、電圧監視回路150は、たとえば、容量素子130の電圧を監視するようにすればよい。

【0148】

以上、実施の形態に基づき、本発明のPLL回路の一観点について説明してきたが、これらは一例にすぎず、上記の記載に限定されるものではない。

【符号の説明】

【0149】

10 PLL回路

11 位相比較回路

12 チャージポンプ

13 フィルタ

14 電圧制御発振器

15 フィードバック分周器

16 バイアス回路

17 制御回路

IN 入力端子

OUT 出力端子

【特許請求の範囲】

【請求項1】

基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号をチャージポンプに供給する位相比較回路と、

前記チャージポンプにバイアス電流を供給するバイアス回路と、

前記2種の位相差信号のうち一方または両方が活性化状態のときに前記バイアス回路の動作を行わせ、前記2種の位相差信号の両方が非活性化状態のときに、前記バイアス回路を停止させる制御回路と、

を有することを特徴とするPLL回路。

【請求項2】

前記2種の位相差信号を遅延して、前記チャージポンプに供給する遅延回路をさらに有し、

前記制御回路は、前記チャージポンプが遅延された前記2種の位相差信号に応じてチャージポンプ電流を流し始める前に、前記バイアス回路の動作を開始させることを特徴とする請求項1に記載のPLL回路。

【請求項3】

前記2種の位相差信号を遅延する他の遅延回路を有し、前記制御回路は、前記2種の位相差信号が非活性化状態に遷移してから前記他の遅延回路による遅延時間経過後に、前記バイアス回路の動作を停止させることを特徴とする請求項1または2に記載のPLL回路。

【請求項4】

前記バイアス回路は、基準電圧を保持する容量素子を有し、前記容量素子で保持された前記基準電圧に基づく前記バイアス電流を、PLL回路内の回路ブロックに供給することを特徴とする請求項1乃至3の何れか一項に記載のPLL回路。

【請求項5】

前記バイアス回路は、第1のスイッチを介して前記基準電圧を発生する回路部と接続され、第2のスイッチを介して前記容量素子と接続される他の容量素子を有し、

前記制御回路は、前記第1のスイッチをオン状態として前記他の容量素子に前記基準電圧を保持させた後、前記第2のスイッチをオン状態として前記容量素子に保持される前記基準電圧を補正させることを特徴とする請求項4に記載のPLL回路。

【請求項6】

前記バイアス回路は、第1のスイッチを介して前記基準電圧を発生する回路部と接続され、第2のスイッチを介して前記容量素子と接続される他の容量素子を有し、

前記制御回路は、前記第2のスイッチをオフ状態として前記容量素子と前記他の容量素子との間の接続を遮断させた後、前記第1のスイッチをオフ状態として前記基準電圧を発生する回路部と、前記他の容量素子との間の接続を遮断させることを特徴とする請求項4または5に記載のPLL回路。

【請求項7】

前記容量素子に保持される前記基準電圧を監視し、前記基準電圧の変動量が閾値を超えた場合に、前記基準電圧に異常が発生している旨を示す異常検知信号を出力する電圧監視回路を有し、

前記制御回路は、前記異常検知信号を受けると、前記バイアス回路に前記容量素子を、所定の期間、充電させることを特徴とする請求項4乃至6の何れか一項に記載のPLL回路。

【請求項8】

前記電圧監視回路は、PLL回路の動作開始時に、前記異常検知信号を出力することを特徴とする請求項7に記載のPLL回路。

【請求項1】

基準信号と、フィードバック信号の位相を比較し、比較結果に応じた2種の位相差信号をチャージポンプに供給する位相比較回路と、

前記チャージポンプにバイアス電流を供給するバイアス回路と、

前記2種の位相差信号のうち一方または両方が活性化状態のときに前記バイアス回路の動作を行わせ、前記2種の位相差信号の両方が非活性化状態のときに、前記バイアス回路を停止させる制御回路と、

を有することを特徴とするPLL回路。

【請求項2】

前記2種の位相差信号を遅延して、前記チャージポンプに供給する遅延回路をさらに有し、

前記制御回路は、前記チャージポンプが遅延された前記2種の位相差信号に応じてチャージポンプ電流を流し始める前に、前記バイアス回路の動作を開始させることを特徴とする請求項1に記載のPLL回路。

【請求項3】

前記2種の位相差信号を遅延する他の遅延回路を有し、前記制御回路は、前記2種の位相差信号が非活性化状態に遷移してから前記他の遅延回路による遅延時間経過後に、前記バイアス回路の動作を停止させることを特徴とする請求項1または2に記載のPLL回路。

【請求項4】

前記バイアス回路は、基準電圧を保持する容量素子を有し、前記容量素子で保持された前記基準電圧に基づく前記バイアス電流を、PLL回路内の回路ブロックに供給することを特徴とする請求項1乃至3の何れか一項に記載のPLL回路。

【請求項5】

前記バイアス回路は、第1のスイッチを介して前記基準電圧を発生する回路部と接続され、第2のスイッチを介して前記容量素子と接続される他の容量素子を有し、

前記制御回路は、前記第1のスイッチをオン状態として前記他の容量素子に前記基準電圧を保持させた後、前記第2のスイッチをオン状態として前記容量素子に保持される前記基準電圧を補正させることを特徴とする請求項4に記載のPLL回路。

【請求項6】

前記バイアス回路は、第1のスイッチを介して前記基準電圧を発生する回路部と接続され、第2のスイッチを介して前記容量素子と接続される他の容量素子を有し、

前記制御回路は、前記第2のスイッチをオフ状態として前記容量素子と前記他の容量素子との間の接続を遮断させた後、前記第1のスイッチをオフ状態として前記基準電圧を発生する回路部と、前記他の容量素子との間の接続を遮断させることを特徴とする請求項4または5に記載のPLL回路。

【請求項7】

前記容量素子に保持される前記基準電圧を監視し、前記基準電圧の変動量が閾値を超えた場合に、前記基準電圧に異常が発生している旨を示す異常検知信号を出力する電圧監視回路を有し、

前記制御回路は、前記異常検知信号を受けると、前記バイアス回路に前記容量素子を、所定の期間、充電させることを特徴とする請求項4乃至6の何れか一項に記載のPLL回路。

【請求項8】

前記電圧監視回路は、PLL回路の動作開始時に、前記異常検知信号を出力することを特徴とする請求項7に記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【公開番号】特開2013−55533(P2013−55533A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−192824(P2011−192824)

【出願日】平成23年9月5日(2011.9.5)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月5日(2011.9.5)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]