PLL回路

【課題】本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【解決手段】本発明は、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力するDCO1と、位相差を示すデジタル信号を出力する位相検出器10と、位相差を示すアナログ信号を出力し、デジタル信号の少なくとも最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有するEXOR型位相比較器21と、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える切替制御部Sと、を備えることを特徴とするPLL回路Pである。

【解決手段】本発明は、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力するDCO1と、位相差を示すデジタル信号を出力する位相検出器10と、位相差を示すアナログ信号を出力し、デジタル信号の少なくとも最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有するEXOR型位相比較器21と、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える切替制御部Sと、を備えることを特徴とするPLL回路Pである。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、基準信号に基づいて所望の周波数の信号を出力するPLL(Phase−Locked Loop)回路に関する。

【背景技術】

【0002】

無線通信回路の周波数シンセサイザやクロック生成回路においてPLL回路が用いられている。近年、低電源電圧での動作が可能であり、チップサイズを縮小できるオールデジタルPLL(ADPLL)回路が研究されている(例えば、非特許文献1を参照。)。

【0003】

ADPLL回路は、アナログPLL回路の電圧制御発振器(VCO:Voltage Contorolled Oscillator)及びアナログ位相比較器の代替として、可変周波数発振器(DCO:Digitally Controlled Oscillator)及びデジタル位相比較器を備える。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】“ALL−DIGITAL FREQUENCY SYNTHEZSIZER in DEEP−SUBMICRON CMOS” Robert Bogdan Staszewski/Poras T.Balsara 著

【発明の概要】

【発明が解決しようとする課題】

【0005】

デジタル位相比較器は、位相差とデジタル信号の間にステップ特性を有するため、DCOの制御電圧に対して制御されていない揺らぎを発生させて、C/Nを劣化させる。ここで、デジタル位相比較器は、デジタル信号のビット数を増やすならば、DCOの制御電圧に対して制御されていない揺らぎを小さくすることはできるがなくすことはできない。

【0006】

アナログ位相比較器(特にEXOR型)は、位相差とアナログ信号の間に線形特性を有するため、VCOの制御電圧に対して制御されていない揺らぎを発生させず、C/Nを向上させる。しかし、アナログ位相比較器は、高速な周波数の切り替えはできない。

【0007】

そこで、前記課題を解決するために、本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、ロック動作を開始する際には、デジタル位相比較器を利用することにより、高速な周波数の切り替えを実現して、ロック動作を終了した後には、アナログ位相比較器を利用することにより、C/Nの向上を実現することとした。

【0009】

具体的には、本発明は、基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振部と、前記位相差を示すデジタル信号を出力するデジタル位相比較部と、前記位相差を示すアナログ信号を出力し、前記デジタル信号の少なくとも最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有するアナログ位相比較部と、前記デジタル信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内に入ったとき、位相比較の主体を前記デジタル位相比較部から前記アナログ位相比較部へ切り替える切替制御部と、を備えることを特徴とするPLL回路である。

【0010】

この構成によれば、最初のロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することができる。

【0011】

また、本発明は、前記アナログ位相比較部は、前記デジタル信号の最下位1ビットに相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、前記アナログ信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替えることを特徴とするPLL回路である。

【0012】

この構成によれば、アンロックからのロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することができる。

【0013】

また、本発明は、前記アナログ位相比較部は、前記デジタル信号の下位mビット(m>1)に相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、前記アナログ信号が示す前記位相差が、前記デジタル信号の下位nビット(m>n>1)に相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替えることを特徴とするPLL回路である。

【0014】

この構成によれば、アンロックからのロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するうえに、上記の位相差が上記の範囲内をいずれの方向に外れたかを認識するPLL回路を提供することができる。

【発明の効果】

【0015】

本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することができる。

【図面の簡単な説明】

【0016】

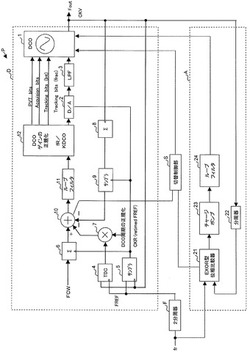

【図1】本発明のPLL回路の構成を示す図である。

【図2】デジタル位相検波特性を示す図である。

【図3】アナログ位相検波特性を示す図である。

【図4】最初のロック動作の処理を示す図である。

【図5】アンロックからのロック動作の処理を示す図である。

【図6】アナログ位相検波特性を示す図である。

【図7】アンロックからのロック動作の処理を示す図である。

【発明を実施するための形態】

【0017】

添付の図面を参照して本発明の実施形態を説明する。以下に説明する実施形態は本発明の実施の例であり、本発明は以下の実施形態に制限されるものではない。

【0018】

(PLL回路の概要)

本発明のPLL回路の構成を図1に示す。PLL回路Pは、デジタルPLL回路D、アナログPLL回路A、切替制御部S及び2分周器Fから構成される。PLL回路Pが最初のロック動作を開始する際には、切替制御部SはデジタルPLL回路Dのデジタル位相比較器を利用する一方で、PLL回路Pが最初のロック動作を終了した後には、切替制御部SはアナログPLL回路Aのアナログ位相比較器を利用する。PLL回路Pがアンロックからのロック動作を開始する際には、切替制御部SはデジタルPLL回路Dのデジタル位相比較器を利用する一方で、PLL回路Pがアンロックからのロック動作を終了した後には、切替制御部SはアナログPLL回路Aのアナログ位相比較器を利用する。

【0019】

デジタルPLL回路Dは、DCO1、D/A(Digital−Analog Converter)2、LPF(Low Pass Filter)3、TDC4、サンプラ5、基準位相アキュムレータ6、乗算器7、可変位相アキュムレータ8、サンプラ9、位相検出器10、ループフィルタ11及びゲイン正規化回路12から構成される。

【0020】

DCO1は、バラクタ(可変容量ダイオード)配列を持ち、発振周波数を2進数コードで制御することができる。ここで、DCO1の発振周波数が広帯域で、切り替え周波数間隔が小さい場合は、バラクタのbit数が実現不可能なほど多くなることがある。そこで、段階的なステップで周波数範囲を小さくし、周波数分解能を改善する方法(ディスクリートチューニング)で、実現可能なバラクタ配列を構成することができる。

【0021】

例えば、2進数コードが入力される複数のバンクを持つバラクタ配列がある。第一バンクは400MHzの可変範囲で2316kHzの周波数間隔でロックができ、第二バンクは118MHzの可変範囲で461kHzの周波数間隔でロックができ、第三バンクは1.5MHzの可変範囲で、23kHzの周波数間隔でロックができる。第一バンク、第二バンク、第三バンクは、それぞれPVTバンク、Acquisitionバンク、Tracking(integer)バンクと呼ばれることがある。そして、第三バンクの1bitにあたるバラクタサイズが基本的に最小サイズになる。

【0022】

デジタルPLL回路Dへの要求として、上記第三バンクでロックできる周波数間隔より狭い間隔の周波数でロックすることが求められることもある。この場合、下位ビットを

D/A2でアナログ電圧に変換してバラクタに入力する。D/A2は、下位ビットとなるTracking bits(fractional)を、DCO1のコントロール電圧に変換して、DCO1のバラクタを制御する。LPF3は、D/A2が出力するアナログ信号について、高周波成分を除去して、DCO1のバラクタに入力する。D/A2の同期用信号として、リタイミングされた基準信号CKRを使用する。

【0023】

TDC(Time−to−Digital Converter)4は、DCO1の出力信号CKVと2分周器F後の基準信号FREFのパルスエッジの差を時間間隔として計測する。出力値は小数部分周に相当するデジタル値となる。

【0024】

サンプラ5は、2分周器F後の基準信号FREFの立上りエッジをDCO1の出力信号CKVの立上りエッジに同期させ、リタイミングされた基準信号CKRを出力する。基準信号CKRにより系全体が同期動作する。例えば、基準位相アキュムレータ6やサンプラ9は、基準信号CKRに基づいてデータ更新タイミングを同期させる。

【0025】

基準位相アキュムレータ6は、分周データFCWを基準信号CKRのタイミングで累積し、位相検出器10に出力する。乗算器7は、DCO1におけるDCO分周周期とTDC4の出力の周期を調整するための正規化係数を乗じる。

【0026】

可変位相アキュムレータ8は、DCO1の出力信号CKVの立ち上がりエッジ毎に+1カウントアップし、そのデジタル値を出力する。サンプラ9は、基準信号CKRの立ち上がりエッジで可変位相アキュムレータ8からの出力値を位相検出器10へ出力する。すなわち、基準信号CKRの周期にDCO1の出力信号CKVの周期が何パルスあるかを計測していることになる。これは整数分周に相当するデジタルデータとなる。

【0027】

位相検出器10は、基準位相アキュムレータ6の出力値、乗算器7の出力値、サンプラ9の出力値を演算により比較し、位相誤差としてループフィルタ11へ出力する。ループフィルタ11の出力は、ゲイン正規化回路12へ入力される。

【0028】

ゲイン正規化回路12は、ループフィルタ11の出力を元に、PVT bits、Acquisition bits、Tracking(integer) bits、及びTracking(fractional) bitsのデジタル信号を出力する。

【0029】

アナログPLL回路Aは、EXOR型位相比較器21、分周器22、チャージポンプ23及びループフィルタ24から構成される。

【0030】

EXOR型位相比較器21は、基準信号fr及び分周器22後のDCO1の出力信号CKVを入力して、チャージポンプ23と合わせてこれらの信号についてのアナログ位相差信号を出力する。ループフィルタ24は、チャージポンプ23からアナログ位相差信号を入力して、位相同期動作に不要な高周波成分を除去する。DCO1は、ループフィルタ24からアナログ位相差信号を入力して、出力周波数及び出力位相を調整する。

【0031】

DCO1は、切替制御部SがデジタルPLL回路Dのデジタル位相比較器を利用するときには、DCOとして機能するが、切替制御部SがアナログPLL回路Aのアナログ位相比較器を利用するときには、VCO及びDCOとして機能する。

【0032】

(実施形態1)

次に、実施形態1の切替制御について説明する。DCO1は、発振部に対応し、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力する。位相検出器10は、デジタル位相比較部に対応し、位相差を示すデジタル信号を出力する。EXOR型位相比較器21は、アナログ位相比較部に対応し、位相差を示すアナログ信号を出力し、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有する。

【0033】

デジタル位相検波特性を図2に示す。位相検出器10は、位相差とデジタル信号の間にステップ特性を有する。1ステップ分の位相差は、最下位1bit分の位相差である。

【0034】

アナログ位相検波特性を図3に示す。EXOR型位相比較器21は、位相差とアナログ信号の間に線形特性を有する。位相差の検出の範囲は、デジタル信号の最下位1ビットに相当する範囲であり、位相差として0を含む範囲である。

【0035】

最初のロック動作において、切替制御部Sは、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える。

【0036】

最初のロック動作の処理を図4に示す。切替制御部Sは、位相比較の主体を位相検出器10にセットする。ゲイン正規化回路12は、DCO1に、PVT bits、Acquisition bits、及びTracking bitsの順序で、デジタル信号を出力して、段階的な位相の引き込みを行う(ステップS1)。

【0037】

切替制御部Sは、位相検出器10が出力するデジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったことを検出する(ステップS2)。そして、切替制御部Sは、DCO1が参照するデジタル信号をホールドする(ステップS3)。さらに、切替制御部Sは、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える(ステップS4)。

【0038】

つまり、デジタルPLL回路Dを利用して、ある程度の精度まで位相の引き込みを行った後に、アナログPLL回路Aを利用して、当該程度の精度を保ったうえでさらに高い精度まで位相の調整を行う。よって、最初のロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路Pを提供することができる。

【0039】

アンロックからのロック動作において、切替制御部Sは、アナログ信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内を外れたとき、位相比較の主体をEXOR型位相比較器21から位相検出器10へ切り替える。

【0040】

アンロックからのロック動作の処理を図5に示す。切替制御部Sは、EXOR型位相比較器21が出力するアナログ信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内を外れたことを検出する(ステップS11)。そして、切替制御部Sは、位相比較の主体をEXOR型位相比較器21から位相検出器10へ切り替えて、ステップS3のデジタル信号のホールドを解く(ステップS12)。

【0041】

ここで、位相差が上述の範囲内を大きく外れることはないならば、ゲイン正規化回路12は、DCO1に、Tracking bitsのみのデジタル信号を出力して、位相の引き込みを行えばよい(ステップS13)。しかし、位相差が上述の範囲内を大きく外れることがあるならば、ゲイン正規化回路12は、PVT bits、Acquisition bits、及びTracking bitsの順序で、デジタル信号を出力して、段階的な位相の引き込みを行えばよい。ステップS14からステップS16までは、それぞれステップS2からステップS4までと同様である。

【0042】

つまり、デジタルPLL回路Dを利用して行った位相の引き込みの精度を確保できなくなったときに、デジタルPLL回路Dを利用して、当該程度の精度まで位相の引き込みを行った後に、アナログPLL回路Aを利用して、当該程度の精度を保ったうえでさらに高い精度まで位相の調整を行う。よって、アンロックからのロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路Pを提供することができる。

【0043】

(実施形態2)

次に、実施形態2の切替制御について説明する。DCO1及び位相検出器10は、実施形態1、2で同様である。EXOR型位相比較器21は、アナログ位相比較部に対応し、位相差を示すアナログ信号を出力し、デジタル信号の下位mビット(m>1)に相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有する。

【0044】

デジタル位相検波特性は、実施形態1、2で同様である。アナログ位相検波特性を図6に示す。EXOR型位相比較器21は、位相差とアナログ信号の間に線形特性を有する。位相差の検出の範囲は、デジタル信号の下位mビット(m>1)に相当する範囲であり、位相差として0を含む範囲である。つまり、EXOR型位相比較器21の位相差の検出範囲(デジタル信号の下位mビット分)は、位相検出器10の位相差の検出精度(デジタル信号の最下位1ビット分)より広く設定されている。

【0045】

最初のロック動作の処理は、実施形態1、2で同様である。アンロックからのロック動作の処理を図7に示す。切替制御部Sは、EXOR型位相比較器21が出力するアナログ信号が示す位相差が、デジタル信号の下位nビット(m>n>1)に相当し位相差として0を含む位相差の範囲内を外れたことを検出する(ステップS21)。実施形態1ではm=1である一方、実施形態2ではm>1であるため、実施形態2において実施形態1に加えてさらに、上記の位相差が上記の範囲内をいずれの方向に外れたかを認識するPLL回路Pを提供することができる。ステップS22からステップS26までは、それぞれステップS12からステップS16までと同様である。

【産業上の利用可能性】

【0046】

本発明に係るPLL回路は、C/Nの向上及び高速な周波数の切り替えを両立できるため、高いC/Nが要求されてDCOが外付けとなる業務用無線機などにも対応できる。

【符号の説明】

【0047】

P:PLL回路

D:デジタルPLL回路

A:アナログPLL回路

S:切替制御部

F:2分周器

1:DCO

2:D/A

3:LPF

4:TDC

5:サンプラ

6:基準位相アキュムレータ

7:乗算器

8:可変位相アキュムレータ

9:サンプラ

10:位相検出器

11:ループフィルタ

12:ゲイン正規化回路

21:EXOR型位相比較器

22:分周器

23:チャージポンプ

24:ループフィルタ

【技術分野】

【0001】

本発明は、基準信号に基づいて所望の周波数の信号を出力するPLL(Phase−Locked Loop)回路に関する。

【背景技術】

【0002】

無線通信回路の周波数シンセサイザやクロック生成回路においてPLL回路が用いられている。近年、低電源電圧での動作が可能であり、チップサイズを縮小できるオールデジタルPLL(ADPLL)回路が研究されている(例えば、非特許文献1を参照。)。

【0003】

ADPLL回路は、アナログPLL回路の電圧制御発振器(VCO:Voltage Contorolled Oscillator)及びアナログ位相比較器の代替として、可変周波数発振器(DCO:Digitally Controlled Oscillator)及びデジタル位相比較器を備える。

【先行技術文献】

【非特許文献】

【0004】

【非特許文献1】“ALL−DIGITAL FREQUENCY SYNTHEZSIZER in DEEP−SUBMICRON CMOS” Robert Bogdan Staszewski/Poras T.Balsara 著

【発明の概要】

【発明が解決しようとする課題】

【0005】

デジタル位相比較器は、位相差とデジタル信号の間にステップ特性を有するため、DCOの制御電圧に対して制御されていない揺らぎを発生させて、C/Nを劣化させる。ここで、デジタル位相比較器は、デジタル信号のビット数を増やすならば、DCOの制御電圧に対して制御されていない揺らぎを小さくすることはできるがなくすことはできない。

【0006】

アナログ位相比較器(特にEXOR型)は、位相差とアナログ信号の間に線形特性を有するため、VCOの制御電圧に対して制御されていない揺らぎを発生させず、C/Nを向上させる。しかし、アナログ位相比較器は、高速な周波数の切り替えはできない。

【0007】

そこで、前記課題を解決するために、本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記目的を達成するために、ロック動作を開始する際には、デジタル位相比較器を利用することにより、高速な周波数の切り替えを実現して、ロック動作を終了した後には、アナログ位相比較器を利用することにより、C/Nの向上を実現することとした。

【0009】

具体的には、本発明は、基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振部と、前記位相差を示すデジタル信号を出力するデジタル位相比較部と、前記位相差を示すアナログ信号を出力し、前記デジタル信号の少なくとも最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有するアナログ位相比較部と、前記デジタル信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内に入ったとき、位相比較の主体を前記デジタル位相比較部から前記アナログ位相比較部へ切り替える切替制御部と、を備えることを特徴とするPLL回路である。

【0010】

この構成によれば、最初のロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することができる。

【0011】

また、本発明は、前記アナログ位相比較部は、前記デジタル信号の最下位1ビットに相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、前記アナログ信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替えることを特徴とするPLL回路である。

【0012】

この構成によれば、アンロックからのロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することができる。

【0013】

また、本発明は、前記アナログ位相比較部は、前記デジタル信号の下位mビット(m>1)に相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、前記アナログ信号が示す前記位相差が、前記デジタル信号の下位nビット(m>n>1)に相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替えることを特徴とするPLL回路である。

【0014】

この構成によれば、アンロックからのロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するうえに、上記の位相差が上記の範囲内をいずれの方向に外れたかを認識するPLL回路を提供することができる。

【発明の効果】

【0015】

本発明は、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路を提供することができる。

【図面の簡単な説明】

【0016】

【図1】本発明のPLL回路の構成を示す図である。

【図2】デジタル位相検波特性を示す図である。

【図3】アナログ位相検波特性を示す図である。

【図4】最初のロック動作の処理を示す図である。

【図5】アンロックからのロック動作の処理を示す図である。

【図6】アナログ位相検波特性を示す図である。

【図7】アンロックからのロック動作の処理を示す図である。

【発明を実施するための形態】

【0017】

添付の図面を参照して本発明の実施形態を説明する。以下に説明する実施形態は本発明の実施の例であり、本発明は以下の実施形態に制限されるものではない。

【0018】

(PLL回路の概要)

本発明のPLL回路の構成を図1に示す。PLL回路Pは、デジタルPLL回路D、アナログPLL回路A、切替制御部S及び2分周器Fから構成される。PLL回路Pが最初のロック動作を開始する際には、切替制御部SはデジタルPLL回路Dのデジタル位相比較器を利用する一方で、PLL回路Pが最初のロック動作を終了した後には、切替制御部SはアナログPLL回路Aのアナログ位相比較器を利用する。PLL回路Pがアンロックからのロック動作を開始する際には、切替制御部SはデジタルPLL回路Dのデジタル位相比較器を利用する一方で、PLL回路Pがアンロックからのロック動作を終了した後には、切替制御部SはアナログPLL回路Aのアナログ位相比較器を利用する。

【0019】

デジタルPLL回路Dは、DCO1、D/A(Digital−Analog Converter)2、LPF(Low Pass Filter)3、TDC4、サンプラ5、基準位相アキュムレータ6、乗算器7、可変位相アキュムレータ8、サンプラ9、位相検出器10、ループフィルタ11及びゲイン正規化回路12から構成される。

【0020】

DCO1は、バラクタ(可変容量ダイオード)配列を持ち、発振周波数を2進数コードで制御することができる。ここで、DCO1の発振周波数が広帯域で、切り替え周波数間隔が小さい場合は、バラクタのbit数が実現不可能なほど多くなることがある。そこで、段階的なステップで周波数範囲を小さくし、周波数分解能を改善する方法(ディスクリートチューニング)で、実現可能なバラクタ配列を構成することができる。

【0021】

例えば、2進数コードが入力される複数のバンクを持つバラクタ配列がある。第一バンクは400MHzの可変範囲で2316kHzの周波数間隔でロックができ、第二バンクは118MHzの可変範囲で461kHzの周波数間隔でロックができ、第三バンクは1.5MHzの可変範囲で、23kHzの周波数間隔でロックができる。第一バンク、第二バンク、第三バンクは、それぞれPVTバンク、Acquisitionバンク、Tracking(integer)バンクと呼ばれることがある。そして、第三バンクの1bitにあたるバラクタサイズが基本的に最小サイズになる。

【0022】

デジタルPLL回路Dへの要求として、上記第三バンクでロックできる周波数間隔より狭い間隔の周波数でロックすることが求められることもある。この場合、下位ビットを

D/A2でアナログ電圧に変換してバラクタに入力する。D/A2は、下位ビットとなるTracking bits(fractional)を、DCO1のコントロール電圧に変換して、DCO1のバラクタを制御する。LPF3は、D/A2が出力するアナログ信号について、高周波成分を除去して、DCO1のバラクタに入力する。D/A2の同期用信号として、リタイミングされた基準信号CKRを使用する。

【0023】

TDC(Time−to−Digital Converter)4は、DCO1の出力信号CKVと2分周器F後の基準信号FREFのパルスエッジの差を時間間隔として計測する。出力値は小数部分周に相当するデジタル値となる。

【0024】

サンプラ5は、2分周器F後の基準信号FREFの立上りエッジをDCO1の出力信号CKVの立上りエッジに同期させ、リタイミングされた基準信号CKRを出力する。基準信号CKRにより系全体が同期動作する。例えば、基準位相アキュムレータ6やサンプラ9は、基準信号CKRに基づいてデータ更新タイミングを同期させる。

【0025】

基準位相アキュムレータ6は、分周データFCWを基準信号CKRのタイミングで累積し、位相検出器10に出力する。乗算器7は、DCO1におけるDCO分周周期とTDC4の出力の周期を調整するための正規化係数を乗じる。

【0026】

可変位相アキュムレータ8は、DCO1の出力信号CKVの立ち上がりエッジ毎に+1カウントアップし、そのデジタル値を出力する。サンプラ9は、基準信号CKRの立ち上がりエッジで可変位相アキュムレータ8からの出力値を位相検出器10へ出力する。すなわち、基準信号CKRの周期にDCO1の出力信号CKVの周期が何パルスあるかを計測していることになる。これは整数分周に相当するデジタルデータとなる。

【0027】

位相検出器10は、基準位相アキュムレータ6の出力値、乗算器7の出力値、サンプラ9の出力値を演算により比較し、位相誤差としてループフィルタ11へ出力する。ループフィルタ11の出力は、ゲイン正規化回路12へ入力される。

【0028】

ゲイン正規化回路12は、ループフィルタ11の出力を元に、PVT bits、Acquisition bits、Tracking(integer) bits、及びTracking(fractional) bitsのデジタル信号を出力する。

【0029】

アナログPLL回路Aは、EXOR型位相比較器21、分周器22、チャージポンプ23及びループフィルタ24から構成される。

【0030】

EXOR型位相比較器21は、基準信号fr及び分周器22後のDCO1の出力信号CKVを入力して、チャージポンプ23と合わせてこれらの信号についてのアナログ位相差信号を出力する。ループフィルタ24は、チャージポンプ23からアナログ位相差信号を入力して、位相同期動作に不要な高周波成分を除去する。DCO1は、ループフィルタ24からアナログ位相差信号を入力して、出力周波数及び出力位相を調整する。

【0031】

DCO1は、切替制御部SがデジタルPLL回路Dのデジタル位相比較器を利用するときには、DCOとして機能するが、切替制御部SがアナログPLL回路Aのアナログ位相比較器を利用するときには、VCO及びDCOとして機能する。

【0032】

(実施形態1)

次に、実施形態1の切替制御について説明する。DCO1は、発振部に対応し、基準信号FREFと出力信号CKVの間の位相差が0になるような出力信号CKVを出力する。位相検出器10は、デジタル位相比較部に対応し、位相差を示すデジタル信号を出力する。EXOR型位相比較器21は、アナログ位相比較部に対応し、位相差を示すアナログ信号を出力し、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有する。

【0033】

デジタル位相検波特性を図2に示す。位相検出器10は、位相差とデジタル信号の間にステップ特性を有する。1ステップ分の位相差は、最下位1bit分の位相差である。

【0034】

アナログ位相検波特性を図3に示す。EXOR型位相比較器21は、位相差とアナログ信号の間に線形特性を有する。位相差の検出の範囲は、デジタル信号の最下位1ビットに相当する範囲であり、位相差として0を含む範囲である。

【0035】

最初のロック動作において、切替制御部Sは、デジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったとき、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える。

【0036】

最初のロック動作の処理を図4に示す。切替制御部Sは、位相比較の主体を位相検出器10にセットする。ゲイン正規化回路12は、DCO1に、PVT bits、Acquisition bits、及びTracking bitsの順序で、デジタル信号を出力して、段階的な位相の引き込みを行う(ステップS1)。

【0037】

切替制御部Sは、位相検出器10が出力するデジタル信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内に入ったことを検出する(ステップS2)。そして、切替制御部Sは、DCO1が参照するデジタル信号をホールドする(ステップS3)。さらに、切替制御部Sは、位相比較の主体を位相検出器10からEXOR型位相比較器21へ切り替える(ステップS4)。

【0038】

つまり、デジタルPLL回路Dを利用して、ある程度の精度まで位相の引き込みを行った後に、アナログPLL回路Aを利用して、当該程度の精度を保ったうえでさらに高い精度まで位相の調整を行う。よって、最初のロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路Pを提供することができる。

【0039】

アンロックからのロック動作において、切替制御部Sは、アナログ信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内を外れたとき、位相比較の主体をEXOR型位相比較器21から位相検出器10へ切り替える。

【0040】

アンロックからのロック動作の処理を図5に示す。切替制御部Sは、EXOR型位相比較器21が出力するアナログ信号が示す位相差が、デジタル信号の最下位1ビットに相当し位相差として0を含む位相差の範囲内を外れたことを検出する(ステップS11)。そして、切替制御部Sは、位相比較の主体をEXOR型位相比較器21から位相検出器10へ切り替えて、ステップS3のデジタル信号のホールドを解く(ステップS12)。

【0041】

ここで、位相差が上述の範囲内を大きく外れることはないならば、ゲイン正規化回路12は、DCO1に、Tracking bitsのみのデジタル信号を出力して、位相の引き込みを行えばよい(ステップS13)。しかし、位相差が上述の範囲内を大きく外れることがあるならば、ゲイン正規化回路12は、PVT bits、Acquisition bits、及びTracking bitsの順序で、デジタル信号を出力して、段階的な位相の引き込みを行えばよい。ステップS14からステップS16までは、それぞれステップS2からステップS4までと同様である。

【0042】

つまり、デジタルPLL回路Dを利用して行った位相の引き込みの精度を確保できなくなったときに、デジタルPLL回路Dを利用して、当該程度の精度まで位相の引き込みを行った後に、アナログPLL回路Aを利用して、当該程度の精度を保ったうえでさらに高い精度まで位相の調整を行う。よって、アンロックからのロック動作において、C/Nの向上及び高速な周波数の切り替えを両立するPLL回路Pを提供することができる。

【0043】

(実施形態2)

次に、実施形態2の切替制御について説明する。DCO1及び位相検出器10は、実施形態1、2で同様である。EXOR型位相比較器21は、アナログ位相比較部に対応し、位相差を示すアナログ信号を出力し、デジタル信号の下位mビット(m>1)に相当し位相差として0を含む位相差の範囲内で、位相差とアナログ信号の間の線形特性を有する。

【0044】

デジタル位相検波特性は、実施形態1、2で同様である。アナログ位相検波特性を図6に示す。EXOR型位相比較器21は、位相差とアナログ信号の間に線形特性を有する。位相差の検出の範囲は、デジタル信号の下位mビット(m>1)に相当する範囲であり、位相差として0を含む範囲である。つまり、EXOR型位相比較器21の位相差の検出範囲(デジタル信号の下位mビット分)は、位相検出器10の位相差の検出精度(デジタル信号の最下位1ビット分)より広く設定されている。

【0045】

最初のロック動作の処理は、実施形態1、2で同様である。アンロックからのロック動作の処理を図7に示す。切替制御部Sは、EXOR型位相比較器21が出力するアナログ信号が示す位相差が、デジタル信号の下位nビット(m>n>1)に相当し位相差として0を含む位相差の範囲内を外れたことを検出する(ステップS21)。実施形態1ではm=1である一方、実施形態2ではm>1であるため、実施形態2において実施形態1に加えてさらに、上記の位相差が上記の範囲内をいずれの方向に外れたかを認識するPLL回路Pを提供することができる。ステップS22からステップS26までは、それぞれステップS12からステップS16までと同様である。

【産業上の利用可能性】

【0046】

本発明に係るPLL回路は、C/Nの向上及び高速な周波数の切り替えを両立できるため、高いC/Nが要求されてDCOが外付けとなる業務用無線機などにも対応できる。

【符号の説明】

【0047】

P:PLL回路

D:デジタルPLL回路

A:アナログPLL回路

S:切替制御部

F:2分周器

1:DCO

2:D/A

3:LPF

4:TDC

5:サンプラ

6:基準位相アキュムレータ

7:乗算器

8:可変位相アキュムレータ

9:サンプラ

10:位相検出器

11:ループフィルタ

12:ゲイン正規化回路

21:EXOR型位相比較器

22:分周器

23:チャージポンプ

24:ループフィルタ

【特許請求の範囲】

【請求項1】

基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振部と、

前記位相差を示すデジタル信号を出力するデジタル位相比較部と、

前記位相差を示すアナログ信号を出力し、前記デジタル信号の少なくとも最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有するアナログ位相比較部と、

前記デジタル信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内に入ったとき、位相比較の主体を前記デジタル位相比較部から前記アナログ位相比較部へ切り替える切替制御部と、

を備えることを特徴とするPLL回路。

【請求項2】

前記アナログ位相比較部は、前記デジタル信号の最下位1ビットに相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、

前記アナログ信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替える

ことを特徴とする、請求項1に記載のPLL回路。

【請求項3】

前記アナログ位相比較部は、前記デジタル信号の下位mビット(m>1)に相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、

前記アナログ信号が示す前記位相差が、前記デジタル信号の下位nビット(m>n>1)に相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替える

ことを特徴とする、請求項1に記載のPLL回路。

【請求項1】

基準信号と出力信号の間の位相差が0になるような前記出力信号を出力する発振部と、

前記位相差を示すデジタル信号を出力するデジタル位相比較部と、

前記位相差を示すアナログ信号を出力し、前記デジタル信号の少なくとも最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有するアナログ位相比較部と、

前記デジタル信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内に入ったとき、位相比較の主体を前記デジタル位相比較部から前記アナログ位相比較部へ切り替える切替制御部と、

を備えることを特徴とするPLL回路。

【請求項2】

前記アナログ位相比較部は、前記デジタル信号の最下位1ビットに相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、

前記アナログ信号が示す前記位相差が、前記デジタル信号の最下位1ビットに相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替える

ことを特徴とする、請求項1に記載のPLL回路。

【請求項3】

前記アナログ位相比較部は、前記デジタル信号の下位mビット(m>1)に相当する前記位相差の範囲内で、前記位相差と前記アナログ信号の間の線形特性を有し、

前記アナログ信号が示す前記位相差が、前記デジタル信号の下位nビット(m>n>1)に相当し前記位相差として0を含む前記位相差の範囲内を外れたとき、前記切替制御部は、位相比較の主体を前記アナログ位相比較部から前記デジタル位相比較部へ切り替える

ことを特徴とする、請求項1に記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2013−58881(P2013−58881A)

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願番号】特願2011−195587(P2011−195587)

【出願日】平成23年9月8日(2011.9.8)

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

【公開日】平成25年3月28日(2013.3.28)

【国際特許分類】

【出願日】平成23年9月8日(2011.9.8)

【出願人】(000004330)日本無線株式会社 (1,186)

【Fターム(参考)】

[ Back to top ]