PLL回路

【課題】出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路を提供する。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

【解決手段】流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えたPLL回路とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、クロック信号を生成するPLL[Phase Locked Loop]回路に関する。

【背景技術】

【0002】

従来、種々の電気機器においてPLL回路が利用されている。ここで従来のPLL回路の構成について、主にアナログ信号を処理する形式(アナログ形式)のPLL回路、および、主にデジタル信号を処理する形式(デジタル形式)のPLL回路を例に挙げ、以下に簡潔に説明する。

【0003】

図11は、アナログ形式のPLL回路100の構成図である。本図に示すようにPLL回路100は、比較器(位相周波数比較器)101、チャージポンプ102、ローパスフィルタ103、電圧制御発振回路104、および分周器105を有する。

【0004】

比較器101は、リファレンス周波数信号および分周器105の出力信号が入力され、これらの位相比較の結果に応じて、パルス信号UPまたはパルス信号DNを出力する。またチャージポンプ102は、流出または流入の出力電流を出力するものであって、パルス信号UPに応じて流出の出力電流のオン/オフが切替えられ、パルス信号DNに応じて流入の出力電流のオン/オフが切替えられるように構成されている。

【0005】

ローパスフィルタ103は、チャージポンプ102の出力側に設けられており、入力電圧に低域通過のフィルタ処理を施して、電圧制御発振回路104に出力する。また電圧制御発振回路104は、ローパスフィルタ103の出力電圧に応じた周波数のクロック信号を、出力クロック信号Soutとして生成する。

【0006】

生成された出力クロック信号Soutは、PLL回路100の外部に出力されるとともに、分周器105に入力される。分周器105に入力された出力クロック信号Soutは、分周の処理が施された上で、比較器101へ出力される。PLL回路100によれば、例えばリファレンス周波数信号が1MHzであり、分周器105が2分周を行う場合に、2MHzの出力クロック信号Soutが得られる。

【0007】

但しPLL回路100によれば、リファレンス周波数信号としてデジタル信号(例えば、AD変換された後の信号)が入力される場合には、上述した位相比較を適切に行うことが難しくなる。これに対し、デジタル形式のPLL回路200の構成図を図12に示す。本図に示すようにPLL回路200は、比較器101や分周器105の代わりに、デジタル回路として構成されたカウンタA、カウンタB、および比較器201を有する。

【0008】

カウンタAは、リファレンス周波数信号のクロックをカウントし、カウンタBは、出力クロック信号Soutのクロックをカウントする。また比較器201は、各カウンタによるカウント結果の大小関係に応じて、パルス信号UPまたはパルス信号DNを出力する。

【0009】

図13は、1MHzのリファレンス周波数信号から2MHzの出力クロック信号Soutが得られるようにした場合における、各カウンタの動作の様子を模式的に例示したものである。本図に示すように、カウンタAは100までのカウントアップを繰返し、カウンタBは200までのカウントアップを繰返すように動作する。比較器201は、各カウンタのカウントアップを繰返すタイミングにズレが発生したとき、このズレを解消させるように、パルス信号UPまたはパルス信号DNを出力する。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2008−72469号公報

【特許文献2】特許第3022870号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述したデジタル形式のPLL回路によれば、デジタル回路をFPGA等により制御することや、カウンタのカウント数を可変にすること等により、出力クロック信号の周波数を自由に変更することが可能となる。

【0012】

しかしこのようなデジタル形式の方式によれば、パルス信号UPやパルス信号DNの周波数が低下することになり(図13に示す例では、リファレンス周波数信号の1/100程度となる)、出力クロック信号の周波数制御を精度良く行うことが、難しくなるおそれがある。

【0013】

本発明は上述した問題に鑑み、出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路の提供を目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するため本発明に係るPLL回路は、流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えた構成とする。

【0015】

本構成によれば、参照信号に応じてチャージポンプの出力電流の電流量を調節するため、出力クロック信号の周波数制御を精度良く行うことが容易となる。

【0016】

また上記構成としてより具体的には、前記参照信号は、正弦波を表すデジタル信号である構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記パルス信号として、前記流出のオン/オフを切替えるUP信号、および、前記流入のオン/オフを切替えるDN信号を生成する構成としてもよい。

【0017】

また上記構成としてより具体的には、前記チャージポンプの出力側に設けられたローパスフィルタと、前記ローパスフィルタの出力電圧に応じた周波数のクロック信号を、前記出力クロック信号として生成する電圧制御発振回路と、を備えた構成としてもよい。

【0018】

また前記参照信号の目標波形を表す目標波形信号を生成する、上記構成のPLL回路において、前記電流量調節部は、前記参照信号と前記目標波形信号との差分値に応じて、前記電流量を調節する構成としてもよい。

【0019】

また上記構成としてより具体的には、前記電流量調節部は、前記差分値の絶対値が大きいほど、前記電流量が大きくなるように前記調節を行う構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記参照信号と前記目標波形信号との差の符号に応じて、UP信号とDN信号の何れを生成するかを決める構成としてもよい。

【0020】

また上記構成としてより具体的には、前記電流量調節部は、前記参照信号の積分値に応じて、前記電流量を調節する構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記参照信号の積分値の符号に応じて、UP信号とDN信号の何れを生成するかを決める構成としてもよい。

【0021】

また前記参照信号がゼロクロスとなるべきタイミングである、ゼロクロスタイミングを特定する上記構成のPLL回路において、前記電流量調節部は、前記ゼロクロスタイミングにおける、前記参照信号とゼロとの差分値に応じて、前記電流量を調節する構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記ゼロクロスタイミングにおける、前記参照信号とゼロとの差の符号に応じて、UP信号とDN信号の何れを生成するかを決める構成としてもよい。

【0022】

また上記構成としてより具体的には、前記参照信号に対して移動平均の算出処理を施す、移動平均算出回路を備えた構成としてもよい。また上記構成としてより具体的には、前記参照信号に対してフィルタ処理を施す、バンドパスフィルタを備えた構成としてもよい。

【発明の効果】

【0023】

上述した通り、本発明に係るPLL回路によれば、参照信号に応じてチャージポンプの出力電流の電流量を調節するため、出力クロック信号の周波数制御を精度良く行うことが容易となる。

【図面の簡単な説明】

【0024】

【図1】本発明の実施形態に係るPLL回路の構成図である。

【図2】本発明の実施形態に係るチャージポンプの構成図である。

【図3】第1実施形態に係るCP制御回路の構成図である。

【図4】第1実施形態に係るCP制御回路の動作に関わる説明図である。

【図5】第2実施形態に係るCP制御回路の動作に関わる説明図である。

【図6】第3実施形態に係るCP制御回路の構成図である。

【図7】第3実施形態に係るCP制御回路の動作に関わる説明図である。

【図8】第4実施形態に係るCP制御回路の構成図である。

【図9】第4実施形態に係るCP制御回路の動作に関わる説明図である。

【図10】第5実施形態に係るCP制御回路の構成図である。

【図11】従来のアナログ形式のPLL回路の構成図である。

【図12】従来のデジタル形式のPLL回路の構成図である。

【図13】カウンタの動作に関する説明図である。

【発明を実施するための形態】

【0025】

本発明の実施形態について、第1実施形態から第5実施形態の各々を例に挙げて、以下に説明する。

【0026】

1.第1実施形態

[PLL回路の全体構成]

まず第1実施形態について説明する。図1は、本実施形態に係るPLL回路9の構成図である。本図に示すようにPLL回路9は、正弦波生成部1、ADコンバータ2、チャージポンプ制御回路(以下、「CP制御回路」と称する)3、チャージポンプ4、ローパスフィルタ5、電圧制御発振回路6、およびゼロクロス信号生成回路7を有している。

【0027】

正弦波生成部1は、所定周期の正弦波(サイン波)のアナログ信号を生成して、後段側のADコンバータ2に出力する。ADコンバータ2は、前段側から受取るアナログ信号に対してAD[Analog to Digital]変換を実行し、変換済みのデジタル信号(正弦波を表すデジタル信号)を参照信号SrefとしてCP制御回路3に送出する。

【0028】

なおPLL回路9においては、正弦波生成部1やADコンバータ2が設けられる代わりに、参照信号Srefに相当する信号が外部から入力されるようになっていても良い。また参照信号Srefは、周期性を有する多値の信号であって、正弦波とは異なる形態であっても構わない。ここで本願における「多値の信号」とは、少なくとも3種以上の値となる信号であり、2値のパルス信号などを含まない概念である。なお参照信号Srefは周期性を有するため、クロック信号の一種(リファレンスクロック信号)と見ることも出来る。

【0029】

CP制御回路3は、参照信号Srefに基づいて、パルス信号UP、パルス信号DN、および調節信号SELを生成するデジタル回路である。CP制御回路3は、これらの信号をチャージポンプ4に送出することにより、チャージポンプ4の動作を制御する。パルス信号UPおよびパルス信号DNは、2値(HレベルとLレベル)のパルス信号であり、各値がオンおよびオフの何れかを表す。なお、CP制御回路3のより詳細な構成等については、改めて説明する。

【0030】

チャージポンプ4は、流出または流入の出力電流を出力するものであって、パルス信号UPに応じて当該流出のオン/オフが切替えられ、パルス信号DNに応じて当該流入のオン/オフが切替えられるように形成されている。

【0031】

すなわちチャージポンプ4は、パルス信号UPがオンのときに、自身から出力側(LPF5)へ電流を流出させる(つまり、「流出」の出力電流を出力する)ようにし、パルス信号DNがオンのときに、出力側から自身へ電流を流入させる(つまり、「流入」の出力電流を出力する)ように動作する。チャージポンプ4の出力電流によって、ローパスフィルタ5に入力される電圧が決められる。

【0032】

またチャージポンプ4は、調節信号SELに応じて、出力電流がオンであるときの電流量が変化するように形成されている。ここでチャージポンプ4の構成例について、図2を参照しながら以下に説明する。なおこの例では、調節信号SELは、複数の信号(SEL−1〜SEL−6)からなっている。

【0033】

図2に示すようにチャージポンプ4は、UP側のPMOSトランジスタT1と、DOWN側のNMOSトランジスタT2とを備える。PMOSトランジスタT1は、ゲートにはパルス信号UPが入力されるようになっており、ソースには、電流可変用のPMOSトランジスタT3〜T5のドレインが共通接続される。PMOSトランジスタT3〜T5はそれぞれ、ソースが電源に接続され、ゲートに信号SEL−1〜SEL−3が供給される。

【0034】

またNMOSトランジスタT2は、ゲートにはパルス信号DNが入力されるようになっており、ソースには、電流可変用のNMOSトランジスタT6〜T8のドレインが共通接続される。NMOSトランジスタT6〜T8はそれぞれ、ソースが接地され、ゲートに信号SEL−4〜SEL−6が供給される。

【0035】

図2に示す構成によれば、パルス信号UPのオン時に、チャージポンプ4からローパスフィルタ5へ電流が流出する。そしてこの流出に係る電流量は、主に信号SEL−1〜SEL−3に応じて(つまり、PMOSトランジスタT3〜T5のうちの何れがオンとなるかに応じて)変化する。

【0036】

またパルス信号DNのオン時に、ローパスフィルタ5からチャージポンプ4へ電流が流入する。そしてこの流入に係る電流量は、主に信号SEL−4〜SEL−6に応じて(つまり、NMOSトランジスタT6〜T8のうちの何れがオンとなるかに応じて)変化する。なお図2に示した構成は一例であって、チャージポンプ4はその他の構成となっていても構わない。

【0037】

図1に戻り、ローパスフィルタ5は、チャージポンプ4の出力側に設けられており、入力電圧に低域通過のフィルタ処理を施して、電圧制御発振回路6に出力する。また電圧制御発振回路6は、ローパスフィルタ5の出力電圧に応じた周波数のクロック信号(方形波)を、出力クロック信号Soutとして生成する。生成された出力クロック信号Soutは、PLL回路9の外部に出力され、種々の目的に利用される。

【0038】

なおPLL回路9は所定の機構(参照信号Srefと出力クロック信号Soutのクロックをカウントして比較する機構や、分周器を用いる機構等であっても構わない)を用いて、参照信号Srefに対応した周波数となるように、出力クロック信号Soutを生成する。本実施形態ではその一例として、125kHzの参照信号Srefに基づいて、これが16逓倍された2MHzの出力クロック信号Soutが生成されるとする。

【0039】

またADコンバータ2、CP制御回路3、およびゼロクロス信号生成回路7には、基準クロックCLの信号が入力されるようになっている。ADコンバータ2は、基準クロックCLの周期でAD変換を行うようになっており、CP制御回路3は、基準クロックCLに応じて所定動作(詳しくは後述する)を行うようになっている。

【0040】

なお基準クロックCLの信号としては、出力クロック信号Soutが用いられるようにしても良く、別途生成されたクロック信号が用いられるようにしても良い。なお以下の説明では、基準クロックCLの周波数は、参照信号Srefが16逓倍されたものであるとする。

【0041】

ゼロクロス信号生成回路7は、ゼロクロスタイミング(参照信号Srefがゼロクロスとなるべきタイミング)を検知し、ゼロクロスタイミングを表す信号をCP制御回路3に出力する。ゼロクロス信号生成回路7は、一例として、まず参照信号Srefの符号反転検出を行って初めのゼロクロスのタイミングを検知し、その後、基準クロックCLを用いて参照信号Srefの周期(本実施形態では16回分の基準クロックCL)をカウントすることで、永続的にゼロクロスタイミングを検知することが可能である。なお、CP制御回路3が行う処理においてゼロクロスタイミングの情報が不要である場合には、ゼロクロス信号生成回路7は設けられなくても良い。

【0042】

[CP制御回路の構成]

次に、CP制御回路3の構成等についてより詳細に説明する。図3は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、パルス信号生成回路32、目標波形生成回路33、およびコンパレータ34を有している。

【0043】

電流量調節回路31は、入力される信号(本実施形態では、後述する差分信号)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。パルス生成回路32は、入力される信号(本実施形態では、後述する差分信号)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。

【0044】

目標波形生成回路33は、参照信号Srefの目標波形(本実施形態では125kHzの正弦波)の信号を生成する回路である。目標波形生成回路33は、例えば、基準クロックCLの間隔での目標波形の値を表すLUT[Look up Table]が用意されており、基準クロックCLと当該LUTを用いることにより、目標波形の信号を生成する。

【0045】

コンパレータ34は、参照信号Srefの値と目標波形の信号の値との差分値(便宜的に「差分値D1」とする)を算出し、算出結果の信号を差分信号として、後段側に送出する。なおコンパレータ34における当該算出は、例えばゼロクロスタイミングの情報が利用され、参照信号Srefと目標波形を同期させるようにして実行される。

【0046】

[CP制御回路の動作]

次に、CP制御回路3の動作についてより詳細に説明する。電流量調節回路31は、差分信号が表す差分値D1に応じて、調節信号SELを生成する。より具体的には、差分値D1の絶対値が大きいほどチャージポンプ4での電流量が増大するように、調節信号SELが生成される。一例としては、差分値D1の絶対値(或いはこれに所定係数を乗じた値)が、チャージポンプ4での電流量となるように、調節信号SELが生成される。調節信号SELは、差分値D1の絶対値が出来るだけ速やかに小さくなるように、適切に生成されることが望ましい。

【0047】

またパルス生成回路32は、差分信号が表す差分値D1の符号に応じて、パルス信号UPおよびパルス信号DNを生成する。より具体的には、パルス信号DNについては、差分値D1が正であればオンとし、そうでないときはオフとする。またパルス信号UPについては、差分値D1が負であればオンとし、そうでないときはオフとする。

【0048】

また本実施形態では、コンパレータ34による差分値D1の算出は、基準クロックCLの周期毎に(つまり、基準クロックCLのタイミングで毎回)実行される。そしてこの算出結果に従って、差分信号の内容が更新される。また電流量調節回路31およびパルス生成回路32による信号生成の動作(信号内容の更新)も、当該算出のタイミングに同期して行われる。

【0049】

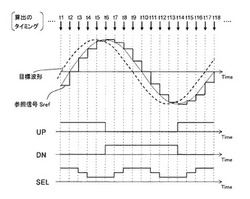

ここで図4は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図4の上段は、参照信号Sref(実線)と目標波形(破線)の様子(参照信号Srefの位相が遅れている例)を模式的に示しており、図4の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図4中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0050】

図4に示すように本実施形態では、基準クロックCLの周期毎のタイミング(図4ではt1〜t18が例示されている)において差分値D1が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0051】

このように電流量調節回路31は、参照信号Srefに応じて(より具体的には、参照信号Srefの値と目標波形の信号の値との差分値D1に応じて)、チャージポンプ4の出力電流の電流量を調節するようになっている。そのためPLL回路9は、このような調節が行われないものに比べて、差分値D1の絶対値をより速やかに小さくすること等が可能であり、出力クロック信号の周波数制御を精度良く行うことが容易である。またこれにより、パルス信号UPやパルス信号DNの周波数が小さくても、出力クロック信号Soutに関するジッタの悪化等を低減させることが容易である。

【0052】

2.第2実施形態

次に、第2実施形態について説明する。なお第2実施形態は、差分値を算出するタイミングに関する点を除き、基本的に第1実施形態と同様である。以下の説明では、第1実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0053】

第2実施形態では、コンパレータ34による差分値D1の算出は、ゼロクロスタイミングおよびその前後のタイミング(以下の説明では一例として、基準クロックCLの1周期分だけ前後のタイミングとする)においてのみ実行される。そしてこの算出結果に従って、差分信号の内容が更新される。また電流量調節回路31およびパルス生成回路32による信号生成の動作(信号内容の更新)も、当該算出のタイミングに同期して行われる。

【0054】

なお第2実施形態のゼロクロス信号生成部7は、ゼロクロスタイミングだけでなく、その前後のタイミングをも検知し、これらのタイミングを表す信号をCP制御回路3に出力するようになっている。これにより差分値D1の算出のタイミングを、ゼロクロスタイミングおよびその前後のタイミングのみとすることが可能となっている。

【0055】

ここで図5は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図5の上段は、参照信号Sref(実線)と目標波形(破線)の様子(参照信号Srefの位相が遅れている例)を模式的に示しており、図5の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図5中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0056】

図5に示すように第2実施形態では、ゼロクロスタイミングおよびその前後のタイミング(図5ではt1〜t8が例示されている)においてのみ差分値D1が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0057】

このように第2実施形態によれば、ゼロクロスタイミングおよびその前後のタイミングを除いては、差分値D1の算出が省略される。そのため参照信号Srefと目標波形の間に振幅の差があったとしても、この振幅の差が差分値D1の算出に与える影響を、極力抑えることが可能である。これにより、PLL回路9におけるジッタの悪化を低減させることが容易となる。

【0058】

3.第3実施形態

次に、第3実施形態について説明する。なお第3実施形態は、PC制御回路3の構成や動作に関する点を除き、基本的に第1実施形態と同様である。以下の説明では、第1実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0059】

図6は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、パルス信号生成回路32、および積分回路36を有している。

【0060】

電流量調節回路31は、入力される信号(本実施形態では、後述する積分信号)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。パルス生成回路32は、入力される信号(本実施形態では、後述する積分信号)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。また積分回路36は、参照信号Srefの値の積分値を算出し、算出結果の信号を積分信号として後段側に送出する。

【0061】

次に、CP制御回路3の動作についてより詳細に説明する。電流量調節回路31は、積分信号が表す積分値の絶対値と目標積分量との差分値(便宜的に「差分値D2」とする)に応じて、調節信号SELを生成する。より具体的には、差分値D2の絶対値が大きいほどチャージポンプ4での電流量が増大するように、調節信号SELが生成される。

【0062】

一例としては、差分値D2の絶対値(或いはこれに所定係数を乗じた値)が、チャージポンプ4での電流量となるように、調節信号SELが生成される。なお目標積分量は、参照信号Srefが理想波形であると仮定した場合の積分値の絶対値(つまり期待される積分値の絶対値)に相当する。参照信号Srefが理想波形である場合には、差分値D2はゼロとなる。調節信号SELは、差分値D2の絶対値が出来るだけ速やかに小さくなるように、適切に生成されることが望ましい。

【0063】

またパルス生成回路32は、差分値D2の符号に応じて、パルス信号UPおよびパルス信号DNを生成する。より具体的には、パルス信号DNについては、差分値D2が正であればオンとし、そうでないときはオフとする。またパルス信号UPについては、差分値D2が負であればオンとし、そうでないときはオフとする。

【0064】

また本実施形態では、積分回路36による積分値の算出は、ゼロクロスタイミングが到来する度に実行される。そしてこの算出結果に従って、積分信号の内容が更新される。また電流量調節回路31およびパルス生成回路32による信号生成の動作(信号内容の更新)も、当該算出のタイミングに同期して行われる。

【0065】

ここで図7は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図7の上段は、参照信号Srefの様子を模式的に示しており、図7の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図7中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0066】

図7に示すように本実施形態では、各ゼロクロスタイミング(図7ではt1〜t3が例示されている)において積分値が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0067】

なお本実施形態では、ゼロクロスタイミングごと、すなわち理想とする参照信号Srefの半周期ごとに積分値を算出するが、その代わりに、一周期ごとに積分値を算出するようにしても良い。このようにすれば目標積分量はゼロとなるため、算出される積分値をそのまま差分値D2として扱うことができ、CP制御回路3の回路構成をより簡略化することが容易となる。

【0068】

4.第4実施形態

次に、第4実施形態について説明する。なお第4実施形態は、PC制御回路3の構成や動作に関する点を除き、基本的に第1実施形態と同様である。以下の説明では、第1実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0069】

図8は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、およびパルス信号生成回路32を有している。電流量調節回路31は、入力される信号(本実施形態では、参照信号Sref)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。パルス生成回路32は、入力される信号(本実施形態では、参照信号Sref)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。

【0070】

次に、CP制御回路3の動作についてより詳細に説明する。電流量調節回路31は、参照信号Srefの値とゼロとの差分値(便宜的に「差分値D3」とする)に応じて、調節信号SELを生成する。より具体的には、差分値D3の絶対値が大きいほどチャージポンプ4での電流量が増大するように、調節信号SELが生成される。一例としては、差分値D3の絶対値(或いはこれに所定係数を乗じた値)が、チャージポンプ4での電流量となるように、調節信号SELが生成される。調節信号は、差分値D3の絶対値が出来るだけ速やかに小さくなるように、適切に生成されることが望ましい。

【0071】

またパルス生成回路32は、差分値D3の符号に応じて、パルス信号UPおよびパルス信号DNを生成する。より具体的には、パルス信号DNについては、差分値D3が正であればオンとし、そうでないときはオフとする。またパルス信号UPについては、差分値D3が負であればオンとし、そうでないときはオフとする。

【0072】

また本実施形態では、電流量調節回路31およびパルス生成回路32による信号生成は、ゼロクロスタイミングが到来する度に実行される。

【0073】

ここで図9は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図9の上段は、参照信号Srefの様子を模式的に示しており、図9の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図9中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0074】

図9に示すように本実施形態では、各ゼロクロスタイミング(図9においてt1〜t3が例示されているように、理想とする波形(本図中の破線の波形)がゼロクロスとなるタイミング)において積分値が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0075】

このように電流量調節回路31は、参照信号Srefに応じて(より具体的には、参照信号Srefの値とゼロとの差分値D3に応じて)、チャージポンプ4の出力電流の電流量を調節するようになっている。そのためPLL回路9は、このような調節が行われないものに比べて、差分値D3の絶対値をより速やかに小さくすること等が可能であり、出力クロック信号の周波数制御を精度良く行うことが容易である。またこれにより、パルス信号UPやパルス信号DNの周波数が小さくても、出力クロック信号Soutに関するジッタの悪化等を低減させることが容易である。

【0076】

5.第5実施形態

次に、第5実施形態について説明する。なお第5実施形態は、参照信号Srefの移動平均を用いるようにした点を除き、基本的に第4実施形態と同様である。以下の説明では、第4実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0077】

図10は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、パルス信号生成回路32、および移動平均算出回路37を有している。移動平均算出回路37は、入力される参照信号Srefの値の移動平均を算出し、算出結果を電流決定回路31およびパルス生成回路32に送出する。なお移動平均の算出は、例えば、直近の1/8周期分の値を用いて行われる。

【0078】

電流量調節回路31は、入力される信号(本実施形態では、参照信号Srefの値の移動平均)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。なお調節信号SELの生成手順は、参照信号Srefの値の代わりに当該移動平均の値が用いられる点を除き、第4実施形態の場合と同様である。

【0079】

パルス生成回路32は、入力される信号(本実施形態では、参照信号Srefの値の移動平均)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。なおパルス信号UPおよびパルス信号DNの生成手順は、参照信号Srefの値の代わりに当該移動平均の値が用いられる点を除き、第4実施形態の場合と同様である。

【0080】

第5実施形態では、参照信号Srefに対して移動平均が算出され、この算出結果を用いて各信号(SEL、UP、DN)が生成される。そのため、正弦波生成部1から出力される正弦波にノイズが入っていた場合であっても、各信号(SEL、UP、DN)の生成に当該ノイズの悪影響が及ぶことを、出来るだけ抑えることが可能である。

【0081】

なお第5実施形態では、第4実施形態のPLL回路9に移動平均算出回路37を設けた形態となっているが、第1実施形態から第3実施形態の何れのPLL回路9についても、移動平均算出回路37に相当するものを設けることが可能である。この場合にも、参照信号Srefに対して移動平均が算出され、この算出結果を用いて各信号(SEL、UP、DN)が生成される。そのため、正弦波生成部1から出力される正弦波にノイズが入っていた場合であっても、各信号(SEL、UP、DN)の生成に当該ノイズの悪影響が及ぶことを、出来るだけ抑えることが可能である。

【0082】

6.その他

上述した通り各実施形態に係るPLL回路9は、流出または流入の出力電流を出力するものであって、パルス信号(流出のオン/オフを切替えるパルス信号UP、および、流入のオン/オフを切替えるパルス信号DN)に応じて出力電流のオン/オフが切替えられるチャージポンプ4と、周期性を有する多値の参照信号Sref(正弦波のアナログ信号がAD変換された信号)に応じてパルス信号UPおよびパルス信号DNを生成する、パルス生成回路32と、を備えており、チャージポンプ4の出力電流に応じた出力クロック信号Soutを生成する。更にPLL回路9は、参照信号Srefに応じて前記出力電流がオンである電流量を調節する、電流量調節回路31をも備えている。

【0083】

このようにPLL回路9によれば、参照信号に応じてチャージポンプの出力電流の電流量を調節するため、出力クロック信号の周波数制御を精度良く行うことが容易となっている。

【0084】

また上述した各実施形態(移動平均算出回路37を有する場合も含む)において、参照信号Srefの周波数が特定されている場合には、ADコンバータ2の後段側に、参照信号Srefに対してバンドパスのフィルタ処理を施すバンドパスフィルタ(BPF)を設けるようにしても良い。このようにすれば、参照信号Srefに含まれるノイズがより減少し、PLL回路9でのジッタが改善される。なおバンドパスフィルタは、正弦波生成部1とADコンバータ2の間に設けられるようにしても良い。

【0085】

また、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0086】

本発明は、PLL回路を有する各種機器に利用することができる。

【符号の説明】

【0087】

1 正弦波生成部

2 ADコンバータ

3 チャージポンプ制御回路

31 電流量調節回路

32 パルス生成回路

33 目標波形生成回路

34 コンパレータ

36 積分回路

37 移動平均算出回路

4 チャージポンプ

5 ローパスフィルタ

6 電圧制御発振回路

7 ゼロクロス信号生成回路

T1〜T8 トランジスタ

【技術分野】

【0001】

本発明は、クロック信号を生成するPLL[Phase Locked Loop]回路に関する。

【背景技術】

【0002】

従来、種々の電気機器においてPLL回路が利用されている。ここで従来のPLL回路の構成について、主にアナログ信号を処理する形式(アナログ形式)のPLL回路、および、主にデジタル信号を処理する形式(デジタル形式)のPLL回路を例に挙げ、以下に簡潔に説明する。

【0003】

図11は、アナログ形式のPLL回路100の構成図である。本図に示すようにPLL回路100は、比較器(位相周波数比較器)101、チャージポンプ102、ローパスフィルタ103、電圧制御発振回路104、および分周器105を有する。

【0004】

比較器101は、リファレンス周波数信号および分周器105の出力信号が入力され、これらの位相比較の結果に応じて、パルス信号UPまたはパルス信号DNを出力する。またチャージポンプ102は、流出または流入の出力電流を出力するものであって、パルス信号UPに応じて流出の出力電流のオン/オフが切替えられ、パルス信号DNに応じて流入の出力電流のオン/オフが切替えられるように構成されている。

【0005】

ローパスフィルタ103は、チャージポンプ102の出力側に設けられており、入力電圧に低域通過のフィルタ処理を施して、電圧制御発振回路104に出力する。また電圧制御発振回路104は、ローパスフィルタ103の出力電圧に応じた周波数のクロック信号を、出力クロック信号Soutとして生成する。

【0006】

生成された出力クロック信号Soutは、PLL回路100の外部に出力されるとともに、分周器105に入力される。分周器105に入力された出力クロック信号Soutは、分周の処理が施された上で、比較器101へ出力される。PLL回路100によれば、例えばリファレンス周波数信号が1MHzであり、分周器105が2分周を行う場合に、2MHzの出力クロック信号Soutが得られる。

【0007】

但しPLL回路100によれば、リファレンス周波数信号としてデジタル信号(例えば、AD変換された後の信号)が入力される場合には、上述した位相比較を適切に行うことが難しくなる。これに対し、デジタル形式のPLL回路200の構成図を図12に示す。本図に示すようにPLL回路200は、比較器101や分周器105の代わりに、デジタル回路として構成されたカウンタA、カウンタB、および比較器201を有する。

【0008】

カウンタAは、リファレンス周波数信号のクロックをカウントし、カウンタBは、出力クロック信号Soutのクロックをカウントする。また比較器201は、各カウンタによるカウント結果の大小関係に応じて、パルス信号UPまたはパルス信号DNを出力する。

【0009】

図13は、1MHzのリファレンス周波数信号から2MHzの出力クロック信号Soutが得られるようにした場合における、各カウンタの動作の様子を模式的に例示したものである。本図に示すように、カウンタAは100までのカウントアップを繰返し、カウンタBは200までのカウントアップを繰返すように動作する。比較器201は、各カウンタのカウントアップを繰返すタイミングにズレが発生したとき、このズレを解消させるように、パルス信号UPまたはパルス信号DNを出力する。

【先行技術文献】

【特許文献】

【0010】

【特許文献1】特開2008−72469号公報

【特許文献2】特許第3022870号公報

【発明の概要】

【発明が解決しようとする課題】

【0011】

上述したデジタル形式のPLL回路によれば、デジタル回路をFPGA等により制御することや、カウンタのカウント数を可変にすること等により、出力クロック信号の周波数を自由に変更することが可能となる。

【0012】

しかしこのようなデジタル形式の方式によれば、パルス信号UPやパルス信号DNの周波数が低下することになり(図13に示す例では、リファレンス周波数信号の1/100程度となる)、出力クロック信号の周波数制御を精度良く行うことが、難しくなるおそれがある。

【0013】

本発明は上述した問題に鑑み、出力クロック信号の周波数制御を精度良く行うことが容易となるPLL回路の提供を目的とする。

【課題を解決するための手段】

【0014】

上記目的を達成するため本発明に係るPLL回路は、流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、を備え、前記出力電流に応じた出力クロック信号を生成するPLL回路であって、前記参照信号に応じて前記出力電流の電流量を調節する、電流量調節部を備えた構成とする。

【0015】

本構成によれば、参照信号に応じてチャージポンプの出力電流の電流量を調節するため、出力クロック信号の周波数制御を精度良く行うことが容易となる。

【0016】

また上記構成としてより具体的には、前記参照信号は、正弦波を表すデジタル信号である構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記パルス信号として、前記流出のオン/オフを切替えるUP信号、および、前記流入のオン/オフを切替えるDN信号を生成する構成としてもよい。

【0017】

また上記構成としてより具体的には、前記チャージポンプの出力側に設けられたローパスフィルタと、前記ローパスフィルタの出力電圧に応じた周波数のクロック信号を、前記出力クロック信号として生成する電圧制御発振回路と、を備えた構成としてもよい。

【0018】

また前記参照信号の目標波形を表す目標波形信号を生成する、上記構成のPLL回路において、前記電流量調節部は、前記参照信号と前記目標波形信号との差分値に応じて、前記電流量を調節する構成としてもよい。

【0019】

また上記構成としてより具体的には、前記電流量調節部は、前記差分値の絶対値が大きいほど、前記電流量が大きくなるように前記調節を行う構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記参照信号と前記目標波形信号との差の符号に応じて、UP信号とDN信号の何れを生成するかを決める構成としてもよい。

【0020】

また上記構成としてより具体的には、前記電流量調節部は、前記参照信号の積分値に応じて、前記電流量を調節する構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記参照信号の積分値の符号に応じて、UP信号とDN信号の何れを生成するかを決める構成としてもよい。

【0021】

また前記参照信号がゼロクロスとなるべきタイミングである、ゼロクロスタイミングを特定する上記構成のPLL回路において、前記電流量調節部は、前記ゼロクロスタイミングにおける、前記参照信号とゼロとの差分値に応じて、前記電流量を調節する構成としてもよい。また上記構成としてより具体的には、前記パルス信号生成回路は、前記ゼロクロスタイミングにおける、前記参照信号とゼロとの差の符号に応じて、UP信号とDN信号の何れを生成するかを決める構成としてもよい。

【0022】

また上記構成としてより具体的には、前記参照信号に対して移動平均の算出処理を施す、移動平均算出回路を備えた構成としてもよい。また上記構成としてより具体的には、前記参照信号に対してフィルタ処理を施す、バンドパスフィルタを備えた構成としてもよい。

【発明の効果】

【0023】

上述した通り、本発明に係るPLL回路によれば、参照信号に応じてチャージポンプの出力電流の電流量を調節するため、出力クロック信号の周波数制御を精度良く行うことが容易となる。

【図面の簡単な説明】

【0024】

【図1】本発明の実施形態に係るPLL回路の構成図である。

【図2】本発明の実施形態に係るチャージポンプの構成図である。

【図3】第1実施形態に係るCP制御回路の構成図である。

【図4】第1実施形態に係るCP制御回路の動作に関わる説明図である。

【図5】第2実施形態に係るCP制御回路の動作に関わる説明図である。

【図6】第3実施形態に係るCP制御回路の構成図である。

【図7】第3実施形態に係るCP制御回路の動作に関わる説明図である。

【図8】第4実施形態に係るCP制御回路の構成図である。

【図9】第4実施形態に係るCP制御回路の動作に関わる説明図である。

【図10】第5実施形態に係るCP制御回路の構成図である。

【図11】従来のアナログ形式のPLL回路の構成図である。

【図12】従来のデジタル形式のPLL回路の構成図である。

【図13】カウンタの動作に関する説明図である。

【発明を実施するための形態】

【0025】

本発明の実施形態について、第1実施形態から第5実施形態の各々を例に挙げて、以下に説明する。

【0026】

1.第1実施形態

[PLL回路の全体構成]

まず第1実施形態について説明する。図1は、本実施形態に係るPLL回路9の構成図である。本図に示すようにPLL回路9は、正弦波生成部1、ADコンバータ2、チャージポンプ制御回路(以下、「CP制御回路」と称する)3、チャージポンプ4、ローパスフィルタ5、電圧制御発振回路6、およびゼロクロス信号生成回路7を有している。

【0027】

正弦波生成部1は、所定周期の正弦波(サイン波)のアナログ信号を生成して、後段側のADコンバータ2に出力する。ADコンバータ2は、前段側から受取るアナログ信号に対してAD[Analog to Digital]変換を実行し、変換済みのデジタル信号(正弦波を表すデジタル信号)を参照信号SrefとしてCP制御回路3に送出する。

【0028】

なおPLL回路9においては、正弦波生成部1やADコンバータ2が設けられる代わりに、参照信号Srefに相当する信号が外部から入力されるようになっていても良い。また参照信号Srefは、周期性を有する多値の信号であって、正弦波とは異なる形態であっても構わない。ここで本願における「多値の信号」とは、少なくとも3種以上の値となる信号であり、2値のパルス信号などを含まない概念である。なお参照信号Srefは周期性を有するため、クロック信号の一種(リファレンスクロック信号)と見ることも出来る。

【0029】

CP制御回路3は、参照信号Srefに基づいて、パルス信号UP、パルス信号DN、および調節信号SELを生成するデジタル回路である。CP制御回路3は、これらの信号をチャージポンプ4に送出することにより、チャージポンプ4の動作を制御する。パルス信号UPおよびパルス信号DNは、2値(HレベルとLレベル)のパルス信号であり、各値がオンおよびオフの何れかを表す。なお、CP制御回路3のより詳細な構成等については、改めて説明する。

【0030】

チャージポンプ4は、流出または流入の出力電流を出力するものであって、パルス信号UPに応じて当該流出のオン/オフが切替えられ、パルス信号DNに応じて当該流入のオン/オフが切替えられるように形成されている。

【0031】

すなわちチャージポンプ4は、パルス信号UPがオンのときに、自身から出力側(LPF5)へ電流を流出させる(つまり、「流出」の出力電流を出力する)ようにし、パルス信号DNがオンのときに、出力側から自身へ電流を流入させる(つまり、「流入」の出力電流を出力する)ように動作する。チャージポンプ4の出力電流によって、ローパスフィルタ5に入力される電圧が決められる。

【0032】

またチャージポンプ4は、調節信号SELに応じて、出力電流がオンであるときの電流量が変化するように形成されている。ここでチャージポンプ4の構成例について、図2を参照しながら以下に説明する。なおこの例では、調節信号SELは、複数の信号(SEL−1〜SEL−6)からなっている。

【0033】

図2に示すようにチャージポンプ4は、UP側のPMOSトランジスタT1と、DOWN側のNMOSトランジスタT2とを備える。PMOSトランジスタT1は、ゲートにはパルス信号UPが入力されるようになっており、ソースには、電流可変用のPMOSトランジスタT3〜T5のドレインが共通接続される。PMOSトランジスタT3〜T5はそれぞれ、ソースが電源に接続され、ゲートに信号SEL−1〜SEL−3が供給される。

【0034】

またNMOSトランジスタT2は、ゲートにはパルス信号DNが入力されるようになっており、ソースには、電流可変用のNMOSトランジスタT6〜T8のドレインが共通接続される。NMOSトランジスタT6〜T8はそれぞれ、ソースが接地され、ゲートに信号SEL−4〜SEL−6が供給される。

【0035】

図2に示す構成によれば、パルス信号UPのオン時に、チャージポンプ4からローパスフィルタ5へ電流が流出する。そしてこの流出に係る電流量は、主に信号SEL−1〜SEL−3に応じて(つまり、PMOSトランジスタT3〜T5のうちの何れがオンとなるかに応じて)変化する。

【0036】

またパルス信号DNのオン時に、ローパスフィルタ5からチャージポンプ4へ電流が流入する。そしてこの流入に係る電流量は、主に信号SEL−4〜SEL−6に応じて(つまり、NMOSトランジスタT6〜T8のうちの何れがオンとなるかに応じて)変化する。なお図2に示した構成は一例であって、チャージポンプ4はその他の構成となっていても構わない。

【0037】

図1に戻り、ローパスフィルタ5は、チャージポンプ4の出力側に設けられており、入力電圧に低域通過のフィルタ処理を施して、電圧制御発振回路6に出力する。また電圧制御発振回路6は、ローパスフィルタ5の出力電圧に応じた周波数のクロック信号(方形波)を、出力クロック信号Soutとして生成する。生成された出力クロック信号Soutは、PLL回路9の外部に出力され、種々の目的に利用される。

【0038】

なおPLL回路9は所定の機構(参照信号Srefと出力クロック信号Soutのクロックをカウントして比較する機構や、分周器を用いる機構等であっても構わない)を用いて、参照信号Srefに対応した周波数となるように、出力クロック信号Soutを生成する。本実施形態ではその一例として、125kHzの参照信号Srefに基づいて、これが16逓倍された2MHzの出力クロック信号Soutが生成されるとする。

【0039】

またADコンバータ2、CP制御回路3、およびゼロクロス信号生成回路7には、基準クロックCLの信号が入力されるようになっている。ADコンバータ2は、基準クロックCLの周期でAD変換を行うようになっており、CP制御回路3は、基準クロックCLに応じて所定動作(詳しくは後述する)を行うようになっている。

【0040】

なお基準クロックCLの信号としては、出力クロック信号Soutが用いられるようにしても良く、別途生成されたクロック信号が用いられるようにしても良い。なお以下の説明では、基準クロックCLの周波数は、参照信号Srefが16逓倍されたものであるとする。

【0041】

ゼロクロス信号生成回路7は、ゼロクロスタイミング(参照信号Srefがゼロクロスとなるべきタイミング)を検知し、ゼロクロスタイミングを表す信号をCP制御回路3に出力する。ゼロクロス信号生成回路7は、一例として、まず参照信号Srefの符号反転検出を行って初めのゼロクロスのタイミングを検知し、その後、基準クロックCLを用いて参照信号Srefの周期(本実施形態では16回分の基準クロックCL)をカウントすることで、永続的にゼロクロスタイミングを検知することが可能である。なお、CP制御回路3が行う処理においてゼロクロスタイミングの情報が不要である場合には、ゼロクロス信号生成回路7は設けられなくても良い。

【0042】

[CP制御回路の構成]

次に、CP制御回路3の構成等についてより詳細に説明する。図3は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、パルス信号生成回路32、目標波形生成回路33、およびコンパレータ34を有している。

【0043】

電流量調節回路31は、入力される信号(本実施形態では、後述する差分信号)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。パルス生成回路32は、入力される信号(本実施形態では、後述する差分信号)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。

【0044】

目標波形生成回路33は、参照信号Srefの目標波形(本実施形態では125kHzの正弦波)の信号を生成する回路である。目標波形生成回路33は、例えば、基準クロックCLの間隔での目標波形の値を表すLUT[Look up Table]が用意されており、基準クロックCLと当該LUTを用いることにより、目標波形の信号を生成する。

【0045】

コンパレータ34は、参照信号Srefの値と目標波形の信号の値との差分値(便宜的に「差分値D1」とする)を算出し、算出結果の信号を差分信号として、後段側に送出する。なおコンパレータ34における当該算出は、例えばゼロクロスタイミングの情報が利用され、参照信号Srefと目標波形を同期させるようにして実行される。

【0046】

[CP制御回路の動作]

次に、CP制御回路3の動作についてより詳細に説明する。電流量調節回路31は、差分信号が表す差分値D1に応じて、調節信号SELを生成する。より具体的には、差分値D1の絶対値が大きいほどチャージポンプ4での電流量が増大するように、調節信号SELが生成される。一例としては、差分値D1の絶対値(或いはこれに所定係数を乗じた値)が、チャージポンプ4での電流量となるように、調節信号SELが生成される。調節信号SELは、差分値D1の絶対値が出来るだけ速やかに小さくなるように、適切に生成されることが望ましい。

【0047】

またパルス生成回路32は、差分信号が表す差分値D1の符号に応じて、パルス信号UPおよびパルス信号DNを生成する。より具体的には、パルス信号DNについては、差分値D1が正であればオンとし、そうでないときはオフとする。またパルス信号UPについては、差分値D1が負であればオンとし、そうでないときはオフとする。

【0048】

また本実施形態では、コンパレータ34による差分値D1の算出は、基準クロックCLの周期毎に(つまり、基準クロックCLのタイミングで毎回)実行される。そしてこの算出結果に従って、差分信号の内容が更新される。また電流量調節回路31およびパルス生成回路32による信号生成の動作(信号内容の更新)も、当該算出のタイミングに同期して行われる。

【0049】

ここで図4は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図4の上段は、参照信号Sref(実線)と目標波形(破線)の様子(参照信号Srefの位相が遅れている例)を模式的に示しており、図4の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図4中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0050】

図4に示すように本実施形態では、基準クロックCLの周期毎のタイミング(図4ではt1〜t18が例示されている)において差分値D1が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0051】

このように電流量調節回路31は、参照信号Srefに応じて(より具体的には、参照信号Srefの値と目標波形の信号の値との差分値D1に応じて)、チャージポンプ4の出力電流の電流量を調節するようになっている。そのためPLL回路9は、このような調節が行われないものに比べて、差分値D1の絶対値をより速やかに小さくすること等が可能であり、出力クロック信号の周波数制御を精度良く行うことが容易である。またこれにより、パルス信号UPやパルス信号DNの周波数が小さくても、出力クロック信号Soutに関するジッタの悪化等を低減させることが容易である。

【0052】

2.第2実施形態

次に、第2実施形態について説明する。なお第2実施形態は、差分値を算出するタイミングに関する点を除き、基本的に第1実施形態と同様である。以下の説明では、第1実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0053】

第2実施形態では、コンパレータ34による差分値D1の算出は、ゼロクロスタイミングおよびその前後のタイミング(以下の説明では一例として、基準クロックCLの1周期分だけ前後のタイミングとする)においてのみ実行される。そしてこの算出結果に従って、差分信号の内容が更新される。また電流量調節回路31およびパルス生成回路32による信号生成の動作(信号内容の更新)も、当該算出のタイミングに同期して行われる。

【0054】

なお第2実施形態のゼロクロス信号生成部7は、ゼロクロスタイミングだけでなく、その前後のタイミングをも検知し、これらのタイミングを表す信号をCP制御回路3に出力するようになっている。これにより差分値D1の算出のタイミングを、ゼロクロスタイミングおよびその前後のタイミングのみとすることが可能となっている。

【0055】

ここで図5は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図5の上段は、参照信号Sref(実線)と目標波形(破線)の様子(参照信号Srefの位相が遅れている例)を模式的に示しており、図5の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図5中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0056】

図5に示すように第2実施形態では、ゼロクロスタイミングおよびその前後のタイミング(図5ではt1〜t8が例示されている)においてのみ差分値D1が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0057】

このように第2実施形態によれば、ゼロクロスタイミングおよびその前後のタイミングを除いては、差分値D1の算出が省略される。そのため参照信号Srefと目標波形の間に振幅の差があったとしても、この振幅の差が差分値D1の算出に与える影響を、極力抑えることが可能である。これにより、PLL回路9におけるジッタの悪化を低減させることが容易となる。

【0058】

3.第3実施形態

次に、第3実施形態について説明する。なお第3実施形態は、PC制御回路3の構成や動作に関する点を除き、基本的に第1実施形態と同様である。以下の説明では、第1実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0059】

図6は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、パルス信号生成回路32、および積分回路36を有している。

【0060】

電流量調節回路31は、入力される信号(本実施形態では、後述する積分信号)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。パルス生成回路32は、入力される信号(本実施形態では、後述する積分信号)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。また積分回路36は、参照信号Srefの値の積分値を算出し、算出結果の信号を積分信号として後段側に送出する。

【0061】

次に、CP制御回路3の動作についてより詳細に説明する。電流量調節回路31は、積分信号が表す積分値の絶対値と目標積分量との差分値(便宜的に「差分値D2」とする)に応じて、調節信号SELを生成する。より具体的には、差分値D2の絶対値が大きいほどチャージポンプ4での電流量が増大するように、調節信号SELが生成される。

【0062】

一例としては、差分値D2の絶対値(或いはこれに所定係数を乗じた値)が、チャージポンプ4での電流量となるように、調節信号SELが生成される。なお目標積分量は、参照信号Srefが理想波形であると仮定した場合の積分値の絶対値(つまり期待される積分値の絶対値)に相当する。参照信号Srefが理想波形である場合には、差分値D2はゼロとなる。調節信号SELは、差分値D2の絶対値が出来るだけ速やかに小さくなるように、適切に生成されることが望ましい。

【0063】

またパルス生成回路32は、差分値D2の符号に応じて、パルス信号UPおよびパルス信号DNを生成する。より具体的には、パルス信号DNについては、差分値D2が正であればオンとし、そうでないときはオフとする。またパルス信号UPについては、差分値D2が負であればオンとし、そうでないときはオフとする。

【0064】

また本実施形態では、積分回路36による積分値の算出は、ゼロクロスタイミングが到来する度に実行される。そしてこの算出結果に従って、積分信号の内容が更新される。また電流量調節回路31およびパルス生成回路32による信号生成の動作(信号内容の更新)も、当該算出のタイミングに同期して行われる。

【0065】

ここで図7は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図7の上段は、参照信号Srefの様子を模式的に示しており、図7の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図7中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0066】

図7に示すように本実施形態では、各ゼロクロスタイミング(図7ではt1〜t3が例示されている)において積分値が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0067】

なお本実施形態では、ゼロクロスタイミングごと、すなわち理想とする参照信号Srefの半周期ごとに積分値を算出するが、その代わりに、一周期ごとに積分値を算出するようにしても良い。このようにすれば目標積分量はゼロとなるため、算出される積分値をそのまま差分値D2として扱うことができ、CP制御回路3の回路構成をより簡略化することが容易となる。

【0068】

4.第4実施形態

次に、第4実施形態について説明する。なお第4実施形態は、PC制御回路3の構成や動作に関する点を除き、基本的に第1実施形態と同様である。以下の説明では、第1実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0069】

図8は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、およびパルス信号生成回路32を有している。電流量調節回路31は、入力される信号(本実施形態では、参照信号Sref)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。パルス生成回路32は、入力される信号(本実施形態では、参照信号Sref)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。

【0070】

次に、CP制御回路3の動作についてより詳細に説明する。電流量調節回路31は、参照信号Srefの値とゼロとの差分値(便宜的に「差分値D3」とする)に応じて、調節信号SELを生成する。より具体的には、差分値D3の絶対値が大きいほどチャージポンプ4での電流量が増大するように、調節信号SELが生成される。一例としては、差分値D3の絶対値(或いはこれに所定係数を乗じた値)が、チャージポンプ4での電流量となるように、調節信号SELが生成される。調節信号は、差分値D3の絶対値が出来るだけ速やかに小さくなるように、適切に生成されることが望ましい。

【0071】

またパルス生成回路32は、差分値D3の符号に応じて、パルス信号UPおよびパルス信号DNを生成する。より具体的には、パルス信号DNについては、差分値D3が正であればオンとし、そうでないときはオフとする。またパルス信号UPについては、差分値D3が負であればオンとし、そうでないときはオフとする。

【0072】

また本実施形態では、電流量調節回路31およびパルス生成回路32による信号生成は、ゼロクロスタイミングが到来する度に実行される。

【0073】

ここで図9は、CP制御回路3の動作に関わるタイミングチャートを例示している。なお図9の上段は、参照信号Srefの様子を模式的に示しており、図9の下段は、このときのパルス信号UP、パルス信号DN、および調節信号SELの状態を示している。また図9中の一点鎖線は、基準クロックCLの各タイミングを表している。

【0074】

図9に示すように本実施形態では、各ゼロクロスタイミング(図9においてt1〜t3が例示されているように、理想とする波形(本図中の破線の波形)がゼロクロスとなるタイミング)において積分値が算出され、それぞれの算出結果が各信号(UP、DN、SEL)に反映されている。

【0075】

このように電流量調節回路31は、参照信号Srefに応じて(より具体的には、参照信号Srefの値とゼロとの差分値D3に応じて)、チャージポンプ4の出力電流の電流量を調節するようになっている。そのためPLL回路9は、このような調節が行われないものに比べて、差分値D3の絶対値をより速やかに小さくすること等が可能であり、出力クロック信号の周波数制御を精度良く行うことが容易である。またこれにより、パルス信号UPやパルス信号DNの周波数が小さくても、出力クロック信号Soutに関するジッタの悪化等を低減させることが容易である。

【0076】

5.第5実施形態

次に、第5実施形態について説明する。なお第5実施形態は、参照信号Srefの移動平均を用いるようにした点を除き、基本的に第4実施形態と同様である。以下の説明では、第4実施形態と異なる部分の説明に重点をおき、共通する部分については説明を省略することがある。

【0077】

図10は、CP制御回路3の構成図である。本図に示すようにCP制御回路3は、電流量調節回路31、パルス信号生成回路32、および移動平均算出回路37を有している。移動平均算出回路37は、入力される参照信号Srefの値の移動平均を算出し、算出結果を電流決定回路31およびパルス生成回路32に送出する。なお移動平均の算出は、例えば、直近の1/8周期分の値を用いて行われる。

【0078】

電流量調節回路31は、入力される信号(本実施形態では、参照信号Srefの値の移動平均)に基づいて調節信号SELを生成し、チャージポンプ4に出力する。なお調節信号SELの生成手順は、参照信号Srefの値の代わりに当該移動平均の値が用いられる点を除き、第4実施形態の場合と同様である。

【0079】

パルス生成回路32は、入力される信号(本実施形態では、参照信号Srefの値の移動平均)に基づいてパルス信号UPおよびパルス信号DNを生成し、チャージポンプ4に出力する。なおパルス信号UPおよびパルス信号DNの生成手順は、参照信号Srefの値の代わりに当該移動平均の値が用いられる点を除き、第4実施形態の場合と同様である。

【0080】

第5実施形態では、参照信号Srefに対して移動平均が算出され、この算出結果を用いて各信号(SEL、UP、DN)が生成される。そのため、正弦波生成部1から出力される正弦波にノイズが入っていた場合であっても、各信号(SEL、UP、DN)の生成に当該ノイズの悪影響が及ぶことを、出来るだけ抑えることが可能である。

【0081】

なお第5実施形態では、第4実施形態のPLL回路9に移動平均算出回路37を設けた形態となっているが、第1実施形態から第3実施形態の何れのPLL回路9についても、移動平均算出回路37に相当するものを設けることが可能である。この場合にも、参照信号Srefに対して移動平均が算出され、この算出結果を用いて各信号(SEL、UP、DN)が生成される。そのため、正弦波生成部1から出力される正弦波にノイズが入っていた場合であっても、各信号(SEL、UP、DN)の生成に当該ノイズの悪影響が及ぶことを、出来るだけ抑えることが可能である。

【0082】

6.その他

上述した通り各実施形態に係るPLL回路9は、流出または流入の出力電流を出力するものであって、パルス信号(流出のオン/オフを切替えるパルス信号UP、および、流入のオン/オフを切替えるパルス信号DN)に応じて出力電流のオン/オフが切替えられるチャージポンプ4と、周期性を有する多値の参照信号Sref(正弦波のアナログ信号がAD変換された信号)に応じてパルス信号UPおよびパルス信号DNを生成する、パルス生成回路32と、を備えており、チャージポンプ4の出力電流に応じた出力クロック信号Soutを生成する。更にPLL回路9は、参照信号Srefに応じて前記出力電流がオンである電流量を調節する、電流量調節回路31をも備えている。

【0083】

このようにPLL回路9によれば、参照信号に応じてチャージポンプの出力電流の電流量を調節するため、出力クロック信号の周波数制御を精度良く行うことが容易となっている。

【0084】

また上述した各実施形態(移動平均算出回路37を有する場合も含む)において、参照信号Srefの周波数が特定されている場合には、ADコンバータ2の後段側に、参照信号Srefに対してバンドパスのフィルタ処理を施すバンドパスフィルタ(BPF)を設けるようにしても良い。このようにすれば、参照信号Srefに含まれるノイズがより減少し、PLL回路9でのジッタが改善される。なおバンドパスフィルタは、正弦波生成部1とADコンバータ2の間に設けられるようにしても良い。

【0085】

また、本発明の構成は、上記実施形態のほか、発明の主旨を逸脱しない範囲で種々の変更を加えることが可能である。すなわち、上記実施形態は、全ての点で例示であって、制限的なものではないと考えられるべきであり、本発明の技術的範囲は、上記実施形態の説明ではなく、特許請求の範囲によって示されるものであり、特許請求の範囲と均等の意味及び範囲内に属する全ての変更が含まれると理解されるべきである。

【産業上の利用可能性】

【0086】

本発明は、PLL回路を有する各種機器に利用することができる。

【符号の説明】

【0087】

1 正弦波生成部

2 ADコンバータ

3 チャージポンプ制御回路

31 電流量調節回路

32 パルス生成回路

33 目標波形生成回路

34 コンパレータ

36 積分回路

37 移動平均算出回路

4 チャージポンプ

5 ローパスフィルタ

6 電圧制御発振回路

7 ゼロクロス信号生成回路

T1〜T8 トランジスタ

【特許請求の範囲】

【請求項1】

流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、

周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、

を備え、

前記出力電流に応じた出力クロック信号を生成するPLL回路であって、

前記参照信号に応じて前記出力電流がオンであるときの電流量を調節する、電流量調節部を備えたことを特徴とするPLL回路。

【請求項2】

前記参照信号は、

正弦波を表すデジタル信号であることを特徴とする請求項1に記載のPLL回路。

【請求項3】

前記パルス信号生成回路は、

前記パルス信号として、前記流出のオン/オフを切替えるUP信号、および、前記流入のオン/オフを切替えるDN信号を生成することを特徴とする請求項2に記載のPLL回路。

【請求項4】

前記チャージポンプの出力側に設けられたローパスフィルタと、

前記ローパスフィルタの出力電圧に応じた周波数のクロック信号を、前記出力クロック信号として生成する電圧制御発振回路と、

を備えたことを特徴とする請求項3に記載のPLL回路。

【請求項5】

前記参照信号の目標波形を表す目標波形信号を生成する、請求項4に記載のPLL回路であって、

前記電流量調節部は、

前記参照信号の値と前記目標波形信号の値との差分値に応じて、前記電流量を調節することを特徴とするPLL回路。

【請求項6】

前記電流量調節部は、

前記差分値の絶対値が大きいほど、前記電流量が大きくなるように前記調節を行うことを特徴とする請求項5に記載のPLL回路。

【請求項7】

前記パルス信号生成回路は、

前記差分値の符号に応じて、UP信号およびDN信号を生成することを特徴とする請求項5または請求項6に記載のPLL回路。

【請求項8】

前記電流量調節部は、

前記参照信号の積分値に応じて、前記電流量を調節することを特徴とする請求項4に記載のPLL回路。

【請求項9】

前記参照信号がゼロクロスとなるべきタイミングである、ゼロクロスタイミングを特定する請求項4に記載のPLL回路であって、

前記電流量調節部は、

前記ゼロクロスタイミングにおける前記参照信号の値とゼロとの差分値に応じて、前記電流量を調節することを特徴とするPLL回路。

【請求項10】

前記パルス信号生成回路は、

前記差分値の符号に応じて、UP信号およびDN信号を生成することを特徴とする請求項9に記載のPLL回路。

【請求項11】

前記参照信号に対して移動平均の算出処理を施す、移動平均算出回路を備えたことを特徴とする請求項1から請求項10の何れかに記載のPLL回路。

【請求項12】

前記参照信号に対してバンドパスのフィルタ処理を施す、バンドパスフィルタを備えたことを特徴とする請求項1から請求項11の何れかに記載のPLL回路。

【請求項1】

流出または流入の出力電流を出力するものであって、パルス信号に応じて前記出力電流のオン/オフが切替えられるチャージポンプと、

周期性を有する多値の参照信号に応じて前記パルス信号を生成する、パルス信号生成部と、

を備え、

前記出力電流に応じた出力クロック信号を生成するPLL回路であって、

前記参照信号に応じて前記出力電流がオンであるときの電流量を調節する、電流量調節部を備えたことを特徴とするPLL回路。

【請求項2】

前記参照信号は、

正弦波を表すデジタル信号であることを特徴とする請求項1に記載のPLL回路。

【請求項3】

前記パルス信号生成回路は、

前記パルス信号として、前記流出のオン/オフを切替えるUP信号、および、前記流入のオン/オフを切替えるDN信号を生成することを特徴とする請求項2に記載のPLL回路。

【請求項4】

前記チャージポンプの出力側に設けられたローパスフィルタと、

前記ローパスフィルタの出力電圧に応じた周波数のクロック信号を、前記出力クロック信号として生成する電圧制御発振回路と、

を備えたことを特徴とする請求項3に記載のPLL回路。

【請求項5】

前記参照信号の目標波形を表す目標波形信号を生成する、請求項4に記載のPLL回路であって、

前記電流量調節部は、

前記参照信号の値と前記目標波形信号の値との差分値に応じて、前記電流量を調節することを特徴とするPLL回路。

【請求項6】

前記電流量調節部は、

前記差分値の絶対値が大きいほど、前記電流量が大きくなるように前記調節を行うことを特徴とする請求項5に記載のPLL回路。

【請求項7】

前記パルス信号生成回路は、

前記差分値の符号に応じて、UP信号およびDN信号を生成することを特徴とする請求項5または請求項6に記載のPLL回路。

【請求項8】

前記電流量調節部は、

前記参照信号の積分値に応じて、前記電流量を調節することを特徴とする請求項4に記載のPLL回路。

【請求項9】

前記参照信号がゼロクロスとなるべきタイミングである、ゼロクロスタイミングを特定する請求項4に記載のPLL回路であって、

前記電流量調節部は、

前記ゼロクロスタイミングにおける前記参照信号の値とゼロとの差分値に応じて、前記電流量を調節することを特徴とするPLL回路。

【請求項10】

前記パルス信号生成回路は、

前記差分値の符号に応じて、UP信号およびDN信号を生成することを特徴とする請求項9に記載のPLL回路。

【請求項11】

前記参照信号に対して移動平均の算出処理を施す、移動平均算出回路を備えたことを特徴とする請求項1から請求項10の何れかに記載のPLL回路。

【請求項12】

前記参照信号に対してバンドパスのフィルタ処理を施す、バンドパスフィルタを備えたことを特徴とする請求項1から請求項11の何れかに記載のPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−77966(P2013−77966A)

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願番号】特願2011−216446(P2011−216446)

【出願日】平成23年9月30日(2011.9.30)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

【公開日】平成25年4月25日(2013.4.25)

【国際特許分類】

【出願日】平成23年9月30日(2011.9.30)

【出願人】(000116024)ローム株式会社 (3,539)

【Fターム(参考)】

[ Back to top ]