PLL回路

【課題】PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにする。

【解決手段】PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にし、校正部60のループフィルタ62の出力電圧V’inと校正用電源66の出力電圧Vdd/2とを電圧比較器63で比較する。比較結果を基に、V’in≒Vdd/2となるように、電流制御装置64によりデジタル制御電圧を生成し、デジタルアナログ変換器65によりアナログ制御電圧V+、V-に変換し、VCO40内の電圧電流変換回路41に供給する。

【解決手段】PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にし、校正部60のループフィルタ62の出力電圧V’inと校正用電源66の出力電圧Vdd/2とを電圧比較器63で比較する。比較結果を基に、V’in≒Vdd/2となるように、電流制御装置64によりデジタル制御電圧を生成し、デジタルアナログ変換器65によりアナログ制御電圧V+、V-に変換し、VCO40内の電圧電流変換回路41に供給する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、ラジオ受信機やテレビ放送受信機、携帯電話機、複合機などの通信機器において、局部発振回路として用いられるPLL(Phase Locked Loop:位相同期ループ)回路に関する。

【背景技術】

【0002】

PLL回路の基本構成は、位相比較器、チャージポンプ、ループフィルタ、VCO(Voltage Controlled Oscillator:電圧制御発振器)、及び分周器からなる。そして、VCOの出力を分周器で分周した信号の位相と、基準信号の位相との位相差を位相比較器で検出し、この位相差に応じたパルス信号(UP信号、DOWN信号)をチャージポンプが出力し、その出力をループフィルタで平滑化してVCOを駆動する。PLL回路はこのような動作を繰り返し、VCOの出力である比較信号の周波数と位相を基準信号にロックさせる(特許文献1)。

【0003】

ここで、電圧電流変換回路及びリングICO(電流制御発振器)からなるVCOにおいては、ループフィルタの出力電圧が電圧電流変換回路により電流に変換され、この電流がリングICOの各遅延段におけるキャパシタを充放電し、順に各遅延段を遷移することにより遅延時間が発生することで周波数変調が行われる。

【0004】

近年、PLL回路には広帯域の発振周波数範囲(ロックレンジ)が要求されており、発振周波数範囲の広帯域化にはVCOのゲインを大きくする(入力電圧対出力周波数特性の傾きを急にする)ことが必要である。しかし、VCOのゲインを大きくすると、外乱に対する出力発振周波数の変動が大きくなる。

【0005】

また、VCOの製造時のばらつき及び温度変化などにより、VCOを構成するトランジスタの閾値電圧(Vth)がばらつき、トランジスタの動作速度が高速(fast)、標準速度(typical)、低速(slow)のように変動することは避けられない。

【0006】

特にICOとしてリングICOを用いる場合、ICOゲインが高い(=入力電流対出力周波数特性の傾きが急である)ため、製造プロセスの微細化に伴う製造ばらつきや温度変化などによるICO入力電流、つまりVCO入力電圧の変動が、遅延段における電流の遷移時間を決めている電流値の変動となり、発振周波数の大きな変動につながり、ジッタが増加してしまう。

【0007】

図5は、トランジスタの動作速度が高速(fast)、標準速度(typical)、低速(slow)の場合のVCOの入力電圧(Vin)対出力周波数(fout)特性を示す図である。この図においてVddは電源の電位である。

図5Aに示すように、トランジスタの動作速度が標準速度の場合、VCOの入力電圧がV1のときにターゲット周波数(ftarget)にロックしても、高速の場合はターゲット周波数をオーバーしてしまい、低速の場合はターゲット周波数に到達しない。

【0008】

ここでVCOのゲインを下げると、外乱に対する出力発振周波数の変動を小さくすることはできる。しかし、図5Bに示すように、高速及び低速では、入力電圧Vinを変化させてもターゲット周波数にロックさせることができなくなるという問題がある。

【0009】

また、一般にチャージポンプの電流源はカレントミラー回路で構成されるので、カレントミラー回路を構成するトランジスタを飽和領域で動作させなければならない。しかし、チャージポンプの出力段中間点の電位の変動により飽和領域で動作せずカレントミラー動作を行わないと、位相比較器から出力されるUP信号に応じた電流(ループフィルタのキャパシタへの充電電流)と、DOWN信号に応じた電流(ループフィルタのキャパシタからの放電電流)の電流値が異なるためにジッタが発生してしまうという問題もある。

【0010】

さらに、ループフィルタのキャパシタをMOSで作ることによりループフィルタを内蔵させることでPLL回路の面積の低減及びコスト削減を実現できるが、MOSの容量(キャパシタンス)に電圧依存性があるため、ループフィルタの入力電圧の変動によりPLLの安定性およびジッタ特性が変化してしまうという問題もある。

【0011】

特許文献1に記載されたPLL回路では、VCOの発振周波数がロックレンジに適合するように、VCOに供給する電流量を制御するキャリブレーションコントロール回路を設けることで、プロセス変動を電流量の調整で打ち消し、VCOの感度を低く設定できるとされている。

【0012】

しかし、このPLL回路では、チャージポンプの電流源を構成するトランジスタが飽和領域で動作しないためにカレントミラー動作を行わなくなることに起因するジッタ、及びループフィルタのキャパシタを構成するMOS容量の電圧依存性に起因するジッタの防止については考慮されていない。

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明は、このような問題を解決するためになされたものであり、その目的は、PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにすることである。

【課題を解決するための手段】

【0014】

本発明のPLL回路は、VCOと、当該VCOの出力信号を分周する分周器と、当該分周器の出力信号と基準周波数信号との位相差を検出する位相比較器と、当該位相比較器の位相差出力に応じた電流を生成するチャージポンプと、当該チャージポンプの電流を平滑化して前記VCOの入力電圧を生成するループフィルタと、前記VCOの出力信号の周波数が前記基準周波数になるとき、前記ループフィルタの出力電圧が所定値になるように、前記VCOの入力電圧対出力周波数特性を校正する校正手段と、を有するPLL回路である。

【発明の効果】

【0015】

本発明によれば、PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制することができる。

【図面の簡単な説明】

【0016】

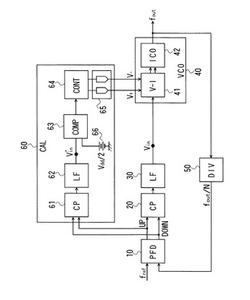

【図1】本発明の実施形態のPLL回路の構成を示すブロック図である。

【図2】図1におけるVCOの入力電圧対出力周波数特性を示す図である。

【図3】図1におけるチャージポンプ、ループフィルタ、及びVCOの回路図である。

【図4】図1におけるループフィルタのキャパシタを構成するMOSの印加電圧対容量特性を示す図である。

【図5】従来のPLL回路のVCOにおける入力電圧対出力周波数特性を示す図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について図面を参照して説明する。

〈PLL回路のブロック図〉

図1は、本発明の実施形態のPLL回路の構成を示すブロック図である。このPLL回路は、位相周波数検出器(PFD)10、チャージポンプ(CP)20、ループフィルタ(LF)30、VCO40、及び分周器(DIV)50からなるPLL部と、チャージポンプ61、ループフィルタ62、電圧比較器(COMP)63、電流制御装置(CONT)64、デジタルアナログ変換器(DAC)65、及び校正用電源66からなる校正部60からなる。

【0018】

校正部60を動作させるときは、PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にすることで、それらをPLLのループから切り離し、校正部60をPLLのループに接続する。

【0019】

位相周波数検出器10は、基準信号(周波数:fref)と、比較信号である分周器50の出力信号(周波数:fout/N)とを比較し、位相差に応じて、UP信号、DOWN信号を出力する。

【0020】

チャージポンプ20は、位相周波数検出器10からのUP信号、DOWN信号に応じて、ループフィルタ30のキャパシタを充電するパルス電流を出力し、そのキャパシタから放電されたパルス電流を吸い込む。

【0021】

ループフィルタ30は、チャージポンプ20の出力を平滑化し、その平滑化電圧をVCO40へ送出する。ループフィルタ30により、PLL回路の安定性及び雑音特性が決まる。ループフィルタ30は、集積化されPLL回路のチップに内蔵されており、そのキャパシタはMOSで構成されている。

【0022】

VCO40は、電圧電流変換回路(V−I)41と、電流制御発振器(ICO)42からなる。電圧電流変換回路41は、ループフィルタ30から送出された電圧値を電流値に変換し、電流制御発振器42は、電圧電流変換回路41により変換された電流値に応じた周波数の発振信号を生成する。

【0023】

分周器50は、VCO40の出力信号を1/Nに分周し、位相周波数検出器10に送出する。

【0024】

校正部60のチャージポンプ61、ループフィルタ62は、それぞれPLL部のチャージポンプ20、ループフィルタ30と同一構成を持つダミー回路である。

【0025】

電圧比較器63は、ループフィルタ62の出力電圧(V’in)と、校正用電源66の電圧とを比較し、その大小関係を表す信号を電流制御装置64に送出する。校正用電源66の電圧はこのPLL回路の電源電圧Vddの1/2である。

【0026】

電流制御装置64は、電圧比較器63の出力信号に応じて、電圧電流変換回路41の出力電流を増減するためのデジタル制御電圧を生成し、デジタルアナログ変換器65は、そのデジタル制御電圧をアナログ化してV+、V-とし、電圧電流変換回路41に印加する。

【0027】

つまり、校正部60では、電圧電流変換回路41において、電流制御発振器42の発振周波数を決める電流値を校正(キャリブレーション)することにより、VCO40への入力電圧が製造ばらつきや温度変化などによって変化しても、一定の電圧に保つために、位相周波数検出器10の出力信号から生成した補正信号を電圧電流変換回路41に与えている。

【0028】

〈校正部60の動作〉

次に校正部60の校正(キャリブレーション)動作について説明する。

この校正動作では、PLL部が任意の基準周波数信号にロックしたときに、VCO40の入力電圧(=ループフィルタ30の出力電圧)VinがVdd/2になるように、VCO40内の電圧電流変換回路41の入力電圧対出力電流特性を調整することで、VCO40の入力電圧対出力周波数特性を調整する。

【0029】

図2は、VCO40の入力電圧対出力周波数特性を示す図である。VCO40の製造時のばらつき及び温度変化などにより、VCO40を構成するトランジスタの動作速度は高速(fast)、標準速度(typical)、低速(slow)のどれかになる。そして、図2のように、VCO40のゲインを下げると、VCO40の入力電圧がVdd/2のときに、標準速度(typical)ではターゲット周波数(ftarget)にロックさせることができても、高速(fast)及び低速(slow)では、ターゲット周波数にロックさせることができない。

【0030】

そこで、本実施形態のPLL回路では、VCO40の入力電圧対出力周波数特性が高速(fast)或いは低速(slow)であった場合、それぞれの特性を、標準速度(typical)の特性に近づけるように調整することで、ターゲット周波数にロックさせることができるようにする。

【0031】

まずチャージポンプ20及びループフィルタ30をスリープ状態にし、これらの回路をPLL部から切り離す。次に校正部60全体をアクティブにする。校正部60のチャージポンプ61、ループフィルタ62は、それぞれPLL部のチャージポンプ20、ループフィルタ30と同一構成を有するので、ループフィルタ62の出力電圧V’inは、PLL部が動作しているときのループフィルタ30の出力電圧Vinと同じになる。

【0032】

V’inがVdd/2より大きいか小さいかを電圧比較器63により比較する。比較の結果、V’in>Vdd/2のとき(図2の低速(slow)に相当)は、電流制御装置64は、制御電圧V-のレベルを小さい値から大きな値へと段階的に変化させる。これにより、図2の低速(slow)の特性を標準速度(typical)に接近させることができる。比較の結果、V’in<Vdd/2のとき(図2の高速(fast)に相当)は、電流制御装置64は、制御電圧V+のレベルを小さい値から大きな値へと段階的に変化させる。これにより、図2の高速(fast)の特性を標準速度(typical)に接近させることができる。

【0033】

V’in≒Vdd/2になったら校正を終了し、PLL部のチャージポンプ20及びループフィルタ30をアクティブにする。電流制御装置64の内部にV+、V-を記憶する機能を設けておけば、校正終了後、校正部60内のチャージポンプ61、ループフィルタ62、及び電圧比較器63をスリープ状態にすることで、消費電流を低減することができる。

【0034】

〈チャージポンプ、ループフィルタ、及びVCOの回路図〉

図3は、図1におけるチャージポンプ20、ループフィルタ30、及びVCO40の回路図である。

【0035】

図示のように、チャージポンプ20は、第1の電流源21と、UP信号によりオンする第1のスイッチングトランジスタ22と、DOWN信号によりオンする第2のスイッチングトランジスタ23と、第2の電流源24との直列回路が電源とグラウンドとの間に接続された構成を持つ。

【0036】

ここで、第1の電流源21及び第2の電流源24はカレントミラー回路により構成されているため、各電流源を構成するトランジスタを飽和領域で動作させる必要がある。そのため、ここではチャージポンプ20の出力段の中間点、即ち第1のスイッチングトランジスタ22と第2のスイッチングトランジスタ23の接続点Mの電位を電源の電位Vddの1/2程度になるようにした。

【0037】

このように構成すると、第1の電流源21からループフィルタ30のキャパシタに流れ込む充電電流Icp_pと、第2の電流源24がループフィルタ30のキャパシタから吸い込む放電電流Icp_nとが同程度の電流になり、ジッタが軽減される。これに対して、Icp_pとIcp_nが異なると、充電電流パルスと放電電流パルスの時間幅が異なるため、ループフィルタ30の出力電圧Vinが変動し、VCO40の出力信号のジッタが増加することになる。

【0038】

ループフィルタ30は、抵抗31及びキャパシタ32の直列回路と、キャパシタ33との並列回路からなり、チャージポンプ20からの充電電流及び放電電流を平滑化し、電圧Vinを生成する。

【0039】

キャパシタ32及び33はMOSにより構成されている。図4は、MOSのゲートとドレイン及びソースの間の印加電圧(Vc)、と容量Cchとの関係、を説明するための図である。

【0040】

図4Aに示すように、ゲートとドレイン及びソースの間に電圧Vcを印加すると、容量Cchは図4Bのように変化する。即ち、電圧Vcが閾値電圧Vthを超えるまでは、電圧Vcの増加に伴って増加する。この間、チャネルは形成されておらず、容量Cchは酸化膜容量値と空乏層容量値の直列容量値となる。電圧Vcが閾値電圧Vthを超えると、チャネルが形成され、容量Cchはゲート容量Coxとなる。

【0041】

ループフィルタ30のキャパシタ32及び33の容量により、PLLのループ安定性及び雑音特性が決まるため、図4Bにおいて、容量Cchが電圧Vc(入力電圧Vin)により変化しない電圧領域(点線に挟まれた安定領域)で使用することが望ましい。

【0042】

例えば、Vdd=1.0[V]程度において、Vthは0.4[V]程度であるので、VinをVdd/2程度に設定すれば容量Cchの安定領域で使用できる。これにより、PLLの安定性が保たれ、ジッタも軽減される。

【0043】

ループフィルタ30により平滑化され、雑音が除去された出力電圧Vinは、電圧電流変換回路41を構成するトランジスタ41bをオンにするので、トランジスタ41bにはVinに対応する電流I1が流れる。

【0044】

校正部60のデジタルアナログ変換器65から出力される電流補正信号(V-、V+)をトランジスタ41c、41dのゲート電圧とすることで、電流源であるトランジスタ41c、41dに流れる電流I-、I+を変化させる。V-、V+の各々に対してサイズの異なるトランジスタを複数用意するとともに、各トランジスタと出力ラインとの間にスイッチを設け、各トランジスタのオン・オフにより、電流補正信号を印加するトランジスタを選択するように構成することもできる。

【0045】

このときトランジスタ41aに流れる電流はI1+I+−I-となるので、I-、I+を変化させることにより、トランジスタ41aに流れる電流を任意の値にすることができる。ここで、電流補正信号V-により減算ができ、電流補正信号V+により加算ができるので、加算しすぎたときに減算を行うなどの微調整が可能になる。

【0046】

トランジスタ41aに流れる電流は、カレントミラーによりトランジスタ41e及び41fにコピーされ、リングICOからなる電流制御発振器42に入力される。

【0047】

電流制御発振器42は、3段のインバータ42a、42b、42cをリング状に接続したリングICOからなり、トランジスタ42d、42e、42f、42g、42h、42iのゲート電流を制御することにより、インバータ42a、42b、42cに流れる電流(VCOリング電流)を制御することができる。

【符号の説明】

【0048】

10…位相周波数検出器、20…チャージポンプ、21…第1の電流源、22…第1のスイッチングトランジスタ、23…第2のスイッチングトランジスタ、24…第2の電流源、30…ループフィルタ、40…VCO、41…電圧電流変換回路、42…電流制御発振器、50…分周器、60…校正部、63…電圧比較器、64…電流制御装置、65…デジタルアナログ変換器、66…校正用電源。

【先行技術文献】

【特許文献】

【0049】

【特許文献1】特開2000−49597号公報

【技術分野】

【0001】

本発明は、ラジオ受信機やテレビ放送受信機、携帯電話機、複合機などの通信機器において、局部発振回路として用いられるPLL(Phase Locked Loop:位相同期ループ)回路に関する。

【背景技術】

【0002】

PLL回路の基本構成は、位相比較器、チャージポンプ、ループフィルタ、VCO(Voltage Controlled Oscillator:電圧制御発振器)、及び分周器からなる。そして、VCOの出力を分周器で分周した信号の位相と、基準信号の位相との位相差を位相比較器で検出し、この位相差に応じたパルス信号(UP信号、DOWN信号)をチャージポンプが出力し、その出力をループフィルタで平滑化してVCOを駆動する。PLL回路はこのような動作を繰り返し、VCOの出力である比較信号の周波数と位相を基準信号にロックさせる(特許文献1)。

【0003】

ここで、電圧電流変換回路及びリングICO(電流制御発振器)からなるVCOにおいては、ループフィルタの出力電圧が電圧電流変換回路により電流に変換され、この電流がリングICOの各遅延段におけるキャパシタを充放電し、順に各遅延段を遷移することにより遅延時間が発生することで周波数変調が行われる。

【0004】

近年、PLL回路には広帯域の発振周波数範囲(ロックレンジ)が要求されており、発振周波数範囲の広帯域化にはVCOのゲインを大きくする(入力電圧対出力周波数特性の傾きを急にする)ことが必要である。しかし、VCOのゲインを大きくすると、外乱に対する出力発振周波数の変動が大きくなる。

【0005】

また、VCOの製造時のばらつき及び温度変化などにより、VCOを構成するトランジスタの閾値電圧(Vth)がばらつき、トランジスタの動作速度が高速(fast)、標準速度(typical)、低速(slow)のように変動することは避けられない。

【0006】

特にICOとしてリングICOを用いる場合、ICOゲインが高い(=入力電流対出力周波数特性の傾きが急である)ため、製造プロセスの微細化に伴う製造ばらつきや温度変化などによるICO入力電流、つまりVCO入力電圧の変動が、遅延段における電流の遷移時間を決めている電流値の変動となり、発振周波数の大きな変動につながり、ジッタが増加してしまう。

【0007】

図5は、トランジスタの動作速度が高速(fast)、標準速度(typical)、低速(slow)の場合のVCOの入力電圧(Vin)対出力周波数(fout)特性を示す図である。この図においてVddは電源の電位である。

図5Aに示すように、トランジスタの動作速度が標準速度の場合、VCOの入力電圧がV1のときにターゲット周波数(ftarget)にロックしても、高速の場合はターゲット周波数をオーバーしてしまい、低速の場合はターゲット周波数に到達しない。

【0008】

ここでVCOのゲインを下げると、外乱に対する出力発振周波数の変動を小さくすることはできる。しかし、図5Bに示すように、高速及び低速では、入力電圧Vinを変化させてもターゲット周波数にロックさせることができなくなるという問題がある。

【0009】

また、一般にチャージポンプの電流源はカレントミラー回路で構成されるので、カレントミラー回路を構成するトランジスタを飽和領域で動作させなければならない。しかし、チャージポンプの出力段中間点の電位の変動により飽和領域で動作せずカレントミラー動作を行わないと、位相比較器から出力されるUP信号に応じた電流(ループフィルタのキャパシタへの充電電流)と、DOWN信号に応じた電流(ループフィルタのキャパシタからの放電電流)の電流値が異なるためにジッタが発生してしまうという問題もある。

【0010】

さらに、ループフィルタのキャパシタをMOSで作ることによりループフィルタを内蔵させることでPLL回路の面積の低減及びコスト削減を実現できるが、MOSの容量(キャパシタンス)に電圧依存性があるため、ループフィルタの入力電圧の変動によりPLLの安定性およびジッタ特性が変化してしまうという問題もある。

【0011】

特許文献1に記載されたPLL回路では、VCOの発振周波数がロックレンジに適合するように、VCOに供給する電流量を制御するキャリブレーションコントロール回路を設けることで、プロセス変動を電流量の調整で打ち消し、VCOの感度を低く設定できるとされている。

【0012】

しかし、このPLL回路では、チャージポンプの電流源を構成するトランジスタが飽和領域で動作しないためにカレントミラー動作を行わなくなることに起因するジッタ、及びループフィルタのキャパシタを構成するMOS容量の電圧依存性に起因するジッタの防止については考慮されていない。

【発明の概要】

【発明が解決しようとする課題】

【0013】

本発明は、このような問題を解決するためになされたものであり、その目的は、PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制できるようにすることである。

【課題を解決するための手段】

【0014】

本発明のPLL回路は、VCOと、当該VCOの出力信号を分周する分周器と、当該分周器の出力信号と基準周波数信号との位相差を検出する位相比較器と、当該位相比較器の位相差出力に応じた電流を生成するチャージポンプと、当該チャージポンプの電流を平滑化して前記VCOの入力電圧を生成するループフィルタと、前記VCOの出力信号の周波数が前記基準周波数になるとき、前記ループフィルタの出力電圧が所定値になるように、前記VCOの入力電圧対出力周波数特性を校正する校正手段と、を有するPLL回路である。

【発明の効果】

【0015】

本発明によれば、PLL回路において、VCOのゲインが低くても、VCOを構成するトランジスタの動作速度に関係なく、ターゲット周波数にロックさせることができ、かつ内蔵ループフィルタのMOS容量の電圧依存性に起因するジッタを抑制することができる。

【図面の簡単な説明】

【0016】

【図1】本発明の実施形態のPLL回路の構成を示すブロック図である。

【図2】図1におけるVCOの入力電圧対出力周波数特性を示す図である。

【図3】図1におけるチャージポンプ、ループフィルタ、及びVCOの回路図である。

【図4】図1におけるループフィルタのキャパシタを構成するMOSの印加電圧対容量特性を示す図である。

【図5】従来のPLL回路のVCOにおける入力電圧対出力周波数特性を示す図である。

【発明を実施するための形態】

【0017】

以下、本発明の実施形態について図面を参照して説明する。

〈PLL回路のブロック図〉

図1は、本発明の実施形態のPLL回路の構成を示すブロック図である。このPLL回路は、位相周波数検出器(PFD)10、チャージポンプ(CP)20、ループフィルタ(LF)30、VCO40、及び分周器(DIV)50からなるPLL部と、チャージポンプ61、ループフィルタ62、電圧比較器(COMP)63、電流制御装置(CONT)64、デジタルアナログ変換器(DAC)65、及び校正用電源66からなる校正部60からなる。

【0018】

校正部60を動作させるときは、PLL部のチャージポンプ20及びループフィルタ30をスリープ状態にすることで、それらをPLLのループから切り離し、校正部60をPLLのループに接続する。

【0019】

位相周波数検出器10は、基準信号(周波数:fref)と、比較信号である分周器50の出力信号(周波数:fout/N)とを比較し、位相差に応じて、UP信号、DOWN信号を出力する。

【0020】

チャージポンプ20は、位相周波数検出器10からのUP信号、DOWN信号に応じて、ループフィルタ30のキャパシタを充電するパルス電流を出力し、そのキャパシタから放電されたパルス電流を吸い込む。

【0021】

ループフィルタ30は、チャージポンプ20の出力を平滑化し、その平滑化電圧をVCO40へ送出する。ループフィルタ30により、PLL回路の安定性及び雑音特性が決まる。ループフィルタ30は、集積化されPLL回路のチップに内蔵されており、そのキャパシタはMOSで構成されている。

【0022】

VCO40は、電圧電流変換回路(V−I)41と、電流制御発振器(ICO)42からなる。電圧電流変換回路41は、ループフィルタ30から送出された電圧値を電流値に変換し、電流制御発振器42は、電圧電流変換回路41により変換された電流値に応じた周波数の発振信号を生成する。

【0023】

分周器50は、VCO40の出力信号を1/Nに分周し、位相周波数検出器10に送出する。

【0024】

校正部60のチャージポンプ61、ループフィルタ62は、それぞれPLL部のチャージポンプ20、ループフィルタ30と同一構成を持つダミー回路である。

【0025】

電圧比較器63は、ループフィルタ62の出力電圧(V’in)と、校正用電源66の電圧とを比較し、その大小関係を表す信号を電流制御装置64に送出する。校正用電源66の電圧はこのPLL回路の電源電圧Vddの1/2である。

【0026】

電流制御装置64は、電圧比較器63の出力信号に応じて、電圧電流変換回路41の出力電流を増減するためのデジタル制御電圧を生成し、デジタルアナログ変換器65は、そのデジタル制御電圧をアナログ化してV+、V-とし、電圧電流変換回路41に印加する。

【0027】

つまり、校正部60では、電圧電流変換回路41において、電流制御発振器42の発振周波数を決める電流値を校正(キャリブレーション)することにより、VCO40への入力電圧が製造ばらつきや温度変化などによって変化しても、一定の電圧に保つために、位相周波数検出器10の出力信号から生成した補正信号を電圧電流変換回路41に与えている。

【0028】

〈校正部60の動作〉

次に校正部60の校正(キャリブレーション)動作について説明する。

この校正動作では、PLL部が任意の基準周波数信号にロックしたときに、VCO40の入力電圧(=ループフィルタ30の出力電圧)VinがVdd/2になるように、VCO40内の電圧電流変換回路41の入力電圧対出力電流特性を調整することで、VCO40の入力電圧対出力周波数特性を調整する。

【0029】

図2は、VCO40の入力電圧対出力周波数特性を示す図である。VCO40の製造時のばらつき及び温度変化などにより、VCO40を構成するトランジスタの動作速度は高速(fast)、標準速度(typical)、低速(slow)のどれかになる。そして、図2のように、VCO40のゲインを下げると、VCO40の入力電圧がVdd/2のときに、標準速度(typical)ではターゲット周波数(ftarget)にロックさせることができても、高速(fast)及び低速(slow)では、ターゲット周波数にロックさせることができない。

【0030】

そこで、本実施形態のPLL回路では、VCO40の入力電圧対出力周波数特性が高速(fast)或いは低速(slow)であった場合、それぞれの特性を、標準速度(typical)の特性に近づけるように調整することで、ターゲット周波数にロックさせることができるようにする。

【0031】

まずチャージポンプ20及びループフィルタ30をスリープ状態にし、これらの回路をPLL部から切り離す。次に校正部60全体をアクティブにする。校正部60のチャージポンプ61、ループフィルタ62は、それぞれPLL部のチャージポンプ20、ループフィルタ30と同一構成を有するので、ループフィルタ62の出力電圧V’inは、PLL部が動作しているときのループフィルタ30の出力電圧Vinと同じになる。

【0032】

V’inがVdd/2より大きいか小さいかを電圧比較器63により比較する。比較の結果、V’in>Vdd/2のとき(図2の低速(slow)に相当)は、電流制御装置64は、制御電圧V-のレベルを小さい値から大きな値へと段階的に変化させる。これにより、図2の低速(slow)の特性を標準速度(typical)に接近させることができる。比較の結果、V’in<Vdd/2のとき(図2の高速(fast)に相当)は、電流制御装置64は、制御電圧V+のレベルを小さい値から大きな値へと段階的に変化させる。これにより、図2の高速(fast)の特性を標準速度(typical)に接近させることができる。

【0033】

V’in≒Vdd/2になったら校正を終了し、PLL部のチャージポンプ20及びループフィルタ30をアクティブにする。電流制御装置64の内部にV+、V-を記憶する機能を設けておけば、校正終了後、校正部60内のチャージポンプ61、ループフィルタ62、及び電圧比較器63をスリープ状態にすることで、消費電流を低減することができる。

【0034】

〈チャージポンプ、ループフィルタ、及びVCOの回路図〉

図3は、図1におけるチャージポンプ20、ループフィルタ30、及びVCO40の回路図である。

【0035】

図示のように、チャージポンプ20は、第1の電流源21と、UP信号によりオンする第1のスイッチングトランジスタ22と、DOWN信号によりオンする第2のスイッチングトランジスタ23と、第2の電流源24との直列回路が電源とグラウンドとの間に接続された構成を持つ。

【0036】

ここで、第1の電流源21及び第2の電流源24はカレントミラー回路により構成されているため、各電流源を構成するトランジスタを飽和領域で動作させる必要がある。そのため、ここではチャージポンプ20の出力段の中間点、即ち第1のスイッチングトランジスタ22と第2のスイッチングトランジスタ23の接続点Mの電位を電源の電位Vddの1/2程度になるようにした。

【0037】

このように構成すると、第1の電流源21からループフィルタ30のキャパシタに流れ込む充電電流Icp_pと、第2の電流源24がループフィルタ30のキャパシタから吸い込む放電電流Icp_nとが同程度の電流になり、ジッタが軽減される。これに対して、Icp_pとIcp_nが異なると、充電電流パルスと放電電流パルスの時間幅が異なるため、ループフィルタ30の出力電圧Vinが変動し、VCO40の出力信号のジッタが増加することになる。

【0038】

ループフィルタ30は、抵抗31及びキャパシタ32の直列回路と、キャパシタ33との並列回路からなり、チャージポンプ20からの充電電流及び放電電流を平滑化し、電圧Vinを生成する。

【0039】

キャパシタ32及び33はMOSにより構成されている。図4は、MOSのゲートとドレイン及びソースの間の印加電圧(Vc)、と容量Cchとの関係、を説明するための図である。

【0040】

図4Aに示すように、ゲートとドレイン及びソースの間に電圧Vcを印加すると、容量Cchは図4Bのように変化する。即ち、電圧Vcが閾値電圧Vthを超えるまでは、電圧Vcの増加に伴って増加する。この間、チャネルは形成されておらず、容量Cchは酸化膜容量値と空乏層容量値の直列容量値となる。電圧Vcが閾値電圧Vthを超えると、チャネルが形成され、容量Cchはゲート容量Coxとなる。

【0041】

ループフィルタ30のキャパシタ32及び33の容量により、PLLのループ安定性及び雑音特性が決まるため、図4Bにおいて、容量Cchが電圧Vc(入力電圧Vin)により変化しない電圧領域(点線に挟まれた安定領域)で使用することが望ましい。

【0042】

例えば、Vdd=1.0[V]程度において、Vthは0.4[V]程度であるので、VinをVdd/2程度に設定すれば容量Cchの安定領域で使用できる。これにより、PLLの安定性が保たれ、ジッタも軽減される。

【0043】

ループフィルタ30により平滑化され、雑音が除去された出力電圧Vinは、電圧電流変換回路41を構成するトランジスタ41bをオンにするので、トランジスタ41bにはVinに対応する電流I1が流れる。

【0044】

校正部60のデジタルアナログ変換器65から出力される電流補正信号(V-、V+)をトランジスタ41c、41dのゲート電圧とすることで、電流源であるトランジスタ41c、41dに流れる電流I-、I+を変化させる。V-、V+の各々に対してサイズの異なるトランジスタを複数用意するとともに、各トランジスタと出力ラインとの間にスイッチを設け、各トランジスタのオン・オフにより、電流補正信号を印加するトランジスタを選択するように構成することもできる。

【0045】

このときトランジスタ41aに流れる電流はI1+I+−I-となるので、I-、I+を変化させることにより、トランジスタ41aに流れる電流を任意の値にすることができる。ここで、電流補正信号V-により減算ができ、電流補正信号V+により加算ができるので、加算しすぎたときに減算を行うなどの微調整が可能になる。

【0046】

トランジスタ41aに流れる電流は、カレントミラーによりトランジスタ41e及び41fにコピーされ、リングICOからなる電流制御発振器42に入力される。

【0047】

電流制御発振器42は、3段のインバータ42a、42b、42cをリング状に接続したリングICOからなり、トランジスタ42d、42e、42f、42g、42h、42iのゲート電流を制御することにより、インバータ42a、42b、42cに流れる電流(VCOリング電流)を制御することができる。

【符号の説明】

【0048】

10…位相周波数検出器、20…チャージポンプ、21…第1の電流源、22…第1のスイッチングトランジスタ、23…第2のスイッチングトランジスタ、24…第2の電流源、30…ループフィルタ、40…VCO、41…電圧電流変換回路、42…電流制御発振器、50…分周器、60…校正部、63…電圧比較器、64…電流制御装置、65…デジタルアナログ変換器、66…校正用電源。

【先行技術文献】

【特許文献】

【0049】

【特許文献1】特開2000−49597号公報

【特許請求の範囲】

【請求項1】

VCOと、

当該VCOの出力信号を分周する分周器と、

当該分周器の出力信号と基準周波数信号との位相差を検出する位相比較器と、

当該位相比較器の位相差出力に応じた電流を生成するチャージポンプと、

当該チャージポンプの電流を平滑化して前記VCOの入力電圧を生成するループフィルタと、

前記VCOの出力信号の周波数が前記基準周波数になるとき、前記ループフィルタの出力電圧が所定値になるように、前記VCOの入力電圧対出力周波数特性を校正する校正手段と、

を有するPLL回路。

【請求項2】

請求項1に記載されたPLL回路において、

前記ループフィルタのキャパシタがMOSにより構成されており、前記所定値が当該MOSを入力電圧対容量特性の安定領域で動作させる値であるPLL回路。

【請求項3】

請求項1又は2に記載されたPLL回路において、

前記位相比較器は、前記位相差の大きさ及び方向に応じてUP信号、DOWN信号を出力し、

前記チャージポンプは、前記UP信号に応じて前記ループフィルタのキャパシタに充電電流を流す第1の電流源と、前記DOWN信号に応じて前記ループフィルタのキャパシタからの放電電流を流す第2の電流源とを有し、

前記第1の電流源及び第2の電流源がカレントミラー回路により構成されており、

前記第1の電流源、前記UP信号によりオンする第1のスイッチ、前記DOWN信号によりオンする第2のスイッチ、及び前記第2の電流源が電源とグラウンドとの間に直列に接続されており、

前記カレントミラー回路を構成するトランジスタが飽和領域で動作するように前記電源の電位、及び前記第1のスイッチと第2のスイッチの接続点の電位を設定したとき、当該電位が前記所定値となるように設定したPLL回路。

【請求項4】

請求項1〜3のいずれかに記載されたPLL回路において、

前記所定値は電源電圧の1/2であるPLL回路。

【請求項5】

請求項1に記載されたPLL回路において、

前記VCOは、電圧電流変換回路及び電流制御発振器からなり、前記校正手段は、当該電圧電流変換回路の入力電圧対出力電流特性を校正するPLL回路。

【請求項6】

請求項5に記載されたPLL回路において、

前記校正手段は、前記位相比較器の出力位相差に応じて、前記電圧電流変換回路の出力電流を増減するための制御電圧を生成するPLL回路。

【請求項7】

請求項1に記載されたPLL回路において、

前記校正手段は、前記チャージポンプ及びループフィルタのダミー回路と、前記チャージポンプ及びループフィルタをPLLから切り離し、前記ダミー回路をPLLに接続したときの前記ダミー回路の出力電圧と前記所定値との差異に応じて、前記VCOの入力電圧対出力周波数特性を校正する手段とを有するPLL回路。

【請求項1】

VCOと、

当該VCOの出力信号を分周する分周器と、

当該分周器の出力信号と基準周波数信号との位相差を検出する位相比較器と、

当該位相比較器の位相差出力に応じた電流を生成するチャージポンプと、

当該チャージポンプの電流を平滑化して前記VCOの入力電圧を生成するループフィルタと、

前記VCOの出力信号の周波数が前記基準周波数になるとき、前記ループフィルタの出力電圧が所定値になるように、前記VCOの入力電圧対出力周波数特性を校正する校正手段と、

を有するPLL回路。

【請求項2】

請求項1に記載されたPLL回路において、

前記ループフィルタのキャパシタがMOSにより構成されており、前記所定値が当該MOSを入力電圧対容量特性の安定領域で動作させる値であるPLL回路。

【請求項3】

請求項1又は2に記載されたPLL回路において、

前記位相比較器は、前記位相差の大きさ及び方向に応じてUP信号、DOWN信号を出力し、

前記チャージポンプは、前記UP信号に応じて前記ループフィルタのキャパシタに充電電流を流す第1の電流源と、前記DOWN信号に応じて前記ループフィルタのキャパシタからの放電電流を流す第2の電流源とを有し、

前記第1の電流源及び第2の電流源がカレントミラー回路により構成されており、

前記第1の電流源、前記UP信号によりオンする第1のスイッチ、前記DOWN信号によりオンする第2のスイッチ、及び前記第2の電流源が電源とグラウンドとの間に直列に接続されており、

前記カレントミラー回路を構成するトランジスタが飽和領域で動作するように前記電源の電位、及び前記第1のスイッチと第2のスイッチの接続点の電位を設定したとき、当該電位が前記所定値となるように設定したPLL回路。

【請求項4】

請求項1〜3のいずれかに記載されたPLL回路において、

前記所定値は電源電圧の1/2であるPLL回路。

【請求項5】

請求項1に記載されたPLL回路において、

前記VCOは、電圧電流変換回路及び電流制御発振器からなり、前記校正手段は、当該電圧電流変換回路の入力電圧対出力電流特性を校正するPLL回路。

【請求項6】

請求項5に記載されたPLL回路において、

前記校正手段は、前記位相比較器の出力位相差に応じて、前記電圧電流変換回路の出力電流を増減するための制御電圧を生成するPLL回路。

【請求項7】

請求項1に記載されたPLL回路において、

前記校正手段は、前記チャージポンプ及びループフィルタのダミー回路と、前記チャージポンプ及びループフィルタをPLLから切り離し、前記ダミー回路をPLLに接続したときの前記ダミー回路の出力電圧と前記所定値との差異に応じて、前記VCOの入力電圧対出力周波数特性を校正する手段とを有するPLL回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図2】

【図3】

【図4】

【図5】

【公開番号】特開2013−85077(P2013−85077A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−222920(P2011−222920)

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000006747)株式会社リコー (37,907)

【Fターム(参考)】

[ Back to top ]