PLL

【課題】 安定性と即応性を備えたPLLを提供すること。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

【解決手段】 本発明の実施形態によるPLLは、位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明の実施形態はPLLに関する。

【背景技術】

【0002】

PLL(Phase-locked loop)は、システムで必要とするさまざまな周波数を正確に得るために使われている。PLLは、CPUプロセッサをはじめ、マイコン、デジタルSoC、ベースバンド、FPGAなど、一般的なデジタルLSIに必ず搭載されている。その用途は、マイコンのクロックのように一定の周波数を出し続ける用途もあれば、無線通信のように頻繁に周波数を切り換える用途もある。

【0003】

従来、PLLは安定に動かすだけで要求仕様をほとんど満足できていた。周波数の変動や誤差が少ない高精度な出力が得られれば十分であった。しかし、近年では、適切なスペクトラム純度、つまりスプリアスや位相雑音が小さいことに対する要求に加えて、高速に応答することへの要求も高まっている。特に、デジタル化された通信/放送では、周波数を高速に切り替えるPLLが要求される。周波数を頻繁に切り替える用途では、周波数特性では把握しにくい時間軸での応答特性が問題となる。

【0004】

さらに、LSIの消費電力を削減するために、ノーマリ・オフ型コンピュータが提案されている。ノーマリ・オフ型コンピュータでは、各回路に供給される電源が頻繁に遮断される。PLLは、電源が遮断されると、安定に動作していた状態を消失してしまい、再度電源を投入した時に、動作が安定化するまでに少なくとも数msオーダーでの遅延が生じてしまう。PLLを電源遮断の対象外とすることも考えられるが、PLLの消費電流は10mAオーダーであり、PLLを電源遮断の対象外にすると、十分に消費電力を削減することができない。また、PLLの高速化だけを重視してPLLを設計すると、出力周波数が安定せず、アプリケーションに応用することが困難である。そのため、安定性と即応性を備えたPLLが望まれていた。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平7−131340号公報

【特許文献2】特開2000−341117号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

そこで本発明は、安定性と即応性を備えたPLLを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明の実施形態によるPLLは、参照信号とフィードバック信号の位相差を検出する位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御することを特徴としている。

【図面の簡単な説明】

【0008】

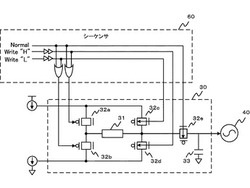

【図1】本発明の第1の実施形態に係るPLLのブロック図。

【図2】本発明の第1の実施形態に係るPLLの出力信号の周波数変化の模式図。

【図3】本発明の第1の実施形態に係るPLLのループフィルタ。

【図4】本発明の第1の実施形態に係るPLLのループフィルタの動作説明図。

【図5】本発明の第1の実施形態に係るPLLのループフィルタの動作説明図。

【図6】本発明の第1の実施形態に係るPLLのループフィルタの動作説明図。

【図7】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図8】本発明の第1の実施形態に係るPLLの処理フローチャート。

【図9】本発明の実施形態に係るPLLの減衰定数と、VCOの周波数変動の関係を示す図。

【図10】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図11】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図12】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図13】本発明の第2の実施形態に係るPLLのループフィルタ。

【図14】本発明の第2の実施形態に係るPLLの抵抗変化素子の状態を示す図。

【図15】本発明の第2の実施形態に係るPLL内のループフィルタの抵抗値変更を説明する図。

【図16】本発明の第2の実施形態に係るPLLの処理フローチャート。

【図17】本発明の第2の実施形態に係るPLLのシーケンサのタイミングチャート。

【図18】本発明の第2の実施形態に係るPLLのループフィルタの変形例。

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、本発明の実施形態について図面を参照して説明する。図1は、本実施形態に係るPLLを示すブロック図である。PLLは、位相検出器10、チャージポンプ20、ループフィルタ30、VCO(Voltage Controlled Oscillator)40、周波数分周器50、シーケンサ60、マルチプレクサ70、スイッチ80を有する。

【0010】

PLLは、参照信号frefの周波数のN倍の周波数を有する信号fvcoを生成する。位相検出器10には、参照信号frefとフィードバック信号fdivが入力され、参照信号frefとフィードバック信号fdivの位相を比較する。そして、フィードバック信号fdivの位相が進んでいる場合には、マルチプレクサ70を介してチャージポンプ20に降圧信号を出力し、フィードバック信号fdivの位相が遅れている場合には、マルチプレクサ70を介してチャージポンプ20に昇圧信号を出力する。

【0011】

チャージポンプ20は、位相検出器10から出力されてマルチプレクサ70を介して入力された信号に基づいて駆動し、昇圧または降圧の向きに電流を流す。チャージポンプ20で発生した電流はループフィルタ30に入力される。

【0012】

ループフィルタ30は、チャージポンプ20で発生した電流をVCO40に印加する電源電圧に変換し、VCO40に入力する。ループフィルタ30の詳細な構成については、図3を用いて後述する。VCO40は、ループフィルタ30から入力された電圧によって出力周波数を制御する発振回路である。VCO40の出力は、PLLの出力として出力されるとともに、スイッチ80を介して周波数分周器50に入力される。

【0013】

周波数分周器50は、入力された信号の周波数を整数分の1にして出力する。周波数分周器50の分周数は一般的に可変である。例えば、参照信号frefが1MHzで動作中に、周波数分周器50の分周数が250から300に変更されると、PLLの出力信号fvcoの周波数は、250MHzから300MHzに変化する。図2に、PLLの出力信号の周波数変化の模式図を示す。分周数が変更されてから出力信号の周波数が変化するまでには、応答特性のリンギングがあり、目標の周波数となるまでに時間がかかる。PLLの出力信号の周波数と目標周波数との差分が、所定の範囲内(±Δf)である状態を、PLLがロックアップ(安定化)した状態であると呼ぶ。また、PLLがロックアップ後、PLLの出力信号の周波数と目標周波数との差分が所定の範囲内を超えた状態をアンロックと呼ぶ。アンロックは、例えば、プロセッサからの要求で目標周波数が変更された場合や、参照周波数が変更された場合や、ノイズの影響によって生じる。PLLは、アンロック状態となった場合だけでなく、PLLの電源がOFFになった後で再びONになった場合に、出力信号の周波数と目標周波数との差分が所定の範囲を超える。

【0014】

PLLが安定化するまでの遅延は、PLLが帰還ループであることに起因する。PLLの閉ループの伝達関数を表現すると、以下のH(s)のようになる。

【数1】

ここで、KVCOはVCO40の利得([rad/s/V]または[Hz/V])、KPDは位相検出器10の利得([V/rad])を表す。また、Aはゲイン(定常値)を表し、ωnは自然周波数[rad]、ωLPFはループフィルタのカットオフ周波数[rad]、ζは減衰定数(ダンピングファクター)、Nは周波数分周器50の分周数である。

【0015】

PLLの出力信号fvcoの周波数を安定化させるまでにかかる時間は、ループフィルタ30の時定数に影響される。PLLの出力信号fvcoの角周波数の変化ωout(=2πfvco)は、以下の式で表される。

【数2】

周波数ステップ応答は以下に示す周期で振動し、時定数(ζωn)−1で減衰する関数となる。

【数3】

PLLのロックアップ時間を短くするためには、ζωnを最大化すれば良い。ζωnは、以下の式で表されるため、ループフィルタ30のフィルタ時定数がPLLのロックアップ時間に影響しているといえる。

【数4】

しかし、単純にζを大きくしてしまうと、ループフィルタのカットオフ周波数ωLPFが大きくなってしまい、PLLの出力信号fvcoにおける位相雑音が増大してしまう。また、参照信号frefの周波数成分が出力信号fvcoに回り込むスプリアスが発生してしまいPLLの基本的な要求仕様である安定した出力を達成できなくなってしまう。

【0016】

そこで、ループフィルタ30の時定数を、アンロック時やPLLの電源ON時に小さくし、ロックアップ後に大きくする。つまり、アンロック時やPLLの電源ON時には、ループフィルタ30の抵抗を小さくし、ロックアップ後には大きくする。なお、以降では、PLLの電源ON時にループフィルタ30の時定数を小さくする(すなわち、抵抗を低くする)として説明するが、PLLの電源OFF時にループフィルタ30の時定数を小さくしてから電源を切ることによって、PLLが起動されるときには時定数が小さい状態であるようにしても良い。

【0017】

本実施形態では、ループフィルタ30のアンロックが検出されたときだけでなく、電源ON(または電源OFF)が検出されたときにループフィルタ30の抵抗を小さくする。そのため、電源ON後に、PLLの出力信号の周波数と目標周波数との差分を比較するよりも前にループフィルタ30の時定数を小さくしておくことができる。これによって、電源ON後によりすばやくロックアップ状態にすることができる。

【0018】

このように、ループフィルタ30の時定数を制御するために、PLLにシーケンサ60、マルチプレクサ70、スイッチ80を設け、ループフィルタ30を図3に示すように構成する。

【0019】

シーケンサ60には、図示しない外部の制御回路から、電源遮断の要求があったとき、アンロック状態が発生する場合(例えば、参照周波数が変更されたときや、周波数分周器50の分周数が変更された場合)、ロックアップが検出された場合に、Control信号が入力される。ロックアップの検出は、図示しないロックアップ検出器によって行う。Control信号には、参照周波数や分周数、その他の設定項目などが含まれる。シーケンサ60は、Control信号に基づいて、ループフィルタ30、マルチプレクサ70、スイッチ80に対して制御信号を送信し、ループフィルタ30の時定数を調整する。図3の例では、シーケンサ60は、Control信号から、抵抗変化型素子31への書き込みを行うか否かを表す信号Normalと、抵抗変化型素子31を高抵抗状態に設定するか否かを示す信号Write”H”と、抵抗変化型素子31を低抵抗状態に設定するか否かを示す信号Write”L”とを生成し、ループフィルタ30を制御する。

【0020】

図3に示すように、ループフィルタ30は、抵抗変化型素子31、シーケンサ60によって制御されるスイッチ32a〜32e、キャパシタ33を有する。

【0021】

スイッチ32a〜32eは、nMOSとpMOSを用いて構成されるスイッチである。スイッチ32a、32cは、チャージポンプ20の充電側に接続され、スイッチ32b、32dは、チャージポンプ20の放電側に接続される。また、スイッチ32aと32bは接続され、スイッチ32cと32dは接続される。なお、図3では、スイッチ32a〜32eのnMOSに印加される信号を図示しており、pMOSに印加される信号は省略している。pMOSには、nMOSに入力される信号の反転値が印加される。

【0022】

抵抗変化型素子31は、例えばスピントルクトランスファーMRAM、相変化メモリ、電界効果による抵抗変化メモリ、イオンメモリなどである。ここでは、電流書き込み方式の抵抗変化型素子であるとして説明する。抵抗変化型素子31は、スイッチ32aおよび32bに一端が接続され、スイッチ32c、32dに他端が接続される。

【0023】

電流書き込み方式の抵抗変化型素子は、所定のプログラム電流が素子の端子間に印加されることによって素子の抵抗値が設定される素子であって、素子に流す電流の向きに応じて、低抵抗状態もしくは高抵抗状態となる。ここでは、抵抗変化素子31のスイッチ32c、32dに接続されている端子から、スイッチ32a、32bに接続されている端子に向かって電流が流れると、抵抗変化素子31が低抵抗状態となり、抵抗変化素子31のスイッチ32a、32bに接続されている端子から、スイッチ32c、32dに接続されている端子に向かって電流が流れると、抵抗変化素子31が高抵抗状態となるとして説明する。

【0024】

アンロック時やPLLの電源がONされたとき、シーケンサ60は、Normal信号を「L」、Write”H”信号を「L」、Write”L”信号を「H」に設定する。Write”H”信号とWrite”L”信号はそれぞれ、遅延器を通り、Normal信号とOR演算されて、スイッチ32a、32bに入力される。また、スイッチ32cには遅延器を介してWrite”H”信号が入力され、スイッチ32dには、遅延器を介してWrite”L”信号が入力される。スイッチ32eには、Normal信号が入力される。

【0025】

すると、スイッチ32b、32cがONとなり、スイッチ32a、32d、32eがOFFとなる。そのため、図4の破線で示すように、スイッチ32c、抵抗変化素子31、スイッチ32bを通る電流が流れる。この電流の大きさは、チャージポンプ20に入力するパルスの長さによって調節することができる。図4の破線で示すようにプログラム電流を流すと、抵抗変化素子31は低抵抗状態となる。

【0026】

一方、PLLがロックアップすると、シーケンサ60は、Normal信号を「L」、Write”H”信号を「H」、Write”L”信号を「L」に設定する。すると、スイッチ32a、32dがONとなり、スイッチ32b、32c、32eがOFFとなる。そのため、図5の破線で示すように、スイッチ32a、抵抗変化素子31、スイッチ32dを通る電流が流れる。プログラム電流を図5の破線で示す方向に流すと、抵抗変化素子31は高抵抗状態となる。

【0027】

抵抗変化素子31が低抵抗状態の場合、高抵抗状態の場合と比較して、ループフィルタ30の時定数が小さくなり、その逆数であるカットオフ周波数ωLPFは大きくなり、減衰定数ζも大きくなる。そのため、低抵抗状態では、高抵抗状態と比較してPLLを早く収束することができる。そして、高抵抗状態では、低抵抗状態と比較して位相雑音とスプリアスを抑え、PLLを安定的に動作させることができる。

【0028】

抵抗変化素子31の抵抗値を変更しない通常状態において、シーケンサ60は、Normal信号を「H」、Write”H”信号を「L」、Write”L”信号を「L」に設定する。すると、スイッチ32a、32b、32eはONとなり、スイッチ32c、32dがOFFとなる。すると、図6の破線で示すように、スイッチ32a、抵抗変化素子31、スイッチ32eを流れる電流、もしくはスイッチ32e、抵抗変化素子31、スイッチ32bを流れる電流を流すことが可能となる。つまり、位相検出器10からの出力に応じて、チャージポンプ20にて充電または放電が行われ、ループフィルタ30を介して、VCO40の電位VVCOが充電又は放電される。

【0029】

このとき、チャージポンプ20は充電または放電しか行わないため、抵抗変化素子31に抵抗値を書き込むプログラム電流よりも小さな電流となる。そのため、通常時において、抵抗変化素子31に書き込まれることは無い。また、位相検出器10の出力のスキューにより、瞬間的に充電と放電が重なって貫通電流が流れることがあるが、その際には、抵抗変化素子31には電流が流れずに、チャージポンプ20とスイッチ32a、32bにのみ電流が流れるため、抵抗変化素子31に誤書き込みは起こらない。

【0030】

ただし、PLLの電源投入直後など、偶発的に位相検出器10からチャージポンプ20へ出力するパルスが長くなった場合、抵抗変化素子31に誤書き込みがされる可能性がある。そこで、図7に示すように、スイッチ32f、32gと、突入抵抗34を挿入することによって、誤書き込みの防止を行うこともできる。スイッチ32f、32gは、Normal信号によってON/OFFするスイッチであって、通常動作時(Normal信号が「H」の時)にはOFFとなり、抵抗変化素子31への書き込み時(Normal信号が「L」の時)にはONとなる。これによって、通常動作時にチャージポンプ20から抵抗変化素子31へ流れる電流量が抑制され、抵抗変化素子31の誤書き込みを防ぐことができる。

【0031】

シーケンサ60は、抵抗変化素子31への抵抗値書き込みを行う状態か、通常動作状態かに応じて、図1のマルチプレクサ70とスイッチ80の制御も行う。マルチプレクサ70は、位相検出器10とチャージポンプ20との間に設けられる。抵抗変化素子31の抵抗値を変更するとき、マルチプレクサ70によって位相検出器10とチャージポンプ20の間の接続を断ち、PLLのフィードバックループを遮断する。マルチプレクサ70は、Normal信号によって出力信号を切り替えるスイッチであって、通常動作時(Normal信号が「H」の時)には位相検出器10からの信号を出力し、抵抗変化素子31への書き込み時(Normal信号が「L」の時)にはシーケンサ60からの信号を出力する。シーケンサ60は、抵抗変化素子31の抵抗値を変更するときに、マルチプレクサ70に書き込み用のパルス信号を入力し、位相検出器10に替ってチャージポンプ20を制御する。

【0032】

スイッチ80は、周波数分周器50の前段と、位相検出器10の前段に設けられる。シーケンサ60は、抵抗変化素子31の抵抗値を変更するときに、スイッチ80に制御信号を入力し、スイッチ80をOFFにする。このスイッチ80のOFFによっても、PLLのフィードバックループを遮断することができる。なお、スイッチ80は、CMOSスイッチであっても良いし、抵抗が無限大になる抵抗変化型素子でも良い。

【0033】

このように、抵抗変化素子31の抵抗値を変更するときに、PLLのフィードバックループを遮断することによって、VCO40と位相検出器10の出力による雑音の影響を受けることを避ける。

【0034】

なお、マルチプレクサ70だけでもPLLのフィードバックループを遮断することができるが、スイッチ80によってもPLLのフィードバックループを遮断した方が、抵抗変化素子31の抵抗値を変更時のPLLの電力を削減することができる。これは、デジタル動作する位相検出器10と周波数分周器50の動作を停止させるからである。

【0035】

図8にループフィルタ30の抵抗値を変更するときのPLLの処理フローチャートを示す。外部の制御回路から、PLLの参照周波数を変えることや、PLLを起動することを示す信号を受け取ると、シーケンサ60がマルチプレクサ70、スイッチ80へ制御信号を入力し、フィードバックループを遮断する(S10)。そして、シーケンサ60が、ループフィルタ30内に設けられたスイッチ32a〜32e(または、32a〜32g)のON/OFFを制御する(S11)。そして、チャージポンプ20経由でループフィルタ30に電流を流すことによって抵抗変化素子31の抵抗値を変更する(S12)。その後、シーケンサ60がマルチプレクサ70、スイッチ80へ制御信号を入力して、フィードバックループを元に戻す。

【0036】

ここで、ループフィルタ30の減衰定数ζの適切な決定方法について述べる。数式4に示したζωnを最大化するために、ループフィルタ30の応答を高速にすればよい。図9に、減衰定数ζと、VCO40の周波数変動の関係を模式的に表す。図9に示すとおり、減衰定数ζが小さいとPLLのフィードバックループは不足制動となり、チャージポンプ20のパルス動作に対して、VCO40の周波数変動は小さくなり、PLLが安定して動作する。それに対して、減衰定数ζが大きいとチャージポンプ20のパルス動作に対するVCO40の周波数変動は大きくなり、PLLのフィードバックループの制動作用が強くなり、減衰振動の収束性が高くなり、その結果PLLが速くロックアップする。そこで、アンロック時やPLLの電源投入時には、数式5を満たすように減衰定数ζを設定して、ロックアップまでの振動を回避することが望ましい。少なくとも、減衰定数ζを1程度に設定すると、セットリング時間を短くすることが可能となる。

【数5】

ロックアップに近づくにつれ、ループフィルタ30の減衰定数ζを低くするように抵抗変化素子31の抵抗値を高くすることによって、位相検出器10へ出力する信号から位相雑音とスプリアスを抑圧することができ、PLLがより安定的に動作する。

【0037】

このように、PLLがアンロックした時や電源を投入されたときには抵抗変化素子31の抵抗値を低く設定し、PLLがロックアップすると抵抗変化素子31の抵抗値を高く設定することによって、安定性と即応性を備えたPLLを提供することができる。また、本実施形態によるPLLでは、抵抗変化素子を用いているため、1つの素子で抵抗値を低抵抗状態と高抵抗状態に変更することができる。

【0038】

(変形例1)

図3を用いた説明では、ループフィルタ30内のスイッチ32a〜32dが、nMOSとpMOSを用いたスイッチであるとして説明したが、チャージポンプ20からのパスが充電と放電に明確に分かれているため、図10に示すように、充電のパスにはpMOSのスイッチを用いて、放電のパスにはnMOSのスイッチを用いても良い。こうすることで、スイッチの回路素子数を削減することが可能である。なお、充電のパスにnMOSのスイッチを用い、放電のパスにpMOSのスイッチを用いることもできるが、トランジスタのオン抵抗が大きくなり、ループフィルタの特性を予測することが難しい。そのため、充電のパスにpMOSのスイッチ、放電のパスにnMOSのスイッチを用いた方が望ましい。

【0039】

図10に示すループフィルタ130に対するシーケンサ60の入力信号は、図3を用いて説明したループフィルタ30に対する入力と同じである。アンロック時やPLLの電源がONされたとき、シーケンサ60は、Normal信号を「L」、Write”H”信号を「L」、Write”L”信号を「H」に設定する。すると、スイッチ132bと132cがONとなり、スイッチ132aと132dがOFFとなる。このため、図4を用いて説明した状態と同様に、抵抗変化素子31が低抵抗状態となる。

【0040】

PLLがロックアップすると、シーケンサ60は、Normal信号を「L」、Write”H”信号を「H」、Write”L”信号を「L」に設定する。すると、スイッチ132aと132dがONとなり、スイッチ132bと132cがOFFとなる。このため、図5を用いて説明した状態と同様に、抵抗変化素子31が高抵抗状態となる。

【0041】

通常状態において、シーケンサ60は、Normal信号を「H」、Write”H”信号を「L」、Write”L”信号を「L」に設定する。すると、スイッチ132a、132b、32eはONとなり、スイッチ132c、132dがOFFとなる。すると、図6を用いて説明した状態と同様の状態となる。

【0042】

(変形例2)

抵抗変化素子として3端子の素子を用いることもできる。3端子の抵抗変化素子は、抵抗値を書き込むための端子を有し、この端子に入力される値に応じて抵抗変化素子に書き込まれる抵抗値が決まる。

【0043】

図11は、3端子の抵抗変化素子を用いたループフィルタを示す図である。3端子の抵抗変化素子231には、シーケンサ60から制御信号が入力され、制御信号に応じて抵抗変化素子231の抵抗値が変化する。シーケンサ60は、抵抗変化素子231の抵抗値を変更するときには、スイッチ32eをOFFにし、通常状態では、スイッチ32eをONにするよう制御する。

【0044】

このように3端子の抵抗変化素子を用いると、図3のループフィルタ30では必要であったスイッチ32a〜32dを設ける必要が無い。

【0045】

(変形例3)

PLLの電源OFF時に、VCO40の電位VVCOの放電を防止するため、図12のようにループフィルタを構成しても良い。図12に示すループフィルタ330では、図3に示すループフィルタ30に、スイッチ32hを追加した構成である。シーケンサ60は、PLLの電源OFF時にスイッチ32eとスイッチ32hとをOFFするように制御する。これによって、PLLの電源がOFFされたときに、キャパシタ33に蓄えられた電荷を保持しておくことができる。そのため、再度電源がONされたときに、ある程度キャパシタ33に電荷が蓄えられた状態であるため、早くロックアップすることができる。ただし、PLLの電源OFF時に、スイッチ32eとスイッチ32hとをOFFするためにシーケンサ60に電圧を引加しておく必要がある。スイッチ32eとスイッチ32hに抵抗が無限大になる抵抗変化型素子を用いればPLLの電源OFF時に、シーケンサ60の電源もOFFにすることができる。

【0046】

以上、本実施形態およびその変形例を説明したが、以上の変形例の他にも、本発明の要旨を逸脱しない範囲において、本実施形態を適宜変更することができる。例えば、変形例1〜3に対しても、誤書き込みを防止するために、図7で説明したようにスイッチと突入抵抗を設けても良い。変形例1〜3やその他の変形のうちのいくつかを組み合わせても良い。

【0047】

(第2の実施形態)

本実施形態は、ループフィルタ内に抵抗変化素子を複数設けた場合の実施形態である。図13は、本実施形態に係るPLLのループフィルタ530とシーケンサ560とを示す図である。本実施形態に係るPLLの他の構成要素は第1の実施形態と同様であるため、説明を省略する。なお、図13では、図3と同様に、スイッチ32a〜32mのnMOSに印加される信号を図示しており、pMOSに印加される信号は省略している。pMOSには、nMOSに入力される信号の反転値が印加される。

【0048】

図13では、一例として、2つの抵抗変化素子が並列に並べられたループフィルタ530を示す。ループフィルタ530では、第1の抵抗変化素子31aの両端にスイッチ32i、32jを設け、第2の抵抗変化素子31bの両端にスイッチ32k、32mを設ける。スイッチ32i、32j、32k、32mは、シーケンサ560から入力される制御信号によってON/OFFする。スイッチ32i、32jには、シーケンサ560からR1_en信号が入力される。R1_en信号が「H」であれば、スイッチ32i、32jがONとなる。スイッチ32k、32mには、シーケンサ560からR2_en信号が入力される。R2_en信号が「H」であれば、スイッチ32k、32mがONとなる。

【0049】

これらのスイッチによって、第1の抵抗変化素子31aに電流を流すのか否かと、第2の抵抗変化素子31bに電流を流すのか否かを選択することができる。なお、以降では、抵抗変化素子の両端に付けられたスイッチ32iと32j、もしくは、32kと32mをOFFにした状態を、抵抗変化素子がOFFの状態であると称する。それに対して、抵抗変化素子の両端に付けられたスイッチ32iと32j、もしくは、32kと32mをONにした状態を抵抗変化素子がONの状態であると称する。

【0050】

図14は、第1の抵抗変化素子31aの状態と第2の抵抗変化素子31bの状態の組み合わせを示す図である。第1の抵抗変化素子31aと第2の抵抗変化素子31bは、それぞれ、高抵抗状態、低抵抗状態、OFFの状態となることができる。なお、第1の抵抗変化素子31aと第2の抵抗変化素子31bの両方がONの状態であれば、ループフィルタ530の抵抗値は、第1の抵抗変化素子31aと第2の抵抗変化素子31bの合成抵抗の値となる。

【0051】

第1の抵抗変化素子31aと第2の抵抗変化素子31bそれぞれの高抵抗状態、低抵抗状態が全て異なる抵抗値であるならば、チャージポンプ20とループフィルタ530の間を流れる電流にかかる抵抗値は、8つの状態(図14の状態1〜状態8)それぞれに異なる値となる。

【0052】

これを利用して、PLLがアンロックとなった時や電源ONされた時にはループフィルタ530の抵抗値を低く設定し、PLLが安定状態に近づくにつれて、段階的に高くなるよう設定することができる。

【0053】

例えば、PLLに入力される参照周波数からクロックをカウントして、PLLがアンロックとなった時や電源ONされた時からの経過時間を測り、図15に示すように、所定の時間Δtが経過する毎に段階分けする。そして、第1段階では図14の状態8、第2段階では状態6、第3段階では状態4、第4段階では状態1というように、段階を経る毎にループフィルタ530の抵抗値が高くなるよう第1の抵抗変化素子31aと第2の抵抗変化素子31bの抵抗値および、それらの素子の両端に設けられたスイッチのON/OFF状態を切り替える。各段階でどの状態にするかは、シーケンサ560内に不揮発ルックアップテーブルを設けて、そのルックアップテーブルに予め設定しておくことができる。

【0054】

また、シーケンサ560に対して位相検出器10の出力を入力し、位相検出器10の出力する位相差の時間的変化に応じて、ループフィルタ530の抵抗値を段階的に変更しても良い。

【0055】

PLLのアンロックが検出された場合と、PLLが電源OFFの状態からの起動が要求された場合とで、ループフィルタ530の抵抗値の初期値を変えることもできる。例えば、PLLのアンロックが検出された場合の方が、PLLの起動が要求されたときよりも安定状態に近いと考えられる。そこで、PLLのアンロックが検出された場合には、ループフィルタ530の抵抗値の初期値を高くし(例えば図14の状態5)、PLLの起動が要求された場合には、ループフィルタ530の抵抗値の初期値を低くする(例えば図14の状態8)。これによって、PLLの起動が要求された場合には、より早くロックアップ状態にでき、PLLのアンロックが検出された場合には、より安定的に動作させることができる。

【0056】

図16にループフィルタ530の抵抗値を変更するときのPLLの処理フローチャートを示す。図16では、図8と同じ処理には同じ記号を付す。ループフィルタ530の抵抗値を変更する場合、スイッチ32i〜32mを用いて抵抗値を変更する抵抗変化素子の1つを選択し、第1の実施形態にて説明したように、スイッチ32a〜32eのON/OFFを制御する(S11)。そして、選択した抵抗変化素子への書き込み終了後、他の抵抗変化素子への書き込みも必要であれば(S20のNo)、その抵抗変化素子を選択して書き込みを行う。

【0057】

図17に、シーケンサ60のタイミングチャートを示す。なお、図17のCLK_refは、PLLに入力される参照周波数を表す。図17に示すように、通常状態では、Normal信号を「H」に設定し、抵抗変化素子に書き込む場合には、「L」に設定する。また、抵抗変化素子の書き込み先に応じて、R1_en信号またはR2_en信号のいずれか一方を「H」、他方を「L」にする。さらに抵抗変化素子に書き込む抵抗値に応じて、Write”H”信号またはWrite”L”信号のいずれか一方を「H」、他方を「L」にする。通常動作時のR1_en信号とR2_en信号は、シーケンサ60内に設けられたルックアップテーブルに基づいて、どちらか少なくとも一方を「H」にする。

【0058】

このように、第2の実施形態によれば、ループフィルタの抵抗値をきめ細かく変更することができる。また、本実施形態によれば、抵抗変化素子を用いるため、固定の抵抗値を有する抵抗を用いた場合と比較して、ループフィルタの抵抗値をより細かい段階で制御することが可能となる。

【0059】

(変形例1)

図13を用いた説明では、ループフィルタ30内のスイッチ32i、32j、32k、32mが、nMOSとpMOSを用いたスイッチであるとして説明したが、図18に示すように、これらをnMOSのスイッチ32n〜32qとして構成しても良い。こうすることで、スイッチの回路素子数を削減することが可能である。なお、nMOSのスイッチ32n〜32qの代わりに、pMOSのスイッチを用いても良い。

【0060】

本実施形態においても、他に様々な変更が可能である。第1の実施形態において説明した変形例を適用しても良い。また、本実施形態の説明では、2つの抵抗変化素子を用いた場合を例としたが、3つ以上の抵抗変化素子を用いても良い。ただし、抵抗変化素子を増やすと、その両端に設けるスイッチが増え、スイッチを構成するトランジスタの接合容量がループフィルタの利得に影響を与える可能性がある。そのため、並列に接続する抵抗変化素子の数は、4以下が好ましい。

【0061】

上記実施形態に限定されることはなく、本発明の要旨を逸脱しない範囲において、適宜変更しても良い。

【符号の説明】

【0062】

10…位相検出器、 20…チャージポンプ、 30…ループフィルタ、 40…VCO、 50…周波数分周器、 60…シーケンサ、 70…マルチプレクサ、 80…スイッチ、 31…抵抗変化素子、 32…スイッチ、 33…キャパシタ、 34…突入抵抗

【技術分野】

【0001】

本発明の実施形態はPLLに関する。

【背景技術】

【0002】

PLL(Phase-locked loop)は、システムで必要とするさまざまな周波数を正確に得るために使われている。PLLは、CPUプロセッサをはじめ、マイコン、デジタルSoC、ベースバンド、FPGAなど、一般的なデジタルLSIに必ず搭載されている。その用途は、マイコンのクロックのように一定の周波数を出し続ける用途もあれば、無線通信のように頻繁に周波数を切り換える用途もある。

【0003】

従来、PLLは安定に動かすだけで要求仕様をほとんど満足できていた。周波数の変動や誤差が少ない高精度な出力が得られれば十分であった。しかし、近年では、適切なスペクトラム純度、つまりスプリアスや位相雑音が小さいことに対する要求に加えて、高速に応答することへの要求も高まっている。特に、デジタル化された通信/放送では、周波数を高速に切り替えるPLLが要求される。周波数を頻繁に切り替える用途では、周波数特性では把握しにくい時間軸での応答特性が問題となる。

【0004】

さらに、LSIの消費電力を削減するために、ノーマリ・オフ型コンピュータが提案されている。ノーマリ・オフ型コンピュータでは、各回路に供給される電源が頻繁に遮断される。PLLは、電源が遮断されると、安定に動作していた状態を消失してしまい、再度電源を投入した時に、動作が安定化するまでに少なくとも数msオーダーでの遅延が生じてしまう。PLLを電源遮断の対象外とすることも考えられるが、PLLの消費電流は10mAオーダーであり、PLLを電源遮断の対象外にすると、十分に消費電力を削減することができない。また、PLLの高速化だけを重視してPLLを設計すると、出力周波数が安定せず、アプリケーションに応用することが困難である。そのため、安定性と即応性を備えたPLLが望まれていた。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開平7−131340号公報

【特許文献2】特開2000−341117号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

そこで本発明は、安定性と即応性を備えたPLLを提供することを目的とする。

【課題を解決するための手段】

【0007】

上記目的を達成するために、本発明の実施形態によるPLLは、参照信号とフィードバック信号の位相差を検出する位相検出器と、前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、前記ループフィルタを制御するシーケンサとを有するPLLであって、前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御することを特徴としている。

【図面の簡単な説明】

【0008】

【図1】本発明の第1の実施形態に係るPLLのブロック図。

【図2】本発明の第1の実施形態に係るPLLの出力信号の周波数変化の模式図。

【図3】本発明の第1の実施形態に係るPLLのループフィルタ。

【図4】本発明の第1の実施形態に係るPLLのループフィルタの動作説明図。

【図5】本発明の第1の実施形態に係るPLLのループフィルタの動作説明図。

【図6】本発明の第1の実施形態に係るPLLのループフィルタの動作説明図。

【図7】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図8】本発明の第1の実施形態に係るPLLの処理フローチャート。

【図9】本発明の実施形態に係るPLLの減衰定数と、VCOの周波数変動の関係を示す図。

【図10】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図11】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図12】本発明の第1の実施形態に係るPLLのループフィルタの変形例。

【図13】本発明の第2の実施形態に係るPLLのループフィルタ。

【図14】本発明の第2の実施形態に係るPLLの抵抗変化素子の状態を示す図。

【図15】本発明の第2の実施形態に係るPLL内のループフィルタの抵抗値変更を説明する図。

【図16】本発明の第2の実施形態に係るPLLの処理フローチャート。

【図17】本発明の第2の実施形態に係るPLLのシーケンサのタイミングチャート。

【図18】本発明の第2の実施形態に係るPLLのループフィルタの変形例。

【発明を実施するための形態】

【0009】

(第1の実施形態)

以下、本発明の実施形態について図面を参照して説明する。図1は、本実施形態に係るPLLを示すブロック図である。PLLは、位相検出器10、チャージポンプ20、ループフィルタ30、VCO(Voltage Controlled Oscillator)40、周波数分周器50、シーケンサ60、マルチプレクサ70、スイッチ80を有する。

【0010】

PLLは、参照信号frefの周波数のN倍の周波数を有する信号fvcoを生成する。位相検出器10には、参照信号frefとフィードバック信号fdivが入力され、参照信号frefとフィードバック信号fdivの位相を比較する。そして、フィードバック信号fdivの位相が進んでいる場合には、マルチプレクサ70を介してチャージポンプ20に降圧信号を出力し、フィードバック信号fdivの位相が遅れている場合には、マルチプレクサ70を介してチャージポンプ20に昇圧信号を出力する。

【0011】

チャージポンプ20は、位相検出器10から出力されてマルチプレクサ70を介して入力された信号に基づいて駆動し、昇圧または降圧の向きに電流を流す。チャージポンプ20で発生した電流はループフィルタ30に入力される。

【0012】

ループフィルタ30は、チャージポンプ20で発生した電流をVCO40に印加する電源電圧に変換し、VCO40に入力する。ループフィルタ30の詳細な構成については、図3を用いて後述する。VCO40は、ループフィルタ30から入力された電圧によって出力周波数を制御する発振回路である。VCO40の出力は、PLLの出力として出力されるとともに、スイッチ80を介して周波数分周器50に入力される。

【0013】

周波数分周器50は、入力された信号の周波数を整数分の1にして出力する。周波数分周器50の分周数は一般的に可変である。例えば、参照信号frefが1MHzで動作中に、周波数分周器50の分周数が250から300に変更されると、PLLの出力信号fvcoの周波数は、250MHzから300MHzに変化する。図2に、PLLの出力信号の周波数変化の模式図を示す。分周数が変更されてから出力信号の周波数が変化するまでには、応答特性のリンギングがあり、目標の周波数となるまでに時間がかかる。PLLの出力信号の周波数と目標周波数との差分が、所定の範囲内(±Δf)である状態を、PLLがロックアップ(安定化)した状態であると呼ぶ。また、PLLがロックアップ後、PLLの出力信号の周波数と目標周波数との差分が所定の範囲内を超えた状態をアンロックと呼ぶ。アンロックは、例えば、プロセッサからの要求で目標周波数が変更された場合や、参照周波数が変更された場合や、ノイズの影響によって生じる。PLLは、アンロック状態となった場合だけでなく、PLLの電源がOFFになった後で再びONになった場合に、出力信号の周波数と目標周波数との差分が所定の範囲を超える。

【0014】

PLLが安定化するまでの遅延は、PLLが帰還ループであることに起因する。PLLの閉ループの伝達関数を表現すると、以下のH(s)のようになる。

【数1】

ここで、KVCOはVCO40の利得([rad/s/V]または[Hz/V])、KPDは位相検出器10の利得([V/rad])を表す。また、Aはゲイン(定常値)を表し、ωnは自然周波数[rad]、ωLPFはループフィルタのカットオフ周波数[rad]、ζは減衰定数(ダンピングファクター)、Nは周波数分周器50の分周数である。

【0015】

PLLの出力信号fvcoの周波数を安定化させるまでにかかる時間は、ループフィルタ30の時定数に影響される。PLLの出力信号fvcoの角周波数の変化ωout(=2πfvco)は、以下の式で表される。

【数2】

周波数ステップ応答は以下に示す周期で振動し、時定数(ζωn)−1で減衰する関数となる。

【数3】

PLLのロックアップ時間を短くするためには、ζωnを最大化すれば良い。ζωnは、以下の式で表されるため、ループフィルタ30のフィルタ時定数がPLLのロックアップ時間に影響しているといえる。

【数4】

しかし、単純にζを大きくしてしまうと、ループフィルタのカットオフ周波数ωLPFが大きくなってしまい、PLLの出力信号fvcoにおける位相雑音が増大してしまう。また、参照信号frefの周波数成分が出力信号fvcoに回り込むスプリアスが発生してしまいPLLの基本的な要求仕様である安定した出力を達成できなくなってしまう。

【0016】

そこで、ループフィルタ30の時定数を、アンロック時やPLLの電源ON時に小さくし、ロックアップ後に大きくする。つまり、アンロック時やPLLの電源ON時には、ループフィルタ30の抵抗を小さくし、ロックアップ後には大きくする。なお、以降では、PLLの電源ON時にループフィルタ30の時定数を小さくする(すなわち、抵抗を低くする)として説明するが、PLLの電源OFF時にループフィルタ30の時定数を小さくしてから電源を切ることによって、PLLが起動されるときには時定数が小さい状態であるようにしても良い。

【0017】

本実施形態では、ループフィルタ30のアンロックが検出されたときだけでなく、電源ON(または電源OFF)が検出されたときにループフィルタ30の抵抗を小さくする。そのため、電源ON後に、PLLの出力信号の周波数と目標周波数との差分を比較するよりも前にループフィルタ30の時定数を小さくしておくことができる。これによって、電源ON後によりすばやくロックアップ状態にすることができる。

【0018】

このように、ループフィルタ30の時定数を制御するために、PLLにシーケンサ60、マルチプレクサ70、スイッチ80を設け、ループフィルタ30を図3に示すように構成する。

【0019】

シーケンサ60には、図示しない外部の制御回路から、電源遮断の要求があったとき、アンロック状態が発生する場合(例えば、参照周波数が変更されたときや、周波数分周器50の分周数が変更された場合)、ロックアップが検出された場合に、Control信号が入力される。ロックアップの検出は、図示しないロックアップ検出器によって行う。Control信号には、参照周波数や分周数、その他の設定項目などが含まれる。シーケンサ60は、Control信号に基づいて、ループフィルタ30、マルチプレクサ70、スイッチ80に対して制御信号を送信し、ループフィルタ30の時定数を調整する。図3の例では、シーケンサ60は、Control信号から、抵抗変化型素子31への書き込みを行うか否かを表す信号Normalと、抵抗変化型素子31を高抵抗状態に設定するか否かを示す信号Write”H”と、抵抗変化型素子31を低抵抗状態に設定するか否かを示す信号Write”L”とを生成し、ループフィルタ30を制御する。

【0020】

図3に示すように、ループフィルタ30は、抵抗変化型素子31、シーケンサ60によって制御されるスイッチ32a〜32e、キャパシタ33を有する。

【0021】

スイッチ32a〜32eは、nMOSとpMOSを用いて構成されるスイッチである。スイッチ32a、32cは、チャージポンプ20の充電側に接続され、スイッチ32b、32dは、チャージポンプ20の放電側に接続される。また、スイッチ32aと32bは接続され、スイッチ32cと32dは接続される。なお、図3では、スイッチ32a〜32eのnMOSに印加される信号を図示しており、pMOSに印加される信号は省略している。pMOSには、nMOSに入力される信号の反転値が印加される。

【0022】

抵抗変化型素子31は、例えばスピントルクトランスファーMRAM、相変化メモリ、電界効果による抵抗変化メモリ、イオンメモリなどである。ここでは、電流書き込み方式の抵抗変化型素子であるとして説明する。抵抗変化型素子31は、スイッチ32aおよび32bに一端が接続され、スイッチ32c、32dに他端が接続される。

【0023】

電流書き込み方式の抵抗変化型素子は、所定のプログラム電流が素子の端子間に印加されることによって素子の抵抗値が設定される素子であって、素子に流す電流の向きに応じて、低抵抗状態もしくは高抵抗状態となる。ここでは、抵抗変化素子31のスイッチ32c、32dに接続されている端子から、スイッチ32a、32bに接続されている端子に向かって電流が流れると、抵抗変化素子31が低抵抗状態となり、抵抗変化素子31のスイッチ32a、32bに接続されている端子から、スイッチ32c、32dに接続されている端子に向かって電流が流れると、抵抗変化素子31が高抵抗状態となるとして説明する。

【0024】

アンロック時やPLLの電源がONされたとき、シーケンサ60は、Normal信号を「L」、Write”H”信号を「L」、Write”L”信号を「H」に設定する。Write”H”信号とWrite”L”信号はそれぞれ、遅延器を通り、Normal信号とOR演算されて、スイッチ32a、32bに入力される。また、スイッチ32cには遅延器を介してWrite”H”信号が入力され、スイッチ32dには、遅延器を介してWrite”L”信号が入力される。スイッチ32eには、Normal信号が入力される。

【0025】

すると、スイッチ32b、32cがONとなり、スイッチ32a、32d、32eがOFFとなる。そのため、図4の破線で示すように、スイッチ32c、抵抗変化素子31、スイッチ32bを通る電流が流れる。この電流の大きさは、チャージポンプ20に入力するパルスの長さによって調節することができる。図4の破線で示すようにプログラム電流を流すと、抵抗変化素子31は低抵抗状態となる。

【0026】

一方、PLLがロックアップすると、シーケンサ60は、Normal信号を「L」、Write”H”信号を「H」、Write”L”信号を「L」に設定する。すると、スイッチ32a、32dがONとなり、スイッチ32b、32c、32eがOFFとなる。そのため、図5の破線で示すように、スイッチ32a、抵抗変化素子31、スイッチ32dを通る電流が流れる。プログラム電流を図5の破線で示す方向に流すと、抵抗変化素子31は高抵抗状態となる。

【0027】

抵抗変化素子31が低抵抗状態の場合、高抵抗状態の場合と比較して、ループフィルタ30の時定数が小さくなり、その逆数であるカットオフ周波数ωLPFは大きくなり、減衰定数ζも大きくなる。そのため、低抵抗状態では、高抵抗状態と比較してPLLを早く収束することができる。そして、高抵抗状態では、低抵抗状態と比較して位相雑音とスプリアスを抑え、PLLを安定的に動作させることができる。

【0028】

抵抗変化素子31の抵抗値を変更しない通常状態において、シーケンサ60は、Normal信号を「H」、Write”H”信号を「L」、Write”L”信号を「L」に設定する。すると、スイッチ32a、32b、32eはONとなり、スイッチ32c、32dがOFFとなる。すると、図6の破線で示すように、スイッチ32a、抵抗変化素子31、スイッチ32eを流れる電流、もしくはスイッチ32e、抵抗変化素子31、スイッチ32bを流れる電流を流すことが可能となる。つまり、位相検出器10からの出力に応じて、チャージポンプ20にて充電または放電が行われ、ループフィルタ30を介して、VCO40の電位VVCOが充電又は放電される。

【0029】

このとき、チャージポンプ20は充電または放電しか行わないため、抵抗変化素子31に抵抗値を書き込むプログラム電流よりも小さな電流となる。そのため、通常時において、抵抗変化素子31に書き込まれることは無い。また、位相検出器10の出力のスキューにより、瞬間的に充電と放電が重なって貫通電流が流れることがあるが、その際には、抵抗変化素子31には電流が流れずに、チャージポンプ20とスイッチ32a、32bにのみ電流が流れるため、抵抗変化素子31に誤書き込みは起こらない。

【0030】

ただし、PLLの電源投入直後など、偶発的に位相検出器10からチャージポンプ20へ出力するパルスが長くなった場合、抵抗変化素子31に誤書き込みがされる可能性がある。そこで、図7に示すように、スイッチ32f、32gと、突入抵抗34を挿入することによって、誤書き込みの防止を行うこともできる。スイッチ32f、32gは、Normal信号によってON/OFFするスイッチであって、通常動作時(Normal信号が「H」の時)にはOFFとなり、抵抗変化素子31への書き込み時(Normal信号が「L」の時)にはONとなる。これによって、通常動作時にチャージポンプ20から抵抗変化素子31へ流れる電流量が抑制され、抵抗変化素子31の誤書き込みを防ぐことができる。

【0031】

シーケンサ60は、抵抗変化素子31への抵抗値書き込みを行う状態か、通常動作状態かに応じて、図1のマルチプレクサ70とスイッチ80の制御も行う。マルチプレクサ70は、位相検出器10とチャージポンプ20との間に設けられる。抵抗変化素子31の抵抗値を変更するとき、マルチプレクサ70によって位相検出器10とチャージポンプ20の間の接続を断ち、PLLのフィードバックループを遮断する。マルチプレクサ70は、Normal信号によって出力信号を切り替えるスイッチであって、通常動作時(Normal信号が「H」の時)には位相検出器10からの信号を出力し、抵抗変化素子31への書き込み時(Normal信号が「L」の時)にはシーケンサ60からの信号を出力する。シーケンサ60は、抵抗変化素子31の抵抗値を変更するときに、マルチプレクサ70に書き込み用のパルス信号を入力し、位相検出器10に替ってチャージポンプ20を制御する。

【0032】

スイッチ80は、周波数分周器50の前段と、位相検出器10の前段に設けられる。シーケンサ60は、抵抗変化素子31の抵抗値を変更するときに、スイッチ80に制御信号を入力し、スイッチ80をOFFにする。このスイッチ80のOFFによっても、PLLのフィードバックループを遮断することができる。なお、スイッチ80は、CMOSスイッチであっても良いし、抵抗が無限大になる抵抗変化型素子でも良い。

【0033】

このように、抵抗変化素子31の抵抗値を変更するときに、PLLのフィードバックループを遮断することによって、VCO40と位相検出器10の出力による雑音の影響を受けることを避ける。

【0034】

なお、マルチプレクサ70だけでもPLLのフィードバックループを遮断することができるが、スイッチ80によってもPLLのフィードバックループを遮断した方が、抵抗変化素子31の抵抗値を変更時のPLLの電力を削減することができる。これは、デジタル動作する位相検出器10と周波数分周器50の動作を停止させるからである。

【0035】

図8にループフィルタ30の抵抗値を変更するときのPLLの処理フローチャートを示す。外部の制御回路から、PLLの参照周波数を変えることや、PLLを起動することを示す信号を受け取ると、シーケンサ60がマルチプレクサ70、スイッチ80へ制御信号を入力し、フィードバックループを遮断する(S10)。そして、シーケンサ60が、ループフィルタ30内に設けられたスイッチ32a〜32e(または、32a〜32g)のON/OFFを制御する(S11)。そして、チャージポンプ20経由でループフィルタ30に電流を流すことによって抵抗変化素子31の抵抗値を変更する(S12)。その後、シーケンサ60がマルチプレクサ70、スイッチ80へ制御信号を入力して、フィードバックループを元に戻す。

【0036】

ここで、ループフィルタ30の減衰定数ζの適切な決定方法について述べる。数式4に示したζωnを最大化するために、ループフィルタ30の応答を高速にすればよい。図9に、減衰定数ζと、VCO40の周波数変動の関係を模式的に表す。図9に示すとおり、減衰定数ζが小さいとPLLのフィードバックループは不足制動となり、チャージポンプ20のパルス動作に対して、VCO40の周波数変動は小さくなり、PLLが安定して動作する。それに対して、減衰定数ζが大きいとチャージポンプ20のパルス動作に対するVCO40の周波数変動は大きくなり、PLLのフィードバックループの制動作用が強くなり、減衰振動の収束性が高くなり、その結果PLLが速くロックアップする。そこで、アンロック時やPLLの電源投入時には、数式5を満たすように減衰定数ζを設定して、ロックアップまでの振動を回避することが望ましい。少なくとも、減衰定数ζを1程度に設定すると、セットリング時間を短くすることが可能となる。

【数5】

ロックアップに近づくにつれ、ループフィルタ30の減衰定数ζを低くするように抵抗変化素子31の抵抗値を高くすることによって、位相検出器10へ出力する信号から位相雑音とスプリアスを抑圧することができ、PLLがより安定的に動作する。

【0037】

このように、PLLがアンロックした時や電源を投入されたときには抵抗変化素子31の抵抗値を低く設定し、PLLがロックアップすると抵抗変化素子31の抵抗値を高く設定することによって、安定性と即応性を備えたPLLを提供することができる。また、本実施形態によるPLLでは、抵抗変化素子を用いているため、1つの素子で抵抗値を低抵抗状態と高抵抗状態に変更することができる。

【0038】

(変形例1)

図3を用いた説明では、ループフィルタ30内のスイッチ32a〜32dが、nMOSとpMOSを用いたスイッチであるとして説明したが、チャージポンプ20からのパスが充電と放電に明確に分かれているため、図10に示すように、充電のパスにはpMOSのスイッチを用いて、放電のパスにはnMOSのスイッチを用いても良い。こうすることで、スイッチの回路素子数を削減することが可能である。なお、充電のパスにnMOSのスイッチを用い、放電のパスにpMOSのスイッチを用いることもできるが、トランジスタのオン抵抗が大きくなり、ループフィルタの特性を予測することが難しい。そのため、充電のパスにpMOSのスイッチ、放電のパスにnMOSのスイッチを用いた方が望ましい。

【0039】

図10に示すループフィルタ130に対するシーケンサ60の入力信号は、図3を用いて説明したループフィルタ30に対する入力と同じである。アンロック時やPLLの電源がONされたとき、シーケンサ60は、Normal信号を「L」、Write”H”信号を「L」、Write”L”信号を「H」に設定する。すると、スイッチ132bと132cがONとなり、スイッチ132aと132dがOFFとなる。このため、図4を用いて説明した状態と同様に、抵抗変化素子31が低抵抗状態となる。

【0040】

PLLがロックアップすると、シーケンサ60は、Normal信号を「L」、Write”H”信号を「H」、Write”L”信号を「L」に設定する。すると、スイッチ132aと132dがONとなり、スイッチ132bと132cがOFFとなる。このため、図5を用いて説明した状態と同様に、抵抗変化素子31が高抵抗状態となる。

【0041】

通常状態において、シーケンサ60は、Normal信号を「H」、Write”H”信号を「L」、Write”L”信号を「L」に設定する。すると、スイッチ132a、132b、32eはONとなり、スイッチ132c、132dがOFFとなる。すると、図6を用いて説明した状態と同様の状態となる。

【0042】

(変形例2)

抵抗変化素子として3端子の素子を用いることもできる。3端子の抵抗変化素子は、抵抗値を書き込むための端子を有し、この端子に入力される値に応じて抵抗変化素子に書き込まれる抵抗値が決まる。

【0043】

図11は、3端子の抵抗変化素子を用いたループフィルタを示す図である。3端子の抵抗変化素子231には、シーケンサ60から制御信号が入力され、制御信号に応じて抵抗変化素子231の抵抗値が変化する。シーケンサ60は、抵抗変化素子231の抵抗値を変更するときには、スイッチ32eをOFFにし、通常状態では、スイッチ32eをONにするよう制御する。

【0044】

このように3端子の抵抗変化素子を用いると、図3のループフィルタ30では必要であったスイッチ32a〜32dを設ける必要が無い。

【0045】

(変形例3)

PLLの電源OFF時に、VCO40の電位VVCOの放電を防止するため、図12のようにループフィルタを構成しても良い。図12に示すループフィルタ330では、図3に示すループフィルタ30に、スイッチ32hを追加した構成である。シーケンサ60は、PLLの電源OFF時にスイッチ32eとスイッチ32hとをOFFするように制御する。これによって、PLLの電源がOFFされたときに、キャパシタ33に蓄えられた電荷を保持しておくことができる。そのため、再度電源がONされたときに、ある程度キャパシタ33に電荷が蓄えられた状態であるため、早くロックアップすることができる。ただし、PLLの電源OFF時に、スイッチ32eとスイッチ32hとをOFFするためにシーケンサ60に電圧を引加しておく必要がある。スイッチ32eとスイッチ32hに抵抗が無限大になる抵抗変化型素子を用いればPLLの電源OFF時に、シーケンサ60の電源もOFFにすることができる。

【0046】

以上、本実施形態およびその変形例を説明したが、以上の変形例の他にも、本発明の要旨を逸脱しない範囲において、本実施形態を適宜変更することができる。例えば、変形例1〜3に対しても、誤書き込みを防止するために、図7で説明したようにスイッチと突入抵抗を設けても良い。変形例1〜3やその他の変形のうちのいくつかを組み合わせても良い。

【0047】

(第2の実施形態)

本実施形態は、ループフィルタ内に抵抗変化素子を複数設けた場合の実施形態である。図13は、本実施形態に係るPLLのループフィルタ530とシーケンサ560とを示す図である。本実施形態に係るPLLの他の構成要素は第1の実施形態と同様であるため、説明を省略する。なお、図13では、図3と同様に、スイッチ32a〜32mのnMOSに印加される信号を図示しており、pMOSに印加される信号は省略している。pMOSには、nMOSに入力される信号の反転値が印加される。

【0048】

図13では、一例として、2つの抵抗変化素子が並列に並べられたループフィルタ530を示す。ループフィルタ530では、第1の抵抗変化素子31aの両端にスイッチ32i、32jを設け、第2の抵抗変化素子31bの両端にスイッチ32k、32mを設ける。スイッチ32i、32j、32k、32mは、シーケンサ560から入力される制御信号によってON/OFFする。スイッチ32i、32jには、シーケンサ560からR1_en信号が入力される。R1_en信号が「H」であれば、スイッチ32i、32jがONとなる。スイッチ32k、32mには、シーケンサ560からR2_en信号が入力される。R2_en信号が「H」であれば、スイッチ32k、32mがONとなる。

【0049】

これらのスイッチによって、第1の抵抗変化素子31aに電流を流すのか否かと、第2の抵抗変化素子31bに電流を流すのか否かを選択することができる。なお、以降では、抵抗変化素子の両端に付けられたスイッチ32iと32j、もしくは、32kと32mをOFFにした状態を、抵抗変化素子がOFFの状態であると称する。それに対して、抵抗変化素子の両端に付けられたスイッチ32iと32j、もしくは、32kと32mをONにした状態を抵抗変化素子がONの状態であると称する。

【0050】

図14は、第1の抵抗変化素子31aの状態と第2の抵抗変化素子31bの状態の組み合わせを示す図である。第1の抵抗変化素子31aと第2の抵抗変化素子31bは、それぞれ、高抵抗状態、低抵抗状態、OFFの状態となることができる。なお、第1の抵抗変化素子31aと第2の抵抗変化素子31bの両方がONの状態であれば、ループフィルタ530の抵抗値は、第1の抵抗変化素子31aと第2の抵抗変化素子31bの合成抵抗の値となる。

【0051】

第1の抵抗変化素子31aと第2の抵抗変化素子31bそれぞれの高抵抗状態、低抵抗状態が全て異なる抵抗値であるならば、チャージポンプ20とループフィルタ530の間を流れる電流にかかる抵抗値は、8つの状態(図14の状態1〜状態8)それぞれに異なる値となる。

【0052】

これを利用して、PLLがアンロックとなった時や電源ONされた時にはループフィルタ530の抵抗値を低く設定し、PLLが安定状態に近づくにつれて、段階的に高くなるよう設定することができる。

【0053】

例えば、PLLに入力される参照周波数からクロックをカウントして、PLLがアンロックとなった時や電源ONされた時からの経過時間を測り、図15に示すように、所定の時間Δtが経過する毎に段階分けする。そして、第1段階では図14の状態8、第2段階では状態6、第3段階では状態4、第4段階では状態1というように、段階を経る毎にループフィルタ530の抵抗値が高くなるよう第1の抵抗変化素子31aと第2の抵抗変化素子31bの抵抗値および、それらの素子の両端に設けられたスイッチのON/OFF状態を切り替える。各段階でどの状態にするかは、シーケンサ560内に不揮発ルックアップテーブルを設けて、そのルックアップテーブルに予め設定しておくことができる。

【0054】

また、シーケンサ560に対して位相検出器10の出力を入力し、位相検出器10の出力する位相差の時間的変化に応じて、ループフィルタ530の抵抗値を段階的に変更しても良い。

【0055】

PLLのアンロックが検出された場合と、PLLが電源OFFの状態からの起動が要求された場合とで、ループフィルタ530の抵抗値の初期値を変えることもできる。例えば、PLLのアンロックが検出された場合の方が、PLLの起動が要求されたときよりも安定状態に近いと考えられる。そこで、PLLのアンロックが検出された場合には、ループフィルタ530の抵抗値の初期値を高くし(例えば図14の状態5)、PLLの起動が要求された場合には、ループフィルタ530の抵抗値の初期値を低くする(例えば図14の状態8)。これによって、PLLの起動が要求された場合には、より早くロックアップ状態にでき、PLLのアンロックが検出された場合には、より安定的に動作させることができる。

【0056】

図16にループフィルタ530の抵抗値を変更するときのPLLの処理フローチャートを示す。図16では、図8と同じ処理には同じ記号を付す。ループフィルタ530の抵抗値を変更する場合、スイッチ32i〜32mを用いて抵抗値を変更する抵抗変化素子の1つを選択し、第1の実施形態にて説明したように、スイッチ32a〜32eのON/OFFを制御する(S11)。そして、選択した抵抗変化素子への書き込み終了後、他の抵抗変化素子への書き込みも必要であれば(S20のNo)、その抵抗変化素子を選択して書き込みを行う。

【0057】

図17に、シーケンサ60のタイミングチャートを示す。なお、図17のCLK_refは、PLLに入力される参照周波数を表す。図17に示すように、通常状態では、Normal信号を「H」に設定し、抵抗変化素子に書き込む場合には、「L」に設定する。また、抵抗変化素子の書き込み先に応じて、R1_en信号またはR2_en信号のいずれか一方を「H」、他方を「L」にする。さらに抵抗変化素子に書き込む抵抗値に応じて、Write”H”信号またはWrite”L”信号のいずれか一方を「H」、他方を「L」にする。通常動作時のR1_en信号とR2_en信号は、シーケンサ60内に設けられたルックアップテーブルに基づいて、どちらか少なくとも一方を「H」にする。

【0058】

このように、第2の実施形態によれば、ループフィルタの抵抗値をきめ細かく変更することができる。また、本実施形態によれば、抵抗変化素子を用いるため、固定の抵抗値を有する抵抗を用いた場合と比較して、ループフィルタの抵抗値をより細かい段階で制御することが可能となる。

【0059】

(変形例1)

図13を用いた説明では、ループフィルタ30内のスイッチ32i、32j、32k、32mが、nMOSとpMOSを用いたスイッチであるとして説明したが、図18に示すように、これらをnMOSのスイッチ32n〜32qとして構成しても良い。こうすることで、スイッチの回路素子数を削減することが可能である。なお、nMOSのスイッチ32n〜32qの代わりに、pMOSのスイッチを用いても良い。

【0060】

本実施形態においても、他に様々な変更が可能である。第1の実施形態において説明した変形例を適用しても良い。また、本実施形態の説明では、2つの抵抗変化素子を用いた場合を例としたが、3つ以上の抵抗変化素子を用いても良い。ただし、抵抗変化素子を増やすと、その両端に設けるスイッチが増え、スイッチを構成するトランジスタの接合容量がループフィルタの利得に影響を与える可能性がある。そのため、並列に接続する抵抗変化素子の数は、4以下が好ましい。

【0061】

上記実施形態に限定されることはなく、本発明の要旨を逸脱しない範囲において、適宜変更しても良い。

【符号の説明】

【0062】

10…位相検出器、 20…チャージポンプ、 30…ループフィルタ、 40…VCO、 50…周波数分周器、 60…シーケンサ、 70…マルチプレクサ、 80…スイッチ、 31…抵抗変化素子、 32…スイッチ、 33…キャパシタ、 34…突入抵抗

【特許請求の範囲】

【請求項1】

参照信号とフィードバック信号の位相差を検出する位相検出器と、

前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、

前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、

前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、

前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、

前記ループフィルタを制御するシーケンサとを有するPLLであって、

前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御することを特徴とするPLL。

【請求項2】

前記ループフィルタは、

チャージポンプの充電側に接続される第1のスイッチおよび第2のスイッチと、

チャージポンプの放電側と前記第1のスイッチの間に接続される第3のスイッチと、

チャージポンプの放電側と前記第2のスイッチの間に接続される第4のスイッチとを更に有し、

前記第1の抵抗変化素子は一端が前記第1のスイッチと前記第3のスイッチに接続され、他端が前記第2のスイッチと前記第4のスイッチに接続され、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込むか否かと、書き込む抵抗値に応じて前記第1乃至第4のスイッチに制御信号を入力することを特徴とする請求項1に記載のPLL。

【請求項3】

前記シーケンサは、前記第1の抵抗変化素子の抵抗値を変化させない通常状態において、前記第1のスイッチと前記第3のスイッチをONにし、前記第2のスイッチと前記第4のスイッチをOFFにするよう制御信号を入力することを特徴とする請求項2に記載のPLL。

【請求項4】

前記シーケンサは、前記第1の抵抗変化素子に第1の抵抗値を書き込む場合には、前記第1のスイッチと前記第4のスイッチをONにし、前記第1の抵抗変化素子に第2の抵抗値を書き込む場合には、前記第2のスイッチと前記第3のスイッチをONにするよう制御信号を入力することを特徴とする請求項2または請求項3に記載のPLL。

【請求項5】

前記チャージポンプの充電側と前記第1のスイッチとの間に設けられる第5のスイッチと、

前記第5のスイッチに並列に設けられる第1の突入抵抗と、

前記チャージポンプの放電側と前記第3のスイッチとの間に設けられる第6のスイッチと、

前記第6のスイッチに並列に設けられる第2の突入抵抗とを更に有し、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込むか否かに応じて前記第5のスイッチおよび前記第6のスイッチにON/OFFを制御する制御信号を入力することを特徴とする請求項2乃至4のいずれか1項に記載のPLL。

【請求項6】

前記第1の抵抗変化素子、前記第2のスイッチおよび第3のスイッチに接続される第7のスイッチと、

前記第7のスイッチに接続される第8のスイッチと、

前記第7のスイッチおよび前記第8のスイッチに接続されるキャパシタとを更に有し、

前記シーケンサは、前記PLLの電源をOFFにする信号を取得すると、前記第7のスイッチおよび前記第8のスイッチをOFFにすることを特徴とする請求項2乃至5のいずれか1項に記載のPLL。

【請求項7】

前記位相検出器と前記チャージポンプの間に設けられたマルチプレクサを更に有し、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込む場合、前記マルチプレクサを制御して、前記位相検出器と前記チャージポンプとの間の接続を断つことを特徴とする請求項1乃至6のいずれか1項に記載のPLL。

【請求項8】

前記第1の抵抗変化素子に並列に設けられた第2の抵抗変化素子と、

前記第1の抵抗変化素子の両端に設けられた第9のスイッチおよび第10のスイッチと、

前記第2の抵抗変化素子の両端に設けられた第11のスイッチおよび第12のスイッチを更に有し、

前記シーケンサは、前記PLLが電源ONされてから所定の時間が経過するごとに、前記第9のスイッチおよび前記第10のスイッチのON/OFFと、前記第11のスイッチおよび前記第12のスイッチのON/OFFと、前記第1の抵抗変化素子の抵抗値と前記第2の抵抗変化素子の抵抗値の少なくともいずれか1つを制御する制御信号を出力することを特徴とする請求項2乃至7のいずれか1項に記載のPLL。

【請求項9】

前記第1のスイッチと前記第2のスイッチは、第1の導電型を有する電界効果トランジスタであり、前記第3のスイッチと前記第4のスイッチは、前記第1の導電型とは異なる第2の導電型を有する電界効果トランジスタであることを特徴とする請求項2乃至8のいずれか1項に記載のPLL。

【請求項10】

前記VCOと前記周波数分周器との間に設けられる第12のスイッチと、

前記周波数分周器と前記位相検出器との間に設けられる第13のスイッチを更に有し、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込む場合、前記第12のスイッチと前記第13のスイッチをOFFにするよう制御信号を入力することを特徴とする請求項2乃至9のいずれか1項に記載のPLL。

【請求項1】

参照信号とフィードバック信号の位相差を検出する位相検出器と、

前記位相検出器の検出結果に基づいて電流を発生するチャージポンプと、

前記チャージポンプに接続され、第1の抵抗変化素子を有するループフィルタと、

前記ループフィルタから入力される信号に応じて出力周波数を制御するVCOと、

前記VCOの出力信号を分周して、前記位相検出器に入力するフィードバック信号を生成する周波数分周器と、

前記ループフィルタを制御するシーケンサとを有するPLLであって、

前記シーケンサは、前記PLLの電源がOFFされることを示す信号が入力された時または前記PLLの電源がONされることを示す信号が入力された時に前記第1の抵抗変化素子の抵抗値が第1の抵抗値となるよう制御し、前記PLLが安定化後には、前記第1の抵抗値よりも高い第2の抵抗値となるよう制御することを特徴とするPLL。

【請求項2】

前記ループフィルタは、

チャージポンプの充電側に接続される第1のスイッチおよび第2のスイッチと、

チャージポンプの放電側と前記第1のスイッチの間に接続される第3のスイッチと、

チャージポンプの放電側と前記第2のスイッチの間に接続される第4のスイッチとを更に有し、

前記第1の抵抗変化素子は一端が前記第1のスイッチと前記第3のスイッチに接続され、他端が前記第2のスイッチと前記第4のスイッチに接続され、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込むか否かと、書き込む抵抗値に応じて前記第1乃至第4のスイッチに制御信号を入力することを特徴とする請求項1に記載のPLL。

【請求項3】

前記シーケンサは、前記第1の抵抗変化素子の抵抗値を変化させない通常状態において、前記第1のスイッチと前記第3のスイッチをONにし、前記第2のスイッチと前記第4のスイッチをOFFにするよう制御信号を入力することを特徴とする請求項2に記載のPLL。

【請求項4】

前記シーケンサは、前記第1の抵抗変化素子に第1の抵抗値を書き込む場合には、前記第1のスイッチと前記第4のスイッチをONにし、前記第1の抵抗変化素子に第2の抵抗値を書き込む場合には、前記第2のスイッチと前記第3のスイッチをONにするよう制御信号を入力することを特徴とする請求項2または請求項3に記載のPLL。

【請求項5】

前記チャージポンプの充電側と前記第1のスイッチとの間に設けられる第5のスイッチと、

前記第5のスイッチに並列に設けられる第1の突入抵抗と、

前記チャージポンプの放電側と前記第3のスイッチとの間に設けられる第6のスイッチと、

前記第6のスイッチに並列に設けられる第2の突入抵抗とを更に有し、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込むか否かに応じて前記第5のスイッチおよび前記第6のスイッチにON/OFFを制御する制御信号を入力することを特徴とする請求項2乃至4のいずれか1項に記載のPLL。

【請求項6】

前記第1の抵抗変化素子、前記第2のスイッチおよび第3のスイッチに接続される第7のスイッチと、

前記第7のスイッチに接続される第8のスイッチと、

前記第7のスイッチおよび前記第8のスイッチに接続されるキャパシタとを更に有し、

前記シーケンサは、前記PLLの電源をOFFにする信号を取得すると、前記第7のスイッチおよび前記第8のスイッチをOFFにすることを特徴とする請求項2乃至5のいずれか1項に記載のPLL。

【請求項7】

前記位相検出器と前記チャージポンプの間に設けられたマルチプレクサを更に有し、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込む場合、前記マルチプレクサを制御して、前記位相検出器と前記チャージポンプとの間の接続を断つことを特徴とする請求項1乃至6のいずれか1項に記載のPLL。

【請求項8】

前記第1の抵抗変化素子に並列に設けられた第2の抵抗変化素子と、

前記第1の抵抗変化素子の両端に設けられた第9のスイッチおよび第10のスイッチと、

前記第2の抵抗変化素子の両端に設けられた第11のスイッチおよび第12のスイッチを更に有し、

前記シーケンサは、前記PLLが電源ONされてから所定の時間が経過するごとに、前記第9のスイッチおよび前記第10のスイッチのON/OFFと、前記第11のスイッチおよび前記第12のスイッチのON/OFFと、前記第1の抵抗変化素子の抵抗値と前記第2の抵抗変化素子の抵抗値の少なくともいずれか1つを制御する制御信号を出力することを特徴とする請求項2乃至7のいずれか1項に記載のPLL。

【請求項9】

前記第1のスイッチと前記第2のスイッチは、第1の導電型を有する電界効果トランジスタであり、前記第3のスイッチと前記第4のスイッチは、前記第1の導電型とは異なる第2の導電型を有する電界効果トランジスタであることを特徴とする請求項2乃至8のいずれか1項に記載のPLL。

【請求項10】

前記VCOと前記周波数分周器との間に設けられる第12のスイッチと、

前記周波数分周器と前記位相検出器との間に設けられる第13のスイッチを更に有し、

前記シーケンサは、前記第1の抵抗変化素子に対して抵抗値を書き込む場合、前記第12のスイッチと前記第13のスイッチをOFFにするよう制御信号を入力することを特徴とする請求項2乃至9のいずれか1項に記載のPLL。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【公開番号】特開2013−31012(P2013−31012A)

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願番号】特願2011−166073(P2011−166073)

【出願日】平成23年7月28日(2011.7.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

【公開日】平成25年2月7日(2013.2.7)

【国際特許分類】

【出願日】平成23年7月28日(2011.7.28)

【出願人】(000003078)株式会社東芝 (54,554)

【Fターム(参考)】

[ Back to top ]