PWM信号生成装置

【課題】PWM信号生成装置において、回路規模を小さくして効果的に放射雑音等のノイズを低減する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

【解決手段】CPU204、カウンタ201、レジスタ202、及びコンパレータ205は基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成する。TFF206は基準クロックに応じて変動クロックを第1のPWM信号として出力する。TFF251は基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する。セレクタ252は第1及び第2のPWM信号を選択的にPWM信号として出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、PWM信号生成装置に関し、特に、ノイズレベルを低減することのできるPWM信号生成装置に関する。

【背景技術】

【0002】

一般に、ASIC(Application Specific Integrated Circuit)等の集積回路では、その内部クロックにおけるノイズを低減する必要がある。従来、ノイズの低減のため、SSCG(spread spectrum clock generator(周波数変調機能付きクロック発生回路)が用いられている。このSSCGでは、クロック信号の周波数を僅かに変動させて、クロック信号の周波数スペクトラムのピーク値を下げている。これによって、放射雑音等のノイズを低減させている。

【0003】

例えば、SSCGを用いた送信装置において、通信放射雑音を低減させるため、PLL回路において、基本クロック信号から高速クロック信号を生成し、PWM信号生成回路によって高速クロック信号を最小単位として通信クロック信号及び受信タイミング信号の各々を独立した任意の時間長のPWM信号として生成するようにしたものがある(特許文献1参照)。

【0004】

ここでは、通信クロック信号においてそのオフタイム幅をパルス毎に変更して、任意の時間長において同一のパルス幅の通信クロック信号と同一のパルス数を有する通信クロック信号(つまり、PWM信号)を生成するようにしている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−224552号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、特許文献1に記載の手法では、PLL回路を複数の送信装置に適用しようとすると、不可避的に回路規模が増大するばかりでなく、効果的に放射雑音を低減することが困難となる。さらに、生成されるPWM信号の周期が、PLL回路で生成する基本クロック信号の整数倍となって、ノイズを分散させることが困難となる。加えて、ノイズの強度が高いスペクトラムに対してはピーク値を下げることが難しい。いずれにしても、特許文献1に記載の手法では、回路規模を小さくして、効果的に放射雑音等のノイズを低減することが難しいという課題がある。

【0007】

従って、本発明の目的は、回路規模を小さくして効果的に放射雑音等のノイズを低減することのできるPWM信号生成装置を提供することにある。

【課題を解決するための手段】

【0008】

上記の目的を達成するため、本発明によるPWM信号生成装置は、基準クロックに応じて動作してPWM信号を生成するPWM信号生成装置において、前記基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成するクロック生成手段と、前記基準クロックに応じて前記変動クロックを第1のPWM信号として出力する第1のPWM出力制御手段と、前記基準クロックを所定の時間遅延させた遅延クロックに応じて前記変動クロックを第2のPWM信号として出力する第2のPWM出力制御手段と、前記第1及び前記第2のPWM信号を選択的に前記PWM信号として出力する選択手段とを有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、PWM信号の周波数を僅かに変動させて出力する際、回路規模を小さくして効果的に放射雑音等のノイズを低減することができるという効果がある。

【図面の簡単な説明】

【0010】

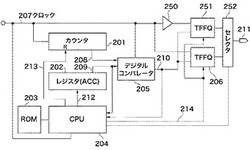

【図1】一般的なPWM信号生成装置の一例を示すブロック図である。

【図2】図1に示すPWM信号生成装置の動作を説明するためのフローチャートである。

【図3】本発明の実施の形態によるPWM信号生成装置の一例についてその概念を説明するためのブロック図である。

【図4】図3で説明した動作原理を用いたハードウェア構成の一例を示す図である。

【図5】図4に示すタイミング回路の一例を説明するための図であり、(a)はその構成の一例を示すブロック図、(b)は(a)に示すフルアダーの真理値表を示す図である。

【図6】図4に示すPWM信号生成装置の動作を説明するためのタイムチャートの一例を示す図である。

【図7】図4に示すPWM信号生成装置の動作を説明するためのタイムチャートの他の例を示す図である。

【図8】図4に示すPWM信号生成装置の動作を説明するためのタイムチャートのさらに他の例を示す図である。

【図9】図4に示す下位ビット制御回路の構成を示すブロック図である。

【図10】図9に示す出力モード設定レジスタのレジスタ値に応じた信号出力を説明するための図である。

【図11】図9に示す出力モード設定レジスタのレジスタ値が”01”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【図12】図9に示す出力モード設定レジスタのレジスタ値が”02”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【図13】図9に示す出力モード設定レジスタのレジスタ値が”03”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【図14】図4に示すクロック選択制御回路の動作の一例を説明するための図であり、(a)は図4に示すクロック選択回路の構成の一例を示すブロック図、(b)は図4に示すセレクタによる選択動作の一例を示す図である。

【図15】図4に示す1ショット回路の一例を示すブロック図である。

【図16】図4に示すクロック選択制御回路の動作の他の例を説明するための図であり、(a)は図4に示すクロック選択制御回路の構成の他の例を示すブロック図、(b)は図4に示すセレクタ13による選択動作の他の例を示す図である。

【図17】図4に示すPWM信号生成装置を用いた通信装置の一例を示すブロック図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態によるPWM信号生成装置について図面を参照して説明する。

【0012】

まず、本発明の実施の形態によるPWM信号生成装置の理解を容易にするため、一般的なPWM信号生成装置の一例について説明することにする。

【0013】

図1は、一般的なPWM(パルス幅変調)信号生成装置の一例を示すブロック図である。

【0014】

図1を参照すると、図示のPWM信号生成装置は、自走のnビット(一般的には,nはニブル(nibble)の整数倍)で構成されたバイナリーカウンタ201を有している。レジスタ202はバイナリーカウンタ201と同一のビット長(レジスタ長)で構成されている。デジタルコンパレータ205はバイナリーカウンタ201及びレジスタ202の各々のLSB(Least Significant Bit)〜MSB(Most Significant Bit)をビット毎に比較して、全ビットの値が一致した際にその出力を“1”とする。

【0015】

デジタルコンパレータ205の出力は、信号線210に出力され、T−フリップフロップ(以下TFFという)206のT入力端子に入力されるとともに、CPU204の割り込み入力端子に入力される。ROM203にはデータ及び実行プログラムが記録され、CPU204はROM203をアクセスしてデータ及び実行プログラムを読み込む。さらに、CPU204にはレジスタ202の出力が信号線209を介して入力され、CPU204の演算出力端子は信号線212を介してレジスタ202の信号入力端子に接続されている。

【0016】

システムクロックが信号線207を介してカウンタ201とCPU204のクロック信号入力端子とに与えられ、さらに、システムクロックは、同期をとるため、デジタルコンパレータ205に与えられる。そして、カウンタ201の制御信号入力端子Rには、CPU204の制御信号出力端子が信号線213を介して接続されている。

【0017】

図2は、図1に示すPWM信号生成装置の動作を説明するためのフローチャートである。

【0018】

図1及び図2を参照して、いまシステムリセットが行われ(ステップS21)、CPU204は動作可能な状態となると、CPU204はROM203からPWMの制御情報、例えば,信号波形のロウ(L)レベル期間のデータ(以下、Lレベルデータと呼ぶ)を読み出す(ステップS22)。そして、CPU204は当該データをレジスタ202にセットする(ステップS23)。CPU204は信号線213を介してカウンタ201にカウント開始信号を送出する(ステップS24)。これによって、カウンタ201はカウントを開始する。

【0019】

カウンタ201が、例えば、バイナリアップカウンタであるとすると、カウンタ201は信号線207を介して入力されるシステムクロックに同期してカウントアップする。そして、デジタルコンパレータ205はカウンタ201のカウント値とレジスタ202にセットされたLレベルデータとを比較して(ステップS25)、カウント値とLレベルデータとが一致するか否かを判定する(ステップS26)。カウント値とLレベルデータとが一致すると(ステップS26において、YES)、デジタルコンパレータ205は、信号線210上に“1”を示す信号を出力する。

【0020】

CPU204は、信号線214を介して予めクリア信号をTFF206に送って、TFF206をリセットする。このため、デジタルコンパレータ205の出力が”1”となると、TFF206の出力信号が反転し(ステップS27)、出力端子211に現われる出力信号が“L”から“H”に変化する。

【0021】

一方、デジタルコンパレータ205の出力はCPU204に対する割り込み信号となる。CPU204が割り込み信号を検出すると(ステップS28)、CPU204はROM203から、信号波形を新たに生成するハイ(H)レベルの期間のデータ(以下、Hレベルデータという)を読み出す(ステップS29)。そして、CPU204はHレベルデータとレジスタ203にセットされたデータ(レジスタデータ)との和を求めて、和データとしてレジスタ202に再セットする。(ステップS30)。この際、CPU204は和のキャリーは切り捨てる。

【0022】

その後、図示のステップS31〜S34において同様の動作を繰り返す。そして、CPU204は、ステップS35においてROMから次のLレベルデータを読み出し、このLレベルとレジスタデータとを加算してレジスタ202にセットする(ステップS36)。その後、処理はステップS25に戻って、以後同様にして処理が繰り返される。この結果、出力端子211から所望のPWM信号が出力される。

【0023】

ここで、図1に示すPWM信号生成装置を適用したPWM信号生成装置の一例について説明する。

【0024】

図3は、本発明の実施の形態によるPWM信号生成装置の一例についてその概念を説明するためのブロック図である。

【0025】

図3を参照して、図示のPWM信号生成装置は、図1に示す構成に加えてバッファ250、TFF(Tタイプフリップフロップ)251、及びセレクタ(選択手段)252を有している。そして、図3に示す例では、CPU(制御手段)204の処理が後述するように図1で説明したCPU204の処理と異なり、さらに、TFF206として同期型TFFが用いられる。

【0026】

図3に示すPWM信号生成装置では、バッファ250の入力端子がクロック信号線207に接続され、バッファ250の出力端子がTFF251のクロック入力端子に接続されている。TFF251のリセット端子は信号線214に接続されており、TFF251のQ出力端子は、2入力セレクタ252の一方の入力端子に接続されている。また、2入力セレクタ252の他方の入力端子には、TFF206のQ出力端子が接続されている。なお、基準クロックはカウンタ207(カウント手段)に与えられ、カウンタ207は基準クロックのパルス数をカウントする。そして、カウンタ207はカウント値をデジタルコンパレータ205(比較手段)に与える。

【0027】

さらに、2入力セレクタ252の出力端子は、信号出力端子211に接続されており、2入力セレクタ252の制御信号入力端子は、CPU204の制御信号出力端子に接続されている。TFF206のクロック入力端子は、クロック信号線207に接続されており、TFF251及び206のT入力端子は信号線210に接続されている。

【0028】

図3に示す例では、説明を簡単にするため、追加クロックを単一のバッファ250による遅延クロックとしている(つまり、バッファ250によって、基準クロックを所定の遅延時間遅延させて、遅延クロックとしている)。ROM203にはオン期間(ON期間)を示すオンタイム情報及びオフ期間(OFF期間)を示すオフタイム情報(パルス幅データ)が格納されている。そして、オンタイム情報及びオフタイム情報におけるLSBを、追加クロック(遅延クロック)に対応する情報(以下、LSB情報と呼ぶ)とする。

【0029】

LSB情報(予め規定されたビット)が”0”(第1の値)であると、2入力セレクタ252に対する入力がTFF206のQ出力端子に接続され、かつTFF206の出力信号がクロック信号線207上のクロック信号の立ち上がりに同期して出力される。

【0030】

一方、図2で説明したように、LSB情報とレジスタ202(レジスタ手段)にセットされたレジスタデータ(レジスタ値)とを加算した結果が”1”(第2の値)であると、LSBのビット時間分だけ出力タイミングをずらす必要が生じる。このため、CPU204は、TFF251の出力信号が出力端子211に出力されるように、2入力セレクタ252に制御信号を送出する。この結果、出力端子211に現われる出力信号はバッファ250の遅延時間分(例えば、δ時間分)だけ遅れて出力されることになる。その後、LSB情報を立てないと、このクロックのタイミングで動作が持続される。

【0031】

このように、セレクタ252は選択的にTFF206及びTFF251に接続されることになる。

【0032】

一方、ビット情報を1減らす情報をLSB情報に加えれば,次のPWM信号生成タイミングにおいて、それ以前のLSB情報と加算された結果を”0”にして、TFF206の出力が2入力セレクタ252によって選択されて、結果的に出力端子211から出力される出力信号(クロック信号)の周波数が変動することになる。

【0033】

図3に示す例においては、CPU204、レジスタ202、カウンタ201、及びデジタルコンパレータ205が基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成するクロック生成手段として機能している。また、TFF206が基準クロックに応じて変動クロックを第1のPWM信号として出力する第1のPWM出力制御手段として機能し、TFF251が基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する第2のPWM出力制御手段として機能する。

【0034】

続いて、図3で説明した動作原理を用いたPWM信号生成装置の一例について説明する。

【0035】

図4は、図3で説明した動作原理を用いたPWM信号生成装置のハードウェア構成の一例を示す図である。

【0036】

図4に示すPWM信号生成装置では、フリーランカウンタ1、このフリーランカウンタ1と同一のビット幅を有するレジスタ2、及びアダー(加算器)14を有している。最も簡単な例では、2進フリーランカウンタ、2進のアダーが用いられる。図示の例では、フリーランカウンタ1のカウント値とレジスタ2のレジスタ値とをクロックのカウント毎に比較する。そして、一致したタイミングでレジスタ値にON幅データ又はOFF幅データを交互にアダー14によって加算する。この加算値がレジスタ2に再設定される。さらに、一致信号が出力される毎に出力レジスタの値をトグルして、PWM信号を生成する。なお、ビット数は、任意のNビット(Nは2以上の整数)で実現することができる。

【0037】

ここでは、一致信号が出力される毎、つまり、クロックの立ち上がりにおいてトグルするレジスタとして、TFF11、12、31、32、33、34を備えている。そして、TFF11、12、31、32、33、及び34にそれぞれバッファ26〜30によってCLK_IN端子から与えられるクロック信号を所定の遅延時間ずらして加える。

【0038】

TFF11、12、及び31〜34のQ出力端子は、それぞれセレクタ13の入力端子に接続されており、セレクタ13において、TFF11、12、及び31〜34のいずれかの出力信号をPWMOUT出力端子21にPWM信号として出力する。そして、セレクタ13によって逐次PWM信号を切り替えて、周波数、オンタイム、及びオフタイムの微調整を行う。

【0039】

いま、N=8とすると、フリーランバイナリカウンタ1は8ビットカウンタとなり、レジスタ2は8ビット長8のレジスタとなる。そして、コンパレータ3はビット毎にカウンタ1のカウント値とレジスタ2のレジスタ値とを比較する。そして、全ビットの値が一致すると、コンパレータ3は”1”を示す出力信号(比較結果信号)を出力する。コンパレータ3の出力信号はDFF4のD入力端子に与えられる。さらに、コンパレータ3の出力信号はTFF11、12、及び31〜34のT入力端子に与えられる。

【0040】

これらTFF11、12、及び31〜34の各々は、T入力端子に”1”が現われると、そのクロック端子に与えられるクロック信号がLレベルからHレベルに立ち上がる際、出力信号が反転するように動作する。

【0041】

TFF11のクロック入力端子には、CLK_IN端子20から与えられるクロック信号が入力される。CLK_IN端子20はバッファ26の入力端子に接続されている。そして、バッファ26〜30が順次接続され、バッファ26〜30の出力端子はそれぞれTFF12及び31〜34のクロック入力端子に接続されている。

【0042】

さらに、CLK_IN入力端子20は、カウンタ1及びDFF4のクロック入力端子に接続されている。TFF11、12、及び31〜34のQ出力端子は、それぞれセレクタ13の入力端子に接続され、セレクタ13の出力端子はPWMOUT出力端子21に接続されている。そして、TFF11、12、及び31〜34のQ出力信号はセレクタ13の選択制御端子に印加される選択信号に応じていずか1つが選択されてPWMOUT出力端子21に出力される。

【0043】

なお、セレクタ13の選択制御端子は、クロック選択制御回路24の出力端子に接続されている。また、TFF11のQ出力端子はDFF10のD入力端子に接続されている。

【0044】

図示のPWM信号生成装置は、タイミング回路17及び18を有している。図5は図4に示すタイミング回路17及び18の一例を説明するための図である。そして、図5(a)はその構成の一例を示すブロック図であり、図5(b)は図5(a)に示すフルアダー7−1及び7−2の真理値表を示す図である。

【0045】

図5(a)において、タイミング回路17はPWM出力信号のタイミングを微小変調するための制御信号情報が入力される度に加算する。タイミング回路18は、この加算結果に応じてPWMOUTに出力されるべき出力信号を選択するための制御信号を生成する。さらに、タイミング回路17は、後述する補正情報を生成する。

【0046】

図4、図5(a)、及び図5(b)を参照して、タイミング回路18の制御信号出力端子、つまり、DFF2−8、7−7のQ出力端子は、それぞれOUTSEL1及びOUTSEL2端子2−10及び7−9を介して、クロック選択制御回路24(図4)に接続されている。DFF2−8及び7−7のクロック入力端子は、CP入力端子2−9を介してDFF4(図4)のQ出力端子に接続されている。

【0047】

また、DFF2−8のD入力端子は、フルアダー7−1のS出力端子に接続されている。そして、DFF7−7のD入力端子は、フルアダー7−2のS出力端子に接続されている。フルアダー7−1及び7−2は、2つのデータ入力端子A及びBとキャリー入力端子Ci、キャリー出力端子C、及び加算結果出力端子Sを有している。フルアダー7−1及び7−2の各々は、図5(b)の真理値表に示すように非同期に動作する。

【0048】

フルアダー7−1のCi入力端子は、接地(GND)されており、この結果、フルアダー7−1のCi入力端子には常にゼロが入力される。フルアダー7−1のA入力端子は入力端子2−5に接続され、そのS出力端子はDFF2−2のD入力端子に接続されている。そして、DFF2−2のQ出力端子がフルアダー7−1のB入力端子に接続されている。

【0049】

フルアダー7−1のC出力端子はフルアダー7−2のCi入力端子に接続されている。フルアダー7−2のA入力端子は入力端子7−8に接続され、そのS出力端子はDFF7−10のD入力端子に接続されている。そして、DFF7−10のQ出力端子がフルアダー7−2のB入力端子に接続されている。なお、フルアダー7−2のC出力端子はオープンとなっている。

【0050】

クロック入力端子2−18は、DFF2−2及び7−10のクロック入力端子に接続されている。DFF2−2のQバー出力端子は、2入力ANDゲート2−11の一方の入力端子に接続されている。DFF2−2のD入力端子は、2入力ORゲート7−3の一方の入力端子に接続されている。DFF7−10のD入力端子は、2入力ORゲート7−3の他方の入力端子に接続されている。2入力ORゲート7−3の出力端子は2入力ANDゲート7−4の一方の入力端子とインバータ2−14の入力端子とに接続されている。

【0051】

2入力ANDゲート7−4の出力端子は出力端子2−7に接続されている。また、ORゲート2−12の一方の入力端子がDFF7−10のQ出力端子に接続され、ORゲート2−12の他方の入力端子がDFF2−2のQ出力端子に接続されている。ORゲート2−12の出力端子はANDゲート2−13の一方の入力端子に接続され、ANDゲート2−13の他方の入力端子はインバータ2−14の出力端子に接続されている。ANDゲート2−13の出力端子は出力端子2−15に接続されている。また、ANDゲート7−4の他方の入力端子は、2−11の2入力ANDゲートの出力端子に接続され、2−11の他方の入力端子は、7−10のQバー出力端子に接続されている。

【0052】

出力端子2−7及び2−15は、それぞれ2入力ORゲート54(図4)の入力端子に接続され、出力端子2−15はさらにセレクタ15−3の制御信号入力端子に接続されている。2入力ORゲート54の出力端子は、セレクタ16の制御信号入力端子に接続されている。

【0053】

DFF4のQ出力端子はレジスタ2のクロック入力端子に接続されるとともに、DFF5のD入力端子に接続されている。DFF5のQ出力端子は、DFF10のクロック入力端子に接続されている。また、DFF5のQ出力端子はクロック入力端子2−18に接続されている。DFF5のクロック端子はclk_IN入力端子20に接続され、DFF5はこの信号の立下り毎にD入力の信号がQ出力端子に出力されるように、クロックの逆相でデータをラッチするように動作する。

【0054】

クロック微調制御回路23のオン幅制御情報出力端子3−14−1及びオフ幅制御情報制御信号出力端子3−14−2がそれぞれセレクタ8の入力端子に接続されている。そして、クロック微調制御回路23はセレクタ8の選択信号入力端子の情報によって各々2ビットからなる2つの制御信号のいずれかをセレクタ8の出力端子に接続する。セレクタ8の出力端子は、そのLSB側がタイミング回路17の入力端子2−5に接続され、MSB側が入力端子7−8に接続されている。

【0055】

基本波形データ入力用レジスタ6及び7はPWMを生成するためのレジスタであり、基本波形データ入力用レジスタ6及び7はセレクタ9の入力端子に接続されている。そして、基本波形データ入力用レジスタ6及び7はセレクタ9の選択信号入力端子によって、レジスタ6及び7のいずれか一方の信号を出力端子9に接続する。セレクタ8及び9の選択信号入力端子は、DFF10のQ出力端子に接続されている。アダー14は非同期に動作し、セレクタ9の出力端子に出力された信号とレジスタ2の出力端子に出力された信号とを加算して、アダー14の出力端子に出力する。

【0056】

アダー14の出力端子はセレクタ16の一方の入力端子群に接続されるとともに、アダー15の一方のバス入力端子に接続されている。アダー15の出力がセレクタ16の他方の入力端子群に接続されている。アダー15の他方のバス入力端子群には、セレクタ15−3の出力端子が接続され、セレクタ15−3の一方のセレクタ入力端子には、定数値”00000001B”15−2が加わり、その他方のセレクタ入力端子には定数値15−4の”11111111B”15−4が加わる。出力端子2−15が”1”のとき、定数値15−4で示す値がアダー15で加算される。2−15が“0”のとき、定数値15−2で示す値がアダー15で、アダー14での演算結果と加算される。すなわち、定数値15−2及び15−4のうち選択された定数値が、アダー14の出力値と非同期に加算演算されて、アダー15の出力端子に出力される。

【0057】

なお、上述の構成では、カウンタ又はレジスタがオーバーフローしてゼロにイニシャライズしても、持続的にPWMの信号を生成することができるカウンタ構成、レジスタ構成、及びアダー構成が必要である。原則的にバイナリーで演算する場合には、バイナリーカウンタを用いれば、最もシンプルな構成となるが、他の構成をもちいるようにしてもよい。

【0058】

セレクタ16の出力バスはレジスタ2の入力バスに接続されている。OR回路50、1ショット回路52、及び遅延バッファ53は、原クロックの2分周クロックまで生成できるタイミングを生成するために付加されている。OR回路50、1ショット回路52、及び遅延バッファ53による信号制御のため、DFF4及び5はRSTXがゼロの際に初期化される。すなわち、DFF4及び5のQ出力端子がゼロとなるように、OR回路50の一端とインバータ51とを介してRSTXからの信号が入力される。

【0059】

つまり、RSTXがインバータ51の入力端子に接続され、インバータ51の出力端子がOR回路50の一方の入力端子に接続され、OR回路50の他方の入力端子は1ショット回路52の出力端子に接続されている。1ショット回路52の入力端子は遅延バッファ53の出力端子に接続され、遅延バッファ53の入力端子はDFF5のQ出力端子に接続されている。また、OR回路50の出力端子はDFF4及び5のDFFのリセット端子に接続されている。

【0060】

図6〜図8は、図4に示すPWM信号生成装置の動作を説明するためのタイムチャートである。

【0061】

図6〜図8に示すタイムチャートでは、説明の便宜上N=8とした例が示されている。また、図4に示すPWM信号生成装置では、リセット回路が示されていないが、リセットの際カウンタ1及びレジスタ6及び7を除いて全てのDFFのQ出力端子の値は非同期にゼロに初期化されるものとする。また、レジスタ2もゼロに初期化され、TFF11及び12のQ出力端子もゼロに初期化される。但し、レジスタ6、7、15−2、及び15−4は、リセットの際においても変化しない固定値が予め与えられるレジスタとする。

【0062】

N=8であるため、カウンタ1及び、レジスタ2のビット長は8ビットであり、カウンタ1はリセットの際にそのQ出力が”FF”にリセットされるものとする。

【0063】

ここで、リセット解除後のPWM信号生成装置の動作について説明する。なお、予めレジスタ6には”2H”の値が、レジスタ7にも”2H”の値が設定されているものとする。

【0064】

図4及び図6〜図8を参照して、カウンタ1はCLK_IN20のクロックの立ち上がり毎に1カウントアップして、リセット解除後1クロックが立ち上がるとカウンタ1は”FF”から1カウントアップして”00”となる。その結果、カウンタ1の値(カウント値)はレジスタ2の値と同一の値となる(リセットでレジスタは”00”に初期化されている)。

【0065】

これによって、当該タイミングにおいてコンパレータ3の出力端子の値が”1”となり、その次のクロックの立下りで、TFF12のQ出力端子が”1”となる。さらに、その次のクロックの立上がりで、DFF4のQ出力端子に”1”がセットされるとともに、TFF11のQ出力端子も”1”にセットされる。

【0066】

従って、レジスタ2にオンタイムレジスタ7のLSB1ビットを除く全てのビット情報とレジスタ2のレジスタ値”0”との加算結果がラッチされる。ここでは、レジスタ2に”2H#の値が設定されることになる(つまり、オンタイムレジスタ7の値である”2H”が設定される)。

【0067】

リセットの際、レジスタ10のQ出力端子は”0”に初期化されており、当該条件では,ONレジスタ7のデータ及び下位ビット制御回路23の初期出力値が、セレクタ9及び8を介してアダー14とタイミング回路17及び18の入力データとして設定される。

【0068】

後述するように、下位ビット制御回路23の初期値は”0”であるから、図5(a)に示す入力端子2−5及び7−8には、値”0”が印加される。DFF2−2及び7−10は予めリセットされているので、そのQ出力端子は”0”である。このため、フルアダー7−1及び7−2のS出力端子には”0”が出力される。従って、DFF4のQ出力端子に”1”がセットされたタイミングで、フルアダー7−1のS出力端子の出力信号”0”がDFF2−8にラッチされ、フルアダー7−2のS出力端子の出力信号”0”がDFF7−7にラッチされる。

【0069】

セレクタ13は、下位ビット制御回路23及びクロック選択制御回路24の初期化よってTFF11の出力を出力端子21に出力するモードが設定されている。同時に当該タイミングにおいては、タイミング回路17の出力端子2−15及び2−7は”0”となり、セレクタ16はアダー14の出力端子がレジスタ2に接続されるモードとなっている。

【0070】

カウンタ1は1カウントアップされて、コンパレータ3の出力端子が”0”となる。次にCLK_IN20に入力されるクロックの立下りで、DFF4のQ出力端子の”1”が、DFF5のQ出力端子にラッチされる。その結果、DFF10のQ出力端子にTFF11のQ出力端子にセットされた”1”がラッチされ、セレクタ8及び9の選択制御端子における選択情報が”1”から”0”に変更される。そしてセレクタ8及び9の出力端子には、オフタイムレジスタ6のデータ及びこれに対応する下位ビット制御情報がそれぞれ下位ビット制御回路23及オフタイムレジスタ6から出力される。

【0071】

つまり、セレクタ9の出力端子からの出力信号は、オンタイムレジスタ7のデータからオフタイムレジスタ6のデータに切り替えられ、”2H”から”2H”に変化する(同一のデータである)。また、セレクタ8の出力は下位ビット制御回路23のオンタイムのビットデータからオフタイムのLSBのビットデータに替わる。

【0072】

このようにして、PWM信号生成装置は図6〜図8に示すタイミングで動作して、下位ビット制御回路23がその制御信号を図6〜図8に示すタイミングで出力する。これによって、図6〜図8に示すオンタイムでのみ微小時間δで変位するパルスを生成することができる。

【0073】

図6〜図8に示すタイムチャートに応じて動作させると、上述のパルス信号(クロック信号)を生成することができる。その際、微小時間δの信号を付加するために、タイミング回路18が、それぞれタイミングの異なるパルスを生成するTFF11、12、31、32、33、及び34の出力を切り替える。

【0074】

また、タイミング回路17は、パルス信号に微小時間δの信号変化を実現するために、レジスタ6及び7のレジスタ値に応じて生成される基本パルス信号に係る情報および23で生成される加減算情報を必要に応じて加算又は減算(補数+1を加算)する。すなわち、23で生成された加算値、減算値を7−1,7−2のフルアダーで加算して、必要な制御情報を生成する。この7−1,7−2のフルアダー演算は、下位の微小PWM変動用bitの演算用の回路で、δの値を1増分させるためには1を加算し、δの値を1減算させるためには、1の補数+1の値を加算させる。

【0075】

上位のPWM回路への桁上げ、桁下げは、15(桁下げ)のアダーが実施する。上位のPWM回路への桁上げの場合には、定数値15−2がアダー15に与えられ、上位のPWM回路への桁下げは、定数値15−4がアダー15に与えられる。そして、定数値15−2又は15−4がアダー14の出力結果と加算されるように、タイミング回路17は制御信号2−7及び2−15を制御する(そのために、17のタイミング回路は、16のセレクタと、15−3のセレクタを切り替え、14のアダーの加算結果に15−2の固定値を加算するか、15−4の固定値を加算するか、または加算しないか、条件を判別して制御する)。

【0076】

DFF5のQ出力信号が遅延バッファ53及び1ショット回路52を介してDFF4及び5に与えられ、DFF4及び5をリセットするので,DFF4及び5のQ出力端子から出力される制御信号が基本クロックの1周期内で初期化される。その結果、図4に示すPWM信号生成装置では、基本クロックの2分周の信号まで容易に微小時間δの変調をかけた信号を生成することができる。

【0077】

タイミング回路18は、下位ビット制御回路23で下位ビット情報が生成される都度、それまでに加算された結果に対してフルアダーで加算を行い、その加算結果をクロック選択制御回路24に与える。これによって、セレクタ13が制御されて、微小時間δを加味したパルス信号が出力端子21に出力制御される。

【0078】

なお、タイミング回路17は、下位ビット制御回路23で下位ビット情報が生成される都度、それまでに加算された結果と下位ビット情報とを比較する。そして、それまでに加算された結果が”0”で、次に下位ビット制御回路23で生成された下位ビット情報を加えた結果が”1”以上であると、タイミング回路17は出力端子2−7に”1”をたて、アダー14の出力結果に”1”を加えた値をレジスタ2に設定する。また、それまでに加算された結果が”1”以上で、次に下位ビット制御回路23で生成される下位ビット情報を加えた結果が”0”であると、タイミング回路17は出力端子2−15に”1”をたて、アダー14の出力結果が1減算された値をレジスタ2に設定する。

【0079】

ここで、図4に示す下位ビット制御回路23についてさらに説明する。

【0080】

図9は図4に示す下位ビット制御回路23の構成を示すブロック図である。

【0081】

図9を参照すると、下位ビット制御回路23は、(X+1)ビットのアップダウンカウンタ3−1(Xは0以上の整数)を有している。アップダウンカウンタ3−1のクロック入力端子はゲート3−9を通じて入力端子3−12の信号が入力され、この入力端子3−12は図4に示すDFF5のQ出力端子に接続されている。

【0082】

本実施形態では、X=0の場合を示しているが,一般的には周波数の微小変調のδに応じて、Xは決定される。例えば,δが2(±2δの変調の場合)のときX=1であればよく、通常用いる範囲のX値のMAX値、例えば、7等の値にしておけばよい。

【0083】

CPUバス入力端子3−11は、MAX値レジスタ3−2、MIN値レジスタ3−3、及び出力モード設定3−15に接続され、このCPUバス入力端子3−11は外部のCPUバスに接続される。そして、外部のCPUは当該バスを用いて各レジスタに制御データを書き込む。

【0084】

MAX値レジスタ3−2の制御信号出力端子は、MAX値検知回路3−5の一方の入力端子に接続され、MIN値レジスタ3−3の制御信号出力端子はMIN値検知回路3−4の一方の入力端子に接続される。MAX値検知回路3−5及びMIN値検知回路3−4の各々は、例えば、デジタルコンパレータで構成される。そして、MAX値検知回路3−5及びMIN値検知回路3−4の他方の入力端子には、MAX値レジスタ3−2及びMIN値レジスタ3−3のレジスタの情報に対応するアップダウンカウンタ3−1の出力端子が、バス3−17を介して接続される。さらに、バス3−17は、出力データ設定回路3−10のデータ入力端子に接続される。

【0085】

MIN値検知回路3−4及びMAX値検知回路3―5の検出結果を出力する出力端子は、U/D制御回路3−6の制御回路の入力端子に接続される。U/D制御回路3−6には、さらに出力モード設定レジスタ3−15の制御データ出力端子が接続される。そして、U/D制御回路3−6のU/D制御信号出力端子がアップダウンカウンタ3−1のU/D制御信号入力端子及びU/D繰り返し回数検知回路3−7に信号線3−20を介して接続される。

【0086】

U/D繰り返し回数検知回路3−7の出力端子は、偶奇判定回路3−8の入力端子に接続され、偶奇判定回路3−8の出力端子は出力データ設定回路3−10の入力端子に接続される。そして、出力データ設定回路3−10の制御信号入力端子には、出力モード設定レジスタ3−15の制御データ出力端子が接続され、さらに、出力データ設定回路3−10にはバス3−17が接続される。

【0087】

加えて、出力データ設定回路3−10のオン幅制御情報出力端子が信号出力端子3−14に接続される。

【0088】

アップダウンカウンタ3−1のクロック信号入力端子には、2入力ANDゲート3−9の出力端子が接続され、このANDゲート3−9の一方の入力端子には、信号入力端子3−12が接続され、他方の入力端子には、U/D制御回路3−6の制御信号出力端子が接続される。

【0089】

また、U/D制御回路3−6において、TFF11のQ出力がその制御信号入力端子3−21に入力される。さらに、TFF11のQ出力は、出力データ設定回路3−10に制御信号として与えられる。

【0090】

続いて、図9に示す下位ビット制御回路23の動作について説明する。まず、外部のCPUがCPUバス入力端子3−11を介して制御情報をMAX値レジスタ3−2、MIN値レジスタ3−3、及び出力モード設定レジスタ3−15に書き込む。例えば、MAX値レジスタ3−2には制御情報として”1”が書き込まれ、MIN値レジスタ3−3には制御情報として”0”が書き込まれる。出力モード設定レジスタ3−15には、PWMの微小増減をONタイムでのみ実行するパラメータ”01”が書き込まれる。

【0091】

図示の下位ビット制御回路は、図示しないリセット回路を有しており,このリセット回路によってアップダウンカウンタ3−1はイニシャル時(パワーオンリセット時)”0”にリセットされる。また、U/D制御回路3−6のU/D制御信号出力端子には、アップダウンカウンタ3−1がクロック毎にアップするカウント値の初期値”1”がリセット時に設定されているものとする。さらに、U/D繰り返し回数検知回路3−7のカウント値も”0”に初期化されており、出力データ設定回路3―10の出力端子には、初期値”0”が設定されている。ここでは、アップダウンカウンタ3−1の出力信号の初期値0がそのまま出力データ設定回路3−10を通じて、その信号出力端子3−14に出力されるように動作する。

【0092】

アップダウンカウンタ3−1、MIN値検知回路3−4、MAX値検知回路3−5、及びU/D制御回路3−6によって微小変位δの値が決定される。具体的には、アップダウンカウンタ3−1は、U/D制御回路3−6によって制御され、DFF5のQ出力を基準として、MIN値検知回路3−4のMIN値とMAX値検知回路3−5のMAX値との間をアップ及びダウンする。

【0093】

図示の例では、アップダウンカウンタ3−1は”0101”の変化を繰り返す。U/D繰り返し回数検知回路3−7は、この”01”の繰り返し回数を検知する。U/D繰り返し回数検知回路3−7による検知結果は、偶奇判定回路3−8によって偶奇を判定される。そして、偶奇判定回路3−8の判定結果が出力データ設定回路3−10に設定される。

【0094】

出力データ設定回路3−10は、出力モード設定レジスタ3−15に設定されている値(モード)、アップダウンカウンタ3−1の出力値、及び偶奇判定回路3−8の出力値に応じて信号出力端子3−14に出力する信号を制御する。

【0095】

図10は、図9に示す出力モード設定レジスタ3−15のレジスタ値に応じた信号出力を説明するための図である。

【0096】

図11は、図9に示す出力モード設定レジスタ3−15のレジスタ値が”01”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【0097】

図12は、図9に示す出力モード設定レジスタ3−15のレジスタ値が”02”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【0098】

図13は、図9に示す出力モード設定レジスタ3−15のレジスタ値が”03”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【0099】

いま、出力モード設定レジスタ3−15の設定モードが”01”のとき、U/D制御回路3−6はTFF11のQ出力が”0”の際にアップダウンカウンタ3−1にクロックが印加しないように制御する。つまり、U/D制御回路3−6はANDゲート3−9においてアップダウンカウンタ3−1への信号入力を禁止する。そして、U/D制御回路3−6はU/D信号を当該タイミングでMIN値検知回路3−4及びMAX値検知回路3−5の比較結果に応じてDFF5の立ち上がりでラッチして、信号線3−20に送出する。

【0100】

U/D繰り返し回数検知回路3−7は信号線3−20の信号をクロックとして、当該入力クロックをTFFによって計数する。偶奇判定回路3−8は、U/D繰り返し回数検知回路3−7の検知結果が”1”であると、繰り返しが偶数番目であると判定する。そして、偶奇判定回路3−8は、信号出力端子3−14に出力する出力データを減算するためのデータを選択する。一方、U/D繰り返し回数検知回路3−7の検知結果が”0”であると、偶奇判定回路3−8は繰り返しが奇数番目であると判定する。そして、偶奇判定回路3−8は、信号出力端子3−14に出力する出力データを加算するためのデータを選択する。

【0101】

出力データ設定回路3−10は、出力モード設定レジスタ3−15の設定モードに応じて出力データを制御する。そして、出力データ設定回路3−10はアップダウンカウンタ3−1のカウンタ出力値に応じて、TFF11のQ出力の信号基準で設定モードを加味した出力データを信号出力端子3−14に出力する。

【0102】

設定モードが”3”である場合には、出力データ設定回路3−10を除いて、設定モード”1”と同じ制御タイミングで下位ビット制御回路23は動作する。そして、設定モード”1”である場合に信号出力端子3−14に現われるON下位出力値が、TFF11のQ出力=1となるタイミングでラッチされ、次のOFF下位出力値とされる。

【0103】

但し、δにおいて2以上の増分がある場合、その増分に対応したタイミングが必要となる。このため、遅延バッファの増設、その遅延クロックによる出力信号を生成するDFFの増設を行う必要がある。そして、増設したDFFを選択して、信号出力するように、セレクタ13、セレクタ選択回路24、及びタイミング回路17及び18を拡張する必要がある。

【0104】

図14は、図4に示すクロック選択制御回路24の動作の一例を説明するための図である。そして、図14(a)は図4に示すクロック選択制御回路24の構成の一例を示すブロック図であり、図14(b)は図4に示すセレクタ13による選択動作の一例を示す図である。

【0105】

図4及び図14を参照すると、図4に示すクロック選択制御回路24は、例えば、デコーダ回路であり、2つの入力端子の組み合わせに応じてクロック信号を出力してセレクタ13を制御する。つまり、クロック選択制御回路24はタイミング回路18の2ビット出力端子OUTSEL1及びOUTSEL2に応じてセレクタ13を制御する。具体的には、クロック選択制御回路24はセレクタ13を制御してTFF11のQ出力、TFF12のQ出力、TFF31のQ出力、又はTFF32のQ出力をPWMOUT21に出力する。

【0106】

図14(a)に示すように、クロック選択制御回路14は2入力ANDゲート11−1〜11−4及びインバータ11−5及び11−6を有している。そして、タイミング回路18の出力端子OUTSEL1に接続される入力端子INSEL1がANDゲート11−2及び11−4の一方の入力端子に接続されるとともに、インバータ11−5の入力端子に接続される。インバータ11−5の出力端子は、ANDゲート11−3及び11−1の一方の入力端子に接続される。

【0107】

タイミング回路18の出力端子OUTSEL2に接続される入力端子INSEL2がANDゲート11−3及び11−4の他方の入力端子に接続されるとともに、インバータ11−6の入力端子に接続される。インバータ11−6の出力端子はANDゲート11−1及び11−2の他方の入力端子に接続される。

【0108】

図14(a)に示す構成のクロック選択制御回路24では、INSEL2及び1の入力値が”00”、”01”、”10”、及び”11”の組み合わせに応じて出力が変化する。例えば、入力値が”00”の際には、ANDゲート11−1の出力のみが”1”となる。入力値が”01”の際には、ANDゲート11−2の出力のみが”1”となる。入力値が”10”の際には、ANDゲート11−3の出力のみが”1”となる。そして、入力値が”11”の際には、ANDゲート11−4の出力のみが”1”となる。

【0109】

その結果、図14(b)に示すように、INSEL2及び1の入力値が”00”の際には、PWNOUT21にはTFF11のQ出力が出力され、INSEL2及び1の入力値が”10”の際には、PWMOUT21にはTFF12のQ出力が出力される。また、INSEL2及び1の入力値が”01”の際には、PWMOUT21にはTFF31のQ出力が出力される。そして、INSEL2及び1の入力値が”11”の際には、PWMOUT21にはTFF32のQ出力が出力される。

【0110】

なお、TFF33及び34のQ出力を選択するSEL05及びSEL06は、図示の例では、GNDに接続されて選択されないように構成されている。

【0111】

図15は、図4に示す1ショット回路52の一例を示すブロック図である。

【0112】

図15において、入力端子INは、2入力ANDゲート11−7の一方の入力端子に接続されるとともに、遅延量の大きなインバータ11−8の入力端子に接続される。そして、インバータ11−8の出力端子はANDゲート11−7の他方の入力端子に接続される。ANDゲート11−7の出力端子は1ショット回路の出力端子である1SHOT_OUTに接続される。

【0113】

入力端子INが”0”であると、インバータ11−8の出力は”1”となる。次に、入力端子INが”0”から”1”に遷移すると、ANDゲート11−7の一方の入力端子は”1”となる。一方、インバータ11−8の出力が接続されているANDゲート11−7の他方の端子は”1”となっているが,インバータ11−8の遅延時間後に”0”となる。このため、ANDゲート11−7の出力は、インバータ11−8の遅延時間分だけ”1”となって、1SHOT_OUTからは1ショットパルスが出力される。

【0114】

なお、インバータ11−8は、図4に示すバッファ53と同等の遅延時間を有しており、これによってDFF4及び5を確実にリセットする。DFF5がリセットされても、1ショット回路52の出力する1ショットパルスを確実に出力するためバッファ53が挿入されている。

【0115】

図16は、図4に示すクロック選択制御回路24の動作の他の例を説明するための図である。そして、図16(a)は図4に示すクロック選択制御回路24の構成の他の例を示すブロック図であり、図16(b)は図4に示すセレクタ13による選択動作の他の例を示す図である。

【0116】

なお、図16(a)において、図14(a)に示すクロック選択制御回路24と同一の構成要素については同一の参照番号を付し、説明を省略する。

【0117】

図示のクロック選択制御回路24は、ANDゲート11−1〜11−4とインバータ11−5〜11−6に加えて、レジスタ(REG)12−1、セレクタ12−2、及び複合ゲート(AND・ORゲート)12−3〜12−8を有している。

【0118】

このクロック選択制御回路24では、ANDゲート11−1〜11−4の出力の接続をレジスタ12−1、セレクタ12−1、及び複合ゲート12−3〜12−8によって切り替える。

【0119】

図示のように、複合ゲート12−3〜12−8においてANDゲートの一方の入力端子はインバータを介してレジスタ12−1に接続されている。また、複合ゲート12−3〜12−8においてANDゲートの他方の入力端子はそれぞれANDゲート11−4の出力端子、ANDゲート11−3の出力端子、GND、ANDゲート11−2の出力端子、GND、及びAND11−1の出力端子に接続されている。

【0120】

レジスタ12−1はその入力バスがREGIN端子に接続され、外部CPUによってデータが設定される。レジスタ12−1のデータ出力端子がセレクタ12−2の制御信号入力端子に接続される。

【0121】

セレクタ12−2はその制御入力端子が”1”であると、すなわち、レジスタ12−1のQ出力が1のとき、複合ゲート12−3〜12−8のORゲートの入力端子に図16(a)の回路に明示されるセレクタ12−2の入力端子に加わる信号が与えられ、SEL01〜SEL06に出力されることになる。つまり、この条件の場合には、複合ゲート12−3〜12−8のANDゲートの一方の入力端子が”0”となるように、セレクタ12−2の制御入力端子に加わる信号と逆相の信号が加わってセレクタ12−2から出力される信号がそのままSEL01〜SEL06に出力される。

【0122】

セレクタ12−2の制御入力端子が”0”であると、すなわち、レジスタ12−1の出力が0のとき、セレクタ12−2の出力端子には、図示されていないセレクタ12−2の他方のGNDに接地された入力端子が接続され、全て”0”が出力される。複合ゲート12−3〜12−8のORゲートの一方の入力端子は、全て”0”となる。一方、ORゲートの他方の入力端子は、ANDゲートの出力端子に接続されているから、当該タイミングで一方の入力端子が全て”1”となり、他方の入力端子の入力信号が直接SEL01〜SEL06に出力される。

【0123】

前述のように、レジスタ12−1は、外部CPUにおいてそのレジスタ値が制御可能となっており、外部CPUは必要に応じてレジスタ12−1のレジスタ値を”1”又は”0”に切り替える。レジスタ12−1のレジスタ値が”1”の場合には、上述した動作と同様の動作が行われる。

【0124】

レジスタ12−1のレジスタ値が”0”の場合には、INSEL1及びINSEL2の値の組み合わせによってPWMOUT21(図4)に出力される出力信号の選択が、レジスタ12−1のレジスタ値が”1”のときと変化する。INSEL1及び2がそれぞれ”0”及び”1”であると、TFF31のQ出力がTFF12のQ出力に変更されて出力される。INSEL1及び2がそれぞれ”1”及び”0”であると、TFF2のQ出力がTFF33のQ出力に変更されて出力される。また、INSEL1及び2がそれぞれ”1”及び”1”の場合には、TFF32のQ出力がTFF34のQ出力に変更されて出力される。これによって、出力信号の微変調特性を変更することができる。

【0125】

図17は、図4に示すPWM信号生成装置を用いた通信装置の一例を示すブロック図である。

【0126】

図17において、図示の通信装置は図4で説明したPWM信号生成装置13−2及び13−3を有している。そして、これらPWM信号生成装置13−2及び13−3はCPU13−1に接続されるとともに、調歩同期方式通信モジュール13−4及び13−5に接続されている。CPU13−1とPWM信号生成装置13−2及び13−3には外部クロック端子13−6からクロック信号端子13−16を介して外部クロックが与えられる。

【0127】

CPU13−1のバス信号線は、バス13−13を介してPWM信号生成装置13−2〜13−3及び通信モジュール13−4〜13−5に接続されており、CPU13−1はこのバス13−13を介してPWM信号生成装置13−2〜13−3及び通信モジュール13−4〜13−5に備えられた制御レジスタにデータを設定する。CPU13−1は通信モジュール13−4及び13−5に対してその他の通信用データも設定する。

【0128】

CPU13−1はバス13−13を介してPWM信号生成装置13−2〜13−3及び通信モジュール13−4〜13−5に初期化データを設定する。続いて、CPU13−1はバス13−13を介してPWM信号生成装置13−2及び13−3に制御データを書き込む。

【0129】

例えば,CPU13−1は通信モジュール13−4に対して基本クロックの4分周のクロックが信号線13−14を介して供給されるように、PWM信号生成装置13−2のオフタイムレジスタ6及びオンタイムレジスタ7の値を書き替える。また、CPU13−1は通信モジュール13−5に対して8分周の基本クロックが信号線13−15の信号線を介して供給されるように、PWM信号生成装置13−3のオフタイムレジスタ6及びオンタイムレジスタ7の値を書き替える。

【0130】

4分周の場合には、オフタイムレジスタ6及びオンタイムレジスタ7の各々には、”10H”が書き込まれる。8分周の場合には、オフタイムレジスタ6及びオンタイムレジスタ7の各々には、”110H”が書き込まれる。さらに、PWM信号生成装置13−2及び13−3において、下位ビット制御回路23のレジスタにそれぞれ異なったレジスタ値が書き込まれる。

【0131】

例えば、PWM信号生成装置13−2においてMAX値レジスタ3−2のレジスタ値及びMIN値レジスタ3−3のレジスタ値がそれぞれ”1”及び”0”を設定し、PWM信号生成装置13−3においてはMAX値レジスタ3−2のレジスタ値及びMIN値レジスタ3−3のレジスタ値をそれぞれ”2”及び”1”と設定することによって、通信モジュール13−4及び13−5のクロックの微調周期変動範囲を互いに変えることができる。なお、ONタイムが固定で、オフタイムを変調することが有利である場合には、出力モード設定レジスタ3−15には”01”が書き込まれる。

【0132】

このようにして、PWM信号生成装置13−2及び13−3の設定を行えば、PWM信号生成装置13−2は、信号線13−14を通じて、PWM信号生成装置13−3は信号線13−15を通じて通信モジュール13−4及び13−5のクロックを互いに異なった範囲のパルス幅変調で実現することができる。また、変化範囲についてノイズスペクトル的に問題が生じる場合には、クロック選択制御回路24のレジスタの設定を変更すれば、パルス幅の変調のモードを変えることができる。

【0133】

上述のように、本実施の形態によるPWM信号生成装置では、基準クロックを倍以上の周波数にすることなく、基準クロックの1周期以下の範囲でクロックに微小時間変調をかけることができる。そして、PLLを用いることなく、しかも高周波クロックを用いる必要がなく、回路規模を小さくしてSSCGを実現することができる。

【0134】

加えて、複数通信を同時に実行するASIC等において、互いに異なるSSCGを用いてクロックを同時に複数生成して、ノイズを削減することができる。

【0135】

以上、本発明について実施の形態に基づいて説明したが、本発明は、これらの実施の形態に限定されるものではなく、この発明の要旨を逸脱しない範囲の様々な形態も本発明に含まれる。

【0136】

例えば、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記録媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0137】

1 カウンタ

2,6,7 レジスタ

3 コンパレータ

4,5,10 DFF(Dタイプフリップフロップ)

8,9,13,15−3,16 セレクタ

11,12,31,32,33,34 TFF((Tタイプフリップフロップ)

14,15 アダー

17,18 タイミング回路

23 下位ビット制御回路

24 クロック選択制御回路

【技術分野】

【0001】

本発明は、PWM信号生成装置に関し、特に、ノイズレベルを低減することのできるPWM信号生成装置に関する。

【背景技術】

【0002】

一般に、ASIC(Application Specific Integrated Circuit)等の集積回路では、その内部クロックにおけるノイズを低減する必要がある。従来、ノイズの低減のため、SSCG(spread spectrum clock generator(周波数変調機能付きクロック発生回路)が用いられている。このSSCGでは、クロック信号の周波数を僅かに変動させて、クロック信号の周波数スペクトラムのピーク値を下げている。これによって、放射雑音等のノイズを低減させている。

【0003】

例えば、SSCGを用いた送信装置において、通信放射雑音を低減させるため、PLL回路において、基本クロック信号から高速クロック信号を生成し、PWM信号生成回路によって高速クロック信号を最小単位として通信クロック信号及び受信タイミング信号の各々を独立した任意の時間長のPWM信号として生成するようにしたものがある(特許文献1参照)。

【0004】

ここでは、通信クロック信号においてそのオフタイム幅をパルス毎に変更して、任意の時間長において同一のパルス幅の通信クロック信号と同一のパルス数を有する通信クロック信号(つまり、PWM信号)を生成するようにしている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2003−224552号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、特許文献1に記載の手法では、PLL回路を複数の送信装置に適用しようとすると、不可避的に回路規模が増大するばかりでなく、効果的に放射雑音を低減することが困難となる。さらに、生成されるPWM信号の周期が、PLL回路で生成する基本クロック信号の整数倍となって、ノイズを分散させることが困難となる。加えて、ノイズの強度が高いスペクトラムに対してはピーク値を下げることが難しい。いずれにしても、特許文献1に記載の手法では、回路規模を小さくして、効果的に放射雑音等のノイズを低減することが難しいという課題がある。

【0007】

従って、本発明の目的は、回路規模を小さくして効果的に放射雑音等のノイズを低減することのできるPWM信号生成装置を提供することにある。

【課題を解決するための手段】

【0008】

上記の目的を達成するため、本発明によるPWM信号生成装置は、基準クロックに応じて動作してPWM信号を生成するPWM信号生成装置において、前記基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成するクロック生成手段と、前記基準クロックに応じて前記変動クロックを第1のPWM信号として出力する第1のPWM出力制御手段と、前記基準クロックを所定の時間遅延させた遅延クロックに応じて前記変動クロックを第2のPWM信号として出力する第2のPWM出力制御手段と、前記第1及び前記第2のPWM信号を選択的に前記PWM信号として出力する選択手段とを有することを特徴とする。

【発明の効果】

【0009】

本発明によれば、PWM信号の周波数を僅かに変動させて出力する際、回路規模を小さくして効果的に放射雑音等のノイズを低減することができるという効果がある。

【図面の簡単な説明】

【0010】

【図1】一般的なPWM信号生成装置の一例を示すブロック図である。

【図2】図1に示すPWM信号生成装置の動作を説明するためのフローチャートである。

【図3】本発明の実施の形態によるPWM信号生成装置の一例についてその概念を説明するためのブロック図である。

【図4】図3で説明した動作原理を用いたハードウェア構成の一例を示す図である。

【図5】図4に示すタイミング回路の一例を説明するための図であり、(a)はその構成の一例を示すブロック図、(b)は(a)に示すフルアダーの真理値表を示す図である。

【図6】図4に示すPWM信号生成装置の動作を説明するためのタイムチャートの一例を示す図である。

【図7】図4に示すPWM信号生成装置の動作を説明するためのタイムチャートの他の例を示す図である。

【図8】図4に示すPWM信号生成装置の動作を説明するためのタイムチャートのさらに他の例を示す図である。

【図9】図4に示す下位ビット制御回路の構成を示すブロック図である。

【図10】図9に示す出力モード設定レジスタのレジスタ値に応じた信号出力を説明するための図である。

【図11】図9に示す出力モード設定レジスタのレジスタ値が”01”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【図12】図9に示す出力モード設定レジスタのレジスタ値が”02”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【図13】図9に示す出力モード設定レジスタのレジスタ値が”03”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【図14】図4に示すクロック選択制御回路の動作の一例を説明するための図であり、(a)は図4に示すクロック選択回路の構成の一例を示すブロック図、(b)は図4に示すセレクタによる選択動作の一例を示す図である。

【図15】図4に示す1ショット回路の一例を示すブロック図である。

【図16】図4に示すクロック選択制御回路の動作の他の例を説明するための図であり、(a)は図4に示すクロック選択制御回路の構成の他の例を示すブロック図、(b)は図4に示すセレクタ13による選択動作の他の例を示す図である。

【図17】図4に示すPWM信号生成装置を用いた通信装置の一例を示すブロック図である。

【発明を実施するための形態】

【0011】

以下、本発明の実施の形態によるPWM信号生成装置について図面を参照して説明する。

【0012】

まず、本発明の実施の形態によるPWM信号生成装置の理解を容易にするため、一般的なPWM信号生成装置の一例について説明することにする。

【0013】

図1は、一般的なPWM(パルス幅変調)信号生成装置の一例を示すブロック図である。

【0014】

図1を参照すると、図示のPWM信号生成装置は、自走のnビット(一般的には,nはニブル(nibble)の整数倍)で構成されたバイナリーカウンタ201を有している。レジスタ202はバイナリーカウンタ201と同一のビット長(レジスタ長)で構成されている。デジタルコンパレータ205はバイナリーカウンタ201及びレジスタ202の各々のLSB(Least Significant Bit)〜MSB(Most Significant Bit)をビット毎に比較して、全ビットの値が一致した際にその出力を“1”とする。

【0015】

デジタルコンパレータ205の出力は、信号線210に出力され、T−フリップフロップ(以下TFFという)206のT入力端子に入力されるとともに、CPU204の割り込み入力端子に入力される。ROM203にはデータ及び実行プログラムが記録され、CPU204はROM203をアクセスしてデータ及び実行プログラムを読み込む。さらに、CPU204にはレジスタ202の出力が信号線209を介して入力され、CPU204の演算出力端子は信号線212を介してレジスタ202の信号入力端子に接続されている。

【0016】

システムクロックが信号線207を介してカウンタ201とCPU204のクロック信号入力端子とに与えられ、さらに、システムクロックは、同期をとるため、デジタルコンパレータ205に与えられる。そして、カウンタ201の制御信号入力端子Rには、CPU204の制御信号出力端子が信号線213を介して接続されている。

【0017】

図2は、図1に示すPWM信号生成装置の動作を説明するためのフローチャートである。

【0018】

図1及び図2を参照して、いまシステムリセットが行われ(ステップS21)、CPU204は動作可能な状態となると、CPU204はROM203からPWMの制御情報、例えば,信号波形のロウ(L)レベル期間のデータ(以下、Lレベルデータと呼ぶ)を読み出す(ステップS22)。そして、CPU204は当該データをレジスタ202にセットする(ステップS23)。CPU204は信号線213を介してカウンタ201にカウント開始信号を送出する(ステップS24)。これによって、カウンタ201はカウントを開始する。

【0019】

カウンタ201が、例えば、バイナリアップカウンタであるとすると、カウンタ201は信号線207を介して入力されるシステムクロックに同期してカウントアップする。そして、デジタルコンパレータ205はカウンタ201のカウント値とレジスタ202にセットされたLレベルデータとを比較して(ステップS25)、カウント値とLレベルデータとが一致するか否かを判定する(ステップS26)。カウント値とLレベルデータとが一致すると(ステップS26において、YES)、デジタルコンパレータ205は、信号線210上に“1”を示す信号を出力する。

【0020】

CPU204は、信号線214を介して予めクリア信号をTFF206に送って、TFF206をリセットする。このため、デジタルコンパレータ205の出力が”1”となると、TFF206の出力信号が反転し(ステップS27)、出力端子211に現われる出力信号が“L”から“H”に変化する。

【0021】

一方、デジタルコンパレータ205の出力はCPU204に対する割り込み信号となる。CPU204が割り込み信号を検出すると(ステップS28)、CPU204はROM203から、信号波形を新たに生成するハイ(H)レベルの期間のデータ(以下、Hレベルデータという)を読み出す(ステップS29)。そして、CPU204はHレベルデータとレジスタ203にセットされたデータ(レジスタデータ)との和を求めて、和データとしてレジスタ202に再セットする。(ステップS30)。この際、CPU204は和のキャリーは切り捨てる。

【0022】

その後、図示のステップS31〜S34において同様の動作を繰り返す。そして、CPU204は、ステップS35においてROMから次のLレベルデータを読み出し、このLレベルとレジスタデータとを加算してレジスタ202にセットする(ステップS36)。その後、処理はステップS25に戻って、以後同様にして処理が繰り返される。この結果、出力端子211から所望のPWM信号が出力される。

【0023】

ここで、図1に示すPWM信号生成装置を適用したPWM信号生成装置の一例について説明する。

【0024】

図3は、本発明の実施の形態によるPWM信号生成装置の一例についてその概念を説明するためのブロック図である。

【0025】

図3を参照して、図示のPWM信号生成装置は、図1に示す構成に加えてバッファ250、TFF(Tタイプフリップフロップ)251、及びセレクタ(選択手段)252を有している。そして、図3に示す例では、CPU(制御手段)204の処理が後述するように図1で説明したCPU204の処理と異なり、さらに、TFF206として同期型TFFが用いられる。

【0026】

図3に示すPWM信号生成装置では、バッファ250の入力端子がクロック信号線207に接続され、バッファ250の出力端子がTFF251のクロック入力端子に接続されている。TFF251のリセット端子は信号線214に接続されており、TFF251のQ出力端子は、2入力セレクタ252の一方の入力端子に接続されている。また、2入力セレクタ252の他方の入力端子には、TFF206のQ出力端子が接続されている。なお、基準クロックはカウンタ207(カウント手段)に与えられ、カウンタ207は基準クロックのパルス数をカウントする。そして、カウンタ207はカウント値をデジタルコンパレータ205(比較手段)に与える。

【0027】

さらに、2入力セレクタ252の出力端子は、信号出力端子211に接続されており、2入力セレクタ252の制御信号入力端子は、CPU204の制御信号出力端子に接続されている。TFF206のクロック入力端子は、クロック信号線207に接続されており、TFF251及び206のT入力端子は信号線210に接続されている。

【0028】

図3に示す例では、説明を簡単にするため、追加クロックを単一のバッファ250による遅延クロックとしている(つまり、バッファ250によって、基準クロックを所定の遅延時間遅延させて、遅延クロックとしている)。ROM203にはオン期間(ON期間)を示すオンタイム情報及びオフ期間(OFF期間)を示すオフタイム情報(パルス幅データ)が格納されている。そして、オンタイム情報及びオフタイム情報におけるLSBを、追加クロック(遅延クロック)に対応する情報(以下、LSB情報と呼ぶ)とする。

【0029】

LSB情報(予め規定されたビット)が”0”(第1の値)であると、2入力セレクタ252に対する入力がTFF206のQ出力端子に接続され、かつTFF206の出力信号がクロック信号線207上のクロック信号の立ち上がりに同期して出力される。

【0030】

一方、図2で説明したように、LSB情報とレジスタ202(レジスタ手段)にセットされたレジスタデータ(レジスタ値)とを加算した結果が”1”(第2の値)であると、LSBのビット時間分だけ出力タイミングをずらす必要が生じる。このため、CPU204は、TFF251の出力信号が出力端子211に出力されるように、2入力セレクタ252に制御信号を送出する。この結果、出力端子211に現われる出力信号はバッファ250の遅延時間分(例えば、δ時間分)だけ遅れて出力されることになる。その後、LSB情報を立てないと、このクロックのタイミングで動作が持続される。

【0031】

このように、セレクタ252は選択的にTFF206及びTFF251に接続されることになる。

【0032】

一方、ビット情報を1減らす情報をLSB情報に加えれば,次のPWM信号生成タイミングにおいて、それ以前のLSB情報と加算された結果を”0”にして、TFF206の出力が2入力セレクタ252によって選択されて、結果的に出力端子211から出力される出力信号(クロック信号)の周波数が変動することになる。

【0033】

図3に示す例においては、CPU204、レジスタ202、カウンタ201、及びデジタルコンパレータ205が基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成するクロック生成手段として機能している。また、TFF206が基準クロックに応じて変動クロックを第1のPWM信号として出力する第1のPWM出力制御手段として機能し、TFF251が基準クロックを所定の時間遅延させた遅延クロックに応じて変動クロックを第2のPWM信号として出力する第2のPWM出力制御手段として機能する。

【0034】

続いて、図3で説明した動作原理を用いたPWM信号生成装置の一例について説明する。

【0035】

図4は、図3で説明した動作原理を用いたPWM信号生成装置のハードウェア構成の一例を示す図である。

【0036】

図4に示すPWM信号生成装置では、フリーランカウンタ1、このフリーランカウンタ1と同一のビット幅を有するレジスタ2、及びアダー(加算器)14を有している。最も簡単な例では、2進フリーランカウンタ、2進のアダーが用いられる。図示の例では、フリーランカウンタ1のカウント値とレジスタ2のレジスタ値とをクロックのカウント毎に比較する。そして、一致したタイミングでレジスタ値にON幅データ又はOFF幅データを交互にアダー14によって加算する。この加算値がレジスタ2に再設定される。さらに、一致信号が出力される毎に出力レジスタの値をトグルして、PWM信号を生成する。なお、ビット数は、任意のNビット(Nは2以上の整数)で実現することができる。

【0037】

ここでは、一致信号が出力される毎、つまり、クロックの立ち上がりにおいてトグルするレジスタとして、TFF11、12、31、32、33、34を備えている。そして、TFF11、12、31、32、33、及び34にそれぞれバッファ26〜30によってCLK_IN端子から与えられるクロック信号を所定の遅延時間ずらして加える。

【0038】

TFF11、12、及び31〜34のQ出力端子は、それぞれセレクタ13の入力端子に接続されており、セレクタ13において、TFF11、12、及び31〜34のいずれかの出力信号をPWMOUT出力端子21にPWM信号として出力する。そして、セレクタ13によって逐次PWM信号を切り替えて、周波数、オンタイム、及びオフタイムの微調整を行う。

【0039】

いま、N=8とすると、フリーランバイナリカウンタ1は8ビットカウンタとなり、レジスタ2は8ビット長8のレジスタとなる。そして、コンパレータ3はビット毎にカウンタ1のカウント値とレジスタ2のレジスタ値とを比較する。そして、全ビットの値が一致すると、コンパレータ3は”1”を示す出力信号(比較結果信号)を出力する。コンパレータ3の出力信号はDFF4のD入力端子に与えられる。さらに、コンパレータ3の出力信号はTFF11、12、及び31〜34のT入力端子に与えられる。

【0040】

これらTFF11、12、及び31〜34の各々は、T入力端子に”1”が現われると、そのクロック端子に与えられるクロック信号がLレベルからHレベルに立ち上がる際、出力信号が反転するように動作する。

【0041】

TFF11のクロック入力端子には、CLK_IN端子20から与えられるクロック信号が入力される。CLK_IN端子20はバッファ26の入力端子に接続されている。そして、バッファ26〜30が順次接続され、バッファ26〜30の出力端子はそれぞれTFF12及び31〜34のクロック入力端子に接続されている。

【0042】

さらに、CLK_IN入力端子20は、カウンタ1及びDFF4のクロック入力端子に接続されている。TFF11、12、及び31〜34のQ出力端子は、それぞれセレクタ13の入力端子に接続され、セレクタ13の出力端子はPWMOUT出力端子21に接続されている。そして、TFF11、12、及び31〜34のQ出力信号はセレクタ13の選択制御端子に印加される選択信号に応じていずか1つが選択されてPWMOUT出力端子21に出力される。

【0043】

なお、セレクタ13の選択制御端子は、クロック選択制御回路24の出力端子に接続されている。また、TFF11のQ出力端子はDFF10のD入力端子に接続されている。

【0044】

図示のPWM信号生成装置は、タイミング回路17及び18を有している。図5は図4に示すタイミング回路17及び18の一例を説明するための図である。そして、図5(a)はその構成の一例を示すブロック図であり、図5(b)は図5(a)に示すフルアダー7−1及び7−2の真理値表を示す図である。

【0045】

図5(a)において、タイミング回路17はPWM出力信号のタイミングを微小変調するための制御信号情報が入力される度に加算する。タイミング回路18は、この加算結果に応じてPWMOUTに出力されるべき出力信号を選択するための制御信号を生成する。さらに、タイミング回路17は、後述する補正情報を生成する。

【0046】

図4、図5(a)、及び図5(b)を参照して、タイミング回路18の制御信号出力端子、つまり、DFF2−8、7−7のQ出力端子は、それぞれOUTSEL1及びOUTSEL2端子2−10及び7−9を介して、クロック選択制御回路24(図4)に接続されている。DFF2−8及び7−7のクロック入力端子は、CP入力端子2−9を介してDFF4(図4)のQ出力端子に接続されている。

【0047】

また、DFF2−8のD入力端子は、フルアダー7−1のS出力端子に接続されている。そして、DFF7−7のD入力端子は、フルアダー7−2のS出力端子に接続されている。フルアダー7−1及び7−2は、2つのデータ入力端子A及びBとキャリー入力端子Ci、キャリー出力端子C、及び加算結果出力端子Sを有している。フルアダー7−1及び7−2の各々は、図5(b)の真理値表に示すように非同期に動作する。

【0048】

フルアダー7−1のCi入力端子は、接地(GND)されており、この結果、フルアダー7−1のCi入力端子には常にゼロが入力される。フルアダー7−1のA入力端子は入力端子2−5に接続され、そのS出力端子はDFF2−2のD入力端子に接続されている。そして、DFF2−2のQ出力端子がフルアダー7−1のB入力端子に接続されている。

【0049】

フルアダー7−1のC出力端子はフルアダー7−2のCi入力端子に接続されている。フルアダー7−2のA入力端子は入力端子7−8に接続され、そのS出力端子はDFF7−10のD入力端子に接続されている。そして、DFF7−10のQ出力端子がフルアダー7−2のB入力端子に接続されている。なお、フルアダー7−2のC出力端子はオープンとなっている。

【0050】

クロック入力端子2−18は、DFF2−2及び7−10のクロック入力端子に接続されている。DFF2−2のQバー出力端子は、2入力ANDゲート2−11の一方の入力端子に接続されている。DFF2−2のD入力端子は、2入力ORゲート7−3の一方の入力端子に接続されている。DFF7−10のD入力端子は、2入力ORゲート7−3の他方の入力端子に接続されている。2入力ORゲート7−3の出力端子は2入力ANDゲート7−4の一方の入力端子とインバータ2−14の入力端子とに接続されている。

【0051】

2入力ANDゲート7−4の出力端子は出力端子2−7に接続されている。また、ORゲート2−12の一方の入力端子がDFF7−10のQ出力端子に接続され、ORゲート2−12の他方の入力端子がDFF2−2のQ出力端子に接続されている。ORゲート2−12の出力端子はANDゲート2−13の一方の入力端子に接続され、ANDゲート2−13の他方の入力端子はインバータ2−14の出力端子に接続されている。ANDゲート2−13の出力端子は出力端子2−15に接続されている。また、ANDゲート7−4の他方の入力端子は、2−11の2入力ANDゲートの出力端子に接続され、2−11の他方の入力端子は、7−10のQバー出力端子に接続されている。

【0052】

出力端子2−7及び2−15は、それぞれ2入力ORゲート54(図4)の入力端子に接続され、出力端子2−15はさらにセレクタ15−3の制御信号入力端子に接続されている。2入力ORゲート54の出力端子は、セレクタ16の制御信号入力端子に接続されている。

【0053】

DFF4のQ出力端子はレジスタ2のクロック入力端子に接続されるとともに、DFF5のD入力端子に接続されている。DFF5のQ出力端子は、DFF10のクロック入力端子に接続されている。また、DFF5のQ出力端子はクロック入力端子2−18に接続されている。DFF5のクロック端子はclk_IN入力端子20に接続され、DFF5はこの信号の立下り毎にD入力の信号がQ出力端子に出力されるように、クロックの逆相でデータをラッチするように動作する。

【0054】

クロック微調制御回路23のオン幅制御情報出力端子3−14−1及びオフ幅制御情報制御信号出力端子3−14−2がそれぞれセレクタ8の入力端子に接続されている。そして、クロック微調制御回路23はセレクタ8の選択信号入力端子の情報によって各々2ビットからなる2つの制御信号のいずれかをセレクタ8の出力端子に接続する。セレクタ8の出力端子は、そのLSB側がタイミング回路17の入力端子2−5に接続され、MSB側が入力端子7−8に接続されている。

【0055】

基本波形データ入力用レジスタ6及び7はPWMを生成するためのレジスタであり、基本波形データ入力用レジスタ6及び7はセレクタ9の入力端子に接続されている。そして、基本波形データ入力用レジスタ6及び7はセレクタ9の選択信号入力端子によって、レジスタ6及び7のいずれか一方の信号を出力端子9に接続する。セレクタ8及び9の選択信号入力端子は、DFF10のQ出力端子に接続されている。アダー14は非同期に動作し、セレクタ9の出力端子に出力された信号とレジスタ2の出力端子に出力された信号とを加算して、アダー14の出力端子に出力する。

【0056】

アダー14の出力端子はセレクタ16の一方の入力端子群に接続されるとともに、アダー15の一方のバス入力端子に接続されている。アダー15の出力がセレクタ16の他方の入力端子群に接続されている。アダー15の他方のバス入力端子群には、セレクタ15−3の出力端子が接続され、セレクタ15−3の一方のセレクタ入力端子には、定数値”00000001B”15−2が加わり、その他方のセレクタ入力端子には定数値15−4の”11111111B”15−4が加わる。出力端子2−15が”1”のとき、定数値15−4で示す値がアダー15で加算される。2−15が“0”のとき、定数値15−2で示す値がアダー15で、アダー14での演算結果と加算される。すなわち、定数値15−2及び15−4のうち選択された定数値が、アダー14の出力値と非同期に加算演算されて、アダー15の出力端子に出力される。

【0057】

なお、上述の構成では、カウンタ又はレジスタがオーバーフローしてゼロにイニシャライズしても、持続的にPWMの信号を生成することができるカウンタ構成、レジスタ構成、及びアダー構成が必要である。原則的にバイナリーで演算する場合には、バイナリーカウンタを用いれば、最もシンプルな構成となるが、他の構成をもちいるようにしてもよい。

【0058】

セレクタ16の出力バスはレジスタ2の入力バスに接続されている。OR回路50、1ショット回路52、及び遅延バッファ53は、原クロックの2分周クロックまで生成できるタイミングを生成するために付加されている。OR回路50、1ショット回路52、及び遅延バッファ53による信号制御のため、DFF4及び5はRSTXがゼロの際に初期化される。すなわち、DFF4及び5のQ出力端子がゼロとなるように、OR回路50の一端とインバータ51とを介してRSTXからの信号が入力される。

【0059】

つまり、RSTXがインバータ51の入力端子に接続され、インバータ51の出力端子がOR回路50の一方の入力端子に接続され、OR回路50の他方の入力端子は1ショット回路52の出力端子に接続されている。1ショット回路52の入力端子は遅延バッファ53の出力端子に接続され、遅延バッファ53の入力端子はDFF5のQ出力端子に接続されている。また、OR回路50の出力端子はDFF4及び5のDFFのリセット端子に接続されている。

【0060】

図6〜図8は、図4に示すPWM信号生成装置の動作を説明するためのタイムチャートである。

【0061】

図6〜図8に示すタイムチャートでは、説明の便宜上N=8とした例が示されている。また、図4に示すPWM信号生成装置では、リセット回路が示されていないが、リセットの際カウンタ1及びレジスタ6及び7を除いて全てのDFFのQ出力端子の値は非同期にゼロに初期化されるものとする。また、レジスタ2もゼロに初期化され、TFF11及び12のQ出力端子もゼロに初期化される。但し、レジスタ6、7、15−2、及び15−4は、リセットの際においても変化しない固定値が予め与えられるレジスタとする。

【0062】

N=8であるため、カウンタ1及び、レジスタ2のビット長は8ビットであり、カウンタ1はリセットの際にそのQ出力が”FF”にリセットされるものとする。

【0063】

ここで、リセット解除後のPWM信号生成装置の動作について説明する。なお、予めレジスタ6には”2H”の値が、レジスタ7にも”2H”の値が設定されているものとする。

【0064】

図4及び図6〜図8を参照して、カウンタ1はCLK_IN20のクロックの立ち上がり毎に1カウントアップして、リセット解除後1クロックが立ち上がるとカウンタ1は”FF”から1カウントアップして”00”となる。その結果、カウンタ1の値(カウント値)はレジスタ2の値と同一の値となる(リセットでレジスタは”00”に初期化されている)。

【0065】

これによって、当該タイミングにおいてコンパレータ3の出力端子の値が”1”となり、その次のクロックの立下りで、TFF12のQ出力端子が”1”となる。さらに、その次のクロックの立上がりで、DFF4のQ出力端子に”1”がセットされるとともに、TFF11のQ出力端子も”1”にセットされる。

【0066】

従って、レジスタ2にオンタイムレジスタ7のLSB1ビットを除く全てのビット情報とレジスタ2のレジスタ値”0”との加算結果がラッチされる。ここでは、レジスタ2に”2H#の値が設定されることになる(つまり、オンタイムレジスタ7の値である”2H”が設定される)。

【0067】

リセットの際、レジスタ10のQ出力端子は”0”に初期化されており、当該条件では,ONレジスタ7のデータ及び下位ビット制御回路23の初期出力値が、セレクタ9及び8を介してアダー14とタイミング回路17及び18の入力データとして設定される。

【0068】

後述するように、下位ビット制御回路23の初期値は”0”であるから、図5(a)に示す入力端子2−5及び7−8には、値”0”が印加される。DFF2−2及び7−10は予めリセットされているので、そのQ出力端子は”0”である。このため、フルアダー7−1及び7−2のS出力端子には”0”が出力される。従って、DFF4のQ出力端子に”1”がセットされたタイミングで、フルアダー7−1のS出力端子の出力信号”0”がDFF2−8にラッチされ、フルアダー7−2のS出力端子の出力信号”0”がDFF7−7にラッチされる。

【0069】

セレクタ13は、下位ビット制御回路23及びクロック選択制御回路24の初期化よってTFF11の出力を出力端子21に出力するモードが設定されている。同時に当該タイミングにおいては、タイミング回路17の出力端子2−15及び2−7は”0”となり、セレクタ16はアダー14の出力端子がレジスタ2に接続されるモードとなっている。

【0070】

カウンタ1は1カウントアップされて、コンパレータ3の出力端子が”0”となる。次にCLK_IN20に入力されるクロックの立下りで、DFF4のQ出力端子の”1”が、DFF5のQ出力端子にラッチされる。その結果、DFF10のQ出力端子にTFF11のQ出力端子にセットされた”1”がラッチされ、セレクタ8及び9の選択制御端子における選択情報が”1”から”0”に変更される。そしてセレクタ8及び9の出力端子には、オフタイムレジスタ6のデータ及びこれに対応する下位ビット制御情報がそれぞれ下位ビット制御回路23及オフタイムレジスタ6から出力される。

【0071】

つまり、セレクタ9の出力端子からの出力信号は、オンタイムレジスタ7のデータからオフタイムレジスタ6のデータに切り替えられ、”2H”から”2H”に変化する(同一のデータである)。また、セレクタ8の出力は下位ビット制御回路23のオンタイムのビットデータからオフタイムのLSBのビットデータに替わる。

【0072】

このようにして、PWM信号生成装置は図6〜図8に示すタイミングで動作して、下位ビット制御回路23がその制御信号を図6〜図8に示すタイミングで出力する。これによって、図6〜図8に示すオンタイムでのみ微小時間δで変位するパルスを生成することができる。

【0073】

図6〜図8に示すタイムチャートに応じて動作させると、上述のパルス信号(クロック信号)を生成することができる。その際、微小時間δの信号を付加するために、タイミング回路18が、それぞれタイミングの異なるパルスを生成するTFF11、12、31、32、33、及び34の出力を切り替える。

【0074】

また、タイミング回路17は、パルス信号に微小時間δの信号変化を実現するために、レジスタ6及び7のレジスタ値に応じて生成される基本パルス信号に係る情報および23で生成される加減算情報を必要に応じて加算又は減算(補数+1を加算)する。すなわち、23で生成された加算値、減算値を7−1,7−2のフルアダーで加算して、必要な制御情報を生成する。この7−1,7−2のフルアダー演算は、下位の微小PWM変動用bitの演算用の回路で、δの値を1増分させるためには1を加算し、δの値を1減算させるためには、1の補数+1の値を加算させる。

【0075】

上位のPWM回路への桁上げ、桁下げは、15(桁下げ)のアダーが実施する。上位のPWM回路への桁上げの場合には、定数値15−2がアダー15に与えられ、上位のPWM回路への桁下げは、定数値15−4がアダー15に与えられる。そして、定数値15−2又は15−4がアダー14の出力結果と加算されるように、タイミング回路17は制御信号2−7及び2−15を制御する(そのために、17のタイミング回路は、16のセレクタと、15−3のセレクタを切り替え、14のアダーの加算結果に15−2の固定値を加算するか、15−4の固定値を加算するか、または加算しないか、条件を判別して制御する)。

【0076】

DFF5のQ出力信号が遅延バッファ53及び1ショット回路52を介してDFF4及び5に与えられ、DFF4及び5をリセットするので,DFF4及び5のQ出力端子から出力される制御信号が基本クロックの1周期内で初期化される。その結果、図4に示すPWM信号生成装置では、基本クロックの2分周の信号まで容易に微小時間δの変調をかけた信号を生成することができる。

【0077】

タイミング回路18は、下位ビット制御回路23で下位ビット情報が生成される都度、それまでに加算された結果に対してフルアダーで加算を行い、その加算結果をクロック選択制御回路24に与える。これによって、セレクタ13が制御されて、微小時間δを加味したパルス信号が出力端子21に出力制御される。

【0078】

なお、タイミング回路17は、下位ビット制御回路23で下位ビット情報が生成される都度、それまでに加算された結果と下位ビット情報とを比較する。そして、それまでに加算された結果が”0”で、次に下位ビット制御回路23で生成された下位ビット情報を加えた結果が”1”以上であると、タイミング回路17は出力端子2−7に”1”をたて、アダー14の出力結果に”1”を加えた値をレジスタ2に設定する。また、それまでに加算された結果が”1”以上で、次に下位ビット制御回路23で生成される下位ビット情報を加えた結果が”0”であると、タイミング回路17は出力端子2−15に”1”をたて、アダー14の出力結果が1減算された値をレジスタ2に設定する。

【0079】

ここで、図4に示す下位ビット制御回路23についてさらに説明する。

【0080】

図9は図4に示す下位ビット制御回路23の構成を示すブロック図である。

【0081】

図9を参照すると、下位ビット制御回路23は、(X+1)ビットのアップダウンカウンタ3−1(Xは0以上の整数)を有している。アップダウンカウンタ3−1のクロック入力端子はゲート3−9を通じて入力端子3−12の信号が入力され、この入力端子3−12は図4に示すDFF5のQ出力端子に接続されている。

【0082】

本実施形態では、X=0の場合を示しているが,一般的には周波数の微小変調のδに応じて、Xは決定される。例えば,δが2(±2δの変調の場合)のときX=1であればよく、通常用いる範囲のX値のMAX値、例えば、7等の値にしておけばよい。

【0083】

CPUバス入力端子3−11は、MAX値レジスタ3−2、MIN値レジスタ3−3、及び出力モード設定3−15に接続され、このCPUバス入力端子3−11は外部のCPUバスに接続される。そして、外部のCPUは当該バスを用いて各レジスタに制御データを書き込む。

【0084】

MAX値レジスタ3−2の制御信号出力端子は、MAX値検知回路3−5の一方の入力端子に接続され、MIN値レジスタ3−3の制御信号出力端子はMIN値検知回路3−4の一方の入力端子に接続される。MAX値検知回路3−5及びMIN値検知回路3−4の各々は、例えば、デジタルコンパレータで構成される。そして、MAX値検知回路3−5及びMIN値検知回路3−4の他方の入力端子には、MAX値レジスタ3−2及びMIN値レジスタ3−3のレジスタの情報に対応するアップダウンカウンタ3−1の出力端子が、バス3−17を介して接続される。さらに、バス3−17は、出力データ設定回路3−10のデータ入力端子に接続される。

【0085】

MIN値検知回路3−4及びMAX値検知回路3―5の検出結果を出力する出力端子は、U/D制御回路3−6の制御回路の入力端子に接続される。U/D制御回路3−6には、さらに出力モード設定レジスタ3−15の制御データ出力端子が接続される。そして、U/D制御回路3−6のU/D制御信号出力端子がアップダウンカウンタ3−1のU/D制御信号入力端子及びU/D繰り返し回数検知回路3−7に信号線3−20を介して接続される。

【0086】

U/D繰り返し回数検知回路3−7の出力端子は、偶奇判定回路3−8の入力端子に接続され、偶奇判定回路3−8の出力端子は出力データ設定回路3−10の入力端子に接続される。そして、出力データ設定回路3−10の制御信号入力端子には、出力モード設定レジスタ3−15の制御データ出力端子が接続され、さらに、出力データ設定回路3−10にはバス3−17が接続される。

【0087】

加えて、出力データ設定回路3−10のオン幅制御情報出力端子が信号出力端子3−14に接続される。

【0088】

アップダウンカウンタ3−1のクロック信号入力端子には、2入力ANDゲート3−9の出力端子が接続され、このANDゲート3−9の一方の入力端子には、信号入力端子3−12が接続され、他方の入力端子には、U/D制御回路3−6の制御信号出力端子が接続される。

【0089】

また、U/D制御回路3−6において、TFF11のQ出力がその制御信号入力端子3−21に入力される。さらに、TFF11のQ出力は、出力データ設定回路3−10に制御信号として与えられる。

【0090】

続いて、図9に示す下位ビット制御回路23の動作について説明する。まず、外部のCPUがCPUバス入力端子3−11を介して制御情報をMAX値レジスタ3−2、MIN値レジスタ3−3、及び出力モード設定レジスタ3−15に書き込む。例えば、MAX値レジスタ3−2には制御情報として”1”が書き込まれ、MIN値レジスタ3−3には制御情報として”0”が書き込まれる。出力モード設定レジスタ3−15には、PWMの微小増減をONタイムでのみ実行するパラメータ”01”が書き込まれる。

【0091】

図示の下位ビット制御回路は、図示しないリセット回路を有しており,このリセット回路によってアップダウンカウンタ3−1はイニシャル時(パワーオンリセット時)”0”にリセットされる。また、U/D制御回路3−6のU/D制御信号出力端子には、アップダウンカウンタ3−1がクロック毎にアップするカウント値の初期値”1”がリセット時に設定されているものとする。さらに、U/D繰り返し回数検知回路3−7のカウント値も”0”に初期化されており、出力データ設定回路3―10の出力端子には、初期値”0”が設定されている。ここでは、アップダウンカウンタ3−1の出力信号の初期値0がそのまま出力データ設定回路3−10を通じて、その信号出力端子3−14に出力されるように動作する。

【0092】

アップダウンカウンタ3−1、MIN値検知回路3−4、MAX値検知回路3−5、及びU/D制御回路3−6によって微小変位δの値が決定される。具体的には、アップダウンカウンタ3−1は、U/D制御回路3−6によって制御され、DFF5のQ出力を基準として、MIN値検知回路3−4のMIN値とMAX値検知回路3−5のMAX値との間をアップ及びダウンする。

【0093】

図示の例では、アップダウンカウンタ3−1は”0101”の変化を繰り返す。U/D繰り返し回数検知回路3−7は、この”01”の繰り返し回数を検知する。U/D繰り返し回数検知回路3−7による検知結果は、偶奇判定回路3−8によって偶奇を判定される。そして、偶奇判定回路3−8の判定結果が出力データ設定回路3−10に設定される。

【0094】

出力データ設定回路3−10は、出力モード設定レジスタ3−15に設定されている値(モード)、アップダウンカウンタ3−1の出力値、及び偶奇判定回路3−8の出力値に応じて信号出力端子3−14に出力する信号を制御する。

【0095】

図10は、図9に示す出力モード設定レジスタ3−15のレジスタ値に応じた信号出力を説明するための図である。

【0096】

図11は、図9に示す出力モード設定レジスタ3−15のレジスタ値が”01”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【0097】

図12は、図9に示す出力モード設定レジスタ3−15のレジスタ値が”02”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【0098】

図13は、図9に示す出力モード設定レジスタ3−15のレジスタ値が”03”モードである際の下位ビット制御回路の動作を説明するためのタイミングチャートである。

【0099】

いま、出力モード設定レジスタ3−15の設定モードが”01”のとき、U/D制御回路3−6はTFF11のQ出力が”0”の際にアップダウンカウンタ3−1にクロックが印加しないように制御する。つまり、U/D制御回路3−6はANDゲート3−9においてアップダウンカウンタ3−1への信号入力を禁止する。そして、U/D制御回路3−6はU/D信号を当該タイミングでMIN値検知回路3−4及びMAX値検知回路3−5の比較結果に応じてDFF5の立ち上がりでラッチして、信号線3−20に送出する。

【0100】

U/D繰り返し回数検知回路3−7は信号線3−20の信号をクロックとして、当該入力クロックをTFFによって計数する。偶奇判定回路3−8は、U/D繰り返し回数検知回路3−7の検知結果が”1”であると、繰り返しが偶数番目であると判定する。そして、偶奇判定回路3−8は、信号出力端子3−14に出力する出力データを減算するためのデータを選択する。一方、U/D繰り返し回数検知回路3−7の検知結果が”0”であると、偶奇判定回路3−8は繰り返しが奇数番目であると判定する。そして、偶奇判定回路3−8は、信号出力端子3−14に出力する出力データを加算するためのデータを選択する。

【0101】

出力データ設定回路3−10は、出力モード設定レジスタ3−15の設定モードに応じて出力データを制御する。そして、出力データ設定回路3−10はアップダウンカウンタ3−1のカウンタ出力値に応じて、TFF11のQ出力の信号基準で設定モードを加味した出力データを信号出力端子3−14に出力する。

【0102】

設定モードが”3”である場合には、出力データ設定回路3−10を除いて、設定モード”1”と同じ制御タイミングで下位ビット制御回路23は動作する。そして、設定モード”1”である場合に信号出力端子3−14に現われるON下位出力値が、TFF11のQ出力=1となるタイミングでラッチされ、次のOFF下位出力値とされる。

【0103】

但し、δにおいて2以上の増分がある場合、その増分に対応したタイミングが必要となる。このため、遅延バッファの増設、その遅延クロックによる出力信号を生成するDFFの増設を行う必要がある。そして、増設したDFFを選択して、信号出力するように、セレクタ13、セレクタ選択回路24、及びタイミング回路17及び18を拡張する必要がある。

【0104】

図14は、図4に示すクロック選択制御回路24の動作の一例を説明するための図である。そして、図14(a)は図4に示すクロック選択制御回路24の構成の一例を示すブロック図であり、図14(b)は図4に示すセレクタ13による選択動作の一例を示す図である。

【0105】

図4及び図14を参照すると、図4に示すクロック選択制御回路24は、例えば、デコーダ回路であり、2つの入力端子の組み合わせに応じてクロック信号を出力してセレクタ13を制御する。つまり、クロック選択制御回路24はタイミング回路18の2ビット出力端子OUTSEL1及びOUTSEL2に応じてセレクタ13を制御する。具体的には、クロック選択制御回路24はセレクタ13を制御してTFF11のQ出力、TFF12のQ出力、TFF31のQ出力、又はTFF32のQ出力をPWMOUT21に出力する。

【0106】

図14(a)に示すように、クロック選択制御回路14は2入力ANDゲート11−1〜11−4及びインバータ11−5及び11−6を有している。そして、タイミング回路18の出力端子OUTSEL1に接続される入力端子INSEL1がANDゲート11−2及び11−4の一方の入力端子に接続されるとともに、インバータ11−5の入力端子に接続される。インバータ11−5の出力端子は、ANDゲート11−3及び11−1の一方の入力端子に接続される。

【0107】

タイミング回路18の出力端子OUTSEL2に接続される入力端子INSEL2がANDゲート11−3及び11−4の他方の入力端子に接続されるとともに、インバータ11−6の入力端子に接続される。インバータ11−6の出力端子はANDゲート11−1及び11−2の他方の入力端子に接続される。

【0108】

図14(a)に示す構成のクロック選択制御回路24では、INSEL2及び1の入力値が”00”、”01”、”10”、及び”11”の組み合わせに応じて出力が変化する。例えば、入力値が”00”の際には、ANDゲート11−1の出力のみが”1”となる。入力値が”01”の際には、ANDゲート11−2の出力のみが”1”となる。入力値が”10”の際には、ANDゲート11−3の出力のみが”1”となる。そして、入力値が”11”の際には、ANDゲート11−4の出力のみが”1”となる。

【0109】

その結果、図14(b)に示すように、INSEL2及び1の入力値が”00”の際には、PWNOUT21にはTFF11のQ出力が出力され、INSEL2及び1の入力値が”10”の際には、PWMOUT21にはTFF12のQ出力が出力される。また、INSEL2及び1の入力値が”01”の際には、PWMOUT21にはTFF31のQ出力が出力される。そして、INSEL2及び1の入力値が”11”の際には、PWMOUT21にはTFF32のQ出力が出力される。

【0110】

なお、TFF33及び34のQ出力を選択するSEL05及びSEL06は、図示の例では、GNDに接続されて選択されないように構成されている。

【0111】

図15は、図4に示す1ショット回路52の一例を示すブロック図である。

【0112】

図15において、入力端子INは、2入力ANDゲート11−7の一方の入力端子に接続されるとともに、遅延量の大きなインバータ11−8の入力端子に接続される。そして、インバータ11−8の出力端子はANDゲート11−7の他方の入力端子に接続される。ANDゲート11−7の出力端子は1ショット回路の出力端子である1SHOT_OUTに接続される。

【0113】

入力端子INが”0”であると、インバータ11−8の出力は”1”となる。次に、入力端子INが”0”から”1”に遷移すると、ANDゲート11−7の一方の入力端子は”1”となる。一方、インバータ11−8の出力が接続されているANDゲート11−7の他方の端子は”1”となっているが,インバータ11−8の遅延時間後に”0”となる。このため、ANDゲート11−7の出力は、インバータ11−8の遅延時間分だけ”1”となって、1SHOT_OUTからは1ショットパルスが出力される。

【0114】

なお、インバータ11−8は、図4に示すバッファ53と同等の遅延時間を有しており、これによってDFF4及び5を確実にリセットする。DFF5がリセットされても、1ショット回路52の出力する1ショットパルスを確実に出力するためバッファ53が挿入されている。

【0115】

図16は、図4に示すクロック選択制御回路24の動作の他の例を説明するための図である。そして、図16(a)は図4に示すクロック選択制御回路24の構成の他の例を示すブロック図であり、図16(b)は図4に示すセレクタ13による選択動作の他の例を示す図である。

【0116】

なお、図16(a)において、図14(a)に示すクロック選択制御回路24と同一の構成要素については同一の参照番号を付し、説明を省略する。

【0117】

図示のクロック選択制御回路24は、ANDゲート11−1〜11−4とインバータ11−5〜11−6に加えて、レジスタ(REG)12−1、セレクタ12−2、及び複合ゲート(AND・ORゲート)12−3〜12−8を有している。

【0118】

このクロック選択制御回路24では、ANDゲート11−1〜11−4の出力の接続をレジスタ12−1、セレクタ12−1、及び複合ゲート12−3〜12−8によって切り替える。

【0119】

図示のように、複合ゲート12−3〜12−8においてANDゲートの一方の入力端子はインバータを介してレジスタ12−1に接続されている。また、複合ゲート12−3〜12−8においてANDゲートの他方の入力端子はそれぞれANDゲート11−4の出力端子、ANDゲート11−3の出力端子、GND、ANDゲート11−2の出力端子、GND、及びAND11−1の出力端子に接続されている。

【0120】

レジスタ12−1はその入力バスがREGIN端子に接続され、外部CPUによってデータが設定される。レジスタ12−1のデータ出力端子がセレクタ12−2の制御信号入力端子に接続される。

【0121】

セレクタ12−2はその制御入力端子が”1”であると、すなわち、レジスタ12−1のQ出力が1のとき、複合ゲート12−3〜12−8のORゲートの入力端子に図16(a)の回路に明示されるセレクタ12−2の入力端子に加わる信号が与えられ、SEL01〜SEL06に出力されることになる。つまり、この条件の場合には、複合ゲート12−3〜12−8のANDゲートの一方の入力端子が”0”となるように、セレクタ12−2の制御入力端子に加わる信号と逆相の信号が加わってセレクタ12−2から出力される信号がそのままSEL01〜SEL06に出力される。

【0122】

セレクタ12−2の制御入力端子が”0”であると、すなわち、レジスタ12−1の出力が0のとき、セレクタ12−2の出力端子には、図示されていないセレクタ12−2の他方のGNDに接地された入力端子が接続され、全て”0”が出力される。複合ゲート12−3〜12−8のORゲートの一方の入力端子は、全て”0”となる。一方、ORゲートの他方の入力端子は、ANDゲートの出力端子に接続されているから、当該タイミングで一方の入力端子が全て”1”となり、他方の入力端子の入力信号が直接SEL01〜SEL06に出力される。

【0123】

前述のように、レジスタ12−1は、外部CPUにおいてそのレジスタ値が制御可能となっており、外部CPUは必要に応じてレジスタ12−1のレジスタ値を”1”又は”0”に切り替える。レジスタ12−1のレジスタ値が”1”の場合には、上述した動作と同様の動作が行われる。

【0124】

レジスタ12−1のレジスタ値が”0”の場合には、INSEL1及びINSEL2の値の組み合わせによってPWMOUT21(図4)に出力される出力信号の選択が、レジスタ12−1のレジスタ値が”1”のときと変化する。INSEL1及び2がそれぞれ”0”及び”1”であると、TFF31のQ出力がTFF12のQ出力に変更されて出力される。INSEL1及び2がそれぞれ”1”及び”0”であると、TFF2のQ出力がTFF33のQ出力に変更されて出力される。また、INSEL1及び2がそれぞれ”1”及び”1”の場合には、TFF32のQ出力がTFF34のQ出力に変更されて出力される。これによって、出力信号の微変調特性を変更することができる。

【0125】

図17は、図4に示すPWM信号生成装置を用いた通信装置の一例を示すブロック図である。

【0126】

図17において、図示の通信装置は図4で説明したPWM信号生成装置13−2及び13−3を有している。そして、これらPWM信号生成装置13−2及び13−3はCPU13−1に接続されるとともに、調歩同期方式通信モジュール13−4及び13−5に接続されている。CPU13−1とPWM信号生成装置13−2及び13−3には外部クロック端子13−6からクロック信号端子13−16を介して外部クロックが与えられる。

【0127】

CPU13−1のバス信号線は、バス13−13を介してPWM信号生成装置13−2〜13−3及び通信モジュール13−4〜13−5に接続されており、CPU13−1はこのバス13−13を介してPWM信号生成装置13−2〜13−3及び通信モジュール13−4〜13−5に備えられた制御レジスタにデータを設定する。CPU13−1は通信モジュール13−4及び13−5に対してその他の通信用データも設定する。

【0128】

CPU13−1はバス13−13を介してPWM信号生成装置13−2〜13−3及び通信モジュール13−4〜13−5に初期化データを設定する。続いて、CPU13−1はバス13−13を介してPWM信号生成装置13−2及び13−3に制御データを書き込む。

【0129】

例えば,CPU13−1は通信モジュール13−4に対して基本クロックの4分周のクロックが信号線13−14を介して供給されるように、PWM信号生成装置13−2のオフタイムレジスタ6及びオンタイムレジスタ7の値を書き替える。また、CPU13−1は通信モジュール13−5に対して8分周の基本クロックが信号線13−15の信号線を介して供給されるように、PWM信号生成装置13−3のオフタイムレジスタ6及びオンタイムレジスタ7の値を書き替える。

【0130】

4分周の場合には、オフタイムレジスタ6及びオンタイムレジスタ7の各々には、”10H”が書き込まれる。8分周の場合には、オフタイムレジスタ6及びオンタイムレジスタ7の各々には、”110H”が書き込まれる。さらに、PWM信号生成装置13−2及び13−3において、下位ビット制御回路23のレジスタにそれぞれ異なったレジスタ値が書き込まれる。

【0131】

例えば、PWM信号生成装置13−2においてMAX値レジスタ3−2のレジスタ値及びMIN値レジスタ3−3のレジスタ値がそれぞれ”1”及び”0”を設定し、PWM信号生成装置13−3においてはMAX値レジスタ3−2のレジスタ値及びMIN値レジスタ3−3のレジスタ値をそれぞれ”2”及び”1”と設定することによって、通信モジュール13−4及び13−5のクロックの微調周期変動範囲を互いに変えることができる。なお、ONタイムが固定で、オフタイムを変調することが有利である場合には、出力モード設定レジスタ3−15には”01”が書き込まれる。

【0132】

このようにして、PWM信号生成装置13−2及び13−3の設定を行えば、PWM信号生成装置13−2は、信号線13−14を通じて、PWM信号生成装置13−3は信号線13−15を通じて通信モジュール13−4及び13−5のクロックを互いに異なった範囲のパルス幅変調で実現することができる。また、変化範囲についてノイズスペクトル的に問題が生じる場合には、クロック選択制御回路24のレジスタの設定を変更すれば、パルス幅の変調のモードを変えることができる。

【0133】

上述のように、本実施の形態によるPWM信号生成装置では、基準クロックを倍以上の周波数にすることなく、基準クロックの1周期以下の範囲でクロックに微小時間変調をかけることができる。そして、PLLを用いることなく、しかも高周波クロックを用いる必要がなく、回路規模を小さくしてSSCGを実現することができる。

【0134】

加えて、複数通信を同時に実行するASIC等において、互いに異なるSSCGを用いてクロックを同時に複数生成して、ノイズを削減することができる。

【0135】

以上、本発明について実施の形態に基づいて説明したが、本発明は、これらの実施の形態に限定されるものではなく、この発明の要旨を逸脱しない範囲の様々な形態も本発明に含まれる。

【0136】

例えば、本発明は、以下の処理を実行することによっても実現される。即ち、上述した実施形態の機能を実現するソフトウェア(プログラム)を、ネットワーク又は各種記録媒体を介してシステム或いは装置に供給し、そのシステム或いは装置のコンピュータ(またはCPUやMPU等)がプログラムを読み出して実行する処理である。

【符号の説明】

【0137】

1 カウンタ

2,6,7 レジスタ

3 コンパレータ

4,5,10 DFF(Dタイプフリップフロップ)

8,9,13,15−3,16 セレクタ

11,12,31,32,33,34 TFF((Tタイプフリップフロップ)

14,15 アダー

17,18 タイミング回路

23 下位ビット制御回路

24 クロック選択制御回路

【特許請求の範囲】

【請求項1】

基準クロックに応じて動作してPWM信号を生成するPWM信号生成装置において、

前記基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成するクロック生成手段と、

前記基準クロックに応じて前記変動クロックを第1のPWM信号として出力する第1のPWM出力制御手段と、

前記基準クロックを所定の時間遅延させた遅延クロックに応じて前記変動クロックを第2のPWM信号として出力する第2のPWM出力制御手段と、

前記第1及び前記第2のPWM信号を選択的に前記PWM信号として出力する選択手段とを有することを特徴とするPWM信号生成装置。

【請求項2】

前記クロック生成手段は、前記基準クロックのパルス数をカウントするカウント手段と、

パルス幅変調におけるそのパルス幅の期間を示すパルス幅データと前記カウント手段によるカウント値とを比較してその比較結果に応じて前記変動クロックを出力する比較手段とを有することを特徴とする請求項1に記載のPWM信号生成装置。

【請求項3】

前記第1のPWM出力制御手段は前記基準クロックで動作するTタイプフリップフロップを有し、

前記第2のPWM出力制御手段は前記遅延クロックで動作するTタイプフリップフロップを有することを特徴とする請求項1又は2記載のPWM信号生成装置。

【請求項4】

前記パルス幅データである前記クロック信号のオン期間を示すオンタイム情報と前記クロック信号のオフ期間を示すオフタイム情報に応じて前記選択手段を制御して、該選択手段に前記第1及び前記第2のPWM信号を選択的に前記PWM信号として出力させる制御手段を有することを特徴とする請求項2記載のPWM信号生成装置。

【請求項5】

前記制御手段は前記オンタイム情報及び前記オフタイム情報の予め規定されたビットが予め定められた第1の値であると前記選択手段を制御して、前記第1のPWM信号を選択させることを特徴とする請求項4記載のPWM信号生成装置。

【請求項6】

前記制御手段は前記オンタイム情報及び前記オフタイム情報の予め規定されたビットと前記レジスタ値とを加算した加算結果が予め定められた第2の値であると前記選択手段を制御して、前記第2のPWM信号を選択させることを特徴とする請求項4又は5記載のPWM信号生成装置。

【請求項1】

基準クロックに応じて動作してPWM信号を生成するPWM信号生成装置において、

前記基準クロックの周波数をその一周期未満の時間で変動させた変動クロックを生成するクロック生成手段と、

前記基準クロックに応じて前記変動クロックを第1のPWM信号として出力する第1のPWM出力制御手段と、

前記基準クロックを所定の時間遅延させた遅延クロックに応じて前記変動クロックを第2のPWM信号として出力する第2のPWM出力制御手段と、

前記第1及び前記第2のPWM信号を選択的に前記PWM信号として出力する選択手段とを有することを特徴とするPWM信号生成装置。

【請求項2】

前記クロック生成手段は、前記基準クロックのパルス数をカウントするカウント手段と、

パルス幅変調におけるそのパルス幅の期間を示すパルス幅データと前記カウント手段によるカウント値とを比較してその比較結果に応じて前記変動クロックを出力する比較手段とを有することを特徴とする請求項1に記載のPWM信号生成装置。

【請求項3】

前記第1のPWM出力制御手段は前記基準クロックで動作するTタイプフリップフロップを有し、

前記第2のPWM出力制御手段は前記遅延クロックで動作するTタイプフリップフロップを有することを特徴とする請求項1又は2記載のPWM信号生成装置。

【請求項4】

前記パルス幅データである前記クロック信号のオン期間を示すオンタイム情報と前記クロック信号のオフ期間を示すオフタイム情報に応じて前記選択手段を制御して、該選択手段に前記第1及び前記第2のPWM信号を選択的に前記PWM信号として出力させる制御手段を有することを特徴とする請求項2記載のPWM信号生成装置。

【請求項5】

前記制御手段は前記オンタイム情報及び前記オフタイム情報の予め規定されたビットが予め定められた第1の値であると前記選択手段を制御して、前記第1のPWM信号を選択させることを特徴とする請求項4記載のPWM信号生成装置。

【請求項6】

前記制御手段は前記オンタイム情報及び前記オフタイム情報の予め規定されたビットと前記レジスタ値とを加算した加算結果が予め定められた第2の値であると前記選択手段を制御して、前記第2のPWM信号を選択させることを特徴とする請求項4又は5記載のPWM信号生成装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【公開番号】特開2012−227693(P2012−227693A)

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願番号】特願2011−92970(P2011−92970)

【出願日】平成23年4月19日(2011.4.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

【公開日】平成24年11月15日(2012.11.15)

【国際特許分類】

【出願日】平成23年4月19日(2011.4.19)

【出願人】(000001007)キヤノン株式会社 (59,756)

【Fターム(参考)】

[ Back to top ]