SOA−PLCハイブリッド集積偏波ダイバーシティ回路およびその製造方法

【課題】容易に他のデバイスに組み込むことが可能なSOA−PLCハイブリッド集積偏波ダイバーシティ回路を提供する。

【解決手段】互いに導波路を結合したPLC−PBSチップとSOA−COSとを備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を提供する。PLC−PBSチップは、第1および第2の光導波路と、マッハツェンダー干渉計回路と、TMモードの光が伝播する第1の石英系光導波路中に形成された半波長板とを含む。SOA−COSは、第1の光導波路に接続された第3の光導波路と、第2の光導波路に接続された第4の光導波路と、少なくとも一方の第3および第4の光導波路に形成されたSOAとを含む。第3と第4の光導波路のそれぞれ第1および第2の光導波路と接続しないもう一端同士は、Uターン部光導波路で接続される。

【解決手段】互いに導波路を結合したPLC−PBSチップとSOA−COSとを備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を提供する。PLC−PBSチップは、第1および第2の光導波路と、マッハツェンダー干渉計回路と、TMモードの光が伝播する第1の石英系光導波路中に形成された半波長板とを含む。SOA−COSは、第1の光導波路に接続された第3の光導波路と、第2の光導波路に接続された第4の光導波路と、少なくとも一方の第3および第4の光導波路に形成されたSOAとを含む。第3と第4の光導波路のそれぞれ第1および第2の光導波路と接続しないもう一端同士は、Uターン部光導波路で接続される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、平面光波回路(PLC)としての偏波ビームスプリッタ(PBS)および半導体光増幅器(SOA)を備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路およびその製造方法に関する。

【背景技術】

【0002】

近年、光通信ネットワークにおけるデータ量の増加にともない、コンパクトで低コストである光学素子が要求される。従来の個別の光学部品を組み合わせる技術に代わり、フォトニック集積回路(PIC)技術に基づく光導波路デバイス技術へとトレンドが移行しつつある。

【0003】

光通信ネットワークにおいて、光導波路デバイスにおける偏波依存性は、実用的に好ましくは、0.1dB以下が要求される。偏波ダイバーシティ回路は、光学デバイスにおける偏波依存性の問題を解消するために使用される。

【0004】

非特許文献1は、図14のように、それぞれ空間的に分離した個別の光学部品である、3つのポート1401〜1403を有するサーキュレータ1409、レンズ1404、偏波ビームスプリッタとしてのハーフミラー1405、半波長板1406、ミラー1407、およびSOA1408を使用した偏波ダイバーシティ回路によりSOAの偏波依存利得(PDG)を解消するための偏波無依存SOAモジュールを開示する。

【先行技術文献】

【特許文献】

【0005】

【非特許文献1】K. Morito and S. Tanaka, ”Record High Saturation Power (+22dBm) and Low Noise Figure (5.7dB) Polarization-Insensitive SOA Module”, IEEE PHOTONICS TECHNOLOGY LETTERS, 17, 6, 1298-1300, (2005)

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、非特許文献1に開示の偏波無依存SOAモジュールは、空間的に分離した個別の光学部品を使用するため、モジュール全体としてサイズが大きくなってしまう。また、非特許文献1に開示の該モジュールでは、ハーフミラー1405やミラー1407等の光学部品が用いられるため、図14に示される該モジュールを形成するには、使用者によるそれぞれの光学部品間の光軸調整が必要であり、非常に手間がかかる。したがって、該モジュールを他のデバイスに組み込む等の応用が難しい。そのため、非特許文献1に開示の該モジュールを商業的に利用することは難しいと考えられる。

【0007】

本発明の目的は、従来のモジュールに比べモジュール(回路)のサイズを低減し、容易に他のデバイスに組み込むことが可能であるPLC−SOAハイブリッド集積偏波ダイバーシティ回路を提供することである。

【課題を解決するための手段】

【0008】

本発明は、互いに導波路を結合したPLC−PBSチップとSOA−COSとを備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路であって、該PLC−PBSチップは、第1および第2の光導波路と、入力された光をTMモードの光およびTEモードの光へ分割し、該分割されたTMモードの光を該第1の光導波路へ出力し、該分割されたTEモードの光を該第2の光導波路へ出力するマッハツェンダー干渉計回路と、該TMモードの光が伝播する第1の石英系光導波路中に形成された偏波回転機構とを含み、該SOA−COSは、該第1の光導波路に接続された第3の光導波路と、該第2の光導波路に接続された第4の光導波路と、少なくとも一方の該第3および第4の光導波路に形成されたSOAとを含み、該第3の光導波路と、該第4の光導波路のそれぞれ該第1の光導波路および該第2の光導波路と接続しないもう一端同士は、Uターン部光導波路で接続されていることを特徴とするSOA−PLCハイブリッド集積偏波ダイバーシティ回路を提供する。

【発明の効果】

【0009】

本発明にかかるPLC−SOAハイブリッド集積偏波ダイバーシティ回路は、従来のモジュールに比べモジュール(回路)のサイズを低減することができ、容易に他のデバイスに組み込むことが可能である。

【図面の簡単な説明】

【0010】

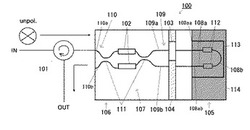

【図1】本発明の第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を示す模式図である。

【図2】本発明の第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、PLC−PBSチップとSOA−COSとの接合部付近を詳細に示した平面図である。

【図3A】図2に示されるA−A’線に沿ったPLC−PBSチップの断面図である。

【図3B】図2に示されるA’’方向から見たPLC−PBSチップの半波長板を形成するための凹部付近の側面図である。

【図4】図2に示されるB−B’線に沿ったSOA−COSのUターン部半導体光導波路部の断面図である。

【図5】(a)および(b)は、本発明の一実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、PLC−PBSチップとSOA−COSとの配置の例を示す模式図である。

【図6】(a)および(b)は、本発明の第1の実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の製造方法を説明するための模式図である。

【図7】本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を示す模式図である。

【図8A】本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、PLC−PBSチップとSOA−COSとの接合部付近を詳細に示した平面図である。

【図8B】本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路のファセットにおける接合部を一部拡大した図である。

【図9】(a)〜(c)は、本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の接合面付近の製造方法を説明するための模式図である。

【図10】本発明の第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の構成を示す模式図である。

【図11】(a)〜(c)は、本発明の第3実施形態にかかるPLC−PBSチップ、SOA−COSおよびUターンPLCチップの接合面付近の製造方法を説明するための模式図である。

【図12】本発明の実施例において、SOAの偏波依存利得を測定するための2種類の構成1211および1212を示す模式図である。

【図13A】(a)〜(d)は、本発明の実施例における測定結果を示す図である。

【図13B】本発明の実施例において、入射する光の波長を変化させたときの偏波依存利得の測定結果を示す図である。

【図14】従来の偏波無依存SOAモジュールの模式図である。

【発明を実施するための形態】

【0011】

(第1実施形態)

(構成)

図1は、本発明の第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の基本構成を示す模式図である。SOA−PLCハイブリッド集積偏波ダイバーシティ回路100は、石英系平面光波回路−偏波ビームスプリッタ(PLC−PBS)チップ106と半導体光増幅器−チップ・オン・サブマウント(SOA−COS)105とが互いの導波路を結合した構成をとる。

【0012】

PLC−PBSチップ106は、石英系光導波路109,110と、石英系光導波路が一部切欠した領域であるスリット104と、PBSとしてのマッハツェンダー干渉計回路(MZI)107と、半波長板103とを備える。MZI107は、石英系光導波路としての入力ポート110aおよび出力ポート110b、2つの方向性カプラ111、石英系光導波路としての2つの出力ポート109a、109b、ならびに2つの干渉計アーム(ヒーター)102を有する。なお、MZI107の出力ポート109aからはTMモードの光が出力され、出力ポート109bからはTEモードの光が出力される。半波長板103は、TMモードの光が出力される出力ポート109a部のスリット104に形成される。

【0013】

SOA−COS105は、直線部108aとUターン部108bを有する半導体光導波路108と、該直線部108aに形成された半導体光増幅器(SOA)112が形成されたSOAチップ113を有する。SOAチップ113はシリコンベンチ114上にハンダ実装される。直線部の半導体光導波路108aは、後述する埋込メサ構造により形成され、Uターン部の半導体光導波路108bは後述するハイメサ構造により形成される。このようにすることで、Uターン部108bでは光の閉じ込めを強くすることができ、小さな曲率半径(例えば125μm)の曲線であっても曲げによる光損失を抑制することが可能になる。したがって、光増幅特性および雑音特性の両方を良好にすることができる。ただし、直線部の半導体光導波路108aおよびUターン部の半導体光導波路108bの両方をハイメサ構造または埋込構造とすることもできる。

【0014】

SOA−COS105がUターン部の半導体光導波路108bを有することで、SOA112の出入力ポート108aaおよび出入力ポート108abが、SOA−COS105のPLC−PBSチップ106側に形成される。すなわち、Uターン部108bを形成することにより、SOA−COS105の同一の端面において光の入力および出力を行うことができ、回路全体のサイズを低減することができる。

【0015】

本実施形態において、SOA112は半導体光導波路の直線部108aに二箇所形成しているが、SOA112の長さが十分な光増幅効果が得られる長さであれば、SOA112を一箇所に形成してもよい。

【0016】

図2は、PLC−PBSチップ106とSOA−COS105との接合部付近を詳細に示した平面図である。具体的には、図2は、PLC−PBSチップ106において、MZI107の出力ポート109a、出力ポート109b、スリット104、およびスリット104に形成された半波長板103を示す。また、図2は、SOA−COS105において、SOA112、シリコンベンチ114、SOAチップ113、および直線部108aとUターン部108bを有する半導体光導波路を示す。

【0017】

図3Aは、図2に示されるA−A’線に沿ったPLC−PBSチップ106の断面図を示す。PLCプラットフォーム304上に、石英系の下部クラッド層303、石英系光導波路109aおよび109bを構成するコア層301、および上部クラッド層302が形成されている。

【0018】

図3Bは、PLC−PBSチップ106のスリット104付近を図2に示されるA”方向から見た断面図である。コア層301を伝播する光がスリット104により反射されて生じる伝播ロスと反射戻り光を低減するために、スリット104は、図3Bに示されるように、PLC−PBSチップ106の上部表面に対して垂直に形成されるのではなく所定の角度をもって形成される。例えば、スリット104の幅は20〜80μm程度、上部表面の垂線に対して5〜12°程度の傾斜を有する。

【0019】

図4は、図2に示されるB−B’線に沿ったSOA−COS105のUターン部の半導体光導波路108bの断面図を示す。SOA−COS105は、シリコンベンチ114上に、SOAチップ113を実装した形態となっている。SOAチップ113は、半導体基板(要番号付け)上に下部クラッド層403、半導体光導波路108bを構成するコア層402、および上部クラッド層401が形成されたハイメサ構造が使用される。

【0020】

SOA−COS105は化合物半導体InP基板上にマイクロプロセスで形成される。下部クラッド層403はInPにより形成される。コア層402は化合物半導体InGaAsPにより形成される。そして、上部クラッド層401はInPにより形成される。なお、本実施形態ないし下記の実施形態にかかるSOA−COS105は、InP以外の半導体材料で形成することもできる。また、本実施形態にかかる導波路チップはSOAのような半導体光導波路に限定されない。LiNbO3光導波路やシリコン系光導波路など、偏波依存性をもつすべての導波路に適用することが可能である。

【0021】

ここで、一般的に、石英系PLCの光導波路では、光導波路を構成するコアとクラッドの比屈折率差は大きくても2.5%程度である。化合物半導体InP等で形成された半導体光導波路では、コアとクラッドの比屈折率差が4〜5%を超える。本実施形態では、図4に示されるように、Uターン型の半導体光導波路(Uターン部108b)をハイメサ構造とすることにより、コア層402とその両側の誘電体または空気との比屈折率差が、例えば30〜40%以上と非常に大きくなる。また、光導波路を折り返した際の折り返し部の曲率半径は、コアとクラッドの比屈折率差が大きいほど小さくすることができる。例えば、本実施形態において、該曲率半径は125μm程度である。そのため、石英系PLCチップ上でUターン型の光導波路の折り返し構造を形成する場合に比べて、SOA−COS105上でハイメサ構造によってUターン型の光導波路の折り返し構造を形成する方がチップのサイズを小さくすることができる。本実施形態では、Uターン部108bを半導体光導波路として形成し、さらにハイメサ構造とすることにより、Uターン部108bのサイズを小さくすることができ、その結果、回路全体のサイズを小さくすることができる。

【0022】

SOA112は、半導体光導波路の直線部108aに埋込メサ構造により形成される。SOA112のコア層は光増幅媒質で形成された活性層(図示せず)を有する。SOA112は、注入電流をオン/オフさせることで、入射光をオン/オフさせる半導体ゲートとして用いることもできる。なお、一般的にSOA112の長さが短すぎると所望の利得が得られず、また、長すぎると伝播する光にノイズが入りやすく雑音特性が悪化する。そのため、好ましい例としては、SOA112の長さは例えば0.5〜2ミリメートル程度である。

【0023】

図1に示されたように、本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路では、PLC−PBSチップ106の石英系光導波路109とSOA−COS105の半導体光導波路108とが調芯され、接合されている。

【0024】

SOA−COS105のSOAチップ113は、PLC−PBSチップ106に比べ薄い。そのため、SOAチップ113をシリコンベンチ114に実装する。このようにすることで、PLC−PBSチップ106とSOA−COS105を接合するときの、接合部分の面積を広くすることが可能になり、PLC−PBSチップ106とSOA−COS105の接合に、十分な強度を得ることができる。

【0025】

本実施形態においては、図5(a)に示されるように、PLC−PBSチップ106とSOA−COS105は、チップごとに導波路の結合を行っている。さらに、本実施形態では、図5(b)に示されるように、ベースのシリコン基板501をそれぞれのチップで共有するシリコン基板テラス構造を用いることもできる。この形態においても、ベースのシリコン基板501は共有されているが、PLC−PBSチップ106とSOA−COS105はそれぞれの導波路が結合している。下記の全ての実施形態においても、この導波路結合の形態は適用可能である。

【0026】

(作用)

本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、入力INからの非偏光の光が、サーキュレータ101によってSOA−PLCハイブリッド集積偏波ダイバーシティ回路100へ伝播される。SOA−PLCハイブリッド集積偏波ダイバーシティ回路100からの光は、サーキュレータ101によって出力OUTに伝播される。

【0027】

一般的に、マッハツェンダー干渉計回路(MZI)は2本のアーム間にΔΦの位相差を有する。MZIアーム中で複屈折が起こる場合、TEモードおよびTMモードでの該位相差はそれぞれ独立して変化する。TEモードの該位相差ΔΦTEとTMモードの該位相差ΔΦTMとの差は、|ΔΦTE−ΔΦTM|=(2π/λ)B・Lで表される。ここで、λは波長、BはMZI中の複屈折率、LはMZIのアーム長である。|ΔΦTE−ΔΦTM|が(2n+1)π(n:整数)であるとき、MZIは入射された非偏光の光を2つの直交する光モード(即ち、TEモードとTMモード)へ分割する。そして、TEモードの光は一方の出力ポートへ出力され、TMモードの光は他方の出力ポートへ出力される。

【0028】

サーキュレータ101から伝播された非偏光の光は、MZI107によって互いに2つの直交モード(即ち、TEモードおよびTMモード)に分けられる。本実施形態にかかる構成においては、MZI107から出射されたTEモードの光は出力ポート109bへ伝播され、TMモードの光は出力ポート109aへ伝播される。出力ポート109aから出力したTMモードの光は、半波長板103によってTEモードの光に変更される。その結果、SOA−COS105にはTEモードの光のみが伝播される。

【0029】

一般的な半導体光増幅器は、例えば5量子井戸構造であり、12dBの飽和パワー、並びに概ね4dB以下の低い雑音指数を有する。半導体光増幅器自体の偏波依存利得は概ね10〜20dB程度である。半導体光増幅器に入射する光について、TEモードの光は19dB程度の小さい信号利得を有するが、TMモードの光は吸収され、−10〜0dB程度の利得を有する。

したがって、本実施形態のようにSOA−COS105にTEモードの光のみを伝播することにより、大きな利得を得ることができる上、SOA112の偏波依存利得(PDG)を低減することができる。

【0030】

上記のように、従来の偏波無依存SOAモジュールでは、空間的に分離した個別の光学部品を使用するため、モジュール全体としてサイズが比較的大きくなること、また、ハーフミラー等の光学部品が用いられるため使用者による光学部品間の光軸調整に手間がかかること等の理由から、該モジュールを大量生産し、他のデバイスに組み込む等の応用が難しいという問題があった。

【0031】

しかしながら、第1実施形態では、SOA−COS105にUターン部108bを設けてSOA−COS105の一端面から光の入出力を可能にし、偏波を分離し、該分離した偏波を統一するように構成されたPLC−PBSチップ106にSOA−COS105に対する入力光および出力光の双方を導波するようにPLC−SOAハイブリッド集積偏波ダイバーシティ回路を構成している。従って、従来のように、SOAへの入力経路と出力経路とを別個に設ける必要がなく、従来の偏波無依存SOAモジュールに比べ、モジュール(回路)のサイズを低減することができる。

【0032】

また、本実施形態では、ハーフミラー、レンズといった光学部品を用いず、PBSとしてのMZI107、および該MZI107のTMモード出力側の導波路に形成された半波長板103を有する平面光波回路としてのPLC−PBSチップ106を用いているので、使用者による光軸調整の煩わしさを必要としない。

【0033】

さらに、本実施形態では、偏波ダイバーシティ回路の構成要素であるPLC−PBSチップ106に対する設計マスクを一度作製してしまえば、従来からある半導体集積回路技術や平面光波回路技術を用いて大量生産が可能である。

【0034】

そして、本実施形態では、導波路チップであるSOA−COS105およびPLC−PBSチップ106の導波路を結合することで、単一の導波路デバイスを形成しているので、他のデバイスに組み込む等の応用が容易である。したがって、該回路は、商業的利用に非常に効果的である。

【0035】

また、本実施形態では、SOA−COS105にTEモードの光のみを伝播するため、SOA112の偏波依存利得(PDG)を低減することができる。

【0036】

(製造方法)

PLC−PBSチップ106では、シリコンや石英などの基板上に微細加工技術を組み合わせて、石英系の材料で光導波路が形成される。

【0037】

一般的に、平面光波回路(PLC)は、光ファイバ製造技術の応用である火炎直接堆積(FHD)法により、PLC基板(例えばシリコン基板)上に下部クラッド層およびコア層となるガラス粒子を堆積し加熱してガラス膜を溶融透明化する。この後、半導体集積回路製造技術であるフォトリソグラフィと反応性イオンエッチングで所望の光導波路パターンを形成し、再びFHD法により上部クラッドを形成する。

【0038】

複屈折は、石英系ガラス導波路に、局所的に加熱すること、またはUV照射することによりトリミングできる。適切に複屈折をトリミングすることで、石英系PLCチップに偏波ビームスプリッタ(PBS)が形成できる。

【0039】

ヒーター102は、MZI107における複屈折をトリミングするために、MZI107の2つのアーム上に形成される。ヒーター102でトリミングする間に、MZIの2つのアームの位相差が適切になるように測定される。PLC−PBSチップ106が、所定の光の波長(例えば、1530nm)において、所定の値(例えば、15dB)の偏光消光比を有するように設定される。

【0040】

図1に示されるように、半波長板103を形成するために、スリット104は、MZI107の2つの出力ポートとSOA−COS105との間に、石英系光導波路109と垂直に交わるように形成される。なお、スリット104は、ダイサー等を用いて形成され、図3Bに示されるように、光が反射するのを防ぐために、PLC−PBSチップ106の上面に対して所定の角度の傾斜をつけて形成される。

【0041】

本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路は、PLC−PBSチップ106の石英系光導波路109とSOA−COS105の半導体光導波路108とが互いに一つの接触面で接触され、調芯され、接合される。

【0042】

具体例として、図6を参照して、下記の製造方法のように本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を製造する。

【0043】

(工程1)図6(a)に示されるように、石英系光導波路110a、110b、109a、109b、ヒーター102が形成されたPLC−PBSチップ106を準備する。試験光を石英系光導波路110a、110b側から伝播させ、ヒーター102に熱を加え適切にトリミングを行い、MZI107の2つのアームの位相差が適切になるように調整する。

【0044】

(工程2)PLC−PBSチップ106のSOA−COS105が接合されるファセットfPLCを光学研磨によって十分に小さな表面粗さの面に修正する。これにより半導体光導波路108a、108bと結合するPLC−PBSチップ106の断面が形成される。ダイサー等により、破線Cの部分にPLC−PBSチップ106の上面に対して垂直ではなく所定の角度をもつようにスリット104を形成する。半波長板103をスリット104中に形成する。半波長板103は、MZI107からTMモードの光を伝播する石英系光導波路側109aに形成する。

【0045】

(工程3)図6(b)に示されるように、直線部108aとUターン部108bを有する半導体光導波路とSOA112が形成されたSOA−COS105を準備する。SOA−COS105の半導体光導波路108aを劈開することにより、PLC−PBSチップ106と結合する接合面を形成する。そして、接触する石英系光導波路と半導体光導波路とを調芯し、PLC−PBSチップ106とSOA−COS105とを接着剤などで固定する。

【0046】

なお、上記工程1〜3に含まれる処理内容や工程の順序等は適宜調整してもよい。

【0047】

上記のSOA−PLCハイブリッド集積偏波ダイバーシティ回路で使用される材料の種類やパラメータ等は単なる例示であり、本実施形態において、ならびに下記の実施形態においても、それらに限定されるものではない。

【0048】

(第2実施形態)

(構成)

図7は、本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路700の構成を示す模式図である。第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路700は、第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路100の構成と略同一である。そのため、本実施形態には、当然、第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路が有する作用、効果が含まれる。ただし、PLC−PBSチップ106とSOA−COS105との導波路の結合において、モードフィールド径の違いによる光の伝播ロスや導波路の結合面における反射を低減するための構成701が用いられる。

【0049】

図8Aに構成701の詳細を示す。図8Aに示すように、構成701は、スポットサイズ変換器(SSC)802a、802bを有し、PLC−PBSチップ106とSOA−COS105との接合面f1に対して垂直ではなく所定の角度をもってそれぞれのチップの光導波路が接合されている。

【0050】

より詳細には、構成701は、コアの中心軸C3を有する直線状の石英系光導波路109a(109b)は、コアの中心軸C1を有する傾斜された石英系光導波路801a(801b)になめらかに接続される。図8Bに示すように、伝播する光が接合面f1に対して斜めに入射するように、中心軸C1は接合面f1に対して所定の角度θ1傾斜している。同様に、コアの中心軸C2を有する傾斜された半導体光導波路(即ち、SSC802a(802b))は、直線部の半導体光導波路108aになめらかに接続される。傾斜された半導体光導波路であるSSC802a(802b)は接合面f1に対して、所定の角度θ2傾斜している。

【0051】

図8Bは、接合面f1における接合部を一部拡大した図である。傾斜された石英系光導波路801a、801bにおける屈折率n1、中心軸C1と接合面f1の垂線とのなす角度θ1、傾斜されたSSC802a、802bにおける屈折率n2、中心軸C2と接合面f1の垂線とのなす角度θ2との間には、スネルの法則より、n1sinθ1=n2sinθ2、という関係がある。この関係を満たすように、傾斜角θ1、θ2が決定される。また、SOA−COS105側の接合面f1上には反射防止(AR)コート803がコーティングされている。なお、PLC側の傾斜角度θ1としては5〜9°、半導体導波路側の傾斜角度θ2としては12°〜17°が好ましい。

【0052】

SSC802a、802bは、PLC−PBSチップ106のSOA−COS105の接合面近傍の石英系光導波路801a、801bのモードフィールドと半導体光導波路108aのモードフィールドとをマッチさせるようにテーパー状の形状を有する光導波路(幅広フレアー型SSC)である。SSC802a、802bは、図8Bに示されるように、部位(i)における幅を保ったまま部位(ii)において曲げられ、部位(iii)においてテーパー状に幅が広くなり、部位(iv)において幅が広がった状態で平行に形成される。本実施形態では、SSC802a、802bは、SOA−COS105の側に形成されているが、PLC−PBSチップ106の側に形成してもよい。SSC802a、802bによって、それぞれの導波路の結合部における結合ロスを低減し、高い結合効率を得ることができる。

【0053】

(作用)

PLC−PBSチップ106における石英系ガラス等の石英系光導波路の屈折率n1に対して、SOA−COS105におけるInP等の半導体光導波路の屈折率n2は異なるため、それぞれの導波路のモードフィールド(電界分布)が互いに異なる。例えば、石英系光導波路のモードフィールド径は概ね3〜8μmであり、InP半導体光導波路のモードフィールド径は概ね1〜2μmである。そのため、本実施形態は、PLC−PBSチップ106における石英系光導波路とSOA−COS105の半導体光導波路を結合する際に、モードフィールド径の違いによる光の伝播ロスや接合面における反射を低減するための構成701を用いる。

【0054】

本実施形態にかかる構成701は、スポットサイズ変換器(SSC)802a、802bを用いてモードフィールド径の違いを修正することができる。また、それぞれのチップの光導波路が所定の角度をもって結合されることで反射を低減することができる。さらに、SOA−COS105側の接合面f1(PLC−PBSチップ106とSOA−COS105との接合面)に反射防止(AR)コート803をコーティングすることで、反射により生じる光の伝播ロスを低減することができる。

【0055】

本実施形態では、上記のような構成をとることにより、PLC−PBSチップ106における石英系光導波路とSOA−COS105の半導体光導波路を結合する際に、モードフィールド径の違いによる光の伝播ロスや接合面における反射を低減することができる。

【0056】

図8Aにおいて、光は、直線部の石英系光導波路109から傾斜された光導波路801a、801bへ入射される。第1実施形態のように、光は、接合面f1に対して垂直に入射せず、所定の角度をもって入射される。光は所定の角度で接合面f1へ入射するため、接合面f1による反射光は再度傾斜された光導波路801a、801bへ戻ることは難しい。よって、石英系光導波路109への接合面f1における反射戻り光は低減される。

【0057】

同様に、光は、SOA−COS105中を伝播しPLC−PBSチップ106へ戻る場合、傾斜された半導体光導波路(即ち、SSC802a、802b)へ入射される。第1実施形態のように、光は、接合面f1に対して垂直に入射せず、所定の角度をもって入射される。光は所定の角度で接合面f1へ入射するため、接合面f1による反射光は再度SSC802a、802bへ戻ることは難しい。よって、SSC802a、802bへの接合面f1における反射戻り光は低減される。

【0058】

(製造方法)

第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の製造方法は、第1実施形態にかかる該回路の製造方法と略同一である。ここで、図9の各図には、構成701付近のみを詳細に記載しているが、その他の部分については、第1実施形態にかかる該回路の構成と略同一であるため省略している。

【0059】

(工程1)

石英系光導波路110、109、曲げられた石英系光導波路701、SOA−COS105との接合面となるファセットfPLCに垂直な方向に対してある角度θ1だけ水平方向に傾いている石英系光導波路801、および、ヒーター102が形成されたPLC−PBSチップ106を準備する。試験光を石英系光導波路110側から伝播させ、石英系光導波路109側において、ヒーター102を通過した光を測定する。測定の間、ヒーター102に熱を加え適切にトリミングを行い、MZI107の2つのアームの位相差が適切になるように調整する。

【0060】

(工程2)

図9(a)に示されるように、PLC−PBSチップ106の余分な部分を破線Aに沿って切断する。すなわち、石英系光導波路801a、801bは角度θ1の直線部分の任意の点において、ファセットfPLCを形成するように、PLC−PBSチップ106の端部をダイサー等により切断する。切断して形成されるファセットfPLCは光学研磨によって十分に小さな表面粗さの面に修正される。以上により半導体光導波路802a、802bと結合するPLC−PBSチップ106の断面が形成される。ダイサー等によりPLC−PBSチップ106の上面に対して垂直ではなく所定の角度をもつスリット104を形成する。半波長板103をスリット104中に形成する。半波長板103は、MZI107からTMモードの光を伝播する石英系光導波路109a側に形成する。

【0061】

(工程3)

図9(b)に示されるように、直線部108aの半導体光導波路、テーパー状の半導体光導波路である所定の角度(接合面f1の垂線と中心軸C2とのなす角度がθ2となるように)に傾斜されたSSC802a、802b、およびSOA112が形成されたSOA−COS105を準備する。SOA−COS105は、半導体光導波路802a、802bの出射角度がθ2になるように劈開され、PLC−PBSチップ106と結合するSOA−COS105のファセットfSOAが形成される。直線部半導体光導波路108aとSOA112は埋込メサ構造により形成され、Uターン部半導体光導波路はハイメサ構造により形成されており、SOA−COS105のファセットfSOAにARコート803がコーティングされている。

【0062】

(工程4)

図9(c)に示されるように、それぞれのチップの光導波路を調芯し、それぞれのチップを接着剤などで固定する。導波路の接合面f1はPLC−PBSチップ側のファセットfPLCとSOA−COS側のファセットfSOAの2つが対向して、石英系光導波路801aと半導体導波路802a、石英系光導波路801bと半導体導波路802bがそれぞれ光学的に結合する空間で形成される。

なお、上記工程1〜4に含まれる処理内容や工程の順序等は適宜調整してもよい。

【0063】

(第3実施形態)

(構成)

図10は、本発明の第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路1000の構成を示す模式図である。第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路1000は、第1実施形態および第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の構成と略同一である。そのため、本実施形態には、第1実施形態および第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路が有する作用、効果が含まれる。ただし、本実施形態においては、SOA−COS1001に光導波路の折り返し部を形成するのではなく、UターンPLCチップ1002にUターン石英系光導波路1003を形成し、SOA112により増幅した光をMZIへ戻すようにしている。そして、SOA112はSOA−COS1001の半導体光導波路の直線部に形成されている。すなわち、第3実施形態においては、PLC−PBSチップ106から伝播された光は、SOA−COS1001に形成されたSOA112で増幅され、UターンPLCチップ1002に形成されたUターン石英系光導波路1003で折り返され、再びSOA−COS1001に形成されたSOA112で増幅され、PLC−PBSチップ106へ戻る。

【0064】

本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路においても、PLC−PBSチップ105とSOA−COS1001との接合部およびSOA−COS1001とUターンPLCチップ1002との接合部におけるそれぞれのチップの光導波路は、第2実施形態にかかる該回路の特徴のように、コアサイズの違いによる光の伝播ロスや接合面における反射を低減するための構成701を用いている。

【0065】

(作用)

上記したように、大きい比屈折率差の光導波路であるほど折り返し部の曲率半径を小さくすることができ、その結果、回路全体のサイズを低減することができる。しかしながら、第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路のように、SOAに適した埋込メサ構造の半導体導波路と、曲率半径の小さいUターンに適したハイメサ構造の半導体導波路を結合して同じチップ内で作製することは、必ずしも容易ではない。

【0066】

Uターン構造をなくし、埋込メサ構造の半導体導波路のみでSOA−COSを構成するほうが、容易に導波路を形成することができる。第2実施形態のSOA−PLCハイブリッド集積偏波ダイバーシティ回路に比べ、本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路は、全体のサイズが少し大きくなるが、SOA−COSの作製が容易になり、偏波ダイバーシティ回路の実現性が高まる。

【0067】

(製造方法)

第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の製造方法は、第1実施形態および第2実施形態にかかる該回路の製造方法と略同一である。ここで、図8の各図には、PLC−PBSチップ106、SOA−COS1001およびUターンPLCチップ1002の接合部における構成701付近のみを詳細に記載している。その他の部分については、第1実施形態および第2実施形態にかかる該回路の構成と略同一であるため省略している。

【0068】

(工程1)

石英系光導波路110、109、所定の角度に傾斜された石英系光導波路801、ヒーター102が形成されたPLC−PBSチップ106を準備する。試験光を石英系光導波路110側から伝播させ、石英系光導波路109側において、ヒーター102を通過した光を測定する。測定の間、ヒーター102に熱を加え適切にトリミングを行い、MZI107の2つのアームの位相差が適切になるように調整する。また、Uターン状の石英系光導波路1003、石英系光導波路109、曲げられた石英系光導波路801、所定の角度に傾斜された石英系光導波路801、が形成されたUターンPLCチップ1002を準備する。

【0069】

(工程2)

図11(a)に示されるように、PLC−PBSチップ106およびUターンPLCチップ1002の余分な部分を破線AおよびA’に沿って切断する。すなわち、石英系光導波路801a、801bは角度θ1の直線部分の任意の点において、ファセットfPLCを形成するように、PLC−PBSチップ106およびUターンPLCチップ1002の端部をダイサー等により切断する。切断して形成されるファセットfPLCは光学研磨によって十分に小さな表面粗さの面に修正される。以上により半導体光導波路802a、802bと結合するPLC−PBSチップ106、およびUターンPLCチップ1002の断面が形成される。また、ダイサー等によりPLC−PBSチップ106の上面に対して垂直ではなく所定の角度をもつスリット104を形成する。半波長板103をスリット104中に形成する。半波長板103は、MZI107からTMモードの光を伝播する石英系光導波路109a側に形成する。

【0070】

(工程3)

図11(b)に示されるように、直線部108aの半導体光導波路、テーパー状の半導体光導波路である傾斜されたSSC802a、802b、およびSOA112が形成されたSOA−COS1001を準備する。SOA−COS1001は、半導体光導波路802a、802bの出射角度がθ2(図8B参照)になるように劈開され、PLC−PBSチップ106およびUターンPLCチップ1002と結合するSOA−COS1001のファセットfSOAが形成される。その後、SOA−COS1001の両方の切断面であるファセットfSOAにARコート803(図8B参照)をコーティングする。

【0071】

(工程4)

図11(c)に示されるように、それぞれのチップの光導波路を調芯し、それぞれのチップを接着剤などで固定する。導波路の接合面f1はPLC−PBSチップおよびUターンPLCチップ側のファセットfPLCとSOA−COS側のファセットfSOAの2つが対向して、石英系光導波路801aと半導体導波路802a、石英系光導波路801bと半導体導波路802bがそれぞれ光学的に結合する空間で形成される。

なお、上記工程1〜4に含まれる処理内容や工程の順序等は適宜調整してもよい。

【0072】

(実施例)

図12は、SOAの偏波依存利得(PDG)を測定するために、2種類のPDG測定構成を示す。図12は、調整可能な光源(TLS)1201、エルビウム添加光ファイバ増幅器(EDFA)1202、偏波コントローラ(PC)1203、減衰器(ATT)1204、入力側光スイッチ1205、光スペクトラムアナライザ(OSA)1206、光パワーメータ(OPM)1207、10:1スプリッタ1208、アイソレータ1209、出力側光スイッチ1210、基準構成1211、および第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路構成1212を示す。構成1211は、2つのストレート型光導波路を有するST−PLCチップとSOAを有するSOA−COS、ならびにUターン型光導波路を有するU−PLCチップとが接合された構成をとる。構成1212に比べ、サーキュレータと偏波ビームスプリッタを有しない。

【0073】

TLS1201から構成1211に光を入射する場合、該構成1211はPDCを用いないため、構成1211を伝播する光はそのまま、入力側光スイッチ1205から出力側光スイッチ1210へと一方向に伝播する。構成1211におけるSOAのPDGを調べるために、TLS1201からTEモードの光(中心波長λ=1550nm)を入射させた場合の測定結果を図13A(a)に、TLS1201からTMモードの光を入射させた場合の測定結果を図13A(b)に示す。なお、図13Aの各図のスケールは、横軸が1549.5〜1550〜1550.5(nm)、縦軸が−60〜0〜+10(dBm)であり、上側の太線のスペクトルが構成1211および1211を通過後の出力光のスペクトル、下側のスペクトルが入力光のスペクトルである。

【0074】

また、構成1212におけるSOAのPDGを調べるために、TLS1201からTEモードの光(中心波長λ=1550nm)を入射させた場合の測定結果を図13A(c)に、TLS1201からTMモードの光を入射させた場合の測定結果を図13A(d)に示す。なお、構成1212において、上記θ1を15°、θ2を7°とすることで、伝播光のリターンロスは−50dB以下に低減された。

【0075】

構成1211において、TEモードの光の場合は、5.8dBの増幅利得が得られたが、TMモードの光の場合は、−5.3dBと負の増幅利得が得られた。構成1212において、TEモードの光の場合は、6.3dBの増幅利得が得られ、TMモードの光の場合は、4.4dBの増幅利得が得られた。

【0076】

この結果から、TEモードの光は、構成1211および構成1212にかかわらず、即ちPDCの構成を有するか否かにかかわらず、SOAによる光増幅利得が得られた。しかしながら、TMモードの光について、構成1212ではSOAによる光増幅利得が得られたが、構成1211ではSOAによる負の光増幅利得(即ち、吸収)が得られた。

【0077】

よって、構成1211の偏波依存利得(PDG)は11.1dBであった。一方、構成1212のPDGは1.9dBであった。本発明の第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路(構成1212)を用いることで、PDGを大きく低減できた。

【0078】

図13Bに、入射光の中心波長を1530、1540、1550nmで測定した場合における、構成1211のPDG1301の変化および構成1212のPDG1302の変化を示す。構成1211では、PDGが11.1〜22.9dBと大きい値をとった。一方、構成1212では、PDGが1.2dBと構成1211の値に比べ大きく低減した。このことから、本実施例にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路は、SOAのPDGを低減するという効果があることが示された。

【符号の説明】

【0079】

100 SOA−PLCハイブリッド集積偏波ダイバーシティ回路

101 サーキュレータ

102 ヒーター

103 半波長板

104 スリット

105 SOA−COS

106 PLC−PBSチップ

107 MZI

108 半導体光導波路

109 石英系光導波路

109a MZI107の出力ポート

109b MZI107の出力ポート

110 石英系光導波路

110a MZI107の入力ポート

110a MZI107の出力ポート

111 カプラ

112 SOA

113 SOAチップ

114 シリコンベンチ

【技術分野】

【0001】

本発明は、平面光波回路(PLC)としての偏波ビームスプリッタ(PBS)および半導体光増幅器(SOA)を備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路およびその製造方法に関する。

【背景技術】

【0002】

近年、光通信ネットワークにおけるデータ量の増加にともない、コンパクトで低コストである光学素子が要求される。従来の個別の光学部品を組み合わせる技術に代わり、フォトニック集積回路(PIC)技術に基づく光導波路デバイス技術へとトレンドが移行しつつある。

【0003】

光通信ネットワークにおいて、光導波路デバイスにおける偏波依存性は、実用的に好ましくは、0.1dB以下が要求される。偏波ダイバーシティ回路は、光学デバイスにおける偏波依存性の問題を解消するために使用される。

【0004】

非特許文献1は、図14のように、それぞれ空間的に分離した個別の光学部品である、3つのポート1401〜1403を有するサーキュレータ1409、レンズ1404、偏波ビームスプリッタとしてのハーフミラー1405、半波長板1406、ミラー1407、およびSOA1408を使用した偏波ダイバーシティ回路によりSOAの偏波依存利得(PDG)を解消するための偏波無依存SOAモジュールを開示する。

【先行技術文献】

【特許文献】

【0005】

【非特許文献1】K. Morito and S. Tanaka, ”Record High Saturation Power (+22dBm) and Low Noise Figure (5.7dB) Polarization-Insensitive SOA Module”, IEEE PHOTONICS TECHNOLOGY LETTERS, 17, 6, 1298-1300, (2005)

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、非特許文献1に開示の偏波無依存SOAモジュールは、空間的に分離した個別の光学部品を使用するため、モジュール全体としてサイズが大きくなってしまう。また、非特許文献1に開示の該モジュールでは、ハーフミラー1405やミラー1407等の光学部品が用いられるため、図14に示される該モジュールを形成するには、使用者によるそれぞれの光学部品間の光軸調整が必要であり、非常に手間がかかる。したがって、該モジュールを他のデバイスに組み込む等の応用が難しい。そのため、非特許文献1に開示の該モジュールを商業的に利用することは難しいと考えられる。

【0007】

本発明の目的は、従来のモジュールに比べモジュール(回路)のサイズを低減し、容易に他のデバイスに組み込むことが可能であるPLC−SOAハイブリッド集積偏波ダイバーシティ回路を提供することである。

【課題を解決するための手段】

【0008】

本発明は、互いに導波路を結合したPLC−PBSチップとSOA−COSとを備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路であって、該PLC−PBSチップは、第1および第2の光導波路と、入力された光をTMモードの光およびTEモードの光へ分割し、該分割されたTMモードの光を該第1の光導波路へ出力し、該分割されたTEモードの光を該第2の光導波路へ出力するマッハツェンダー干渉計回路と、該TMモードの光が伝播する第1の石英系光導波路中に形成された偏波回転機構とを含み、該SOA−COSは、該第1の光導波路に接続された第3の光導波路と、該第2の光導波路に接続された第4の光導波路と、少なくとも一方の該第3および第4の光導波路に形成されたSOAとを含み、該第3の光導波路と、該第4の光導波路のそれぞれ該第1の光導波路および該第2の光導波路と接続しないもう一端同士は、Uターン部光導波路で接続されていることを特徴とするSOA−PLCハイブリッド集積偏波ダイバーシティ回路を提供する。

【発明の効果】

【0009】

本発明にかかるPLC−SOAハイブリッド集積偏波ダイバーシティ回路は、従来のモジュールに比べモジュール(回路)のサイズを低減することができ、容易に他のデバイスに組み込むことが可能である。

【図面の簡単な説明】

【0010】

【図1】本発明の第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を示す模式図である。

【図2】本発明の第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、PLC−PBSチップとSOA−COSとの接合部付近を詳細に示した平面図である。

【図3A】図2に示されるA−A’線に沿ったPLC−PBSチップの断面図である。

【図3B】図2に示されるA’’方向から見たPLC−PBSチップの半波長板を形成するための凹部付近の側面図である。

【図4】図2に示されるB−B’線に沿ったSOA−COSのUターン部半導体光導波路部の断面図である。

【図5】(a)および(b)は、本発明の一実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、PLC−PBSチップとSOA−COSとの配置の例を示す模式図である。

【図6】(a)および(b)は、本発明の第1の実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の製造方法を説明するための模式図である。

【図7】本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を示す模式図である。

【図8A】本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、PLC−PBSチップとSOA−COSとの接合部付近を詳細に示した平面図である。

【図8B】本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路のファセットにおける接合部を一部拡大した図である。

【図9】(a)〜(c)は、本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の接合面付近の製造方法を説明するための模式図である。

【図10】本発明の第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の構成を示す模式図である。

【図11】(a)〜(c)は、本発明の第3実施形態にかかるPLC−PBSチップ、SOA−COSおよびUターンPLCチップの接合面付近の製造方法を説明するための模式図である。

【図12】本発明の実施例において、SOAの偏波依存利得を測定するための2種類の構成1211および1212を示す模式図である。

【図13A】(a)〜(d)は、本発明の実施例における測定結果を示す図である。

【図13B】本発明の実施例において、入射する光の波長を変化させたときの偏波依存利得の測定結果を示す図である。

【図14】従来の偏波無依存SOAモジュールの模式図である。

【発明を実施するための形態】

【0011】

(第1実施形態)

(構成)

図1は、本発明の第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の基本構成を示す模式図である。SOA−PLCハイブリッド集積偏波ダイバーシティ回路100は、石英系平面光波回路−偏波ビームスプリッタ(PLC−PBS)チップ106と半導体光増幅器−チップ・オン・サブマウント(SOA−COS)105とが互いの導波路を結合した構成をとる。

【0012】

PLC−PBSチップ106は、石英系光導波路109,110と、石英系光導波路が一部切欠した領域であるスリット104と、PBSとしてのマッハツェンダー干渉計回路(MZI)107と、半波長板103とを備える。MZI107は、石英系光導波路としての入力ポート110aおよび出力ポート110b、2つの方向性カプラ111、石英系光導波路としての2つの出力ポート109a、109b、ならびに2つの干渉計アーム(ヒーター)102を有する。なお、MZI107の出力ポート109aからはTMモードの光が出力され、出力ポート109bからはTEモードの光が出力される。半波長板103は、TMモードの光が出力される出力ポート109a部のスリット104に形成される。

【0013】

SOA−COS105は、直線部108aとUターン部108bを有する半導体光導波路108と、該直線部108aに形成された半導体光増幅器(SOA)112が形成されたSOAチップ113を有する。SOAチップ113はシリコンベンチ114上にハンダ実装される。直線部の半導体光導波路108aは、後述する埋込メサ構造により形成され、Uターン部の半導体光導波路108bは後述するハイメサ構造により形成される。このようにすることで、Uターン部108bでは光の閉じ込めを強くすることができ、小さな曲率半径(例えば125μm)の曲線であっても曲げによる光損失を抑制することが可能になる。したがって、光増幅特性および雑音特性の両方を良好にすることができる。ただし、直線部の半導体光導波路108aおよびUターン部の半導体光導波路108bの両方をハイメサ構造または埋込構造とすることもできる。

【0014】

SOA−COS105がUターン部の半導体光導波路108bを有することで、SOA112の出入力ポート108aaおよび出入力ポート108abが、SOA−COS105のPLC−PBSチップ106側に形成される。すなわち、Uターン部108bを形成することにより、SOA−COS105の同一の端面において光の入力および出力を行うことができ、回路全体のサイズを低減することができる。

【0015】

本実施形態において、SOA112は半導体光導波路の直線部108aに二箇所形成しているが、SOA112の長さが十分な光増幅効果が得られる長さであれば、SOA112を一箇所に形成してもよい。

【0016】

図2は、PLC−PBSチップ106とSOA−COS105との接合部付近を詳細に示した平面図である。具体的には、図2は、PLC−PBSチップ106において、MZI107の出力ポート109a、出力ポート109b、スリット104、およびスリット104に形成された半波長板103を示す。また、図2は、SOA−COS105において、SOA112、シリコンベンチ114、SOAチップ113、および直線部108aとUターン部108bを有する半導体光導波路を示す。

【0017】

図3Aは、図2に示されるA−A’線に沿ったPLC−PBSチップ106の断面図を示す。PLCプラットフォーム304上に、石英系の下部クラッド層303、石英系光導波路109aおよび109bを構成するコア層301、および上部クラッド層302が形成されている。

【0018】

図3Bは、PLC−PBSチップ106のスリット104付近を図2に示されるA”方向から見た断面図である。コア層301を伝播する光がスリット104により反射されて生じる伝播ロスと反射戻り光を低減するために、スリット104は、図3Bに示されるように、PLC−PBSチップ106の上部表面に対して垂直に形成されるのではなく所定の角度をもって形成される。例えば、スリット104の幅は20〜80μm程度、上部表面の垂線に対して5〜12°程度の傾斜を有する。

【0019】

図4は、図2に示されるB−B’線に沿ったSOA−COS105のUターン部の半導体光導波路108bの断面図を示す。SOA−COS105は、シリコンベンチ114上に、SOAチップ113を実装した形態となっている。SOAチップ113は、半導体基板(要番号付け)上に下部クラッド層403、半導体光導波路108bを構成するコア層402、および上部クラッド層401が形成されたハイメサ構造が使用される。

【0020】

SOA−COS105は化合物半導体InP基板上にマイクロプロセスで形成される。下部クラッド層403はInPにより形成される。コア層402は化合物半導体InGaAsPにより形成される。そして、上部クラッド層401はInPにより形成される。なお、本実施形態ないし下記の実施形態にかかるSOA−COS105は、InP以外の半導体材料で形成することもできる。また、本実施形態にかかる導波路チップはSOAのような半導体光導波路に限定されない。LiNbO3光導波路やシリコン系光導波路など、偏波依存性をもつすべての導波路に適用することが可能である。

【0021】

ここで、一般的に、石英系PLCの光導波路では、光導波路を構成するコアとクラッドの比屈折率差は大きくても2.5%程度である。化合物半導体InP等で形成された半導体光導波路では、コアとクラッドの比屈折率差が4〜5%を超える。本実施形態では、図4に示されるように、Uターン型の半導体光導波路(Uターン部108b)をハイメサ構造とすることにより、コア層402とその両側の誘電体または空気との比屈折率差が、例えば30〜40%以上と非常に大きくなる。また、光導波路を折り返した際の折り返し部の曲率半径は、コアとクラッドの比屈折率差が大きいほど小さくすることができる。例えば、本実施形態において、該曲率半径は125μm程度である。そのため、石英系PLCチップ上でUターン型の光導波路の折り返し構造を形成する場合に比べて、SOA−COS105上でハイメサ構造によってUターン型の光導波路の折り返し構造を形成する方がチップのサイズを小さくすることができる。本実施形態では、Uターン部108bを半導体光導波路として形成し、さらにハイメサ構造とすることにより、Uターン部108bのサイズを小さくすることができ、その結果、回路全体のサイズを小さくすることができる。

【0022】

SOA112は、半導体光導波路の直線部108aに埋込メサ構造により形成される。SOA112のコア層は光増幅媒質で形成された活性層(図示せず)を有する。SOA112は、注入電流をオン/オフさせることで、入射光をオン/オフさせる半導体ゲートとして用いることもできる。なお、一般的にSOA112の長さが短すぎると所望の利得が得られず、また、長すぎると伝播する光にノイズが入りやすく雑音特性が悪化する。そのため、好ましい例としては、SOA112の長さは例えば0.5〜2ミリメートル程度である。

【0023】

図1に示されたように、本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路では、PLC−PBSチップ106の石英系光導波路109とSOA−COS105の半導体光導波路108とが調芯され、接合されている。

【0024】

SOA−COS105のSOAチップ113は、PLC−PBSチップ106に比べ薄い。そのため、SOAチップ113をシリコンベンチ114に実装する。このようにすることで、PLC−PBSチップ106とSOA−COS105を接合するときの、接合部分の面積を広くすることが可能になり、PLC−PBSチップ106とSOA−COS105の接合に、十分な強度を得ることができる。

【0025】

本実施形態においては、図5(a)に示されるように、PLC−PBSチップ106とSOA−COS105は、チップごとに導波路の結合を行っている。さらに、本実施形態では、図5(b)に示されるように、ベースのシリコン基板501をそれぞれのチップで共有するシリコン基板テラス構造を用いることもできる。この形態においても、ベースのシリコン基板501は共有されているが、PLC−PBSチップ106とSOA−COS105はそれぞれの導波路が結合している。下記の全ての実施形態においても、この導波路結合の形態は適用可能である。

【0026】

(作用)

本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路において、入力INからの非偏光の光が、サーキュレータ101によってSOA−PLCハイブリッド集積偏波ダイバーシティ回路100へ伝播される。SOA−PLCハイブリッド集積偏波ダイバーシティ回路100からの光は、サーキュレータ101によって出力OUTに伝播される。

【0027】

一般的に、マッハツェンダー干渉計回路(MZI)は2本のアーム間にΔΦの位相差を有する。MZIアーム中で複屈折が起こる場合、TEモードおよびTMモードでの該位相差はそれぞれ独立して変化する。TEモードの該位相差ΔΦTEとTMモードの該位相差ΔΦTMとの差は、|ΔΦTE−ΔΦTM|=(2π/λ)B・Lで表される。ここで、λは波長、BはMZI中の複屈折率、LはMZIのアーム長である。|ΔΦTE−ΔΦTM|が(2n+1)π(n:整数)であるとき、MZIは入射された非偏光の光を2つの直交する光モード(即ち、TEモードとTMモード)へ分割する。そして、TEモードの光は一方の出力ポートへ出力され、TMモードの光は他方の出力ポートへ出力される。

【0028】

サーキュレータ101から伝播された非偏光の光は、MZI107によって互いに2つの直交モード(即ち、TEモードおよびTMモード)に分けられる。本実施形態にかかる構成においては、MZI107から出射されたTEモードの光は出力ポート109bへ伝播され、TMモードの光は出力ポート109aへ伝播される。出力ポート109aから出力したTMモードの光は、半波長板103によってTEモードの光に変更される。その結果、SOA−COS105にはTEモードの光のみが伝播される。

【0029】

一般的な半導体光増幅器は、例えば5量子井戸構造であり、12dBの飽和パワー、並びに概ね4dB以下の低い雑音指数を有する。半導体光増幅器自体の偏波依存利得は概ね10〜20dB程度である。半導体光増幅器に入射する光について、TEモードの光は19dB程度の小さい信号利得を有するが、TMモードの光は吸収され、−10〜0dB程度の利得を有する。

したがって、本実施形態のようにSOA−COS105にTEモードの光のみを伝播することにより、大きな利得を得ることができる上、SOA112の偏波依存利得(PDG)を低減することができる。

【0030】

上記のように、従来の偏波無依存SOAモジュールでは、空間的に分離した個別の光学部品を使用するため、モジュール全体としてサイズが比較的大きくなること、また、ハーフミラー等の光学部品が用いられるため使用者による光学部品間の光軸調整に手間がかかること等の理由から、該モジュールを大量生産し、他のデバイスに組み込む等の応用が難しいという問題があった。

【0031】

しかしながら、第1実施形態では、SOA−COS105にUターン部108bを設けてSOA−COS105の一端面から光の入出力を可能にし、偏波を分離し、該分離した偏波を統一するように構成されたPLC−PBSチップ106にSOA−COS105に対する入力光および出力光の双方を導波するようにPLC−SOAハイブリッド集積偏波ダイバーシティ回路を構成している。従って、従来のように、SOAへの入力経路と出力経路とを別個に設ける必要がなく、従来の偏波無依存SOAモジュールに比べ、モジュール(回路)のサイズを低減することができる。

【0032】

また、本実施形態では、ハーフミラー、レンズといった光学部品を用いず、PBSとしてのMZI107、および該MZI107のTMモード出力側の導波路に形成された半波長板103を有する平面光波回路としてのPLC−PBSチップ106を用いているので、使用者による光軸調整の煩わしさを必要としない。

【0033】

さらに、本実施形態では、偏波ダイバーシティ回路の構成要素であるPLC−PBSチップ106に対する設計マスクを一度作製してしまえば、従来からある半導体集積回路技術や平面光波回路技術を用いて大量生産が可能である。

【0034】

そして、本実施形態では、導波路チップであるSOA−COS105およびPLC−PBSチップ106の導波路を結合することで、単一の導波路デバイスを形成しているので、他のデバイスに組み込む等の応用が容易である。したがって、該回路は、商業的利用に非常に効果的である。

【0035】

また、本実施形態では、SOA−COS105にTEモードの光のみを伝播するため、SOA112の偏波依存利得(PDG)を低減することができる。

【0036】

(製造方法)

PLC−PBSチップ106では、シリコンや石英などの基板上に微細加工技術を組み合わせて、石英系の材料で光導波路が形成される。

【0037】

一般的に、平面光波回路(PLC)は、光ファイバ製造技術の応用である火炎直接堆積(FHD)法により、PLC基板(例えばシリコン基板)上に下部クラッド層およびコア層となるガラス粒子を堆積し加熱してガラス膜を溶融透明化する。この後、半導体集積回路製造技術であるフォトリソグラフィと反応性イオンエッチングで所望の光導波路パターンを形成し、再びFHD法により上部クラッドを形成する。

【0038】

複屈折は、石英系ガラス導波路に、局所的に加熱すること、またはUV照射することによりトリミングできる。適切に複屈折をトリミングすることで、石英系PLCチップに偏波ビームスプリッタ(PBS)が形成できる。

【0039】

ヒーター102は、MZI107における複屈折をトリミングするために、MZI107の2つのアーム上に形成される。ヒーター102でトリミングする間に、MZIの2つのアームの位相差が適切になるように測定される。PLC−PBSチップ106が、所定の光の波長(例えば、1530nm)において、所定の値(例えば、15dB)の偏光消光比を有するように設定される。

【0040】

図1に示されるように、半波長板103を形成するために、スリット104は、MZI107の2つの出力ポートとSOA−COS105との間に、石英系光導波路109と垂直に交わるように形成される。なお、スリット104は、ダイサー等を用いて形成され、図3Bに示されるように、光が反射するのを防ぐために、PLC−PBSチップ106の上面に対して所定の角度の傾斜をつけて形成される。

【0041】

本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路は、PLC−PBSチップ106の石英系光導波路109とSOA−COS105の半導体光導波路108とが互いに一つの接触面で接触され、調芯され、接合される。

【0042】

具体例として、図6を参照して、下記の製造方法のように本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路を製造する。

【0043】

(工程1)図6(a)に示されるように、石英系光導波路110a、110b、109a、109b、ヒーター102が形成されたPLC−PBSチップ106を準備する。試験光を石英系光導波路110a、110b側から伝播させ、ヒーター102に熱を加え適切にトリミングを行い、MZI107の2つのアームの位相差が適切になるように調整する。

【0044】

(工程2)PLC−PBSチップ106のSOA−COS105が接合されるファセットfPLCを光学研磨によって十分に小さな表面粗さの面に修正する。これにより半導体光導波路108a、108bと結合するPLC−PBSチップ106の断面が形成される。ダイサー等により、破線Cの部分にPLC−PBSチップ106の上面に対して垂直ではなく所定の角度をもつようにスリット104を形成する。半波長板103をスリット104中に形成する。半波長板103は、MZI107からTMモードの光を伝播する石英系光導波路側109aに形成する。

【0045】

(工程3)図6(b)に示されるように、直線部108aとUターン部108bを有する半導体光導波路とSOA112が形成されたSOA−COS105を準備する。SOA−COS105の半導体光導波路108aを劈開することにより、PLC−PBSチップ106と結合する接合面を形成する。そして、接触する石英系光導波路と半導体光導波路とを調芯し、PLC−PBSチップ106とSOA−COS105とを接着剤などで固定する。

【0046】

なお、上記工程1〜3に含まれる処理内容や工程の順序等は適宜調整してもよい。

【0047】

上記のSOA−PLCハイブリッド集積偏波ダイバーシティ回路で使用される材料の種類やパラメータ等は単なる例示であり、本実施形態において、ならびに下記の実施形態においても、それらに限定されるものではない。

【0048】

(第2実施形態)

(構成)

図7は、本発明の第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路700の構成を示す模式図である。第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路700は、第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路100の構成と略同一である。そのため、本実施形態には、当然、第1実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路が有する作用、効果が含まれる。ただし、PLC−PBSチップ106とSOA−COS105との導波路の結合において、モードフィールド径の違いによる光の伝播ロスや導波路の結合面における反射を低減するための構成701が用いられる。

【0049】

図8Aに構成701の詳細を示す。図8Aに示すように、構成701は、スポットサイズ変換器(SSC)802a、802bを有し、PLC−PBSチップ106とSOA−COS105との接合面f1に対して垂直ではなく所定の角度をもってそれぞれのチップの光導波路が接合されている。

【0050】

より詳細には、構成701は、コアの中心軸C3を有する直線状の石英系光導波路109a(109b)は、コアの中心軸C1を有する傾斜された石英系光導波路801a(801b)になめらかに接続される。図8Bに示すように、伝播する光が接合面f1に対して斜めに入射するように、中心軸C1は接合面f1に対して所定の角度θ1傾斜している。同様に、コアの中心軸C2を有する傾斜された半導体光導波路(即ち、SSC802a(802b))は、直線部の半導体光導波路108aになめらかに接続される。傾斜された半導体光導波路であるSSC802a(802b)は接合面f1に対して、所定の角度θ2傾斜している。

【0051】

図8Bは、接合面f1における接合部を一部拡大した図である。傾斜された石英系光導波路801a、801bにおける屈折率n1、中心軸C1と接合面f1の垂線とのなす角度θ1、傾斜されたSSC802a、802bにおける屈折率n2、中心軸C2と接合面f1の垂線とのなす角度θ2との間には、スネルの法則より、n1sinθ1=n2sinθ2、という関係がある。この関係を満たすように、傾斜角θ1、θ2が決定される。また、SOA−COS105側の接合面f1上には反射防止(AR)コート803がコーティングされている。なお、PLC側の傾斜角度θ1としては5〜9°、半導体導波路側の傾斜角度θ2としては12°〜17°が好ましい。

【0052】

SSC802a、802bは、PLC−PBSチップ106のSOA−COS105の接合面近傍の石英系光導波路801a、801bのモードフィールドと半導体光導波路108aのモードフィールドとをマッチさせるようにテーパー状の形状を有する光導波路(幅広フレアー型SSC)である。SSC802a、802bは、図8Bに示されるように、部位(i)における幅を保ったまま部位(ii)において曲げられ、部位(iii)においてテーパー状に幅が広くなり、部位(iv)において幅が広がった状態で平行に形成される。本実施形態では、SSC802a、802bは、SOA−COS105の側に形成されているが、PLC−PBSチップ106の側に形成してもよい。SSC802a、802bによって、それぞれの導波路の結合部における結合ロスを低減し、高い結合効率を得ることができる。

【0053】

(作用)

PLC−PBSチップ106における石英系ガラス等の石英系光導波路の屈折率n1に対して、SOA−COS105におけるInP等の半導体光導波路の屈折率n2は異なるため、それぞれの導波路のモードフィールド(電界分布)が互いに異なる。例えば、石英系光導波路のモードフィールド径は概ね3〜8μmであり、InP半導体光導波路のモードフィールド径は概ね1〜2μmである。そのため、本実施形態は、PLC−PBSチップ106における石英系光導波路とSOA−COS105の半導体光導波路を結合する際に、モードフィールド径の違いによる光の伝播ロスや接合面における反射を低減するための構成701を用いる。

【0054】

本実施形態にかかる構成701は、スポットサイズ変換器(SSC)802a、802bを用いてモードフィールド径の違いを修正することができる。また、それぞれのチップの光導波路が所定の角度をもって結合されることで反射を低減することができる。さらに、SOA−COS105側の接合面f1(PLC−PBSチップ106とSOA−COS105との接合面)に反射防止(AR)コート803をコーティングすることで、反射により生じる光の伝播ロスを低減することができる。

【0055】

本実施形態では、上記のような構成をとることにより、PLC−PBSチップ106における石英系光導波路とSOA−COS105の半導体光導波路を結合する際に、モードフィールド径の違いによる光の伝播ロスや接合面における反射を低減することができる。

【0056】

図8Aにおいて、光は、直線部の石英系光導波路109から傾斜された光導波路801a、801bへ入射される。第1実施形態のように、光は、接合面f1に対して垂直に入射せず、所定の角度をもって入射される。光は所定の角度で接合面f1へ入射するため、接合面f1による反射光は再度傾斜された光導波路801a、801bへ戻ることは難しい。よって、石英系光導波路109への接合面f1における反射戻り光は低減される。

【0057】

同様に、光は、SOA−COS105中を伝播しPLC−PBSチップ106へ戻る場合、傾斜された半導体光導波路(即ち、SSC802a、802b)へ入射される。第1実施形態のように、光は、接合面f1に対して垂直に入射せず、所定の角度をもって入射される。光は所定の角度で接合面f1へ入射するため、接合面f1による反射光は再度SSC802a、802bへ戻ることは難しい。よって、SSC802a、802bへの接合面f1における反射戻り光は低減される。

【0058】

(製造方法)

第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の製造方法は、第1実施形態にかかる該回路の製造方法と略同一である。ここで、図9の各図には、構成701付近のみを詳細に記載しているが、その他の部分については、第1実施形態にかかる該回路の構成と略同一であるため省略している。

【0059】

(工程1)

石英系光導波路110、109、曲げられた石英系光導波路701、SOA−COS105との接合面となるファセットfPLCに垂直な方向に対してある角度θ1だけ水平方向に傾いている石英系光導波路801、および、ヒーター102が形成されたPLC−PBSチップ106を準備する。試験光を石英系光導波路110側から伝播させ、石英系光導波路109側において、ヒーター102を通過した光を測定する。測定の間、ヒーター102に熱を加え適切にトリミングを行い、MZI107の2つのアームの位相差が適切になるように調整する。

【0060】

(工程2)

図9(a)に示されるように、PLC−PBSチップ106の余分な部分を破線Aに沿って切断する。すなわち、石英系光導波路801a、801bは角度θ1の直線部分の任意の点において、ファセットfPLCを形成するように、PLC−PBSチップ106の端部をダイサー等により切断する。切断して形成されるファセットfPLCは光学研磨によって十分に小さな表面粗さの面に修正される。以上により半導体光導波路802a、802bと結合するPLC−PBSチップ106の断面が形成される。ダイサー等によりPLC−PBSチップ106の上面に対して垂直ではなく所定の角度をもつスリット104を形成する。半波長板103をスリット104中に形成する。半波長板103は、MZI107からTMモードの光を伝播する石英系光導波路109a側に形成する。

【0061】

(工程3)

図9(b)に示されるように、直線部108aの半導体光導波路、テーパー状の半導体光導波路である所定の角度(接合面f1の垂線と中心軸C2とのなす角度がθ2となるように)に傾斜されたSSC802a、802b、およびSOA112が形成されたSOA−COS105を準備する。SOA−COS105は、半導体光導波路802a、802bの出射角度がθ2になるように劈開され、PLC−PBSチップ106と結合するSOA−COS105のファセットfSOAが形成される。直線部半導体光導波路108aとSOA112は埋込メサ構造により形成され、Uターン部半導体光導波路はハイメサ構造により形成されており、SOA−COS105のファセットfSOAにARコート803がコーティングされている。

【0062】

(工程4)

図9(c)に示されるように、それぞれのチップの光導波路を調芯し、それぞれのチップを接着剤などで固定する。導波路の接合面f1はPLC−PBSチップ側のファセットfPLCとSOA−COS側のファセットfSOAの2つが対向して、石英系光導波路801aと半導体導波路802a、石英系光導波路801bと半導体導波路802bがそれぞれ光学的に結合する空間で形成される。

なお、上記工程1〜4に含まれる処理内容や工程の順序等は適宜調整してもよい。

【0063】

(第3実施形態)

(構成)

図10は、本発明の第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路1000の構成を示す模式図である。第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路1000は、第1実施形態および第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の構成と略同一である。そのため、本実施形態には、第1実施形態および第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路が有する作用、効果が含まれる。ただし、本実施形態においては、SOA−COS1001に光導波路の折り返し部を形成するのではなく、UターンPLCチップ1002にUターン石英系光導波路1003を形成し、SOA112により増幅した光をMZIへ戻すようにしている。そして、SOA112はSOA−COS1001の半導体光導波路の直線部に形成されている。すなわち、第3実施形態においては、PLC−PBSチップ106から伝播された光は、SOA−COS1001に形成されたSOA112で増幅され、UターンPLCチップ1002に形成されたUターン石英系光導波路1003で折り返され、再びSOA−COS1001に形成されたSOA112で増幅され、PLC−PBSチップ106へ戻る。

【0064】

本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路においても、PLC−PBSチップ105とSOA−COS1001との接合部およびSOA−COS1001とUターンPLCチップ1002との接合部におけるそれぞれのチップの光導波路は、第2実施形態にかかる該回路の特徴のように、コアサイズの違いによる光の伝播ロスや接合面における反射を低減するための構成701を用いている。

【0065】

(作用)

上記したように、大きい比屈折率差の光導波路であるほど折り返し部の曲率半径を小さくすることができ、その結果、回路全体のサイズを低減することができる。しかしながら、第2実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路のように、SOAに適した埋込メサ構造の半導体導波路と、曲率半径の小さいUターンに適したハイメサ構造の半導体導波路を結合して同じチップ内で作製することは、必ずしも容易ではない。

【0066】

Uターン構造をなくし、埋込メサ構造の半導体導波路のみでSOA−COSを構成するほうが、容易に導波路を形成することができる。第2実施形態のSOA−PLCハイブリッド集積偏波ダイバーシティ回路に比べ、本実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路は、全体のサイズが少し大きくなるが、SOA−COSの作製が容易になり、偏波ダイバーシティ回路の実現性が高まる。

【0067】

(製造方法)

第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路の製造方法は、第1実施形態および第2実施形態にかかる該回路の製造方法と略同一である。ここで、図8の各図には、PLC−PBSチップ106、SOA−COS1001およびUターンPLCチップ1002の接合部における構成701付近のみを詳細に記載している。その他の部分については、第1実施形態および第2実施形態にかかる該回路の構成と略同一であるため省略している。

【0068】

(工程1)

石英系光導波路110、109、所定の角度に傾斜された石英系光導波路801、ヒーター102が形成されたPLC−PBSチップ106を準備する。試験光を石英系光導波路110側から伝播させ、石英系光導波路109側において、ヒーター102を通過した光を測定する。測定の間、ヒーター102に熱を加え適切にトリミングを行い、MZI107の2つのアームの位相差が適切になるように調整する。また、Uターン状の石英系光導波路1003、石英系光導波路109、曲げられた石英系光導波路801、所定の角度に傾斜された石英系光導波路801、が形成されたUターンPLCチップ1002を準備する。

【0069】

(工程2)

図11(a)に示されるように、PLC−PBSチップ106およびUターンPLCチップ1002の余分な部分を破線AおよびA’に沿って切断する。すなわち、石英系光導波路801a、801bは角度θ1の直線部分の任意の点において、ファセットfPLCを形成するように、PLC−PBSチップ106およびUターンPLCチップ1002の端部をダイサー等により切断する。切断して形成されるファセットfPLCは光学研磨によって十分に小さな表面粗さの面に修正される。以上により半導体光導波路802a、802bと結合するPLC−PBSチップ106、およびUターンPLCチップ1002の断面が形成される。また、ダイサー等によりPLC−PBSチップ106の上面に対して垂直ではなく所定の角度をもつスリット104を形成する。半波長板103をスリット104中に形成する。半波長板103は、MZI107からTMモードの光を伝播する石英系光導波路109a側に形成する。

【0070】

(工程3)

図11(b)に示されるように、直線部108aの半導体光導波路、テーパー状の半導体光導波路である傾斜されたSSC802a、802b、およびSOA112が形成されたSOA−COS1001を準備する。SOA−COS1001は、半導体光導波路802a、802bの出射角度がθ2(図8B参照)になるように劈開され、PLC−PBSチップ106およびUターンPLCチップ1002と結合するSOA−COS1001のファセットfSOAが形成される。その後、SOA−COS1001の両方の切断面であるファセットfSOAにARコート803(図8B参照)をコーティングする。

【0071】

(工程4)

図11(c)に示されるように、それぞれのチップの光導波路を調芯し、それぞれのチップを接着剤などで固定する。導波路の接合面f1はPLC−PBSチップおよびUターンPLCチップ側のファセットfPLCとSOA−COS側のファセットfSOAの2つが対向して、石英系光導波路801aと半導体導波路802a、石英系光導波路801bと半導体導波路802bがそれぞれ光学的に結合する空間で形成される。

なお、上記工程1〜4に含まれる処理内容や工程の順序等は適宜調整してもよい。

【0072】

(実施例)

図12は、SOAの偏波依存利得(PDG)を測定するために、2種類のPDG測定構成を示す。図12は、調整可能な光源(TLS)1201、エルビウム添加光ファイバ増幅器(EDFA)1202、偏波コントローラ(PC)1203、減衰器(ATT)1204、入力側光スイッチ1205、光スペクトラムアナライザ(OSA)1206、光パワーメータ(OPM)1207、10:1スプリッタ1208、アイソレータ1209、出力側光スイッチ1210、基準構成1211、および第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路構成1212を示す。構成1211は、2つのストレート型光導波路を有するST−PLCチップとSOAを有するSOA−COS、ならびにUターン型光導波路を有するU−PLCチップとが接合された構成をとる。構成1212に比べ、サーキュレータと偏波ビームスプリッタを有しない。

【0073】

TLS1201から構成1211に光を入射する場合、該構成1211はPDCを用いないため、構成1211を伝播する光はそのまま、入力側光スイッチ1205から出力側光スイッチ1210へと一方向に伝播する。構成1211におけるSOAのPDGを調べるために、TLS1201からTEモードの光(中心波長λ=1550nm)を入射させた場合の測定結果を図13A(a)に、TLS1201からTMモードの光を入射させた場合の測定結果を図13A(b)に示す。なお、図13Aの各図のスケールは、横軸が1549.5〜1550〜1550.5(nm)、縦軸が−60〜0〜+10(dBm)であり、上側の太線のスペクトルが構成1211および1211を通過後の出力光のスペクトル、下側のスペクトルが入力光のスペクトルである。

【0074】

また、構成1212におけるSOAのPDGを調べるために、TLS1201からTEモードの光(中心波長λ=1550nm)を入射させた場合の測定結果を図13A(c)に、TLS1201からTMモードの光を入射させた場合の測定結果を図13A(d)に示す。なお、構成1212において、上記θ1を15°、θ2を7°とすることで、伝播光のリターンロスは−50dB以下に低減された。

【0075】

構成1211において、TEモードの光の場合は、5.8dBの増幅利得が得られたが、TMモードの光の場合は、−5.3dBと負の増幅利得が得られた。構成1212において、TEモードの光の場合は、6.3dBの増幅利得が得られ、TMモードの光の場合は、4.4dBの増幅利得が得られた。

【0076】

この結果から、TEモードの光は、構成1211および構成1212にかかわらず、即ちPDCの構成を有するか否かにかかわらず、SOAによる光増幅利得が得られた。しかしながら、TMモードの光について、構成1212ではSOAによる光増幅利得が得られたが、構成1211ではSOAによる負の光増幅利得(即ち、吸収)が得られた。

【0077】

よって、構成1211の偏波依存利得(PDG)は11.1dBであった。一方、構成1212のPDGは1.9dBであった。本発明の第3実施形態にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路(構成1212)を用いることで、PDGを大きく低減できた。

【0078】

図13Bに、入射光の中心波長を1530、1540、1550nmで測定した場合における、構成1211のPDG1301の変化および構成1212のPDG1302の変化を示す。構成1211では、PDGが11.1〜22.9dBと大きい値をとった。一方、構成1212では、PDGが1.2dBと構成1211の値に比べ大きく低減した。このことから、本実施例にかかるSOA−PLCハイブリッド集積偏波ダイバーシティ回路は、SOAのPDGを低減するという効果があることが示された。

【符号の説明】

【0079】

100 SOA−PLCハイブリッド集積偏波ダイバーシティ回路

101 サーキュレータ

102 ヒーター

103 半波長板

104 スリット

105 SOA−COS

106 PLC−PBSチップ

107 MZI

108 半導体光導波路

109 石英系光導波路

109a MZI107の出力ポート

109b MZI107の出力ポート

110 石英系光導波路

110a MZI107の入力ポート

110a MZI107の出力ポート

111 カプラ

112 SOA

113 SOAチップ

114 シリコンベンチ

【特許請求の範囲】

【請求項1】

互いに導波路を結合したPLC−PBSチップとSOA−COSとを備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路であって、

前記PLC−PBSチップは、

第1および第2の光導波路と、

入力された光をTMモードの光およびTEモードの光へ分割し、前記分割されたTMモードの光を前記第1の光導波路へ出力し、前記分割されたTEモードの光を前記第2の光導波路へ出力するマッハツェンダー干渉計回路と、

前記TMモードの光が伝播する第1の光導波路中に形成された偏波回転機構とを含み、

前記SOA−COSは、

前記第1の光導波路に接続された第3の光導波路と、

前記第2の光導波路に接続された第4の光導波路と、

少なくとも一方の前記第3および第4の光導波路に形成されたSOAとを含み、

前記第3の光導波路と、前記第4の光導波路のそれぞれ前記第1の光導波路および前記第2の光導波路と接続しないもう一端同士は、Uターン部光導波路で接続されていることを特徴とするSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項2】

前記Uターン部光導波路は、前記SOA−COS上に形成されていることを特徴とする請求項1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項3】

前記第1および第2の光導波路が埋込メサ構造を有し、前記Uターン部光導波路がハイメサ構造を有することを特徴とする請求項2に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項4】

前記SOA−COSと導波路を結合したUターンPLCチップをさらに備え、前記Uターン部光導波路は、前記UターンPLCチップ上に形成されていることを特徴とする請求項1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項5】

2つのチップの接合面において、前記第1から第4の光導波路の少なくとも1つの光導波路がスポットサイズ変換器を含むことを特徴とする請求項1から4のいずれか1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項6】

2つのチップの接合面において、接合される前記光導波路が接合面に対していずれも傾斜を有し、

前記傾斜された光導波路同士がが、前記接合面に対してそれぞれ第1の角度および第2の角度を有して接合されていることを特徴とする請求項1から4のいずれか1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項7】

2つのチップの接合面に、反射防止コートが形成されていることを特徴とする請求項1から6のいずれか1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項1】

互いに導波路を結合したPLC−PBSチップとSOA−COSとを備えるSOA−PLCハイブリッド集積偏波ダイバーシティ回路であって、

前記PLC−PBSチップは、

第1および第2の光導波路と、

入力された光をTMモードの光およびTEモードの光へ分割し、前記分割されたTMモードの光を前記第1の光導波路へ出力し、前記分割されたTEモードの光を前記第2の光導波路へ出力するマッハツェンダー干渉計回路と、

前記TMモードの光が伝播する第1の光導波路中に形成された偏波回転機構とを含み、

前記SOA−COSは、

前記第1の光導波路に接続された第3の光導波路と、

前記第2の光導波路に接続された第4の光導波路と、

少なくとも一方の前記第3および第4の光導波路に形成されたSOAとを含み、

前記第3の光導波路と、前記第4の光導波路のそれぞれ前記第1の光導波路および前記第2の光導波路と接続しないもう一端同士は、Uターン部光導波路で接続されていることを特徴とするSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項2】

前記Uターン部光導波路は、前記SOA−COS上に形成されていることを特徴とする請求項1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項3】

前記第1および第2の光導波路が埋込メサ構造を有し、前記Uターン部光導波路がハイメサ構造を有することを特徴とする請求項2に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項4】

前記SOA−COSと導波路を結合したUターンPLCチップをさらに備え、前記Uターン部光導波路は、前記UターンPLCチップ上に形成されていることを特徴とする請求項1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項5】

2つのチップの接合面において、前記第1から第4の光導波路の少なくとも1つの光導波路がスポットサイズ変換器を含むことを特徴とする請求項1から4のいずれか1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項6】

2つのチップの接合面において、接合される前記光導波路が接合面に対していずれも傾斜を有し、

前記傾斜された光導波路同士がが、前記接合面に対してそれぞれ第1の角度および第2の角度を有して接合されていることを特徴とする請求項1から4のいずれか1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【請求項7】

2つのチップの接合面に、反射防止コートが形成されていることを特徴とする請求項1から6のいずれか1に記載のSOA−PLCハイブリッド集積偏波ダイバーシティ回路。

【図1】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図9】

【図10】

【図11】

【図12】

【図13A】

【図13B】

【図14】

【図2】

【図3A】

【図3B】

【図4】

【図5】

【図6】

【図7】

【図8A】

【図8B】

【図9】

【図10】

【図11】

【図12】

【図13A】

【図13B】

【図14】

【公開番号】特開2012−163614(P2012−163614A)

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願番号】特願2011−21814(P2011−21814)

【出願日】平成23年2月3日(2011.2.3)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

【公開日】平成24年8月30日(2012.8.30)

【国際特許分類】

【出願日】平成23年2月3日(2011.2.3)

【出願人】(000005290)古河電気工業株式会社 (4,457)

【Fターム(参考)】

[ Back to top ]