SiC半導体のイオン注入層及びその製造方法

【課題】 結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層を提供する。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

【解決手段】 本発明に係るSiC半導体1のイオン注入層2は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっている。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明は、SiC半導体のイオン注入層及びそのイオン注入層を製造するイオン注入層製造方法に関する。

【0002】

【従来の技術】近年、炭化珪素(SiC)あるいは窒化ガリウム(GAN)等の軽元素で構成される化合物半導体の研究が盛んに行なわれている。これらの化合物半導体は、軽元素によって構成されているため、結合エネルギーが強く、その結果、エネルギーの禁制帯幅(バンドギャップ)、絶縁破壊電界、熱伝導度が大きいことが特徴である。このワイドバンドギャップの特徴を活かした、高効率・高耐圧パワーデバイス、高周波パワーデバイス、高温動作デバイスが注目を集めている。これらの半導体デバイスは、イオン注入法によって製造される場合が多い。

【0003】

【発明が解決しようとする課題】しかしながら、従来のSiC半導体は、{0001}面に対する傾きが10°以内の面方位を有するSiCにイオンを注入して製造されていたが、イオン注入工程においてSiC結晶が乱れるという問題点があった。そして、イオン注入工程において生じた結晶の乱れは、その後のアニール工程においても回復することが困難であった。イオン注入時の結晶の乱れを最小にする手法として、加熱した試料にイオンを注入するホットインプランテイションと呼ばれる方法が採用される場合もあるが、この方法では、イオン注入装置の試料ホルダ−を500℃程度の高温に均一に加熱する必要があるので、汎用のイオン注入装置を使用することができない上、イオン注入の後に行なわれる結晶回復のためのアニール工程において、1000℃を超える温度で熱処理する必要があった。こうした熱処理は、予期しない不純物の拡散をもたらすことがあり、また、プロセス途中で必要となる高温の処理は、プロセスの自由度、デバイス設計の自由度を制限することとなる。さらに、高温処理により結晶表面が荒れるという問題点もあった。

【0004】そこで、本発明は上記課題を解決し、結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層、及びイオン注入層製造方法を提供することを目的とする。

【0005】

【課題を解決するための手段】本発明に係るSiC半導体のイオン注入層は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっていることを特徴とする。

【0006】このように、イオン注入層が{03−38}面から10°以内の角度αのオフ角を有する面方位に広がることによって、結晶の乱れが少ないイオン注入層を実現することができる。

【0007】また、上記SiC半導体のイオン注入層は、オフ角αは5°以内であることが好ましく、さらに、オフ角は3°以内であることが好ましい。イオン注入層が広がっている面の面方位が{03−38}面に近くなるほど、SiC半導体のイオン注入層の結晶の乱れが少なくなる。

【0008】本発明に係るSiC半導体製造方法は、{03−38}面、又は{03−38}面に対して約10°以内のオフ角αだけ傾いた面、を露出させたSiC単結晶からなる種結晶上に、4H型ポリタイプのSiC単結晶を成長させるSiC結晶成長工程と、SiC結晶成長工程において成長されたSiC結晶にイオンを注入するイオン注入工程と、を備えることを特徴とする。

【0009】このようにSiC結晶成長工程において、{03−38}面、又は{03−38}面に対して約10°以内のオフ角αだけ傾いた面、を露出させたSiC単結晶からなる種結晶上に4H型ポリタイプのSiC単結晶を成長させたSiC単結晶は、{03−38}面に対する傾きが10°以内の面方位を有する。そして、このSiC単結晶に、イオン注入工程においてイオンを注入することにより、結晶の乱れが少ないSiC半導体を製造することができる。従来は、{0001}面に対する傾きが10°以内の面方位を有するSiCにイオンを注入することによって製造されていたが、{0001}面は六方最密面であることから、不純物イオンが注入された場合に結晶がストレスを受ける。このため、イオン注入によって結晶格子が大きく乱れる原因となっていた。発明者らは、SiCの面方位について鋭意検討した結果、{03−38}面、及び{03−38}面に対する傾きが10°以内の面方位がイオン注入の際のストレスが少ない面であることを見出した。これは、{03−38}面は、最密面から離れた面でありながら原子の結合手が比較的周期的に現れている面であるためであると考えられる。従来は、イオン注入工程における結晶の乱れを最小限にするため、ホットインプランテーションを呼ばれる手法が採用されていたが、本発明によれば室温でイオン注入を行なっても、結晶の乱れを低減できるので、従来のように高温処理を行なう必要がなく、結晶表面が荒れるという問題を解消することができる。

【0010】また、上記SiC半導体製造方法は、SiC結晶成長工程において、{03−38}面から傾けれらるオフ角αは、5°以内であることが好ましい。さらに、オフ角は3°以内であることが好ましい。すなわち、種結晶の表面が{03−38}面に近くなるほど、成長されるSiC結晶の面方位は{03−38}面に近くなり、SiC半導体の結晶の乱れが少なくなる。

【0011】また、上記SiC半導体製造方法は、イオン注入工程によってイオンが注入されたSiC結晶を1000℃以下の温度によって熱処理するアニール工程を、さらに備えることを特徴としても良い。

【0012】本発明によれば、製造されたイオン注入層は結晶の乱れが少ないので、結晶を回復させるアニール工程における熱処理の温度を従来(1000℃)より低く設定することができ、結晶表面の荒れを低減したSiC半導体を実現できる。

【0013】

【発明の実施の形態】以下、図面と共に本発明に係るSiC半導体のイオン注入層及びイオン注入層製造方法の好適な実施形態について詳細に説明する。ここで、格子面の記号の説明をすると、負の指数については、結晶学上、”−”(バー)を数字の上に付けることになっているが、明細書作成の都合上、数字の前に負号を付けることにする。なお、図面の説明においては同一要素には同一符号を付し、重複する説明を省略する。

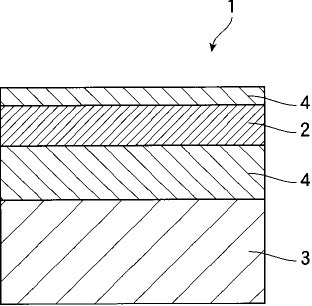

【0014】(第1実施形態)図1は、第1実施形態に係るイオン注入層2が形成されたSiC半導体1を示す図である。第1実施形態に係るイオン注入層は、窒素(N)イオンが注入されたn型層が4H型SiC層3の{03−38}面に広がっているイオン注入層2である。

【0015】第1実施形態に係るイオン注入層2の製造方法について説明する。まず、4HSiC{03−38}の面方位を有する基板3にアルミ(Al)ドープp型4HSiC層4をエピタキシャル成長させる。ここで、用いる基板3は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製する。基板3は全てp型で、ショットキー障壁の容量−電圧特性から求めた実効アクセプタ密度は5〜8×1018/cm3、厚さは360〜420μmである。CVD法によるp型SiC層4の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.5sccm、C3H8については0.40sccm、Al(CH3)3については8×10-4sccm、H2については3.0slmとし、基板温度1520℃で90分間成長させる。このような成長条件によって成長されたp型SiC層4のアクセプタ密度は6〜8×1015/cm3、膜厚は5μmである。

【0016】このようにして作製したp型SiC層4にNイオンを注入し、イオン注入層2を形成する。Nイオン注入は140keV、80keV、50keV、25keVの4段階で行い、総ドーズ量は5×1014〜2×1016/cm2である。各注入エネルギーのドーズ比を0.48(140keV)、0.26(80keV)、0.18(50keV)、0.08(25keV)とすることによって、深さ約0.4μmのボックスプロファイルを形成する。イオン注入は室温、あるいは500℃で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中で1000〜1700℃、30分の条件で行う。

【0017】次に、上記製造方法によって製造されたイオン注入層2の特性について説明する。ここでは、{03−38}面方位を有するイオン注入層(以下、「{03−38}面方位イオン注入層」という)2の特性を、{0001}面から8°のオフ角を有する面方位に広がるイオン注入層(以下、「{0001}面方位イオン注入層」という)の特性と比較して説明する。{0001}面方位イオン注入層の製造方法は、上記した{03−38}面方位イオン注入層2の製造方法と基本的に同じであるが、p型SiC層4を成長させる際に導入するAl(CH3)3の流量が2×10-4sccmである点が異なる。

【0018】まず、イオン注入層の結晶性を評価するために、ラザフォード後方散乱(RBS)のチャネリング測定を行った。RBS測定は、エネルギー2.0MeVのHe2+イオンを用い、散乱角170°の条件で測定した。図2は、トータルドーズ量5×1015/cm2の試料(室温注入、1500℃のアニール前後)のRBSスペクトルを示す図である。注入直後の状態では{0001}面方位イオン注入層、{03−38}面方位イオン注入層2とも、表面近傍におけるチャネリング時の後方散乱イールド(yield)がランダム散乱時のイールドと一致しており、注入層がほぼ完全な非晶質になっていることが分かる。1500℃のアニールを行った試料では、結晶性が改善され、チャネリング時の散乱イールド(アラインスペクトル)がランダムスペクトルより低下している。しかしながら、その結晶性回復の度合いには大きな面方位依存性が見られた。{0001}面方位イオン注入層では、1500℃のアニールを施してもアラインスペクトルの散乱イールドはかなり大きく、注入層領域(表面の約0.4μm)ではランダムイールドの20〜40%にも達する。したがって、{0001}面方位イオン注入層では、アニール時の再結晶化が不十分で、多くの結晶欠陥が残存することが分かる。実際、この試料を断面透過電子顕微鏡(TEM)観察によって分析すると、再結晶化した4HSiC層の中に、3C−SiC粒が混在すること、またこの3C−SiC粒の周辺では4HSiCも一部多結晶化し、多くの粒界や転位が形成されていることが判明した。一方、{03−38}面方位イオン注入層2では、アニールによってチャネリング時の散乱イールドが非常に小さくなり(ランダム時の1.2%)、未注入試料と同程度まで結晶性が回復していることが分かる。断面TEM観察でも、{03−38}面方位イオン注入層2では、3C−SiCの混在や粒界、転位の発生が観測されず、優れた再結晶化が進行することが分かった。これは、{0001}面方位イオン注入層では再結晶化の過程で原子配列が一義的に決まらないサイトが多数存在するために、原子のミスアライメントが多く発生するのに対し、{03−38}面方位イオン注入層2ではSiC特有の周期的ポテンンシャルが表面に現れているために、完全な非晶質からの再結晶化であっても、非常にスム−ズに、欠陥の発生を伴わない再結晶化が進むためであると考えられる。

【0019】次に、イオン注入層の電気的性質をファン・デア・ポー(van der Pauw)法によって評価した。イオン注入層を約10mm角に切りだし、注入層の電気的分離を行うために、その中央部8mm角が残るよう反応性イオンエッチングによってメサ構造を作製した。このメサ構造の4隅にニッケル(Ni: 厚さ180nm)を蒸着し、950℃、20分間の熱処理を行った。この試料のシート抵抗、キャリヤ密度、移動度をファン・デア・ポー法、およびホール効果測定によって調べた。図3は、室温、あるいは500℃の高温でNイオンを注入し、1500℃でアニールした試料のシート抵抗の注入ドーズ量依存性を示す図である。{0001}面方位イオン注入層の場合、シート抵抗の最小値は室温注入で710Ω/□(ドーズ量:8×1014/cm2)、500℃の高温注入で420Ω/□(ドーズ量:8×1014/cm2)である。特に、室温注入では、ドーズ量が1×1015/cm2を越えるとシート抵抗が増大してしまう。この原因は、上述のように、注入によって完全な非晶質領域が形成されてしまうと、1500℃のアニールを行っても多くの欠陥が残留して注入イオンの活性化を妨げるからであると考えられる。一方、{03−38}面方位イオン注入層2では、シート抵抗の最小値は室温注入で120Ω/□(ドーズ量: 5×1015/cm2)、500℃の高温注入で86Ω/□(ドーズ量: 1×1016/cm2)となり、室温注入、高温注入ともにシート抵抗の大幅な低減が可能であることが分かった。デバイスの工業化を考えると、イオン注入装置の製造、運転コスト、注入プロセス時のスループットの点で室温注入のメリットは大きい。したがって、4HSiC{03−38}面を用いることによって、室温注入でも低いシート抵抗が得られた意義は非常に大きい。

【0020】次に、ドーズ量を5×1015/cm2に固定し、注入層における注入イオンの電気的活性化率のアニール温度依存性を調べた結果を図4に示す。SiC中のNドナーは室温において必ずしも完全にイオン化して自由電子を供給していないので、ホール効果測定を室温から300℃の高温まで行い、出払い領域のシートキャリヤ密度をドーズ量で割った値を電気的活性化率と定義した。図4から分かるように{0001}面方位イオン注入層では、アニール温度を1700℃まで上昇させても活性化率はあまり高くならない。特に、室温注入の場合には、活性化率が10%以下に留まっている。しかしながら、{03−38}面方位イオン注入層2では、室温注入でも、高い活性化率が得られることが分かる。室温注入、1200℃アニールの試料でも84%という高い活性化率を達成でき、1500℃アニールを施すことによってほぼ100%の活性化率が得られる。ちなみに、室温注入、1200℃アニールの試料で比較すると、{0001}面方位イオン注入層ではシート抵抗が2230Ω/□、{03−38}面方位イオン注入層2ではシート抵抗が180Ω/□となり、一桁以上の改善が見られた。{03−38}面方位イオン注入層2では、再結晶化の速度が非常に速く、1200℃程度の比較的低温でも良好な結晶性回復特性を示すものと思われる。このように、{03−38}面方位イオン注入層2を用いると、低温プロセスで十分低抵抗のn型層を形成でき、かつオーム性電極の接触抵抗率も低減できるので、pinダイオードのカソ−ド、MOSFET、MESFETやJFETなどのn型ソース、ドレイン領域の形成に有効であり、高性能SiCデバイスの実現につながる。

【0021】(第2実施形態)第2実施形態に係るイオン注入層は、燐(P)イオンが注入されたn型層が4H型SiCの{03−38}面に広がっているイオン注入層である。第2実施形態に係るイオン注入層が形成されるSiC半導体の構造は、第1実施形態で説明したSiC半導体と同様に、基板に成長されたSiC層にイオン注入層が形成されたものである。従って、ここでは、図示は省略する。

【0022】第2実施形態に係るイオン注入層の製造方法について説明する。まず、4HSiC{03−38}の面方位を有する基板にホウ素(B)ドープp型4HSiC層をエピタキシャル成長させる。ここで、用いる基板は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製する。基板は全てp型で、ショットキー障壁の容量−電圧特性から求めた実効アクセプタ密度は6〜8×1018/cm3、厚さは380〜420μmである。CVD法によるp型4HSiC層の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C2H4については0.66sccm、B2H6については6×10-6sccm、H2については3.0slmとし、基板温度1500℃で110分間成長させる。このような成長条件によって成長されたp型SiC層のアクセプタ密度は3〜5×1015/cm3、膜厚は5μmである。

【0023】このようにして作製したSiCエピタキシャルウェーハにPイオンを注入し、イオン注入層を形成する。Pイオン注入は180keV、120keV、80keV、40keV、20keVの5段階で行い、総ドーズ量は5×1015cm-2である。各注入エネルギーのドーズ比を0.42(180keV)、0.21(120keV)、0.13(80keV)、0.10(40keV)、0.04(20keV)とすることによって、深さ約0.3μmのボックスプロファイルを形成する。イオン注入は室温、あるいは800℃で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中で1000〜1700℃、30分の条件で行う。

【0024】次に、上記製造方法によって製造されたイオン注入層の特性について説明する。ここでは、{0001}面から8°のオフ角を有する面方位に広がるイオン注入層(以下、「{0001}面方位イオン注入層」という)の特性と比較して、{03−38}面方位を有するイオン注入層(以下、「{03−38}面方位イオン注入層」という)の特性を説明する。{0001}面方位イオン注入層の製造方法は、上記した{03−38}面方位イオン注入層の製造方法と基本的に同じであるが、p型SiC層を成長させる際に導入するB2H6の流量が2×10-6sccmである点が異なる。

【0025】イオン注入層の電気的性質をファン・デア・ポー(van der Pauw)法によって評価した。イオン注入層を約10mm角に切りだし、注入層の電気的分離を行うために、その中央部8mm角が残るよう反応性イオンエッチングによってメサ構造を作製した。このメサ構造の4隅にニッケル(Ni: 厚さ180nm)を蒸着し、950℃、20分間の熱処理を行った。

【0026】図5は、室温、あるいは800℃の高温でイオン注入を行ったイオン注入層のシート抵抗のアニール温度依存性を示す図である。シート抵抗はアニール温度の上昇と共に単調に減少するが、そのシート抵抗の絶対値に大きな面方位依存性が観測された。{0001}面方位イオン注入層の場合、高温注入、1600〜1700℃のアニールによって94〜97Ω/□という低いシート抵抗が得られたが、室温注入ではアニール温度を1700℃まで上げてもシート抵抗は285Ω/□までしか低減できなかった。これに対して{03−38}面方位イオン注入層の場合は、室温注入、1200℃アニールでも102Ω/□、室温注入、1500℃アニールでは67Ω/□という低い値が得られた。また、高温注入によって得られた{03−38}面方位イオン注入層では、1200℃アニールによって56Ω/□という優れた値を得た。このように、Pイオン注入の場合も、4HSiC{03−38}面を用いると、低い注入温度、あるいは低いアニール温度で良好な低抵抗n型層が形成できることが分かった。これは、4HSiC{03−38}では、再結晶化の速度が非常に速く、比較的低温でも良好な結晶性回復特性を示すからであると考えられる。

【0027】次に、前述のイオン注入層(10mm角)を用いてオーム性電極の接触抵抗率の評価を行った。注入層表面に幅20μm、長さ200μmの短冊状の電極を間隔10〜200μmで配置し、TLM法によって電極の接触抵抗率を測定した。図6は、図5に対応する接触抵抗率の注入層アニール温度依存性を示す図(電極の熱処理は950℃で固定)である。接触抵抗率の面方位依存性、注入温度あるいはアニール温度依存性は、図5のシート抵抗と同様の傾向を示した。すなわち、{0001}面方位イオン注入層の場合、1×10-6Ωcm2程度の低い接触抵抗率を得るためには、高温注入と1500℃以上の高温アニールが必要である。一方、{03−38}面方位イオン注入層では、室温注入の後、1200℃以上のアニールを行えば1×10-6Ωcm2程度の低い接触抵抗率が得られる。室温注入後、1500℃アニールを行った{03−38}面方位イオン注入層では4×10-7Ωcm2という極めて低い優れた特性を得た。これは、4HSiC{03−38}面では上述のように注入イオンの活性化率が高く、非常に高濃度のドーピングが容易だからである。このように、4HSiC{03−38}面を用いると、低温プロセスで十分低抵抗のn型層を形成でき、かつオーム性電極の接触抵抗率も低減できるので、Pinダイオードのカソ−ド、MOSFET、MESFETやJFETなどのn型ソース、ドレイン領域の形成に有効であり、高性能SiCデバイスの実現につながる。

【0028】(第3実施形態)第3実施形態に係るイオン注入層は、アルミ(Al)イオンが注入されたp型層が4H型SiCの{03−38}面に広がっているイオン注入層である。第3実施形態に係るイオン注入層が形成されるSiC半導体の構造は、第1実施形態で説明したSiC半導体と同様に、基板に成長されたSiC層にイオン注入層が形成されたものである。従って、ここでは、図示は省略する。

【0029】第3実施形態に係るイオン注入層の製造方法について説明する。まず、4HSiC{03−38}の面方位を有する基板に窒素(N)ドープn型4HSiC層をエピタキシャル成長させる。ここで、用いる基板は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製する。基板は全てn型で、ショットキー障壁の容量―電圧特性から求めた実効アクセプタ密度は3〜6×1018/cm3、厚さは380〜400μmである。CVD法によるn型4HSiC層の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.66sccm、N2については3×10-4sccm、H2については3.0slmとし、基板温度1520℃で90分間成長させる。このような成長条件によって成長されたn型4HSiC層のドナー密度は3〜5×1015/cm3、膜厚は5μmである。

【0030】このようにして作製したSiCエピタキシャルウェーハにAlイオンを注入し、イオン注入層を形成する。Alイオン注入は180keV、120keV、80keV、40keV、20keVの5段階で行い、総ドーズ量は5×1015cm-2である。各注入エネルギーのドーズ比を0.42(180keV)、0.21(120keV)、0.13(80keV)、0.10(40keV)、0.04(20keV)とすることによって、深さ約0.3μmのボックスプロファイルを形成する。イオン注入は室温、あるいは500℃で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中で1000〜1700℃、30分の条件で行う。

【0031】次に、上記製造方法によって製造されたイオン注入層の特性について説明する。ここでは、{0001}面から8°のオフ角を有する面方位に広がるイオン注入層(以下、「{0001}面方位イオン注入層」という)の特性と比較して、{03−38}面方位を有するイオン注入層(以下、「{03−38}面方位イオン注入層」という)の特性を説明する。{0001}面方位イオン注入層の製造方法は、上記した{03−38}面方位イオン注入層の製造方法と基本的に同じであるが、n型4HSiC層を成長させる際に導入するN2の流量が2×10-3sccmである点が異なる。

【0032】イオン注入層の電気的性質をファン・デア・ポー(van der Pauw)法によって評価した。イオン注入層を約10mm角に切りだし、注入層の電気的分離を行うために、その中央部8mm角が残るよう反応性イオンエッチングによってメサ構造を作製した。このメサ構造の4隅にチタン/アルミ(Ti: 厚さ20nm/Al: 250nm)を蒸着し、900℃、20分間の熱処理を行った。

【0033】図7は、室温、あるいは500℃の高温で注入した試料の注入層のシート抵抗のアニール温度依存性を示す図である。シート抵抗はアニール温度の上昇と共に単調に減少するが、そのシート抵抗の絶対値に大きな面方位依存性が観測された{0001}面イオン注入層の場合、高温注入、1600〜1700℃のアニールによって3200〜3800Ω/□というSiCとしては比較的低いシート抵抗が得られたが、デバイス応用を考えると十分な値ではない。室温注入ではアニール温度を1700℃まで上げてもシート抵抗は18000Ω/□と非常に高く、高性能デバイスを作製する上で大きな障害となる特性しか得られなかった。これに対して{03−38}面方位イオン注入層の場合は、室温注入、1200℃アニールでも2020Ω/□、室温注入、1500℃アニールでは1240Ω/□という低い値が得られた。また、{03−38}面方位イオン注入層では、高温注入を行うと、1200℃アニールによって1080Ω/□という優れた値を得た。このように、Alイオン注入の場合も4HSiC{03−38}面を用いると、低い注入温度、あるいは低いアニール温度で良好な低抵抗p型層が形成できることが分かった。これは、4HSiC{03−38}では、再結晶化の速度が非常に速く、比較的低温でも良好な結晶性回復特性を示すからであると考えられる。

【0034】次に、前述のイオン注入層(10mm角)を用いてオーム性電極の接触抵抗率の評価を行った。注入層表面に幅20μm、長さ200μmの短冊状の電極を間隔10〜200μmで配置し、TLM法によって電極の接触抵抗率を測定した。図8は、図7に対応する接触抵抗率の注入層アニール温度依存性(電極の熱処理は900℃で固定)を示す図である。接触抵抗率の面方位依存性、注入温度あるいはアニール温度依存性は、図7のシート抵抗と同様の傾向を示した。すなわち、{0001}面方位イオン注入層の場合、5×10-6Ωcm2以下の低い接触抵抗率を得るためには、高温注入と1500℃以上の高温アニールが必要である。一方、{03−38}面方位イオン注入層では、室温注入の後、1200℃以上のアニールを行えば3×10-6Ωcm2以下の低い接触抵抗率が得られる。室温注入後、1500℃アニールを行った{03−38}面方位イオン注入層では8×10-7Ωcm2という極めて低い優れた特性を得た。これは、4HSiC{03−38}面では上述のように注入イオンの活性化率が高く、非常に高濃度のドーピングが容易だからである。このように、4HSiC{03−38}面を用いると、低温プロセスで十分低抵抗のp型層を形成でき、かつオーム性電極の接触抵抗率も低減できるので、Pinダイオードのアノード、MOSFETやIGBTなどのp型ベ−ス領域の形成に有効であり、高性能SiCデバイスの実現につながる。

【0035】また、高ドーズイオン注入層の表面の平坦性を原子間力顕微鏡(AFM)により調べた。測定領域を1μm〜20μm角の間で変化させ、表面粗さをRms(二乗平均)で評価した。表1は、測定領域10μm角で比較した結果を示す表である。前述のように、Alイオンをトータルドーズ量5×1015/cm2注入して、アニールを行った。

【0036】

【表1】

【0037】{0001}面方位イオン注入層の表面ではRms値が0.26nm、{03−38}面方位イオン注入層の表面ではRms値が0.16nmとなり、{03−38}面方位イオン注入層の方が少し小さい値が得られ、表面の平坦性に優れることが分かる。このRms値は注入直後の状態でもほとんど変化しないが、アニール後には変化が見られた{0001}面方位イオン注入層の場合には、低抵抗層を形成するためには、1500℃以上の高温アニールが必要となるが、このような高温アニールを行うと、表面に幅0.3〜0.7μmのマクロステップが形成され、表面の平坦性が悪化した。{0001}面方位イオン注入層で最も低いシート抵抗が得られた高温注入、1700℃アニールの試料では、光学顕微鏡では鏡面を保っているものの、AFMではRms値が6.8nmまで増大し、明らかな表面荒れが観測された。高温の熱処理時におけるマクロステップの形成は、SiC{0001}オフ面が表面エネルギーを低減させるために生じる面固有の現象であり、完全に抑制することは容易ではない。一方、{03−38}面方位イオン注入層の場合には、低抵抗p型層が得られる室温注入、1200〜1500℃アニールの試料でもRms値は1.2〜1.6nmと小さい。1700℃の高温アニールを行っても、Rms値は1.8nmに留まっている。これは4HSiC{03−38}面ではオフ角を導入していないので、表面エネルギーの低い面が既に現れており、マクロステップの形成などによって表面エネルギーを下げる必要がないからであると推測される。このように、4HSiC{03−38}面では高温の熱処理を行っても表面の平坦性が維持されることは、デバイスの性能向上に有効である。例えば、ショットキー障壁/SiC界面の平坦性が維持されるので、漏れ電流の少ない良好な特性が期待される。また、酸化膜/SiC界面の平坦性もよいので、酸化膜の絶縁特性が向上する、界面のキャリヤ散乱が低減されてMOS構造のチャネル移動度が向上する、という効果が期待される。

【0038】以下、本発明に係るイオン注入層を適用した様々な半導体デバイスのデバイス特性について説明する。

【0039】(第1適用例)イオン注入層を適用した第1の例は、ショットキーダイオードである。本発明に係るイオン注入層を適用して、図9に示すショットキーダイオード10を製造した。ショットキーダイオード10の製造方法について説明する。

【0040】デバイス作製に用いた基板11は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板11は全てn型で、ホール効果測定によって求めたキャリヤ密度は8〜9×1018cm-3、厚さは160〜210μmである。このデバイスでは縦方向に電流を流すため、基板11の抵抗を下げ、かつ薄い基板11を用いるのが有効である。この基板11の{03−38}面上に、CVD法によって窒素ドープn型SiC層12をエピタキシャル成長した。n型SiC層はバッファ層12aとドリフト層12bからなり、バッファ層12aはドナー密度1〜5×1017/cm3、膜厚は2μm、ドリフト層12bはドナー密度6〜8×1015/cm3、膜厚は12μmである。CVD法によるバッファ層12aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.30sccm、N2については1×10-2sccm、H2については3.0slmとし、基板温度1550℃で45分間成長させる。また、CVD法によるドリフト層12bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.50sccm、N2については4×10-4sccm、H2については3.0slmとし、基板温度1550℃で200分間成長させる。

【0041】このようにして作製したSiCエピタキシャルウェーハを用いて、図9に示す構造のショットキーダイオード10を作製した。ショットキー電極端部での電界集中、絶縁破壊を抑制するために、ショットキー電極の周囲に幅150μm、深さ0.5μmのp型ガードリング14を設けた。ガードリング14はホウ素(B)イオン注入により形成した。Bイオン注入のエネルギーは30〜280keVでトータルドーズ量は1.1×1013/cm2である。イオン注入のマスクには、Al(厚さ4μm)、あるいはCVDにより形成したSiO2膜(厚さ5μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。アニールの後、1150℃、2時間のウェット酸化により熱酸化膜19を形成し、さらにCVDによって厚さ800nmのSiN膜を堆積した。次に裏面にNi(厚さ200nm)を蒸着し、1000℃、20分間の熱処理を行ってオーミック電極18を形成した。次いで表面側にTi/Al(Ti: 200nm/Al: 850nm)を蒸着してショットキー電極16を形成した。ショットキー電極16は500℃、30分間の熱処理を行って安定化させた。ショットキーダイオードの表面はポリイミド17を塗布して保護した。ショットキー電極16とガードリング領域14の重なりは20μmであり、ショットキー電極16の直径は300μmφ〜3mmφである。これらのガードリング14、電極パターン形成には、フォトリソグラフィ技術を用いた。

【0042】次に、作製された図9に示すショットキーダイオード10の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したショットキーダイオード(以下、「{03―38}ショットキーダイオード」という)10の特性を、{0001}面方位イオン注入層を適用したショットキーダイオード(以下、「{0001}ショットキーダイオード」という)と比較して説明する。なお、{0001}ショットキーダイオードの製造方法は、{03−38}ショットキーダイオード10の製造方法と基本的に同じであるが、バッファ層を成長させる際に導入するN2の流量が8×10-2sccmである点、ドリフト層を成長させる際に導入するN2流量が3×10-3sccmである点が異なる。

【0043】図10は、ショットキーダイオード(1mmφ)の典型的な電流−電圧特性を示す図である。順方向特性は結晶の面方位依存性は小さく、オン抵抗3〜4mΩcm2という良好な値が得られた。順方向特性の片対数プロットから求めた理想因子N値は1.02〜1.05であり、障壁高さは{0001}ショットキーダイオードで1.08eV、{03−38}ショットキーダイオード10で1.16eVとなった。逆方向特性では1500V以上の耐圧を達成し、しかも、−1000V印加時のリ−ク電流も10-4A/cm2程度と小さい。ショットキー電極16が300μmφ〜1mmφ程度の小さいダイオードでは{0001}ショットキーダイオードでも同様のダイオード特性が得られたが、電極面積の大きいダイオードでは両者の間に大きな差が見られた。図11は、{03−38}ショットキーダイオード10、{0001}ショットキーダイオードの耐圧(平均値)の電極面積依存性を示す図である。各電極面積について、少なくとも40ケのダイオードを測定して耐圧の平均値を求めた。{0001}ショットキーダイオードでは、電極面積が7.9×10-3cm2(1mmφ)を越えると急激に耐圧が低下する。これに対して、{03−38}ショットキーダイオード10は、7×10-2cm2(3mmφ)の電極面積でも高い耐圧を維持している。この3mmφのダイオードで耐圧1200Vを基準にして歩留まりを求めると、{0001}ショットキーダイオードで13%、{03−38}ショットキーダイオード10では72%となった。また、耐圧だけでなく、−1000V印加時のリ−ク電流密度の平均値を電極直径3mmφのダイオードで比較すると、{0001}ショットキーダイオードでは9×10-2A/cm2、{03−38}ショットキーダイオード10では3×10-4A/cm2となり、二桁以上の差が認められた。これは、4HSiC{03−38}面を用いることによって、基板11からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。また、4HSiC{03−38}面を用いることによって成長表面、およびイオン注入により形成したガードリング部14の表面の平坦性がよくなり、ショットキー電極16/SiC界面での電界集中が低減されるという効果も寄与していると思われる。本適用例ではBイオン注入によってガードリング14を形成したが、Alイオン注入を用いた場合でも同様の効果がある。

【0044】(第2適用例)イオン注入層を適用した第2の例は、プレーナ型pnダイオードである。本発明に係るイオン注入層を適用して、図12に示すプレーナ型pnダイオード20を製造した。プレーナ型pnダイオード20の製造方法について説明する。

【0045】デバイス作製に用いた基板21は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板21は全てn型で、ホール効果測定によって求めたキャリヤ密度は8〜9×1018cm-3、厚さは160〜210μmである。この基板21の{03−38}面上に、CVD法によって窒素ドープn型SiC層22をエピタキシャル成長した。成長層はバッファ層22aとドリフト層22bからなり、バッファ層22aはドナー密度1〜5×1017cm-3、膜厚は4μm、ドリフト層22bはドナー密度1〜2×1015cm-3、膜厚は76μmである。CVD法によるバッファ層22aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については1.5sccm、N2については8×10-2sccm、H2については3.0slmとし、基板温度1750℃、100Torrの圧力下で10分間成長させる。また、CVD法によるドリフト層22bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については15sccm、C3H8については4.5sccm、N2については1×10-3sccm、H2については3.0slmとし、基板温度1750℃、100Torrの圧力下で180分間成長させる。

【0046】ここでは、高い耐圧を得るために高純度・厚膜成長層を短時間で成膜できるように、高温での高速成長を行った。このようにして作製したSiCエピタキシャルウェーハを用いて、図12に示す構造のプレーナ型pnダイオード20を作製した。まず、p型アノード24を形成するために、Alイオンを720keV、400keV、280keV、160keV、80keV、40keV、20keVの7段階で注入した。総ドーズ量は1.3×1015/cm2である。各注入エネルギーのドーズ量を2.7×1013/cm2 (720keV)、1.8×1013/cm2 (400keV)、1.2×1013/cm2 (280keV)、1.0×1013/cm2 (160keV)、7.2×1014/cm2 (80keV)、4.2×1014/cm2 (40keV)、1.3×1014/cm2 (20keV)とすることによって、深さ約0.7μmのp型層の内、表面約0.2μmが1020/cm3以上の高濃度層となるドーピングプロファイルを形成した。次に、p型アノード領域端部での電界集中、絶縁破壊を抑制するために、この周囲に幅300μm、深さ0.7μmのp型ガードリング23を設けた。ガードリング23もAlイオン注入により形成した。Alイオン注入のエネルギーは同じく20〜720keVの7段階でトータルドーズ量は1.0×1013cm-2である。ガードリング23の形成時には、注入層がボックスプロファイルとなるよう設計した。イオン注入は全て室温で行い、イオン注入のマスクには、Al(厚さ5μm)、あるいはCVDにより形成したSiO2膜(厚さ6μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。アニールの後、1150℃、2時間のウェット酸化により熱酸化膜を形成し、さらに、CVDによって厚さ800nmのSiO2膜30を堆積した。次に裏面にNi(厚さ200nm)29、表面側にNi/Al(Ni: 200nm/Al: 1200nm)27を蒸着し、1000℃、20分間の熱処理を行ってオーミック電極27を形成した。ダイオードの表面はポリイミド28を塗布して保護した。p型アノードのサイズは3mm角(面積0.09cm2)である。

【0047】次に、作製された図12に示すプレーナ型pnダイオード20の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したプレーナ型pnダイオード(以下、「{03−38}プレーナ型pnダイオード」という)20の特性を、{0001}面方位イオン注入層を適用したプレーナ型pnダイオード(以下、「{0001}プレーナ型pnダイオード」という)と比較して説明する。なお、{0001}プレーナ型pnダイオードの製造方法は、{03−38}プレーナ型pnダイオード20の製造方法と基本的に同じであるが、バッファ層を成長させる際に導入するN2の流量が6×10-1sccmである点、ドリフト層を成長させる際に導入するN2流量が4×10-2sccmである点が異なる。

【0048】図13は、プレーナ型pnダイオード(3mm角)の典型的な電流−電圧特性を示す図である。順方向、逆方向特性とも、明らかな面方位依存性が見られた。まず順方向特性に着目すると{0001}プレーナ型pnダイオードは比較的電流が流れにくく、5A程度以上では約12mΩcm2の直列抵抗(オン抵抗)によって電気伝導が支配される。一方、{03−38}プレーナ型pnダイオード20では、オン抵抗は2〜3mΩcm2と非常に小さく、約2.8Vの立ち上がり電圧より高い領域では急激に電流が増大する{03−38}プレーナ型pnダイオード20では30A(333A/cm2)という高い電流を3.9Vの電圧降下で達成することができた。{03−38}プレーナ型pnダイオードに比べて、{0001}プレーナ型pnダイオードでは電流が流れにくいのは、4HSiC{0001}を用いた場合には、p型アノードの表面部に形成した高濃度p型層の電気的活性化率が低いために抵抗が高いこと、およびこのp型層への電極の接触抵抗が高いことが原因と考えられる。4HSiC{03−38}を用いると、室温注入でも低抵抗・高濃度p型層が形成できるので、この部分の抵抗と接触抵抗を大幅に低減できる。また、逆方向特性では{0001}プレーナ型pnダイオードの耐圧が5210Vに留まっているのに対し{03−38}プレーナ型pnダイオード20では8860Vもの高耐圧を得ることができた。−4500V印加時のリ−ク電流は、{0001}プレーナ型pnダイオードで3×10-5A/cm2、{03−38}プレーナ型pnダイオード20で5×10-8A/cm2となり、やはり明確な差が見られた。また、絶縁破壊時のアバランシェ電流に着目すると、{03−38}プレーナ型pnダイオード20では絶縁破壊時に5A(55A/cm2)まで電流を増してもダイオードの物理的破壊に至らない安定な特性が得られた。しかし、{0001}プレーナ型pnダイオード20では1A(11A/cm2)を越えると物理的破壊によって整流特性が著しく悪化するダイオードが大半を占めた。これは、4HSiC{03−38}面を用いることによって、基板21からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。

【0049】また、作製したプレーナ型pnダイオードの+4Vと−1000Vの間のスイッチング特性や高温(300℃)でのオフ特性(−3000V)の長期信頼性には特に面方位依存性が見られなかったが、オン特性(200A/cm2)の長期信頼性には面方位による差が認められた。図14は、{03−38}プレーナ型pnダイオード20、{0001}プレーナ型pnダイオードに順方向電流18A(200A/cm2)を長時間流し続けたときの順方向電圧降下をプロットした図である。{0001}プレーナ型pnダイオードでは約3000secを越えた付近から電圧降下が増大し始め、10000sec後には初期の3.6Vから4.7Vまで増大した。しかしながら、{03−38}プレーナ型pnダイオード20では10000sec後も電圧降下は3.7Vであり、ほとんど劣化していない。この原因を調べるために、長期信頼性試験を行ったダイオードを透過電子顕微鏡(TEM)により観察したところ、劣化した{0001}プレーナ型pnダイオードでは、[0001]面に多数の積層欠陥が発生していること、および{03−38}プレーナ型pnダイオード20ではこのような積層欠陥の発生が見られないことが分かった。この積層欠陥の発生機構は現在のところ明らかでないが、III−V族半導体の発光ダイオードでは、順方向バイアス時にキャリヤ再結合によって放射されるエネルギーが結晶歪が大きい部分に部分転位の発生を引き起こし、この部分転位が最密充填面内に伸びることによって積層欠陥が形成されることが知られている。{0001}プレーナ型pnダイオードの場合も順方向バイアス時に同様の現象が起こり、最密充填面に相当する[0001]面に積層欠陥が発生したものと推測される。この積層欠陥の影響によって少数キャリヤ寿命が低下し、順方向電圧降下が増大したものと思われる{03−38}プレーナ型pnダイオード20の場合にこのような積層欠陥の発生が抑制される理由は、この面ではSiとC原子が適度に混在するので、PN接合界面における歪が非常に小さく、部分転位や積層欠陥などの欠陥が発生しにくいものと思われる。また、イオン注入後のアニールによって損傷がほぼ完全に除去できるので、欠陥発生の引き金になる歪や点欠陥の集合体が非常に少ないことも寄与している。なお、この実施例ではAlイオン注入によってガードリング23を形成したが、Bイオン注入を用いた場合でも同様の効果がある。

【0050】(第3適用例)イオン注入層を適用した第3の例は、Nチャネル反転MOSFETである。本発明に係るイオン注入層を適用して、図15に示すNチャネル反転MOSFET40を製造した。Nチャネル反転MOSFET40の製造方法について説明する。

【0051】用いた基板41は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板41は全てp型で、ショットキー障壁の容量−電圧特性から求めた実効アクセプタ密度は3〜5×1018/cm3、厚さは380〜420μmである。この基板11の{03−38}面に、CVD法によってホウ素ドープp型SiC層42をエピタキシャル成長した。p型SiC成長層42のアクセプタ密度は5〜8×1015/cm3、膜厚は4μmである。CVD法によるp型SiC層42の成長条件は以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.66sccm、B2H6については1×10-5sccm、H2については3.0slmとし、基板温度1500℃で100分間成長させる。

【0052】このようにして作製したSiCエピタキシャルウェーハを用いて、図15に示す構造のNチャネル反転型MOSFET40を作製した。まず、試料をRCA洗浄し、HFデイップした後、ウェット酸化によりゲート酸化膜48を形成した。酸化条件は、1100℃、25分である。ゲート酸化膜48の厚さは46〜53nmである。ウェット酸化の後、酸化と同じ温度でアルゴン雰囲気、30分間のアニールを行った。

【0053】次に、SiH4を原料ガスに用いた減圧CVD法によって700℃で多結晶Si(厚さ1.6μm)を堆積し、POCl3を用いて900℃で燐(P)を拡散して低抵抗n型多結晶Siを形成した。この多結晶SiをCF4とO2ガスを用いた反応性イオンエッチングによってパターニングし、幅4μm、幅200μmの多結晶Siゲート47を形成した。続いて、この多結晶Siゲート電極をマスクに窒素(N)イオンを注入してソース領域44、ドレイン領域43を形成した。Nイオン注入は120keV、70keV、40keV、25keVの4段階で行い、総ドーズ量は2×1015/cm2である。イオン注入は室温で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中1200℃、30分の条件で行った。

【0054】次に、ソース電極46、ドレイン電極45としてチタン/アルミ(Ti:30nm、Al:250nm)を形成し、850℃で30分間の熱処理を施した。これらの選択的イオン注入用マスクや電極金属のパターニングには、フォトリソグラフィ技術を用いた。ここで用いた自己整合プロセスは、デバイス作製のマスク数の低減、工程数の低減だけでなく、デバイスの微細化、ゲート・ドレイン間やゲート・ソース間の寄生容量の低減に有効である。

【0055】次に、作製された図15に示すNチャネル反転MOSFET40の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したNチャネル反転MOSFET(以下、「{03―38}Nチャネル反転MOSFET」という)40の特性を、{0001}面方位イオン注入層を適用したNチャネル反転MOSFET(以下、「{0001}Nチャネル反転MOSFET」という)と比較して説明する。なお、{0001}Nチャネル反転MOSFETの製造方法は、{03−38}Nチャネル反転MOSFET40の製造方法と基本的に同じであるが、p型SiC層を成長させる際に導入するB2H6の流量が4×10-6sccmである点、ウェット酸化後のアニールの条件が1150℃、2時間である点が異なる。アニールの条件が異なるのは、{03−38}面を用いた場合は、{0001}面を用いた場合に比べて酸化速度が非常に速いためである。

【0056】図16は、MOSFETの典型的なゲート特性(ドレイン電圧0.1Vの線形領域)を示す図である。図16に示されるように、作製したMOSFETのドレイン特性には明確な線形領域と飽和領域が見られ、MOSFETとしての動作が確認された。{0001}Nチャネル反転MOSFETは、9.8Vという高いしきい値電圧を示し、かつゲート電圧を15Vまで増してもドレイン電流が1μA以下に留まっている。一方、{03−38}Nチャネル反転MOSFET40は、しきい値電圧が4.4Vと低く、ゲート電圧の増大に対してドレイン電流が急峻に立ち上がる良好な特性が得られた。このゲート特性から求めた線形領域での実効チャネル移動度は、{0001}Nチャネル反転MOSFETで4.5cm2/Vs、{03−38}Nチャネル反転MOSFET40で86cm2/Vsとなり4HSiC{03−38}を用いることによって約20倍の高いチャネル移動度を達成することができた。飽和領域で求めた電界効果移動度も{0001}Nチャネル反転MOSFETで3.1cm2/Vs、{03−38}Nチャネル反転MOSFET40で72cm2/Vsとなり、大きな違いが見られた。

【0057】このMOSFET特性の面方位による違いは主に三つの原因による。一つは、MOS界面の品質の違いである。MOSキャパシタの容量−電圧特性や、MOSFETの温度特性から4HSiC{03−38}面ではMOS界面の欠陥密度が4HSiC{0001}面より約1桁少ないことが分かっている。したがって、{03−38}Nチャネル反転MOSFET40では、反転層において電子のトラップや散乱が起こりにくいので、高いチャネル移動度が得られる。二番目の理由は、MOS界面の平坦性の違いである。上述したように、4HSiC{0001}面に高ドーズのイオン注入をしてアニールを行うと、マクロステップが発生して表面の平坦性が悪化する。MOS反転層チャネルは非常に薄いので、このようなMOS界面の平坦性には敏感であり、平坦性が悪化するとチャネル移動度も低下する4HSiC{03−38}面では、高ドーズのイオン注入、アニールを行っても優れた平坦性が維持されるので、高いチャネル移動度が得られる。もう一つの理由は、ソース領域44、およびオーム性電極の接触抵抗である。Nチャネル反転MOSFETの作製時に同じウェーハ上に作製したテストパターンを評価した結果、今回のプロセスで形成したn型ソース領域のシート抵抗が4HSiC{0001}面で2300Ω/□、4HSiC{03−38}面で210Ω/□であることが分かった。また、このソース領域44への接触抵抗率は4HSiC{0001}面で8×10-4Ωcm2、4HSiC{03−38}面で3×10-6Ωcm2であった。このように、4HSiC{03−38}面を用いることによって、寄生抵抗成分を一桁以上低減できたことも、上記のMOSFET特性の向上に大きく寄与している。従来、SiCのデバイスプロセスではイオン注入層の活性化と損傷低減に要するアニール温度がSiの融点(1420℃)より高いために、自己整合プロセスの適用は困難とされてきた。しかしながら、4HSiC{03−38}面を用いることによって室温注入でもイオン注入後のアニール温度を大幅に低減できるので、自己整合プロセスを採用しても高性能MOSFETを作製できることが分かった。ここでは、Nチャネル反転MOSFETについて述べたが、Alイオン注入によってソース領域、ドレイン領域を形成するPチャネル反転MOSFETや、CMOSデバイスの作製にも4HSiC{03−38}面の活用が非常に有効である4HSiC{03−38}面を用いて低温イオン注入プロセスを使えば、微細CMOS論理ゲートやオペアンプなどの高温動作高速集積回路の実現が可能である。

【0058】(第4適用例)イオン注入層を適用した第4の例は、Nチャネル縦型DI(Double Implanted)MOSFETである。本発明に係るイオン注入層を適用して、図17に示すNチャネル縦型DIMOSFET50を製造した。縦型のSiパワーMOSFETは二重拡散などのプロセスによって作製されるが、SiCではp型ウェル、n型ソースなどを形成するのにイオン注入技術が不可欠となる。この構造では、イオン注入によって形成したp型領域とエピタキシャル成長によって形成したn型ドリフト層のpn接合によって耐圧を維持する。Nチャネル縦型DIMOSFET50の製造方法について説明する。

【0059】デバイス作製に用いた基板51は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板51は全てn型で、ホール効果測定によって求めたキャリヤ密度は8〜9×1018/cm3、厚さは160〜210μmである。このデバイスでは縦方向に電流を流すため、基板51の抵抗を下げ、かつ薄い基板51を用いるのが有効である。この基板51の{03−38}面上に、CVD法によって窒素ドープn型SiC層52をエピタキシャル成長した。成長層はバッファ層52aとドリフト層52bからなり、バッファ層52aはドナー密度1〜5×1017cm-3、膜厚は2μm、ドリフト層52bはドナー密度5〜6×1015cm-3、膜厚は18μmである。CVD法によるバッファ層52aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.30sccm、N2については1×10-2sccm、H2については3.0slmとし、基板温度1550℃で45分間成長させる。また、CVD法によるドリフト層52bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.40sccm、N2については2×10-4sccm、H2については3.0slmとし、基板温度1550℃で250分間成長させる。

【0060】このようにして作製したSiCエピタキシャルウェーハを用いて、図17に示す構造の縦型DIMOSFET50を作製した。まず、アルミ(Al)イオンを注入して深さ0.7μm、アクセプタ密度約0.5〜3×1017/cm3のp型ウェル領域53を形成した。Alイオン注入は560keV、420keV、300keV、180keV、100keV、50keVの6段階で行い、総ドーズ量は1.4×1013/cm2である。このとき、p型ウェル53の深い領域は接合近傍での電界集中を緩和するために1017/cm3以上の密度、浅い領域はn型反転層を得るためのしきい値電圧を低減し、かつ高いチャネル移動度を得るために1016/cm3台のド−パント密度になるように設計して作製した。

【0061】次に、ソース領域54、ドレイン領域55の形成のために、燐(P)イオンを注入して低抵抗n型領域を作製した。Pイオン注入は180keV、110keV、60keV、30keVの4段階で行い、総ドーズ量は2×1015/cm2である。イオン注入はともに室温で行った。また、デバイス端部での絶縁破壊を抑制するために、活性領域の周囲に幅250μm、深さ0.7μmのp型ガードリングを設けた。ガードリングはホウ素(B)イオン注入により形成した。Bイオン注入のエネルギーは30〜360keVでトータルドーズ量は1.2×1013cm-2である。イオン注入のマスクには、Al(厚さ5μm)、あるいはCVDにより形成したSiO2膜(厚さ6μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。チャネル長は2μm、セルピッチ(ストライプ構造)は22μmである。

【0062】次に、試料をRCA洗浄し、HFデイップした後、ドライ酸化によりゲート酸化膜58を形成した。酸化条件は1150℃、25分であり、形成されるゲート酸化膜の厚さは44〜51nmである。

【0063】このゲート酸化のあと、減圧CVD法によって基板温度850℃で厚さ約1μmの多結晶Siを堆積し、燐を850℃の拡散によりドーピングし、低抵抗n型多結晶Siを形成した。次に、反応性イオンエッチングによってこの多結晶Siを部分的にエッチングしてゲート電極60を作製した。次に、ゲート・ドレイン間の絶縁用のSiO2膜(厚さ約0.8μm)60を基板温度500℃のプラズマCVD法によって堆積した。この後、裏面全面にニッケル(Ni: 200nm)を蒸着し、ドレイン電極59とした。表面側のソース電極56にはニッケル/アルミ(Ni: 100nm/Al: 400nm)を用い、両方の電極を950℃で15分間の熱処理を施すことによって良好なオーミック接触を得た。これらの選択的イオン注入用マスクや電極金属のパターニングには、フォトリソグラフィ技術を用いた。この縦型MOSFET50の活性領域の面積は9×10-2cm2(3mm角)である。

【0064】次に、作製された図17に示すNチャネル縦型DIMOSFET50の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したNチャネル縦型DIMOSFET(以下、「{03―38}Nチャネル縦型DIMOSFET」という)50の特性を、{0001}面方位イオン注入層を適用したNチャネル縦型DIMOSFET(以下、「{0001}Nチャネル縦型DIMOSFET」という)と比較して説明する。なお、{0001}Nチャネル縦型DIMOSFETの製造方法は、{03−38}Nチャネル縦型DIMOSFET50の製造方法と基本的に同じであるが、バッファ層を成長させる際に導入するN2の流量が8×10-2sccmである点、ドリフト層を成長させる際に導入するN2の流量が2×10-3sccmである点、ゲート酸化膜を形成するための酸化条件が1150℃、3時間である点が異なる。

【0065】図18は、低ドレイン電圧領域における縦型DIMOSFET(3mm角)の典型的なドレイン特性を示す図、図19は高ドレイン電圧領域における縦型DIMOSFET(3mm角)の典型的なドレイン特性を示す図である。{0001}Nチャネル縦型DIMOSFET、{03−38}Nチャネル縦型DIMOSFET50は共に明確な線形領域と飽和領域が見られ、MOSFETとして動作したが、その特性にはやはり大きな差が見られた。{0001}Nチャネル縦型DIMOSFETは、ゲート電圧を15Vまで増してもドレイン電流が500mA以下に留まっている。一方、{03−38}Nチャネル縦型DIMOSFET50は、比較的小さいゲート電圧、ドレイン電圧で9A(100A/cm2)以上のドレイン電流が流れ、ゲート電圧15Vのときには、ドレイン電圧3.4Vで9A(100A/cm2)を達成した。この特性からオン抵抗を見積もると34mΩcm2となり、非常に良好な値が得られた。ちなみに、{0001}Nチャネル縦型DIMOSFETでは、オン抵抗が970mΩcm2と大きかった。これに対し{03−38}Nチャネル縦型DIMOSFET50においてオン抵抗が小さかったのは、一つには4HSiC{03−38}を用いることによってMOSチャネル移動度が大幅に向上したためである。このチャネル移動度の向上には、MOS界面の欠陥密度の低減と優れた平坦性の両方が寄与している。{0001}Nチャネル縦型DIMOSFETではチャネル移動度が極めて低いために、オン抵抗がドリフト領域の抵抗ではなく、MOSチャネル抵抗によって支配されてしまう。また、二つ目の重要な理由は、ソース領域54、およびオーム性電極の接触抵抗の差である。Nチャネル縦型DIMOSFETの作製時に同じウェーハ上に形成したテストパターンを評価した結果、今回のプロセスで形成したn型ソース領域のシート抵抗が4HSiC{0001}面で1260Ω/□、4HSiC{03−38}面で110Ω/□であることが分かった。また、このソース領域への接触抵抗率は4HSiC{0001}面で9×10-4Ωcm2、4HSiC{03−38}面で3×10-6Ωcm2であった。このように、4HSiC{03−38}面を用いることによって、寄生抵抗成分を一桁以上低減できたことも、上記のMOSFET特性の向上に大きく寄与している。

【0066】次に、この3mm角のDIMOSFETにつき、ゲート電圧0V時(オフ状態)のドレイン耐圧を調べたところ、{0001}Nチャネル縦型DI MOSFETで1720V、{03−38} Nチャネル縦型DIMOSFET50で2680Vとなり、大きな差が見られた。これは4HSiC{03−38}を用いることによってデバイス活性領域となるSiCエピタキシャル成長層中52の欠陥密度、特にマイクロパイプ密度が低減されたからであると考えられる。この3mm角の{03−38}Nチャネル縦型 DIMOSFET50では、ゲート電圧15V、ドレイン電圧3.8Vで10A以上のオン電流を流すことができた。

【0067】(第5適用例)イオン注入層を適用した第5の例は、高周波MESFETである。本発明に係るイオン注入層を適用して、図20に示す高周波MESFET70を製造した。高周波MESFET70の製造方法について説明する。

【0068】用いた基板71は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板71はアンドープ成長によって作製した高抵抗ウェーハで、電流−電圧特性から概算した抵抗率は106Ωcmであり、厚さは280〜320μmである。基板71の面方位は、{03−38}である。この基板71上に、CVD法によってアンドープのバッファ層72a、窒素(N)ドープn型チャネル層72bを連続的にエピタキシャル成長した。バッファ層72aの実効ドナー密度は1×1014/cm3以下、膜厚は5μm、チャネル層のドナー密度は3×1017/cm3、膜厚は0.2μmである。CVD法によるバッファ層72aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.50sccm、H2については3.0slmとし、基板温度1520℃で120分間成長させる。また、CVD法によるチャネル層72bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.15sccm、C3H8については0.10sccm、N2については2×10-2sccm、H2については3.0slmとし、基板温度1520℃で10分間成長させる。

【0069】このようにして作製したSiCエピタキシャルウェーハを用いて、図20に示す構造の高周波MESFET70を作製した。まず、蒸着とフォトリソグラフィによって形成したAl(厚さ1.5μm)をマスクに用いて、反応性イオンエッチング(RIE)によって素子分離のための溝を形成した。RIEにはSF6とO2をエッチングガスに用い、圧力0.08Torr、高周波電力120Wの条件で行った。このときのエッチング速度は約60nm/minであり、20分間のエッチングによって深さ約1.2μmの溝を形成した。次に、このRIEに用いたAlマスクをパターニングすることによってイオン注入用のマスクとし、窒素(N)イオンを注入して低抵抗n型のソース領域74、ドレイン領域73を形成した。Nイオン注入は70keV、40keV、25keV、10keVの4段階で行い、総ドーズ量は3×1015/cm2である。イオン注入は室温で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中1200℃、30分の条件で行った。さらに、ソース領域74、ドレイン領域73のオーム性電極としてニッケル(Ni: 200nm)を蒸着し、リフトオフ・プロセスによりパターンを形成した後、900℃、10分間の熱処理を加えた。

【0070】次に、電子線露光とリフトオフ・プロセスを用いて微細なショットキーゲート電極77を形成した。ゲート電極材料にはチタン/プラチナ/金(Ti: 10nm、Pt: 120nm、Au: 350nm)を用い、電極77を形成した後、400℃、20分間の熱処理を行ってショットキー電極77の安定化を図った。ソース電極76、ドレイン電極75上に厚さ800nmのAlを堆積した後、GaAsMESFETの作製で用いられるプロセスによってAuのエアブリッジを作製し、ソース・フィンガーを接続した。作製した高周波MESFET70のゲート長は0.4μm、ゲート幅は900μm、ソース・ゲート間距離は0.4μm、ゲート・ドレイン間距離は1.2μmである。

【0071】次に、作製された図20に示す高周波MESFET70の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用した高周波MESFET(以下、「{03―38}高周波MESFET」という)70の特性を、{0001}面方位イオン注入層を適用した高周波MESFET(以下、「{0001}高周波MESFET」という)と比較して説明する。なお、{0001}高周波MESFETの製造方法は、{03−38}高周波MESFET70の製造方法と基本的に同じであるが、チャネル層を成長させる際に導入するN2の流量が1×10-3sccmである点が異なる。

【0072】作製した高周波MESFETのドレイン特性には明確な線形領域と飽和領域が見られ、MESFETとしての動作が確認された。MESFETの典型的なドレイン特性を図21(a)及び(b)に示す。MESFETの直流特性の性能指標となる相互コンダクタンスgmを見積もると、ゲート電圧0V、ドレイン電圧10Vの条件において{0001}高周波MESFETでgm=58mS/mm、{03−38}高周波MESFET70ではgm=74mS/mm となった。この違いは主に、ソース領域64、およびオーム性電極の接触抵抗の差に起因すると考えられる。高周波MESFETの作製時に同じウェーハ上に作製したテストパターンを評価した結果、今回のプロセスで形成したn型ソース領域のシート抵抗が4HSiC{0001}面で1830Ω/□、4HSiC{03−38}面で186Ω/□であることが分かった。また、このソース領域への接触抵抗率は4HSiC{0001}面で8×10-4Ωcm2、4HSiC{03−38}面で3×10-6Ωcm2であった。このように、4HSiC{03−38}面を用いることによって、寄生抵抗成分を一桁以上低減できたことも、上記のMESFET特性の向上に大きく寄与している。オフ時のドレイン耐圧は{0001}高周波MESFETで120V、{03−38}高周波MESFET70では155Vであった。これは、4HSiC{03−38}面を用いることによって、基板71からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。また、4HSiC{03−38}面を用いることによって成長表面の平坦性が良くなり、ショットキー電極77/SiC界面での電界集中が低減されるという効果も寄与していると思われる。

【0073】次に、このMESFETの高周波特性をオン・ウェーハのマイクロ波測定装置で評価した結果を図2222に示す。ドレイン電圧50Vの条件でテストしたときの遮断周波数ftと最高発振周波数fmaxを求めた{0001}高周波MESFETではft=6.2GHz、fmax=16GHz、{03−38}高周波MESFET70ではft=16GHz、fmax=43GHzと見積もられ、{03−38}高周波MESFETの方が優れた特性が得られた。また、周波数3GHzでの性能テストを行った結果、最高パワー密度が{0001}高周波MESFETで2.1W/mm(トータルパワー 1.8W)、{03−38}高周波MESFET70で3.4W/mm(トータルパワー3.1W)となり、やはり{03−38}高周波MESFETの方が高い出力が得られた。このように、4HSiC{03−38}面を用いることによって優れた高周波特性が得られたのは、上述のように、ソース領域74、およびオーム性電極の接触抵抗などの寄生抵抗が大幅に低減できるからである。

【0074】(第6適用例)イオン注入層を適用した第6の例は、スーパージャンクション(SJ)構造のショットキーダイオードである。本発明に係るイオン注入層を適用して、図23に示すSJ構造のショットキーダイオード80を製造した。SJ構造のショットキーダイオードについて説明する。Siパワーデバイスでは、単一のpn接合、あるいはショットキー障壁の逆バイアス状態を用いてオフ状態(高耐圧の維持)を実現しているのに対し、SJ構造では通常のpn接合(あるいはショットキー障壁)のn型領域に、高電圧が印加される方向とは垂直方向に多層のpn接合が形成される。オフ状態では、これら多層pn接合が互いに逆バイアスになるので、空乏層が二次元的に広がる。このとき、適切に空乏層内の空間電荷分布を設計すれば、ドリフト領域内の電界分布を均一にできる。この結果、比較的高濃度ドーピングを行った低抵抗層を用いても高い耐圧を維持できるようになり、高耐圧かつ低オン抵抗のパワーデバイスを実現することが出来る。このSJ構造は古くから提唱されていたが、当時は多層pn接合を制御良く作製する技術が確立されていなかったので実用化はされなかった。最近の半導体加工技術の進展によって、このような多層pn接合の形成と空間電荷分布の精密制御が可能になり、SiパワーMOSFETの分野で実用化が進められている。このSJ構造がSiCに対しても有効であるのは明らかである。

【0075】次に、SJ構造のショットキーダイオードの製造方法について説明する。デバイス作製に用いた基板81は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板81は全てn型で、ホール効果測定によって求めたキャリヤ密度は1〜2×1019/cm3、厚さは160〜210μmである。このデバイスでは縦方向に電流を流すため、基板81の抵抗を下げ、かつ薄い基板81を用いるのが有効である。この基板81の{03−38}面上に、CVD法によって窒素ドープn型SiC層をエピタキシャル成長した。成長層はバッファ層82とドリフト層83からなり、バッファ層82はドナー密度1〜5×1017/cm3、膜厚は2μm、ドリフト層83はドナー密度4×1016/cm3、膜厚は3.5μmである。CVD法によるバッファ層82の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.30sccm、N2については1×10-2sccm、H2については3.0slmとし、基板温度1520℃で45分間成長させる。また、CVD法によるドリフト層83の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.50sccm、N2については2×10-3sccm、H2については3.0slmとし、基板温度1520℃で60分間成長させる。

【0076】このSiCエピウェハ上に減圧CVD法によって厚さ6μmのSiO2膜を堆積した。このSiO2膜上にAlを蒸着し、フォトリソグラフィによって幅2μmのストライプ状のパターンを形成した。このAlパターンをマスクとして、CF4とO2ガスを用いた反応性イオンエッチングによってSiO2膜を選択的にエッチングした。次に、ストライプ状のパターンに加工されたSiO2膜をマスクとして高エネルギーイオン注入を行い、n型成長層(ドリフト層)83の一部をp型に変換した。高エネルギーイオン注入によって成長層を貫通する深いp型領域83aを形成した。注入イオンはAl+であり、注入エネルギーは30keV〜6500keVの15段階でトータルドーズ量は、3×1013/cm2である。イオン注入時の試料加熱は行わない。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1600℃、30分の条件で行った。このイオン注入によって、幅約2μmのストライプ状の注入領域はアクセプタ密度が約4×1016/cm3のp型(深さ約3.5μm)となり、SJ構造が形成される。

【0077】このようにして作製したSJ構造を有するSiCエピタキシャルウェハを用いて、図23に示す構造のSJショットキーダイオード80を作製した。まず、ショットキー電極端部での電界集中、絶縁破壊を抑制するために、ショットキー電極の周囲に幅150μm、深さ0.5μmのp型ガードリング84を設けた。ガードリング84は、ホウ素(B)イオン注入によって形成した。Bイオン注入のエネルギーは30〜280keVでトータルドーズ量は1.1×1013/cm2である。イオン注入のマスクには、Al(厚さ4μm)、あるいはCVDにより形成したSiO2膜(厚さ5μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。アニールの後、1150℃、2時間のウェット酸化により熱酸化膜87を形成し、さらに、CVDによって厚さ800nmのSiN膜88を堆積した。

【0078】次に、裏面にNi(厚さ200nm)を蒸着し、1000℃、20分間の熱処理を行ってオーミック電極90を形成した。続いて、表面側にTi/Al(Ti:200nm/Al:850nm)を蒸着し、ショットキー電極86を形成した。ショットキー電極86は、500℃、30分間の熱処理を行って安定化させた。ダイオードの表面はポリイミド89を塗布して保護した。ショットキー電極86とガードリング84の重なりは20μmであり、ショットキー電極86の直径は3mmφである。

【0079】次に、作製された図23に示すSJショットキーダイオード80の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したSJショットキーダイオード(以下、「{03−38}SJショットキーダイオード」という)80の特性を、{0001}面方位イオン注入層を適用したSJショットキーダイオード(以下、「{0001}SJショットキーダイオード」という)と比較して説明する。なお、{0001}SJショットキーダイオードの製造方法は、{03−38}SJショットキーダイオード80の製造方法と基本的に同じであるが、バッファ層82を成長させる際に導入するN2の流量が8×10-2sccmである点、ドリフト層83を成長させる際に導入するN2の流量が1×10-2sccmである点が異なる。

【0080】図24は、SJショットキーダイオード(3mmφ)の典型的な電流−電圧特性を示す図である。順方向特性は、結晶の面方位依存性は小さく、オン抵抗0.5〜0.7mΩcm2という良好な値が得られた。順方向特性の片対数プロットから求めた理想因子n値は、1.02〜1.05であり障壁高さは{0001}SJショットキーダイオードで1.09eV、{03−38}SJショットキーダイオード80で1.18eVとなった。これに対して、逆方向特性では用いた面方位によって大きな差が見られた。{0001}SJショットキーダイオードでは、最高耐圧が580V、平均耐圧が362Vに留まっているのに対し、{03−38}SJショットキーダイオード80では、最高耐圧が764V、平均耐圧が612Vとなり、優れた特性が得られた。また、耐圧だけでなく、−300V印加時のリーク電流密度の平均値を電極直径3mmφのダイオードで比較すると、{0001}SJショットキーダイオードでは3×10-1A/cm2、{03−38}SJショットキーダイオード80では1×10-4A/cm2となり、三桁以上の差が認められた。これは、4HSiC{03−38}面を用いることによって、基板81からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。また、4HSiC{03−38}面を用いることによって、成長表面、及びイオン注入によって形成されたSJ部、及びガードリング84部の平坦性が良くなり、ショットキー電極/SiC界面での電極集中が低減されるという効果も寄与していると思われる。この実施例では、Bイオン注入によってガードリング84を形成したが、Alイオン注入を用いた場合でも同様の効果がある。イオン注入によって形成されたSJ構造を4HSiC{03−38}MOSFETに適用すれば、高耐圧、低損失の優れたパワートランジスタを実現できる。

【0081】以上、本発明の実施形態について詳細に説明してきたが、本発明は上記実施形態に限定されるものではない。

【0082】上記実施形態においては、窒素(N)、燐(P)、アルミ(Al)、ホウ素(B)イオンを注入したイオン注入層について説明したが、例えば、砒素(As)やガリウム(Ga)、インジウム(In)等の上記以外のイオンを注入することとしても良い。

【0083】

【発明の効果】本発明によれば、イオン注入層が{03−38}面から10°以内の角度αのオフ角を有する面方位に広がることによって、結晶の乱れが少ないイオン注入層を実現することができる。

【図面の簡単な説明】

【図1】イオン注入層を説明するための図である。

【図2】イオン注入層のRBSスペクトルを示す図である。

【図3】イオン注入層のシート抵抗の注入ドーズ量依存性を示す図である。

【図4】イオン注入層における注入イオンの電気的活性化率のアニール温度依存性を示す図である。

【図5】イオン注入層のシート抵抗のアニール温度依存性を示す図である。

【図6】イオン注入層の接触抵抗率のアニール温度依存性を示す図である。

【図7】イオン注入層のシート抵抗の注入層アニール温度依存性を示す図である。

【図8】イオン注入層の接触抵抗率の注入層アニール温度依存性を示す図である。

【図9】イオン注入層が適用されたショットキーダイオードを示す図である。

【図10】ショットキーダイオードの電流−電圧特性を示す図である。

【図11】ショットキーダイオードの耐圧(平均値)の電極面積依存性を示す図である。

【図12】イオン注入層が適用されたプレーナ型pnダイオードを示す図である。

【図13】プレーナ型pnダイオード(3mm角)の電流−電圧特性を示す図である。

【図14】プレーナ型pnダイオードに順方向電流を長時間流したときの順方向電圧降下をプロットした図である。

【図15】イオン注入層が適用されたNチャネル反転MOSFETを示す図である。

【図16】Nチャネル反転MOSFETのゲート特性を示す図である。

【図17】イオン注入層が適用されたNチャネル縦型DIMOSFETを示す図である。

【図18】低ドレイン電圧領域における縦型DIMOSFET(3mm角)のドレイン特性を示す図である。

【図19】高ドレイン電圧領域における縦型DIMOSFET(3mm角)のドレイン特性を示す図である。

【図20】イオン注入層が適用された高周波MESFETを示す図である。

【図21】(a),(b)は、高周波MESFETの典型的なドレイン特性を示す図である。

【図22】高周波MESFETの高周波特性をオン・ウェーハのマイクロ波測定装置で評価した結果を示す図である。

【図23】イオン注入層が適用されたSJショットキーダイオードを示す図である。

【図24】SJショットキーダイオード(3mmφ)の電流−電圧特性を示す図である

【符号の説明】

10…ショットキーダイオード、11…基板、12…窒素ドープn型SiC層、12a…バッファ層、12b…ドリフト層、14…ガードリング、16…ショットキー電極、17…ポリイミド、18…オーミック電極、19…酸化膜。

【0001】

【発明の属する技術分野】本発明は、SiC半導体のイオン注入層及びそのイオン注入層を製造するイオン注入層製造方法に関する。

【0002】

【従来の技術】近年、炭化珪素(SiC)あるいは窒化ガリウム(GAN)等の軽元素で構成される化合物半導体の研究が盛んに行なわれている。これらの化合物半導体は、軽元素によって構成されているため、結合エネルギーが強く、その結果、エネルギーの禁制帯幅(バンドギャップ)、絶縁破壊電界、熱伝導度が大きいことが特徴である。このワイドバンドギャップの特徴を活かした、高効率・高耐圧パワーデバイス、高周波パワーデバイス、高温動作デバイスが注目を集めている。これらの半導体デバイスは、イオン注入法によって製造される場合が多い。

【0003】

【発明が解決しようとする課題】しかしながら、従来のSiC半導体は、{0001}面に対する傾きが10°以内の面方位を有するSiCにイオンを注入して製造されていたが、イオン注入工程においてSiC結晶が乱れるという問題点があった。そして、イオン注入工程において生じた結晶の乱れは、その後のアニール工程においても回復することが困難であった。イオン注入時の結晶の乱れを最小にする手法として、加熱した試料にイオンを注入するホットインプランテイションと呼ばれる方法が採用される場合もあるが、この方法では、イオン注入装置の試料ホルダ−を500℃程度の高温に均一に加熱する必要があるので、汎用のイオン注入装置を使用することができない上、イオン注入の後に行なわれる結晶回復のためのアニール工程において、1000℃を超える温度で熱処理する必要があった。こうした熱処理は、予期しない不純物の拡散をもたらすことがあり、また、プロセス途中で必要となる高温の処理は、プロセスの自由度、デバイス設計の自由度を制限することとなる。さらに、高温処理により結晶表面が荒れるという問題点もあった。

【0004】そこで、本発明は上記課題を解決し、結晶の乱れ及び結晶表面の荒れを低減させたイオン注入層、及びイオン注入層製造方法を提供することを目的とする。

【0005】

【課題を解決するための手段】本発明に係るSiC半導体のイオン注入層は、4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっていることを特徴とする。

【0006】このように、イオン注入層が{03−38}面から10°以内の角度αのオフ角を有する面方位に広がることによって、結晶の乱れが少ないイオン注入層を実現することができる。

【0007】また、上記SiC半導体のイオン注入層は、オフ角αは5°以内であることが好ましく、さらに、オフ角は3°以内であることが好ましい。イオン注入層が広がっている面の面方位が{03−38}面に近くなるほど、SiC半導体のイオン注入層の結晶の乱れが少なくなる。

【0008】本発明に係るSiC半導体製造方法は、{03−38}面、又は{03−38}面に対して約10°以内のオフ角αだけ傾いた面、を露出させたSiC単結晶からなる種結晶上に、4H型ポリタイプのSiC単結晶を成長させるSiC結晶成長工程と、SiC結晶成長工程において成長されたSiC結晶にイオンを注入するイオン注入工程と、を備えることを特徴とする。

【0009】このようにSiC結晶成長工程において、{03−38}面、又は{03−38}面に対して約10°以内のオフ角αだけ傾いた面、を露出させたSiC単結晶からなる種結晶上に4H型ポリタイプのSiC単結晶を成長させたSiC単結晶は、{03−38}面に対する傾きが10°以内の面方位を有する。そして、このSiC単結晶に、イオン注入工程においてイオンを注入することにより、結晶の乱れが少ないSiC半導体を製造することができる。従来は、{0001}面に対する傾きが10°以内の面方位を有するSiCにイオンを注入することによって製造されていたが、{0001}面は六方最密面であることから、不純物イオンが注入された場合に結晶がストレスを受ける。このため、イオン注入によって結晶格子が大きく乱れる原因となっていた。発明者らは、SiCの面方位について鋭意検討した結果、{03−38}面、及び{03−38}面に対する傾きが10°以内の面方位がイオン注入の際のストレスが少ない面であることを見出した。これは、{03−38}面は、最密面から離れた面でありながら原子の結合手が比較的周期的に現れている面であるためであると考えられる。従来は、イオン注入工程における結晶の乱れを最小限にするため、ホットインプランテーションを呼ばれる手法が採用されていたが、本発明によれば室温でイオン注入を行なっても、結晶の乱れを低減できるので、従来のように高温処理を行なう必要がなく、結晶表面が荒れるという問題を解消することができる。

【0010】また、上記SiC半導体製造方法は、SiC結晶成長工程において、{03−38}面から傾けれらるオフ角αは、5°以内であることが好ましい。さらに、オフ角は3°以内であることが好ましい。すなわち、種結晶の表面が{03−38}面に近くなるほど、成長されるSiC結晶の面方位は{03−38}面に近くなり、SiC半導体の結晶の乱れが少なくなる。

【0011】また、上記SiC半導体製造方法は、イオン注入工程によってイオンが注入されたSiC結晶を1000℃以下の温度によって熱処理するアニール工程を、さらに備えることを特徴としても良い。

【0012】本発明によれば、製造されたイオン注入層は結晶の乱れが少ないので、結晶を回復させるアニール工程における熱処理の温度を従来(1000℃)より低く設定することができ、結晶表面の荒れを低減したSiC半導体を実現できる。

【0013】

【発明の実施の形態】以下、図面と共に本発明に係るSiC半導体のイオン注入層及びイオン注入層製造方法の好適な実施形態について詳細に説明する。ここで、格子面の記号の説明をすると、負の指数については、結晶学上、”−”(バー)を数字の上に付けることになっているが、明細書作成の都合上、数字の前に負号を付けることにする。なお、図面の説明においては同一要素には同一符号を付し、重複する説明を省略する。

【0014】(第1実施形態)図1は、第1実施形態に係るイオン注入層2が形成されたSiC半導体1を示す図である。第1実施形態に係るイオン注入層は、窒素(N)イオンが注入されたn型層が4H型SiC層3の{03−38}面に広がっているイオン注入層2である。

【0015】第1実施形態に係るイオン注入層2の製造方法について説明する。まず、4HSiC{03−38}の面方位を有する基板3にアルミ(Al)ドープp型4HSiC層4をエピタキシャル成長させる。ここで、用いる基板3は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製する。基板3は全てp型で、ショットキー障壁の容量−電圧特性から求めた実効アクセプタ密度は5〜8×1018/cm3、厚さは360〜420μmである。CVD法によるp型SiC層4の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.5sccm、C3H8については0.40sccm、Al(CH3)3については8×10-4sccm、H2については3.0slmとし、基板温度1520℃で90分間成長させる。このような成長条件によって成長されたp型SiC層4のアクセプタ密度は6〜8×1015/cm3、膜厚は5μmである。

【0016】このようにして作製したp型SiC層4にNイオンを注入し、イオン注入層2を形成する。Nイオン注入は140keV、80keV、50keV、25keVの4段階で行い、総ドーズ量は5×1014〜2×1016/cm2である。各注入エネルギーのドーズ比を0.48(140keV)、0.26(80keV)、0.18(50keV)、0.08(25keV)とすることによって、深さ約0.4μmのボックスプロファイルを形成する。イオン注入は室温、あるいは500℃で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中で1000〜1700℃、30分の条件で行う。

【0017】次に、上記製造方法によって製造されたイオン注入層2の特性について説明する。ここでは、{03−38}面方位を有するイオン注入層(以下、「{03−38}面方位イオン注入層」という)2の特性を、{0001}面から8°のオフ角を有する面方位に広がるイオン注入層(以下、「{0001}面方位イオン注入層」という)の特性と比較して説明する。{0001}面方位イオン注入層の製造方法は、上記した{03−38}面方位イオン注入層2の製造方法と基本的に同じであるが、p型SiC層4を成長させる際に導入するAl(CH3)3の流量が2×10-4sccmである点が異なる。

【0018】まず、イオン注入層の結晶性を評価するために、ラザフォード後方散乱(RBS)のチャネリング測定を行った。RBS測定は、エネルギー2.0MeVのHe2+イオンを用い、散乱角170°の条件で測定した。図2は、トータルドーズ量5×1015/cm2の試料(室温注入、1500℃のアニール前後)のRBSスペクトルを示す図である。注入直後の状態では{0001}面方位イオン注入層、{03−38}面方位イオン注入層2とも、表面近傍におけるチャネリング時の後方散乱イールド(yield)がランダム散乱時のイールドと一致しており、注入層がほぼ完全な非晶質になっていることが分かる。1500℃のアニールを行った試料では、結晶性が改善され、チャネリング時の散乱イールド(アラインスペクトル)がランダムスペクトルより低下している。しかしながら、その結晶性回復の度合いには大きな面方位依存性が見られた。{0001}面方位イオン注入層では、1500℃のアニールを施してもアラインスペクトルの散乱イールドはかなり大きく、注入層領域(表面の約0.4μm)ではランダムイールドの20〜40%にも達する。したがって、{0001}面方位イオン注入層では、アニール時の再結晶化が不十分で、多くの結晶欠陥が残存することが分かる。実際、この試料を断面透過電子顕微鏡(TEM)観察によって分析すると、再結晶化した4HSiC層の中に、3C−SiC粒が混在すること、またこの3C−SiC粒の周辺では4HSiCも一部多結晶化し、多くの粒界や転位が形成されていることが判明した。一方、{03−38}面方位イオン注入層2では、アニールによってチャネリング時の散乱イールドが非常に小さくなり(ランダム時の1.2%)、未注入試料と同程度まで結晶性が回復していることが分かる。断面TEM観察でも、{03−38}面方位イオン注入層2では、3C−SiCの混在や粒界、転位の発生が観測されず、優れた再結晶化が進行することが分かった。これは、{0001}面方位イオン注入層では再結晶化の過程で原子配列が一義的に決まらないサイトが多数存在するために、原子のミスアライメントが多く発生するのに対し、{03−38}面方位イオン注入層2ではSiC特有の周期的ポテンンシャルが表面に現れているために、完全な非晶質からの再結晶化であっても、非常にスム−ズに、欠陥の発生を伴わない再結晶化が進むためであると考えられる。

【0019】次に、イオン注入層の電気的性質をファン・デア・ポー(van der Pauw)法によって評価した。イオン注入層を約10mm角に切りだし、注入層の電気的分離を行うために、その中央部8mm角が残るよう反応性イオンエッチングによってメサ構造を作製した。このメサ構造の4隅にニッケル(Ni: 厚さ180nm)を蒸着し、950℃、20分間の熱処理を行った。この試料のシート抵抗、キャリヤ密度、移動度をファン・デア・ポー法、およびホール効果測定によって調べた。図3は、室温、あるいは500℃の高温でNイオンを注入し、1500℃でアニールした試料のシート抵抗の注入ドーズ量依存性を示す図である。{0001}面方位イオン注入層の場合、シート抵抗の最小値は室温注入で710Ω/□(ドーズ量:8×1014/cm2)、500℃の高温注入で420Ω/□(ドーズ量:8×1014/cm2)である。特に、室温注入では、ドーズ量が1×1015/cm2を越えるとシート抵抗が増大してしまう。この原因は、上述のように、注入によって完全な非晶質領域が形成されてしまうと、1500℃のアニールを行っても多くの欠陥が残留して注入イオンの活性化を妨げるからであると考えられる。一方、{03−38}面方位イオン注入層2では、シート抵抗の最小値は室温注入で120Ω/□(ドーズ量: 5×1015/cm2)、500℃の高温注入で86Ω/□(ドーズ量: 1×1016/cm2)となり、室温注入、高温注入ともにシート抵抗の大幅な低減が可能であることが分かった。デバイスの工業化を考えると、イオン注入装置の製造、運転コスト、注入プロセス時のスループットの点で室温注入のメリットは大きい。したがって、4HSiC{03−38}面を用いることによって、室温注入でも低いシート抵抗が得られた意義は非常に大きい。

【0020】次に、ドーズ量を5×1015/cm2に固定し、注入層における注入イオンの電気的活性化率のアニール温度依存性を調べた結果を図4に示す。SiC中のNドナーは室温において必ずしも完全にイオン化して自由電子を供給していないので、ホール効果測定を室温から300℃の高温まで行い、出払い領域のシートキャリヤ密度をドーズ量で割った値を電気的活性化率と定義した。図4から分かるように{0001}面方位イオン注入層では、アニール温度を1700℃まで上昇させても活性化率はあまり高くならない。特に、室温注入の場合には、活性化率が10%以下に留まっている。しかしながら、{03−38}面方位イオン注入層2では、室温注入でも、高い活性化率が得られることが分かる。室温注入、1200℃アニールの試料でも84%という高い活性化率を達成でき、1500℃アニールを施すことによってほぼ100%の活性化率が得られる。ちなみに、室温注入、1200℃アニールの試料で比較すると、{0001}面方位イオン注入層ではシート抵抗が2230Ω/□、{03−38}面方位イオン注入層2ではシート抵抗が180Ω/□となり、一桁以上の改善が見られた。{03−38}面方位イオン注入層2では、再結晶化の速度が非常に速く、1200℃程度の比較的低温でも良好な結晶性回復特性を示すものと思われる。このように、{03−38}面方位イオン注入層2を用いると、低温プロセスで十分低抵抗のn型層を形成でき、かつオーム性電極の接触抵抗率も低減できるので、pinダイオードのカソ−ド、MOSFET、MESFETやJFETなどのn型ソース、ドレイン領域の形成に有効であり、高性能SiCデバイスの実現につながる。

【0021】(第2実施形態)第2実施形態に係るイオン注入層は、燐(P)イオンが注入されたn型層が4H型SiCの{03−38}面に広がっているイオン注入層である。第2実施形態に係るイオン注入層が形成されるSiC半導体の構造は、第1実施形態で説明したSiC半導体と同様に、基板に成長されたSiC層にイオン注入層が形成されたものである。従って、ここでは、図示は省略する。

【0022】第2実施形態に係るイオン注入層の製造方法について説明する。まず、4HSiC{03−38}の面方位を有する基板にホウ素(B)ドープp型4HSiC層をエピタキシャル成長させる。ここで、用いる基板は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製する。基板は全てp型で、ショットキー障壁の容量−電圧特性から求めた実効アクセプタ密度は6〜8×1018/cm3、厚さは380〜420μmである。CVD法によるp型4HSiC層の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C2H4については0.66sccm、B2H6については6×10-6sccm、H2については3.0slmとし、基板温度1500℃で110分間成長させる。このような成長条件によって成長されたp型SiC層のアクセプタ密度は3〜5×1015/cm3、膜厚は5μmである。

【0023】このようにして作製したSiCエピタキシャルウェーハにPイオンを注入し、イオン注入層を形成する。Pイオン注入は180keV、120keV、80keV、40keV、20keVの5段階で行い、総ドーズ量は5×1015cm-2である。各注入エネルギーのドーズ比を0.42(180keV)、0.21(120keV)、0.13(80keV)、0.10(40keV)、0.04(20keV)とすることによって、深さ約0.3μmのボックスプロファイルを形成する。イオン注入は室温、あるいは800℃で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中で1000〜1700℃、30分の条件で行う。

【0024】次に、上記製造方法によって製造されたイオン注入層の特性について説明する。ここでは、{0001}面から8°のオフ角を有する面方位に広がるイオン注入層(以下、「{0001}面方位イオン注入層」という)の特性と比較して、{03−38}面方位を有するイオン注入層(以下、「{03−38}面方位イオン注入層」という)の特性を説明する。{0001}面方位イオン注入層の製造方法は、上記した{03−38}面方位イオン注入層の製造方法と基本的に同じであるが、p型SiC層を成長させる際に導入するB2H6の流量が2×10-6sccmである点が異なる。

【0025】イオン注入層の電気的性質をファン・デア・ポー(van der Pauw)法によって評価した。イオン注入層を約10mm角に切りだし、注入層の電気的分離を行うために、その中央部8mm角が残るよう反応性イオンエッチングによってメサ構造を作製した。このメサ構造の4隅にニッケル(Ni: 厚さ180nm)を蒸着し、950℃、20分間の熱処理を行った。

【0026】図5は、室温、あるいは800℃の高温でイオン注入を行ったイオン注入層のシート抵抗のアニール温度依存性を示す図である。シート抵抗はアニール温度の上昇と共に単調に減少するが、そのシート抵抗の絶対値に大きな面方位依存性が観測された。{0001}面方位イオン注入層の場合、高温注入、1600〜1700℃のアニールによって94〜97Ω/□という低いシート抵抗が得られたが、室温注入ではアニール温度を1700℃まで上げてもシート抵抗は285Ω/□までしか低減できなかった。これに対して{03−38}面方位イオン注入層の場合は、室温注入、1200℃アニールでも102Ω/□、室温注入、1500℃アニールでは67Ω/□という低い値が得られた。また、高温注入によって得られた{03−38}面方位イオン注入層では、1200℃アニールによって56Ω/□という優れた値を得た。このように、Pイオン注入の場合も、4HSiC{03−38}面を用いると、低い注入温度、あるいは低いアニール温度で良好な低抵抗n型層が形成できることが分かった。これは、4HSiC{03−38}では、再結晶化の速度が非常に速く、比較的低温でも良好な結晶性回復特性を示すからであると考えられる。

【0027】次に、前述のイオン注入層(10mm角)を用いてオーム性電極の接触抵抗率の評価を行った。注入層表面に幅20μm、長さ200μmの短冊状の電極を間隔10〜200μmで配置し、TLM法によって電極の接触抵抗率を測定した。図6は、図5に対応する接触抵抗率の注入層アニール温度依存性を示す図(電極の熱処理は950℃で固定)である。接触抵抗率の面方位依存性、注入温度あるいはアニール温度依存性は、図5のシート抵抗と同様の傾向を示した。すなわち、{0001}面方位イオン注入層の場合、1×10-6Ωcm2程度の低い接触抵抗率を得るためには、高温注入と1500℃以上の高温アニールが必要である。一方、{03−38}面方位イオン注入層では、室温注入の後、1200℃以上のアニールを行えば1×10-6Ωcm2程度の低い接触抵抗率が得られる。室温注入後、1500℃アニールを行った{03−38}面方位イオン注入層では4×10-7Ωcm2という極めて低い優れた特性を得た。これは、4HSiC{03−38}面では上述のように注入イオンの活性化率が高く、非常に高濃度のドーピングが容易だからである。このように、4HSiC{03−38}面を用いると、低温プロセスで十分低抵抗のn型層を形成でき、かつオーム性電極の接触抵抗率も低減できるので、Pinダイオードのカソ−ド、MOSFET、MESFETやJFETなどのn型ソース、ドレイン領域の形成に有効であり、高性能SiCデバイスの実現につながる。

【0028】(第3実施形態)第3実施形態に係るイオン注入層は、アルミ(Al)イオンが注入されたp型層が4H型SiCの{03−38}面に広がっているイオン注入層である。第3実施形態に係るイオン注入層が形成されるSiC半導体の構造は、第1実施形態で説明したSiC半導体と同様に、基板に成長されたSiC層にイオン注入層が形成されたものである。従って、ここでは、図示は省略する。

【0029】第3実施形態に係るイオン注入層の製造方法について説明する。まず、4HSiC{03−38}の面方位を有する基板に窒素(N)ドープn型4HSiC層をエピタキシャル成長させる。ここで、用いる基板は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製する。基板は全てn型で、ショットキー障壁の容量―電圧特性から求めた実効アクセプタ密度は3〜6×1018/cm3、厚さは380〜400μmである。CVD法によるn型4HSiC層の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.66sccm、N2については3×10-4sccm、H2については3.0slmとし、基板温度1520℃で90分間成長させる。このような成長条件によって成長されたn型4HSiC層のドナー密度は3〜5×1015/cm3、膜厚は5μmである。

【0030】このようにして作製したSiCエピタキシャルウェーハにAlイオンを注入し、イオン注入層を形成する。Alイオン注入は180keV、120keV、80keV、40keV、20keVの5段階で行い、総ドーズ量は5×1015cm-2である。各注入エネルギーのドーズ比を0.42(180keV)、0.21(120keV)、0.13(80keV)、0.10(40keV)、0.04(20keV)とすることによって、深さ約0.3μmのボックスプロファイルを形成する。イオン注入は室温、あるいは500℃で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中で1000〜1700℃、30分の条件で行う。

【0031】次に、上記製造方法によって製造されたイオン注入層の特性について説明する。ここでは、{0001}面から8°のオフ角を有する面方位に広がるイオン注入層(以下、「{0001}面方位イオン注入層」という)の特性と比較して、{03−38}面方位を有するイオン注入層(以下、「{03−38}面方位イオン注入層」という)の特性を説明する。{0001}面方位イオン注入層の製造方法は、上記した{03−38}面方位イオン注入層の製造方法と基本的に同じであるが、n型4HSiC層を成長させる際に導入するN2の流量が2×10-3sccmである点が異なる。

【0032】イオン注入層の電気的性質をファン・デア・ポー(van der Pauw)法によって評価した。イオン注入層を約10mm角に切りだし、注入層の電気的分離を行うために、その中央部8mm角が残るよう反応性イオンエッチングによってメサ構造を作製した。このメサ構造の4隅にチタン/アルミ(Ti: 厚さ20nm/Al: 250nm)を蒸着し、900℃、20分間の熱処理を行った。

【0033】図7は、室温、あるいは500℃の高温で注入した試料の注入層のシート抵抗のアニール温度依存性を示す図である。シート抵抗はアニール温度の上昇と共に単調に減少するが、そのシート抵抗の絶対値に大きな面方位依存性が観測された{0001}面イオン注入層の場合、高温注入、1600〜1700℃のアニールによって3200〜3800Ω/□というSiCとしては比較的低いシート抵抗が得られたが、デバイス応用を考えると十分な値ではない。室温注入ではアニール温度を1700℃まで上げてもシート抵抗は18000Ω/□と非常に高く、高性能デバイスを作製する上で大きな障害となる特性しか得られなかった。これに対して{03−38}面方位イオン注入層の場合は、室温注入、1200℃アニールでも2020Ω/□、室温注入、1500℃アニールでは1240Ω/□という低い値が得られた。また、{03−38}面方位イオン注入層では、高温注入を行うと、1200℃アニールによって1080Ω/□という優れた値を得た。このように、Alイオン注入の場合も4HSiC{03−38}面を用いると、低い注入温度、あるいは低いアニール温度で良好な低抵抗p型層が形成できることが分かった。これは、4HSiC{03−38}では、再結晶化の速度が非常に速く、比較的低温でも良好な結晶性回復特性を示すからであると考えられる。

【0034】次に、前述のイオン注入層(10mm角)を用いてオーム性電極の接触抵抗率の評価を行った。注入層表面に幅20μm、長さ200μmの短冊状の電極を間隔10〜200μmで配置し、TLM法によって電極の接触抵抗率を測定した。図8は、図7に対応する接触抵抗率の注入層アニール温度依存性(電極の熱処理は900℃で固定)を示す図である。接触抵抗率の面方位依存性、注入温度あるいはアニール温度依存性は、図7のシート抵抗と同様の傾向を示した。すなわち、{0001}面方位イオン注入層の場合、5×10-6Ωcm2以下の低い接触抵抗率を得るためには、高温注入と1500℃以上の高温アニールが必要である。一方、{03−38}面方位イオン注入層では、室温注入の後、1200℃以上のアニールを行えば3×10-6Ωcm2以下の低い接触抵抗率が得られる。室温注入後、1500℃アニールを行った{03−38}面方位イオン注入層では8×10-7Ωcm2という極めて低い優れた特性を得た。これは、4HSiC{03−38}面では上述のように注入イオンの活性化率が高く、非常に高濃度のドーピングが容易だからである。このように、4HSiC{03−38}面を用いると、低温プロセスで十分低抵抗のp型層を形成でき、かつオーム性電極の接触抵抗率も低減できるので、Pinダイオードのアノード、MOSFETやIGBTなどのp型ベ−ス領域の形成に有効であり、高性能SiCデバイスの実現につながる。

【0035】また、高ドーズイオン注入層の表面の平坦性を原子間力顕微鏡(AFM)により調べた。測定領域を1μm〜20μm角の間で変化させ、表面粗さをRms(二乗平均)で評価した。表1は、測定領域10μm角で比較した結果を示す表である。前述のように、Alイオンをトータルドーズ量5×1015/cm2注入して、アニールを行った。

【0036】

【表1】

【0037】{0001}面方位イオン注入層の表面ではRms値が0.26nm、{03−38}面方位イオン注入層の表面ではRms値が0.16nmとなり、{03−38}面方位イオン注入層の方が少し小さい値が得られ、表面の平坦性に優れることが分かる。このRms値は注入直後の状態でもほとんど変化しないが、アニール後には変化が見られた{0001}面方位イオン注入層の場合には、低抵抗層を形成するためには、1500℃以上の高温アニールが必要となるが、このような高温アニールを行うと、表面に幅0.3〜0.7μmのマクロステップが形成され、表面の平坦性が悪化した。{0001}面方位イオン注入層で最も低いシート抵抗が得られた高温注入、1700℃アニールの試料では、光学顕微鏡では鏡面を保っているものの、AFMではRms値が6.8nmまで増大し、明らかな表面荒れが観測された。高温の熱処理時におけるマクロステップの形成は、SiC{0001}オフ面が表面エネルギーを低減させるために生じる面固有の現象であり、完全に抑制することは容易ではない。一方、{03−38}面方位イオン注入層の場合には、低抵抗p型層が得られる室温注入、1200〜1500℃アニールの試料でもRms値は1.2〜1.6nmと小さい。1700℃の高温アニールを行っても、Rms値は1.8nmに留まっている。これは4HSiC{03−38}面ではオフ角を導入していないので、表面エネルギーの低い面が既に現れており、マクロステップの形成などによって表面エネルギーを下げる必要がないからであると推測される。このように、4HSiC{03−38}面では高温の熱処理を行っても表面の平坦性が維持されることは、デバイスの性能向上に有効である。例えば、ショットキー障壁/SiC界面の平坦性が維持されるので、漏れ電流の少ない良好な特性が期待される。また、酸化膜/SiC界面の平坦性もよいので、酸化膜の絶縁特性が向上する、界面のキャリヤ散乱が低減されてMOS構造のチャネル移動度が向上する、という効果が期待される。

【0038】以下、本発明に係るイオン注入層を適用した様々な半導体デバイスのデバイス特性について説明する。

【0039】(第1適用例)イオン注入層を適用した第1の例は、ショットキーダイオードである。本発明に係るイオン注入層を適用して、図9に示すショットキーダイオード10を製造した。ショットキーダイオード10の製造方法について説明する。

【0040】デバイス作製に用いた基板11は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板11は全てn型で、ホール効果測定によって求めたキャリヤ密度は8〜9×1018cm-3、厚さは160〜210μmである。このデバイスでは縦方向に電流を流すため、基板11の抵抗を下げ、かつ薄い基板11を用いるのが有効である。この基板11の{03−38}面上に、CVD法によって窒素ドープn型SiC層12をエピタキシャル成長した。n型SiC層はバッファ層12aとドリフト層12bからなり、バッファ層12aはドナー密度1〜5×1017/cm3、膜厚は2μm、ドリフト層12bはドナー密度6〜8×1015/cm3、膜厚は12μmである。CVD法によるバッファ層12aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.30sccm、N2については1×10-2sccm、H2については3.0slmとし、基板温度1550℃で45分間成長させる。また、CVD法によるドリフト層12bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.50sccm、N2については4×10-4sccm、H2については3.0slmとし、基板温度1550℃で200分間成長させる。

【0041】このようにして作製したSiCエピタキシャルウェーハを用いて、図9に示す構造のショットキーダイオード10を作製した。ショットキー電極端部での電界集中、絶縁破壊を抑制するために、ショットキー電極の周囲に幅150μm、深さ0.5μmのp型ガードリング14を設けた。ガードリング14はホウ素(B)イオン注入により形成した。Bイオン注入のエネルギーは30〜280keVでトータルドーズ量は1.1×1013/cm2である。イオン注入のマスクには、Al(厚さ4μm)、あるいはCVDにより形成したSiO2膜(厚さ5μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。アニールの後、1150℃、2時間のウェット酸化により熱酸化膜19を形成し、さらにCVDによって厚さ800nmのSiN膜を堆積した。次に裏面にNi(厚さ200nm)を蒸着し、1000℃、20分間の熱処理を行ってオーミック電極18を形成した。次いで表面側にTi/Al(Ti: 200nm/Al: 850nm)を蒸着してショットキー電極16を形成した。ショットキー電極16は500℃、30分間の熱処理を行って安定化させた。ショットキーダイオードの表面はポリイミド17を塗布して保護した。ショットキー電極16とガードリング領域14の重なりは20μmであり、ショットキー電極16の直径は300μmφ〜3mmφである。これらのガードリング14、電極パターン形成には、フォトリソグラフィ技術を用いた。

【0042】次に、作製された図9に示すショットキーダイオード10の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したショットキーダイオード(以下、「{03―38}ショットキーダイオード」という)10の特性を、{0001}面方位イオン注入層を適用したショットキーダイオード(以下、「{0001}ショットキーダイオード」という)と比較して説明する。なお、{0001}ショットキーダイオードの製造方法は、{03−38}ショットキーダイオード10の製造方法と基本的に同じであるが、バッファ層を成長させる際に導入するN2の流量が8×10-2sccmである点、ドリフト層を成長させる際に導入するN2流量が3×10-3sccmである点が異なる。

【0043】図10は、ショットキーダイオード(1mmφ)の典型的な電流−電圧特性を示す図である。順方向特性は結晶の面方位依存性は小さく、オン抵抗3〜4mΩcm2という良好な値が得られた。順方向特性の片対数プロットから求めた理想因子N値は1.02〜1.05であり、障壁高さは{0001}ショットキーダイオードで1.08eV、{03−38}ショットキーダイオード10で1.16eVとなった。逆方向特性では1500V以上の耐圧を達成し、しかも、−1000V印加時のリ−ク電流も10-4A/cm2程度と小さい。ショットキー電極16が300μmφ〜1mmφ程度の小さいダイオードでは{0001}ショットキーダイオードでも同様のダイオード特性が得られたが、電極面積の大きいダイオードでは両者の間に大きな差が見られた。図11は、{03−38}ショットキーダイオード10、{0001}ショットキーダイオードの耐圧(平均値)の電極面積依存性を示す図である。各電極面積について、少なくとも40ケのダイオードを測定して耐圧の平均値を求めた。{0001}ショットキーダイオードでは、電極面積が7.9×10-3cm2(1mmφ)を越えると急激に耐圧が低下する。これに対して、{03−38}ショットキーダイオード10は、7×10-2cm2(3mmφ)の電極面積でも高い耐圧を維持している。この3mmφのダイオードで耐圧1200Vを基準にして歩留まりを求めると、{0001}ショットキーダイオードで13%、{03−38}ショットキーダイオード10では72%となった。また、耐圧だけでなく、−1000V印加時のリ−ク電流密度の平均値を電極直径3mmφのダイオードで比較すると、{0001}ショットキーダイオードでは9×10-2A/cm2、{03−38}ショットキーダイオード10では3×10-4A/cm2となり、二桁以上の差が認められた。これは、4HSiC{03−38}面を用いることによって、基板11からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。また、4HSiC{03−38}面を用いることによって成長表面、およびイオン注入により形成したガードリング部14の表面の平坦性がよくなり、ショットキー電極16/SiC界面での電界集中が低減されるという効果も寄与していると思われる。本適用例ではBイオン注入によってガードリング14を形成したが、Alイオン注入を用いた場合でも同様の効果がある。

【0044】(第2適用例)イオン注入層を適用した第2の例は、プレーナ型pnダイオードである。本発明に係るイオン注入層を適用して、図12に示すプレーナ型pnダイオード20を製造した。プレーナ型pnダイオード20の製造方法について説明する。

【0045】デバイス作製に用いた基板21は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板21は全てn型で、ホール効果測定によって求めたキャリヤ密度は8〜9×1018cm-3、厚さは160〜210μmである。この基板21の{03−38}面上に、CVD法によって窒素ドープn型SiC層22をエピタキシャル成長した。成長層はバッファ層22aとドリフト層22bからなり、バッファ層22aはドナー密度1〜5×1017cm-3、膜厚は4μm、ドリフト層22bはドナー密度1〜2×1015cm-3、膜厚は76μmである。CVD法によるバッファ層22aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については1.5sccm、N2については8×10-2sccm、H2については3.0slmとし、基板温度1750℃、100Torrの圧力下で10分間成長させる。また、CVD法によるドリフト層22bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については15sccm、C3H8については4.5sccm、N2については1×10-3sccm、H2については3.0slmとし、基板温度1750℃、100Torrの圧力下で180分間成長させる。

【0046】ここでは、高い耐圧を得るために高純度・厚膜成長層を短時間で成膜できるように、高温での高速成長を行った。このようにして作製したSiCエピタキシャルウェーハを用いて、図12に示す構造のプレーナ型pnダイオード20を作製した。まず、p型アノード24を形成するために、Alイオンを720keV、400keV、280keV、160keV、80keV、40keV、20keVの7段階で注入した。総ドーズ量は1.3×1015/cm2である。各注入エネルギーのドーズ量を2.7×1013/cm2 (720keV)、1.8×1013/cm2 (400keV)、1.2×1013/cm2 (280keV)、1.0×1013/cm2 (160keV)、7.2×1014/cm2 (80keV)、4.2×1014/cm2 (40keV)、1.3×1014/cm2 (20keV)とすることによって、深さ約0.7μmのp型層の内、表面約0.2μmが1020/cm3以上の高濃度層となるドーピングプロファイルを形成した。次に、p型アノード領域端部での電界集中、絶縁破壊を抑制するために、この周囲に幅300μm、深さ0.7μmのp型ガードリング23を設けた。ガードリング23もAlイオン注入により形成した。Alイオン注入のエネルギーは同じく20〜720keVの7段階でトータルドーズ量は1.0×1013cm-2である。ガードリング23の形成時には、注入層がボックスプロファイルとなるよう設計した。イオン注入は全て室温で行い、イオン注入のマスクには、Al(厚さ5μm)、あるいはCVDにより形成したSiO2膜(厚さ6μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。アニールの後、1150℃、2時間のウェット酸化により熱酸化膜を形成し、さらに、CVDによって厚さ800nmのSiO2膜30を堆積した。次に裏面にNi(厚さ200nm)29、表面側にNi/Al(Ni: 200nm/Al: 1200nm)27を蒸着し、1000℃、20分間の熱処理を行ってオーミック電極27を形成した。ダイオードの表面はポリイミド28を塗布して保護した。p型アノードのサイズは3mm角(面積0.09cm2)である。

【0047】次に、作製された図12に示すプレーナ型pnダイオード20の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したプレーナ型pnダイオード(以下、「{03−38}プレーナ型pnダイオード」という)20の特性を、{0001}面方位イオン注入層を適用したプレーナ型pnダイオード(以下、「{0001}プレーナ型pnダイオード」という)と比較して説明する。なお、{0001}プレーナ型pnダイオードの製造方法は、{03−38}プレーナ型pnダイオード20の製造方法と基本的に同じであるが、バッファ層を成長させる際に導入するN2の流量が6×10-1sccmである点、ドリフト層を成長させる際に導入するN2流量が4×10-2sccmである点が異なる。

【0048】図13は、プレーナ型pnダイオード(3mm角)の典型的な電流−電圧特性を示す図である。順方向、逆方向特性とも、明らかな面方位依存性が見られた。まず順方向特性に着目すると{0001}プレーナ型pnダイオードは比較的電流が流れにくく、5A程度以上では約12mΩcm2の直列抵抗(オン抵抗)によって電気伝導が支配される。一方、{03−38}プレーナ型pnダイオード20では、オン抵抗は2〜3mΩcm2と非常に小さく、約2.8Vの立ち上がり電圧より高い領域では急激に電流が増大する{03−38}プレーナ型pnダイオード20では30A(333A/cm2)という高い電流を3.9Vの電圧降下で達成することができた。{03−38}プレーナ型pnダイオードに比べて、{0001}プレーナ型pnダイオードでは電流が流れにくいのは、4HSiC{0001}を用いた場合には、p型アノードの表面部に形成した高濃度p型層の電気的活性化率が低いために抵抗が高いこと、およびこのp型層への電極の接触抵抗が高いことが原因と考えられる。4HSiC{03−38}を用いると、室温注入でも低抵抗・高濃度p型層が形成できるので、この部分の抵抗と接触抵抗を大幅に低減できる。また、逆方向特性では{0001}プレーナ型pnダイオードの耐圧が5210Vに留まっているのに対し{03−38}プレーナ型pnダイオード20では8860Vもの高耐圧を得ることができた。−4500V印加時のリ−ク電流は、{0001}プレーナ型pnダイオードで3×10-5A/cm2、{03−38}プレーナ型pnダイオード20で5×10-8A/cm2となり、やはり明確な差が見られた。また、絶縁破壊時のアバランシェ電流に着目すると、{03−38}プレーナ型pnダイオード20では絶縁破壊時に5A(55A/cm2)まで電流を増してもダイオードの物理的破壊に至らない安定な特性が得られた。しかし、{0001}プレーナ型pnダイオード20では1A(11A/cm2)を越えると物理的破壊によって整流特性が著しく悪化するダイオードが大半を占めた。これは、4HSiC{03−38}面を用いることによって、基板21からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。

【0049】また、作製したプレーナ型pnダイオードの+4Vと−1000Vの間のスイッチング特性や高温(300℃)でのオフ特性(−3000V)の長期信頼性には特に面方位依存性が見られなかったが、オン特性(200A/cm2)の長期信頼性には面方位による差が認められた。図14は、{03−38}プレーナ型pnダイオード20、{0001}プレーナ型pnダイオードに順方向電流18A(200A/cm2)を長時間流し続けたときの順方向電圧降下をプロットした図である。{0001}プレーナ型pnダイオードでは約3000secを越えた付近から電圧降下が増大し始め、10000sec後には初期の3.6Vから4.7Vまで増大した。しかしながら、{03−38}プレーナ型pnダイオード20では10000sec後も電圧降下は3.7Vであり、ほとんど劣化していない。この原因を調べるために、長期信頼性試験を行ったダイオードを透過電子顕微鏡(TEM)により観察したところ、劣化した{0001}プレーナ型pnダイオードでは、[0001]面に多数の積層欠陥が発生していること、および{03−38}プレーナ型pnダイオード20ではこのような積層欠陥の発生が見られないことが分かった。この積層欠陥の発生機構は現在のところ明らかでないが、III−V族半導体の発光ダイオードでは、順方向バイアス時にキャリヤ再結合によって放射されるエネルギーが結晶歪が大きい部分に部分転位の発生を引き起こし、この部分転位が最密充填面内に伸びることによって積層欠陥が形成されることが知られている。{0001}プレーナ型pnダイオードの場合も順方向バイアス時に同様の現象が起こり、最密充填面に相当する[0001]面に積層欠陥が発生したものと推測される。この積層欠陥の影響によって少数キャリヤ寿命が低下し、順方向電圧降下が増大したものと思われる{03−38}プレーナ型pnダイオード20の場合にこのような積層欠陥の発生が抑制される理由は、この面ではSiとC原子が適度に混在するので、PN接合界面における歪が非常に小さく、部分転位や積層欠陥などの欠陥が発生しにくいものと思われる。また、イオン注入後のアニールによって損傷がほぼ完全に除去できるので、欠陥発生の引き金になる歪や点欠陥の集合体が非常に少ないことも寄与している。なお、この実施例ではAlイオン注入によってガードリング23を形成したが、Bイオン注入を用いた場合でも同様の効果がある。

【0050】(第3適用例)イオン注入層を適用した第3の例は、Nチャネル反転MOSFETである。本発明に係るイオン注入層を適用して、図15に示すNチャネル反転MOSFET40を製造した。Nチャネル反転MOSFET40の製造方法について説明する。

【0051】用いた基板41は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板41は全てp型で、ショットキー障壁の容量−電圧特性から求めた実効アクセプタ密度は3〜5×1018/cm3、厚さは380〜420μmである。この基板11の{03−38}面に、CVD法によってホウ素ドープp型SiC層42をエピタキシャル成長した。p型SiC成長層42のアクセプタ密度は5〜8×1015/cm3、膜厚は4μmである。CVD法によるp型SiC層42の成長条件は以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.66sccm、B2H6については1×10-5sccm、H2については3.0slmとし、基板温度1500℃で100分間成長させる。

【0052】このようにして作製したSiCエピタキシャルウェーハを用いて、図15に示す構造のNチャネル反転型MOSFET40を作製した。まず、試料をRCA洗浄し、HFデイップした後、ウェット酸化によりゲート酸化膜48を形成した。酸化条件は、1100℃、25分である。ゲート酸化膜48の厚さは46〜53nmである。ウェット酸化の後、酸化と同じ温度でアルゴン雰囲気、30分間のアニールを行った。

【0053】次に、SiH4を原料ガスに用いた減圧CVD法によって700℃で多結晶Si(厚さ1.6μm)を堆積し、POCl3を用いて900℃で燐(P)を拡散して低抵抗n型多結晶Siを形成した。この多結晶SiをCF4とO2ガスを用いた反応性イオンエッチングによってパターニングし、幅4μm、幅200μmの多結晶Siゲート47を形成した。続いて、この多結晶Siゲート電極をマスクに窒素(N)イオンを注入してソース領域44、ドレイン領域43を形成した。Nイオン注入は120keV、70keV、40keV、25keVの4段階で行い、総ドーズ量は2×1015/cm2である。イオン注入は室温で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中1200℃、30分の条件で行った。

【0054】次に、ソース電極46、ドレイン電極45としてチタン/アルミ(Ti:30nm、Al:250nm)を形成し、850℃で30分間の熱処理を施した。これらの選択的イオン注入用マスクや電極金属のパターニングには、フォトリソグラフィ技術を用いた。ここで用いた自己整合プロセスは、デバイス作製のマスク数の低減、工程数の低減だけでなく、デバイスの微細化、ゲート・ドレイン間やゲート・ソース間の寄生容量の低減に有効である。

【0055】次に、作製された図15に示すNチャネル反転MOSFET40の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したNチャネル反転MOSFET(以下、「{03―38}Nチャネル反転MOSFET」という)40の特性を、{0001}面方位イオン注入層を適用したNチャネル反転MOSFET(以下、「{0001}Nチャネル反転MOSFET」という)と比較して説明する。なお、{0001}Nチャネル反転MOSFETの製造方法は、{03−38}Nチャネル反転MOSFET40の製造方法と基本的に同じであるが、p型SiC層を成長させる際に導入するB2H6の流量が4×10-6sccmである点、ウェット酸化後のアニールの条件が1150℃、2時間である点が異なる。アニールの条件が異なるのは、{03−38}面を用いた場合は、{0001}面を用いた場合に比べて酸化速度が非常に速いためである。

【0056】図16は、MOSFETの典型的なゲート特性(ドレイン電圧0.1Vの線形領域)を示す図である。図16に示されるように、作製したMOSFETのドレイン特性には明確な線形領域と飽和領域が見られ、MOSFETとしての動作が確認された。{0001}Nチャネル反転MOSFETは、9.8Vという高いしきい値電圧を示し、かつゲート電圧を15Vまで増してもドレイン電流が1μA以下に留まっている。一方、{03−38}Nチャネル反転MOSFET40は、しきい値電圧が4.4Vと低く、ゲート電圧の増大に対してドレイン電流が急峻に立ち上がる良好な特性が得られた。このゲート特性から求めた線形領域での実効チャネル移動度は、{0001}Nチャネル反転MOSFETで4.5cm2/Vs、{03−38}Nチャネル反転MOSFET40で86cm2/Vsとなり4HSiC{03−38}を用いることによって約20倍の高いチャネル移動度を達成することができた。飽和領域で求めた電界効果移動度も{0001}Nチャネル反転MOSFETで3.1cm2/Vs、{03−38}Nチャネル反転MOSFET40で72cm2/Vsとなり、大きな違いが見られた。

【0057】このMOSFET特性の面方位による違いは主に三つの原因による。一つは、MOS界面の品質の違いである。MOSキャパシタの容量−電圧特性や、MOSFETの温度特性から4HSiC{03−38}面ではMOS界面の欠陥密度が4HSiC{0001}面より約1桁少ないことが分かっている。したがって、{03−38}Nチャネル反転MOSFET40では、反転層において電子のトラップや散乱が起こりにくいので、高いチャネル移動度が得られる。二番目の理由は、MOS界面の平坦性の違いである。上述したように、4HSiC{0001}面に高ドーズのイオン注入をしてアニールを行うと、マクロステップが発生して表面の平坦性が悪化する。MOS反転層チャネルは非常に薄いので、このようなMOS界面の平坦性には敏感であり、平坦性が悪化するとチャネル移動度も低下する4HSiC{03−38}面では、高ドーズのイオン注入、アニールを行っても優れた平坦性が維持されるので、高いチャネル移動度が得られる。もう一つの理由は、ソース領域44、およびオーム性電極の接触抵抗である。Nチャネル反転MOSFETの作製時に同じウェーハ上に作製したテストパターンを評価した結果、今回のプロセスで形成したn型ソース領域のシート抵抗が4HSiC{0001}面で2300Ω/□、4HSiC{03−38}面で210Ω/□であることが分かった。また、このソース領域44への接触抵抗率は4HSiC{0001}面で8×10-4Ωcm2、4HSiC{03−38}面で3×10-6Ωcm2であった。このように、4HSiC{03−38}面を用いることによって、寄生抵抗成分を一桁以上低減できたことも、上記のMOSFET特性の向上に大きく寄与している。従来、SiCのデバイスプロセスではイオン注入層の活性化と損傷低減に要するアニール温度がSiの融点(1420℃)より高いために、自己整合プロセスの適用は困難とされてきた。しかしながら、4HSiC{03−38}面を用いることによって室温注入でもイオン注入後のアニール温度を大幅に低減できるので、自己整合プロセスを採用しても高性能MOSFETを作製できることが分かった。ここでは、Nチャネル反転MOSFETについて述べたが、Alイオン注入によってソース領域、ドレイン領域を形成するPチャネル反転MOSFETや、CMOSデバイスの作製にも4HSiC{03−38}面の活用が非常に有効である4HSiC{03−38}面を用いて低温イオン注入プロセスを使えば、微細CMOS論理ゲートやオペアンプなどの高温動作高速集積回路の実現が可能である。

【0058】(第4適用例)イオン注入層を適用した第4の例は、Nチャネル縦型DI(Double Implanted)MOSFETである。本発明に係るイオン注入層を適用して、図17に示すNチャネル縦型DIMOSFET50を製造した。縦型のSiパワーMOSFETは二重拡散などのプロセスによって作製されるが、SiCではp型ウェル、n型ソースなどを形成するのにイオン注入技術が不可欠となる。この構造では、イオン注入によって形成したp型領域とエピタキシャル成長によって形成したn型ドリフト層のpn接合によって耐圧を維持する。Nチャネル縦型DIMOSFET50の製造方法について説明する。

【0059】デバイス作製に用いた基板51は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板51は全てn型で、ホール効果測定によって求めたキャリヤ密度は8〜9×1018/cm3、厚さは160〜210μmである。このデバイスでは縦方向に電流を流すため、基板51の抵抗を下げ、かつ薄い基板51を用いるのが有効である。この基板51の{03−38}面上に、CVD法によって窒素ドープn型SiC層52をエピタキシャル成長した。成長層はバッファ層52aとドリフト層52bからなり、バッファ層52aはドナー密度1〜5×1017cm-3、膜厚は2μm、ドリフト層52bはドナー密度5〜6×1015cm-3、膜厚は18μmである。CVD法によるバッファ層52aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.30sccm、N2については1×10-2sccm、H2については3.0slmとし、基板温度1550℃で45分間成長させる。また、CVD法によるドリフト層52bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.40sccm、N2については2×10-4sccm、H2については3.0slmとし、基板温度1550℃で250分間成長させる。

【0060】このようにして作製したSiCエピタキシャルウェーハを用いて、図17に示す構造の縦型DIMOSFET50を作製した。まず、アルミ(Al)イオンを注入して深さ0.7μm、アクセプタ密度約0.5〜3×1017/cm3のp型ウェル領域53を形成した。Alイオン注入は560keV、420keV、300keV、180keV、100keV、50keVの6段階で行い、総ドーズ量は1.4×1013/cm2である。このとき、p型ウェル53の深い領域は接合近傍での電界集中を緩和するために1017/cm3以上の密度、浅い領域はn型反転層を得るためのしきい値電圧を低減し、かつ高いチャネル移動度を得るために1016/cm3台のド−パント密度になるように設計して作製した。

【0061】次に、ソース領域54、ドレイン領域55の形成のために、燐(P)イオンを注入して低抵抗n型領域を作製した。Pイオン注入は180keV、110keV、60keV、30keVの4段階で行い、総ドーズ量は2×1015/cm2である。イオン注入はともに室温で行った。また、デバイス端部での絶縁破壊を抑制するために、活性領域の周囲に幅250μm、深さ0.7μmのp型ガードリングを設けた。ガードリングはホウ素(B)イオン注入により形成した。Bイオン注入のエネルギーは30〜360keVでトータルドーズ量は1.2×1013cm-2である。イオン注入のマスクには、Al(厚さ5μm)、あるいはCVDにより形成したSiO2膜(厚さ6μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。チャネル長は2μm、セルピッチ(ストライプ構造)は22μmである。

【0062】次に、試料をRCA洗浄し、HFデイップした後、ドライ酸化によりゲート酸化膜58を形成した。酸化条件は1150℃、25分であり、形成されるゲート酸化膜の厚さは44〜51nmである。

【0063】このゲート酸化のあと、減圧CVD法によって基板温度850℃で厚さ約1μmの多結晶Siを堆積し、燐を850℃の拡散によりドーピングし、低抵抗n型多結晶Siを形成した。次に、反応性イオンエッチングによってこの多結晶Siを部分的にエッチングしてゲート電極60を作製した。次に、ゲート・ドレイン間の絶縁用のSiO2膜(厚さ約0.8μm)60を基板温度500℃のプラズマCVD法によって堆積した。この後、裏面全面にニッケル(Ni: 200nm)を蒸着し、ドレイン電極59とした。表面側のソース電極56にはニッケル/アルミ(Ni: 100nm/Al: 400nm)を用い、両方の電極を950℃で15分間の熱処理を施すことによって良好なオーミック接触を得た。これらの選択的イオン注入用マスクや電極金属のパターニングには、フォトリソグラフィ技術を用いた。この縦型MOSFET50の活性領域の面積は9×10-2cm2(3mm角)である。

【0064】次に、作製された図17に示すNチャネル縦型DIMOSFET50の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したNチャネル縦型DIMOSFET(以下、「{03―38}Nチャネル縦型DIMOSFET」という)50の特性を、{0001}面方位イオン注入層を適用したNチャネル縦型DIMOSFET(以下、「{0001}Nチャネル縦型DIMOSFET」という)と比較して説明する。なお、{0001}Nチャネル縦型DIMOSFETの製造方法は、{03−38}Nチャネル縦型DIMOSFET50の製造方法と基本的に同じであるが、バッファ層を成長させる際に導入するN2の流量が8×10-2sccmである点、ドリフト層を成長させる際に導入するN2の流量が2×10-3sccmである点、ゲート酸化膜を形成するための酸化条件が1150℃、3時間である点が異なる。

【0065】図18は、低ドレイン電圧領域における縦型DIMOSFET(3mm角)の典型的なドレイン特性を示す図、図19は高ドレイン電圧領域における縦型DIMOSFET(3mm角)の典型的なドレイン特性を示す図である。{0001}Nチャネル縦型DIMOSFET、{03−38}Nチャネル縦型DIMOSFET50は共に明確な線形領域と飽和領域が見られ、MOSFETとして動作したが、その特性にはやはり大きな差が見られた。{0001}Nチャネル縦型DIMOSFETは、ゲート電圧を15Vまで増してもドレイン電流が500mA以下に留まっている。一方、{03−38}Nチャネル縦型DIMOSFET50は、比較的小さいゲート電圧、ドレイン電圧で9A(100A/cm2)以上のドレイン電流が流れ、ゲート電圧15Vのときには、ドレイン電圧3.4Vで9A(100A/cm2)を達成した。この特性からオン抵抗を見積もると34mΩcm2となり、非常に良好な値が得られた。ちなみに、{0001}Nチャネル縦型DIMOSFETでは、オン抵抗が970mΩcm2と大きかった。これに対し{03−38}Nチャネル縦型DIMOSFET50においてオン抵抗が小さかったのは、一つには4HSiC{03−38}を用いることによってMOSチャネル移動度が大幅に向上したためである。このチャネル移動度の向上には、MOS界面の欠陥密度の低減と優れた平坦性の両方が寄与している。{0001}Nチャネル縦型DIMOSFETではチャネル移動度が極めて低いために、オン抵抗がドリフト領域の抵抗ではなく、MOSチャネル抵抗によって支配されてしまう。また、二つ目の重要な理由は、ソース領域54、およびオーム性電極の接触抵抗の差である。Nチャネル縦型DIMOSFETの作製時に同じウェーハ上に形成したテストパターンを評価した結果、今回のプロセスで形成したn型ソース領域のシート抵抗が4HSiC{0001}面で1260Ω/□、4HSiC{03−38}面で110Ω/□であることが分かった。また、このソース領域への接触抵抗率は4HSiC{0001}面で9×10-4Ωcm2、4HSiC{03−38}面で3×10-6Ωcm2であった。このように、4HSiC{03−38}面を用いることによって、寄生抵抗成分を一桁以上低減できたことも、上記のMOSFET特性の向上に大きく寄与している。

【0066】次に、この3mm角のDIMOSFETにつき、ゲート電圧0V時(オフ状態)のドレイン耐圧を調べたところ、{0001}Nチャネル縦型DI MOSFETで1720V、{03−38} Nチャネル縦型DIMOSFET50で2680Vとなり、大きな差が見られた。これは4HSiC{03−38}を用いることによってデバイス活性領域となるSiCエピタキシャル成長層中52の欠陥密度、特にマイクロパイプ密度が低減されたからであると考えられる。この3mm角の{03−38}Nチャネル縦型 DIMOSFET50では、ゲート電圧15V、ドレイン電圧3.8Vで10A以上のオン電流を流すことができた。

【0067】(第5適用例)イオン注入層を適用した第5の例は、高周波MESFETである。本発明に係るイオン注入層を適用して、図20に示す高周波MESFET70を製造した。高周波MESFET70の製造方法について説明する。

【0068】用いた基板71は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板71はアンドープ成長によって作製した高抵抗ウェーハで、電流−電圧特性から概算した抵抗率は106Ωcmであり、厚さは280〜320μmである。基板71の面方位は、{03−38}である。この基板71上に、CVD法によってアンドープのバッファ層72a、窒素(N)ドープn型チャネル層72bを連続的にエピタキシャル成長した。バッファ層72aの実効ドナー密度は1×1014/cm3以下、膜厚は5μm、チャネル層のドナー密度は3×1017/cm3、膜厚は0.2μmである。CVD法によるバッファ層72aの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.50sccm、H2については3.0slmとし、基板温度1520℃で120分間成長させる。また、CVD法によるチャネル層72bの主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.15sccm、C3H8については0.10sccm、N2については2×10-2sccm、H2については3.0slmとし、基板温度1520℃で10分間成長させる。

【0069】このようにして作製したSiCエピタキシャルウェーハを用いて、図20に示す構造の高周波MESFET70を作製した。まず、蒸着とフォトリソグラフィによって形成したAl(厚さ1.5μm)をマスクに用いて、反応性イオンエッチング(RIE)によって素子分離のための溝を形成した。RIEにはSF6とO2をエッチングガスに用い、圧力0.08Torr、高周波電力120Wの条件で行った。このときのエッチング速度は約60nm/minであり、20分間のエッチングによって深さ約1.2μmの溝を形成した。次に、このRIEに用いたAlマスクをパターニングすることによってイオン注入用のマスクとし、窒素(N)イオンを注入して低抵抗n型のソース領域74、ドレイン領域73を形成した。Nイオン注入は70keV、40keV、25keV、10keVの4段階で行い、総ドーズ量は3×1015/cm2である。イオン注入は室温で行い、注入イオン活性化のための熱処理はアルゴンガス雰囲気中1200℃、30分の条件で行った。さらに、ソース領域74、ドレイン領域73のオーム性電極としてニッケル(Ni: 200nm)を蒸着し、リフトオフ・プロセスによりパターンを形成した後、900℃、10分間の熱処理を加えた。

【0070】次に、電子線露光とリフトオフ・プロセスを用いて微細なショットキーゲート電極77を形成した。ゲート電極材料にはチタン/プラチナ/金(Ti: 10nm、Pt: 120nm、Au: 350nm)を用い、電極77を形成した後、400℃、20分間の熱処理を行ってショットキー電極77の安定化を図った。ソース電極76、ドレイン電極75上に厚さ800nmのAlを堆積した後、GaAsMESFETの作製で用いられるプロセスによってAuのエアブリッジを作製し、ソース・フィンガーを接続した。作製した高周波MESFET70のゲート長は0.4μm、ゲート幅は900μm、ソース・ゲート間距離は0.4μm、ゲート・ドレイン間距離は1.2μmである。

【0071】次に、作製された図20に示す高周波MESFET70の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用した高周波MESFET(以下、「{03―38}高周波MESFET」という)70の特性を、{0001}面方位イオン注入層を適用した高周波MESFET(以下、「{0001}高周波MESFET」という)と比較して説明する。なお、{0001}高周波MESFETの製造方法は、{03−38}高周波MESFET70の製造方法と基本的に同じであるが、チャネル層を成長させる際に導入するN2の流量が1×10-3sccmである点が異なる。

【0072】作製した高周波MESFETのドレイン特性には明確な線形領域と飽和領域が見られ、MESFETとしての動作が確認された。MESFETの典型的なドレイン特性を図21(a)及び(b)に示す。MESFETの直流特性の性能指標となる相互コンダクタンスgmを見積もると、ゲート電圧0V、ドレイン電圧10Vの条件において{0001}高周波MESFETでgm=58mS/mm、{03−38}高周波MESFET70ではgm=74mS/mm となった。この違いは主に、ソース領域64、およびオーム性電極の接触抵抗の差に起因すると考えられる。高周波MESFETの作製時に同じウェーハ上に作製したテストパターンを評価した結果、今回のプロセスで形成したn型ソース領域のシート抵抗が4HSiC{0001}面で1830Ω/□、4HSiC{03−38}面で186Ω/□であることが分かった。また、このソース領域への接触抵抗率は4HSiC{0001}面で8×10-4Ωcm2、4HSiC{03−38}面で3×10-6Ωcm2であった。このように、4HSiC{03−38}面を用いることによって、寄生抵抗成分を一桁以上低減できたことも、上記のMESFET特性の向上に大きく寄与している。オフ時のドレイン耐圧は{0001}高周波MESFETで120V、{03−38}高周波MESFET70では155Vであった。これは、4HSiC{03−38}面を用いることによって、基板71からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。また、4HSiC{03−38}面を用いることによって成長表面の平坦性が良くなり、ショットキー電極77/SiC界面での電界集中が低減されるという効果も寄与していると思われる。

【0073】次に、このMESFETの高周波特性をオン・ウェーハのマイクロ波測定装置で評価した結果を図2222に示す。ドレイン電圧50Vの条件でテストしたときの遮断周波数ftと最高発振周波数fmaxを求めた{0001}高周波MESFETではft=6.2GHz、fmax=16GHz、{03−38}高周波MESFET70ではft=16GHz、fmax=43GHzと見積もられ、{03−38}高周波MESFETの方が優れた特性が得られた。また、周波数3GHzでの性能テストを行った結果、最高パワー密度が{0001}高周波MESFETで2.1W/mm(トータルパワー 1.8W)、{03−38}高周波MESFET70で3.4W/mm(トータルパワー3.1W)となり、やはり{03−38}高周波MESFETの方が高い出力が得られた。このように、4HSiC{03−38}面を用いることによって優れた高周波特性が得られたのは、上述のように、ソース領域74、およびオーム性電極の接触抵抗などの寄生抵抗が大幅に低減できるからである。

【0074】(第6適用例)イオン注入層を適用した第6の例は、スーパージャンクション(SJ)構造のショットキーダイオードである。本発明に係るイオン注入層を適用して、図23に示すSJ構造のショットキーダイオード80を製造した。SJ構造のショットキーダイオードについて説明する。Siパワーデバイスでは、単一のpn接合、あるいはショットキー障壁の逆バイアス状態を用いてオフ状態(高耐圧の維持)を実現しているのに対し、SJ構造では通常のpn接合(あるいはショットキー障壁)のn型領域に、高電圧が印加される方向とは垂直方向に多層のpn接合が形成される。オフ状態では、これら多層pn接合が互いに逆バイアスになるので、空乏層が二次元的に広がる。このとき、適切に空乏層内の空間電荷分布を設計すれば、ドリフト領域内の電界分布を均一にできる。この結果、比較的高濃度ドーピングを行った低抵抗層を用いても高い耐圧を維持できるようになり、高耐圧かつ低オン抵抗のパワーデバイスを実現することが出来る。このSJ構造は古くから提唱されていたが、当時は多層pn接合を制御良く作製する技術が確立されていなかったので実用化はされなかった。最近の半導体加工技術の進展によって、このような多層pn接合の形成と空間電荷分布の精密制御が可能になり、SiパワーMOSFETの分野で実用化が進められている。このSJ構造がSiCに対しても有効であるのは明らかである。

【0075】次に、SJ構造のショットキーダイオードの製造方法について説明する。デバイス作製に用いた基板81は、改良レーリー法によって成長したインゴットをスライスし、鏡面研磨することによって作製した。基板81は全てn型で、ホール効果測定によって求めたキャリヤ密度は1〜2×1019/cm3、厚さは160〜210μmである。このデバイスでは縦方向に電流を流すため、基板81の抵抗を下げ、かつ薄い基板81を用いるのが有効である。この基板81の{03−38}面上に、CVD法によって窒素ドープn型SiC層をエピタキシャル成長した。成長層はバッファ層82とドリフト層83からなり、バッファ層82はドナー密度1〜5×1017/cm3、膜厚は2μm、ドリフト層83はドナー密度4×1016/cm3、膜厚は3.5μmである。CVD法によるバッファ層82の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.30sccm、C3H8については0.30sccm、N2については1×10-2sccm、H2については3.0slmとし、基板温度1520℃で45分間成長させる。また、CVD法によるドリフト層83の主な成長条件は、以下の通りである。導入する気体流量を、SiH4については0.50sccm、C3H8については0.50sccm、N2については2×10-3sccm、H2については3.0slmとし、基板温度1520℃で60分間成長させる。

【0076】このSiCエピウェハ上に減圧CVD法によって厚さ6μmのSiO2膜を堆積した。このSiO2膜上にAlを蒸着し、フォトリソグラフィによって幅2μmのストライプ状のパターンを形成した。このAlパターンをマスクとして、CF4とO2ガスを用いた反応性イオンエッチングによってSiO2膜を選択的にエッチングした。次に、ストライプ状のパターンに加工されたSiO2膜をマスクとして高エネルギーイオン注入を行い、n型成長層(ドリフト層)83の一部をp型に変換した。高エネルギーイオン注入によって成長層を貫通する深いp型領域83aを形成した。注入イオンはAl+であり、注入エネルギーは30keV〜6500keVの15段階でトータルドーズ量は、3×1013/cm2である。イオン注入時の試料加熱は行わない。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1600℃、30分の条件で行った。このイオン注入によって、幅約2μmのストライプ状の注入領域はアクセプタ密度が約4×1016/cm3のp型(深さ約3.5μm)となり、SJ構造が形成される。

【0077】このようにして作製したSJ構造を有するSiCエピタキシャルウェハを用いて、図23に示す構造のSJショットキーダイオード80を作製した。まず、ショットキー電極端部での電界集中、絶縁破壊を抑制するために、ショットキー電極の周囲に幅150μm、深さ0.5μmのp型ガードリング84を設けた。ガードリング84は、ホウ素(B)イオン注入によって形成した。Bイオン注入のエネルギーは30〜280keVでトータルドーズ量は1.1×1013/cm2である。イオン注入のマスクには、Al(厚さ4μm)、あるいはCVDにより形成したSiO2膜(厚さ5μm)を用いた。注入イオン活性化のための熱処理はアルゴンガス雰囲気中1500℃、30分の条件で行った。アニールの後、1150℃、2時間のウェット酸化により熱酸化膜87を形成し、さらに、CVDによって厚さ800nmのSiN膜88を堆積した。

【0078】次に、裏面にNi(厚さ200nm)を蒸着し、1000℃、20分間の熱処理を行ってオーミック電極90を形成した。続いて、表面側にTi/Al(Ti:200nm/Al:850nm)を蒸着し、ショットキー電極86を形成した。ショットキー電極86は、500℃、30分間の熱処理を行って安定化させた。ダイオードの表面はポリイミド89を塗布して保護した。ショットキー電極86とガードリング84の重なりは20μmであり、ショットキー電極86の直径は3mmφである。

【0079】次に、作製された図23に示すSJショットキーダイオード80の特性について説明する。ここでは、{03−38}面方位イオン注入層を適用したSJショットキーダイオード(以下、「{03−38}SJショットキーダイオード」という)80の特性を、{0001}面方位イオン注入層を適用したSJショットキーダイオード(以下、「{0001}SJショットキーダイオード」という)と比較して説明する。なお、{0001}SJショットキーダイオードの製造方法は、{03−38}SJショットキーダイオード80の製造方法と基本的に同じであるが、バッファ層82を成長させる際に導入するN2の流量が8×10-2sccmである点、ドリフト層83を成長させる際に導入するN2の流量が1×10-2sccmである点が異なる。

【0080】図24は、SJショットキーダイオード(3mmφ)の典型的な電流−電圧特性を示す図である。順方向特性は、結晶の面方位依存性は小さく、オン抵抗0.5〜0.7mΩcm2という良好な値が得られた。順方向特性の片対数プロットから求めた理想因子n値は、1.02〜1.05であり障壁高さは{0001}SJショットキーダイオードで1.09eV、{03−38}SJショットキーダイオード80で1.18eVとなった。これに対して、逆方向特性では用いた面方位によって大きな差が見られた。{0001}SJショットキーダイオードでは、最高耐圧が580V、平均耐圧が362Vに留まっているのに対し、{03−38}SJショットキーダイオード80では、最高耐圧が764V、平均耐圧が612Vとなり、優れた特性が得られた。また、耐圧だけでなく、−300V印加時のリーク電流密度の平均値を電極直径3mmφのダイオードで比較すると、{0001}SJショットキーダイオードでは3×10-1A/cm2、{03−38}SJショットキーダイオード80では1×10-4A/cm2となり、三桁以上の差が認められた。これは、4HSiC{03−38}面を用いることによって、基板81からのマイクロパイプやらせん転位の貫通が抑制され、高品質SiC結晶が得られたからであると考えられる。また、4HSiC{03−38}面を用いることによって、成長表面、及びイオン注入によって形成されたSJ部、及びガードリング84部の平坦性が良くなり、ショットキー電極/SiC界面での電極集中が低減されるという効果も寄与していると思われる。この実施例では、Bイオン注入によってガードリング84を形成したが、Alイオン注入を用いた場合でも同様の効果がある。イオン注入によって形成されたSJ構造を4HSiC{03−38}MOSFETに適用すれば、高耐圧、低損失の優れたパワートランジスタを実現できる。

【0081】以上、本発明の実施形態について詳細に説明してきたが、本発明は上記実施形態に限定されるものではない。

【0082】上記実施形態においては、窒素(N)、燐(P)、アルミ(Al)、ホウ素(B)イオンを注入したイオン注入層について説明したが、例えば、砒素(As)やガリウム(Ga)、インジウム(In)等の上記以外のイオンを注入することとしても良い。

【0083】

【発明の効果】本発明によれば、イオン注入層が{03−38}面から10°以内の角度αのオフ角を有する面方位に広がることによって、結晶の乱れが少ないイオン注入層を実現することができる。

【図面の簡単な説明】

【図1】イオン注入層を説明するための図である。

【図2】イオン注入層のRBSスペクトルを示す図である。

【図3】イオン注入層のシート抵抗の注入ドーズ量依存性を示す図である。

【図4】イオン注入層における注入イオンの電気的活性化率のアニール温度依存性を示す図である。

【図5】イオン注入層のシート抵抗のアニール温度依存性を示す図である。

【図6】イオン注入層の接触抵抗率のアニール温度依存性を示す図である。

【図7】イオン注入層のシート抵抗の注入層アニール温度依存性を示す図である。

【図8】イオン注入層の接触抵抗率の注入層アニール温度依存性を示す図である。

【図9】イオン注入層が適用されたショットキーダイオードを示す図である。

【図10】ショットキーダイオードの電流−電圧特性を示す図である。

【図11】ショットキーダイオードの耐圧(平均値)の電極面積依存性を示す図である。

【図12】イオン注入層が適用されたプレーナ型pnダイオードを示す図である。

【図13】プレーナ型pnダイオード(3mm角)の電流−電圧特性を示す図である。

【図14】プレーナ型pnダイオードに順方向電流を長時間流したときの順方向電圧降下をプロットした図である。

【図15】イオン注入層が適用されたNチャネル反転MOSFETを示す図である。

【図16】Nチャネル反転MOSFETのゲート特性を示す図である。

【図17】イオン注入層が適用されたNチャネル縦型DIMOSFETを示す図である。

【図18】低ドレイン電圧領域における縦型DIMOSFET(3mm角)のドレイン特性を示す図である。

【図19】高ドレイン電圧領域における縦型DIMOSFET(3mm角)のドレイン特性を示す図である。

【図20】イオン注入層が適用された高周波MESFETを示す図である。

【図21】(a),(b)は、高周波MESFETの典型的なドレイン特性を示す図である。

【図22】高周波MESFETの高周波特性をオン・ウェーハのマイクロ波測定装置で評価した結果を示す図である。

【図23】イオン注入層が適用されたSJショットキーダイオードを示す図である。

【図24】SJショットキーダイオード(3mmφ)の電流−電圧特性を示す図である

【符号の説明】

10…ショットキーダイオード、11…基板、12…窒素ドープn型SiC層、12a…バッファ層、12b…ドリフト層、14…ガードリング、16…ショットキー電極、17…ポリイミド、18…オーミック電極、19…酸化膜。

【特許請求の範囲】

【請求項1】 4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっていることを特徴とするSiC半導体のイオン注入層。

【請求項2】 前記オフ角αは、5°以内であることを特徴とする請求項1に記載のSiC半導体のイオン注入層。

【請求項3】 前記オフ角αは、3°以内であることを特徴とする請求項1に記載のSiC半導体のイオン注入層。

【請求項4】 {03−38}面、又は{03−38}面に対して約10°以内のオフ角αだけ傾いた面、を露出させたSiC単結晶からなる種結晶上に、4H型ポリタイプのSiC単結晶を成長させるSiC結晶成長工程と、前記SiC結晶成長工程において成長されたSiC結晶にイオンを注入するイオン注入工程と、を備えることを特徴とするイオン注入層製造方法。

【請求項5】 前記SiC結晶成長工程において、{03−38}面から傾けれらるオフ角αは、5°以内であることを特徴とする請求項4に記載のイオン注入層製造方法。

【請求項6】 前記SiC結晶成長工程において、{03−38}面から傾けれらるオフ角αは、3°以内であることを特徴とする請求項4に記載のイオン注入層製造方法。

【請求項7】 前記イオン注入工程によってイオンが注入されたSiC結晶を1000℃以下の温度によって熱処理するアニール工程を、さらに備えることを特徴とする請求項4〜6のいずれか1項に記載のイオン注入層製造方法。

【請求項1】 4H型SiCの{03−38}面から10°以内の角度αのオフ角を有する面方位の面に広がっていることを特徴とするSiC半導体のイオン注入層。

【請求項2】 前記オフ角αは、5°以内であることを特徴とする請求項1に記載のSiC半導体のイオン注入層。

【請求項3】 前記オフ角αは、3°以内であることを特徴とする請求項1に記載のSiC半導体のイオン注入層。

【請求項4】 {03−38}面、又は{03−38}面に対して約10°以内のオフ角αだけ傾いた面、を露出させたSiC単結晶からなる種結晶上に、4H型ポリタイプのSiC単結晶を成長させるSiC結晶成長工程と、前記SiC結晶成長工程において成長されたSiC結晶にイオンを注入するイオン注入工程と、を備えることを特徴とするイオン注入層製造方法。

【請求項5】 前記SiC結晶成長工程において、{03−38}面から傾けれらるオフ角αは、5°以内であることを特徴とする請求項4に記載のイオン注入層製造方法。

【請求項6】 前記SiC結晶成長工程において、{03−38}面から傾けれらるオフ角αは、3°以内であることを特徴とする請求項4に記載のイオン注入層製造方法。

【請求項7】 前記イオン注入工程によってイオンが注入されたSiC結晶を1000℃以下の温度によって熱処理するアニール工程を、さらに備えることを特徴とする請求項4〜6のいずれか1項に記載のイオン注入層製造方法。

【図1】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図16】

【図17】

【図18】

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【公開番号】特開2002−261041(P2002−261041A)

【公開日】平成14年9月13日(2002.9.13)

【国際特許分類】

【出願番号】特願2001−60380(P2001−60380)

【出願日】平成13年3月5日(2001.3.5)

【出願人】(599012835)株式会社シクスオン (10)

【出願人】(000156938)関西電力株式会社 (1,442)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(000005979)三菱商事株式会社 (56)

【Fターム(参考)】

【公開日】平成14年9月13日(2002.9.13)

【国際特許分類】

【出願日】平成13年3月5日(2001.3.5)

【出願人】(599012835)株式会社シクスオン (10)

【出願人】(000156938)関西電力株式会社 (1,442)

【出願人】(000002130)住友電気工業株式会社 (12,747)

【出願人】(000005979)三菱商事株式会社 (56)

【Fターム(参考)】

[ Back to top ]