TFT基板の製造方法

【課題】 TFT基板の品質を良好にし、TFT基板の製造コストを安価にする。

【解決手段】 厚さ60nmのCr膜28、厚さ300nmのAl−Si膜29をスパッタリングにより連続成膜し、この上にレジストパターン(図示せず)を形成し、このレジストをマスクにしてAl−Si膜29をリン酸:硝酸:酢酸:水系のエッチング液を使用したウエットエッチングにより加工したのち、Cr膜28をCF4+O2ガスを使用したドライエッチングにより加工し、画素電極24と接続されたソース電極31、映像信号線(図示せず)と接続されたドレイン電極32を形成し、つぎにN+型非晶質Si膜をSF6+HClガスを使用したドライエッチングにより加工し、N+型半導体層27を形成する。

【解決手段】 厚さ60nmのCr膜28、厚さ300nmのAl−Si膜29をスパッタリングにより連続成膜し、この上にレジストパターン(図示せず)を形成し、このレジストをマスクにしてAl−Si膜29をリン酸:硝酸:酢酸:水系のエッチング液を使用したウエットエッチングにより加工したのち、Cr膜28をCF4+O2ガスを使用したドライエッチングにより加工し、画素電極24と接続されたソース電極31、映像信号線(図示せず)と接続されたドレイン電極32を形成し、つぎにN+型非晶質Si膜をSF6+HClガスを使用したドライエッチングにより加工し、N+型半導体層27を形成する。

【発明の詳細な説明】

【0001】

【発明の属する技術分野】本発明はアクティブ・マトリックス方式の液晶表示装置のTFT(Thin FilmTransistor;薄膜トランジスタ)を有するTFT基板の製造方法に関するものである。

【0002】

【従来の技術】図4により従来の逆スタガ型のTFT基板の製造方法について説明する。まず、図4(a)に示すように、ガラス基板1上にAl膜を成膜し、Al膜をホトエッチングプロセスによりパターン化し、走査信号線(図示せず)と接続されたゲート電極2を形成する。つぎに、図4(b)に示すように、陽極酸化処理を行なうことによりゲート電極2等の表面にAl2O3からなる陽極酸化膜3を形成する。つぎに、図4(c)に示すように、ITO(Indium-Tin-Oxide)膜を成膜し、ITO膜をホトエッチングプロセスによりパターン化し、画素電極4を形成する。つぎに、図4(d)に示すように、プラズマCVD法によりSiN膜、導電型決定不純物がドープされていないi型非晶質Si(a−Si)膜、リン(P)をドープしたN+型非晶質Si膜を連続成膜し、i型非晶質Si膜、N+型非晶質Si膜をホトエッチングプロセスによりパターン化して、i型半導体層6を形成したのち、SiN膜をホトエッチングプロセスによりパターン化して、ゲート絶縁膜となる絶縁膜5を形成する。つぎに、図4(e)および図5に示すように、Cr膜8、Al膜9をスパッタリングにより連続成膜し、この上にレジストパターン(図示せず)を形成し、このレジストをマスクにしてAl膜9をウエットエッチングにより加工したのち、Cr膜8をウエットエッチングにより加工し、画素電極4と接続されたソース電極11、映像信号線(図示せず)と接続されたドレイン電極12を形成する。つぎに、N+型非晶質Si膜をドライエッチングにより加工し、N+型半導体層7を形成したのち、レジストを剥離し、ゲート電極2、i型半導体層6、ソース電極11、ドレイン電極12等からなるTFT13を設ける。つぎに、図4(f)に示すように、プラズマCVD法によりSiN膜を成膜し、SiN膜をホトエッチングプロセスによりパターン化し、保護膜10を形成する。

【0003】

【発明が解決しようとする課題】しかし、このようなTFT基板の製造方法においては、Cr膜8をウエットエッチングするときに、レジストがあるものの実質的にはAl膜9がマスクとなるから、図6に示すように、Al膜9がCr膜8よりも突き出した構造となるので、保護膜10がAl膜9のひさしの下に回り込むことができないため、空洞14が形成されてしまうから、TFT基板の品質を低下させる。たとえば、空洞14部がエッチング液、レジスト剥離液等で汚染されやすく、保護膜10にピンホールが1つでもあると、保護膜10形成時のエッチング液等がそのピンホールを介して空洞14に侵入し、空洞14がエッチング液等の通路になって、広範囲のCr膜8、Al膜9が損傷する。また、空洞14が形成されると、図7に示すように、保護膜10にクラック15が発生することがある。さらに、製造コストを低減するために保護膜10の厚さを小さくしたときには、図8R>8に示すように、空洞14部に保護膜10が形成されないことがあるから、製造コストが高価となったとしても保護膜10を厚くする必要がある。

【0004】本発明は上述の課題を解決するためになされたもので、TFT基板の品質が良好であり、TFT基板の製造コストが安価なTFT基板の製造方法を提供することを目的とする。

【0005】

【課題を解決するための手段】この目的を達成するため、本発明においては、ソース電極、ドレイン電極が第1、第2の金属膜から形成されたTFT基板を製造する方法において、上記第1、第2の金属膜を連続成膜したのち、上記第2の金属膜をウエットエッチングにより加工し、上記第1の金属膜をドライエッチングにより加工する。

【0006】この場合、上記第1の金属膜をドライエッチングにより加工したのち、N+型非晶質Si膜をドライエッチングにより加工する。

【0007】

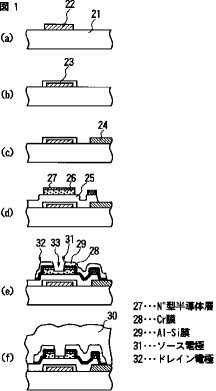

【発明の実施の形態】図1により本願発明に係る逆スタガ型のTFT基板の製造方法について説明する。まず、図1(a)に示すように、ガラス基板21上にスパッタ法により厚さ300nmのAl−Ti−Ta膜を成膜し、Al−Ti−Ta膜をホトエッチングプロセスによりパターン化し、走査信号線(図示せず)と接続されたゲート電極22を形成する。つぎに、図1(b)に示すように、陽極酸化処理を行なうことによりゲート電極22等の表面にAl2O3からなる厚さ180nmの陽極酸化膜23を形成する。つぎに、図1(c)に示すように、厚さ140nmのITO膜を成膜し、ITO膜をホトエッチングプロセスによりパターン化し、画素電極24を形成する。つぎに、図1(d)に示すように、プラズマCVD法により厚さ240nmのSiN膜、導電型決定不純物がドープされていない厚さ200nmのi型非晶質Si膜、リンをドープした厚さ25nmのN+型非晶質Si膜を連続成膜し、i型非晶質Si膜、N+型非晶質Si膜をホトエッチングプロセスによりパターン化して、i型半導体層26を形成したのち、SiN膜をホトエッチングプロセスによりパターン化して、ゲート絶縁膜となる絶縁膜25を形成する。つぎに、図1(e)および図2に示すように、厚さ60nmのCr膜28、厚さ300nmのAl−Si膜29をスパッタリングにより連続成膜し、この上にレジストパターン(図示せず)を形成し、このレジストをマスクにしてAl−Si膜29をリン酸:硝酸:酢酸:水系のエッチング液を使用したウエットエッチングにより加工したのち、Cr膜28をCF4+O2ガスを使用したドライエッチングにより加工し、画素電極24と接続されたソース電極31、映像信号線(図示せず)と接続されたドレイン電極32を形成する。つぎに、N+型非晶質Si膜をSF6+HClガスを使用したドライエッチングにより加工し、N+型半導体層27を形成したのち、レジストを剥離し、ゲート電極22、i型半導体層26、ソース電極31、ドレイン電極32等からなるTFT33を設ける。つぎに、図1(f)に示すように、プラズマCVD法によりSiN膜を成膜し、SiN膜をホトエッチングプロセスによりパターン化し、保護膜30を形成する。

【0008】このTFT基板の製造方法においては、Cr膜28をドライエッチングにより加工するから、図3に示すように、Al−Si膜29がCr膜28よりも突き出した構造となることがないので、空洞が形成されることがない。このため、保護膜30にピンホールがあったとしても、広範囲のCr膜28、Al−Si膜29が損傷することがなく、また保護膜30にクラックが発生することがなく、さらに製造コストを低減するために保護膜30の厚さを小さくしたたとしても、保護膜30を全面に形成することができるから、保護膜30を薄くして製造コストが安価にすることができる。

【0009】なお、上述実施の形態においては、第1の金属膜としてCr膜28を用いたが、第1の金属膜としてCr−Mo膜等を用いてもよい。また、上述実施の形態においては、第2の金属膜としてAl−Si膜29を用いたが、第2の金属膜としてMo膜、Ti膜等を用いてもよい。また、上述実施の形態においては、N+型非晶質Si膜をSF6+HClガスを使用したドライエッチングにより加工し、N+型半導体層27を形成したが、N+型非晶質Si膜をCF4+O2ガスを使用したドライエッチングにより加工し、N+型半導体層27を形成してもよい。

【0010】

【発明の効果】以上説明したように、本発明に係るTFT基板の製造方法においては、第2の金属膜が第1の金属膜よりも突き出した構造となることがないから、空洞が形成されることがないので、TFT基板の品質が良好であり、また保護膜を薄くすることができるため、TFT基板の製造コストが安価になる。

【図面の簡単な説明】

【図1】本発明に係るTFT基板の製造方法の説明図である。

【図2】本発明に係るTFT基板の製造方法の説明図である。

【図3】本発明に係るTFT基板の製造方法で製造したTFT基板の一部を示す断面図である。

【図4】従来のTFT基板の製造方法の説明図である。

【図5】従来のTFT基板の製造方法の説明図である。

【図6】従来のTFT基板の製造方法で製造したTFT基板の一部を示す断面図である。

【図7】従来のTFT基板の製造方法で製造した他のTFT基板の一部を示す断面図である。

【図8】従来のTFT基板の製造方法で製造した他のTFT基板の一部を示す断面図である。

【符号の説明】

27…N+型半導体層

28…Cr膜

29…Al−Si膜

31…ソース電極

32…ドレイン電極

【0001】

【発明の属する技術分野】本発明はアクティブ・マトリックス方式の液晶表示装置のTFT(Thin FilmTransistor;薄膜トランジスタ)を有するTFT基板の製造方法に関するものである。

【0002】

【従来の技術】図4により従来の逆スタガ型のTFT基板の製造方法について説明する。まず、図4(a)に示すように、ガラス基板1上にAl膜を成膜し、Al膜をホトエッチングプロセスによりパターン化し、走査信号線(図示せず)と接続されたゲート電極2を形成する。つぎに、図4(b)に示すように、陽極酸化処理を行なうことによりゲート電極2等の表面にAl2O3からなる陽極酸化膜3を形成する。つぎに、図4(c)に示すように、ITO(Indium-Tin-Oxide)膜を成膜し、ITO膜をホトエッチングプロセスによりパターン化し、画素電極4を形成する。つぎに、図4(d)に示すように、プラズマCVD法によりSiN膜、導電型決定不純物がドープされていないi型非晶質Si(a−Si)膜、リン(P)をドープしたN+型非晶質Si膜を連続成膜し、i型非晶質Si膜、N+型非晶質Si膜をホトエッチングプロセスによりパターン化して、i型半導体層6を形成したのち、SiN膜をホトエッチングプロセスによりパターン化して、ゲート絶縁膜となる絶縁膜5を形成する。つぎに、図4(e)および図5に示すように、Cr膜8、Al膜9をスパッタリングにより連続成膜し、この上にレジストパターン(図示せず)を形成し、このレジストをマスクにしてAl膜9をウエットエッチングにより加工したのち、Cr膜8をウエットエッチングにより加工し、画素電極4と接続されたソース電極11、映像信号線(図示せず)と接続されたドレイン電極12を形成する。つぎに、N+型非晶質Si膜をドライエッチングにより加工し、N+型半導体層7を形成したのち、レジストを剥離し、ゲート電極2、i型半導体層6、ソース電極11、ドレイン電極12等からなるTFT13を設ける。つぎに、図4(f)に示すように、プラズマCVD法によりSiN膜を成膜し、SiN膜をホトエッチングプロセスによりパターン化し、保護膜10を形成する。

【0003】

【発明が解決しようとする課題】しかし、このようなTFT基板の製造方法においては、Cr膜8をウエットエッチングするときに、レジストがあるものの実質的にはAl膜9がマスクとなるから、図6に示すように、Al膜9がCr膜8よりも突き出した構造となるので、保護膜10がAl膜9のひさしの下に回り込むことができないため、空洞14が形成されてしまうから、TFT基板の品質を低下させる。たとえば、空洞14部がエッチング液、レジスト剥離液等で汚染されやすく、保護膜10にピンホールが1つでもあると、保護膜10形成時のエッチング液等がそのピンホールを介して空洞14に侵入し、空洞14がエッチング液等の通路になって、広範囲のCr膜8、Al膜9が損傷する。また、空洞14が形成されると、図7に示すように、保護膜10にクラック15が発生することがある。さらに、製造コストを低減するために保護膜10の厚さを小さくしたときには、図8R>8に示すように、空洞14部に保護膜10が形成されないことがあるから、製造コストが高価となったとしても保護膜10を厚くする必要がある。

【0004】本発明は上述の課題を解決するためになされたもので、TFT基板の品質が良好であり、TFT基板の製造コストが安価なTFT基板の製造方法を提供することを目的とする。

【0005】

【課題を解決するための手段】この目的を達成するため、本発明においては、ソース電極、ドレイン電極が第1、第2の金属膜から形成されたTFT基板を製造する方法において、上記第1、第2の金属膜を連続成膜したのち、上記第2の金属膜をウエットエッチングにより加工し、上記第1の金属膜をドライエッチングにより加工する。

【0006】この場合、上記第1の金属膜をドライエッチングにより加工したのち、N+型非晶質Si膜をドライエッチングにより加工する。

【0007】

【発明の実施の形態】図1により本願発明に係る逆スタガ型のTFT基板の製造方法について説明する。まず、図1(a)に示すように、ガラス基板21上にスパッタ法により厚さ300nmのAl−Ti−Ta膜を成膜し、Al−Ti−Ta膜をホトエッチングプロセスによりパターン化し、走査信号線(図示せず)と接続されたゲート電極22を形成する。つぎに、図1(b)に示すように、陽極酸化処理を行なうことによりゲート電極22等の表面にAl2O3からなる厚さ180nmの陽極酸化膜23を形成する。つぎに、図1(c)に示すように、厚さ140nmのITO膜を成膜し、ITO膜をホトエッチングプロセスによりパターン化し、画素電極24を形成する。つぎに、図1(d)に示すように、プラズマCVD法により厚さ240nmのSiN膜、導電型決定不純物がドープされていない厚さ200nmのi型非晶質Si膜、リンをドープした厚さ25nmのN+型非晶質Si膜を連続成膜し、i型非晶質Si膜、N+型非晶質Si膜をホトエッチングプロセスによりパターン化して、i型半導体層26を形成したのち、SiN膜をホトエッチングプロセスによりパターン化して、ゲート絶縁膜となる絶縁膜25を形成する。つぎに、図1(e)および図2に示すように、厚さ60nmのCr膜28、厚さ300nmのAl−Si膜29をスパッタリングにより連続成膜し、この上にレジストパターン(図示せず)を形成し、このレジストをマスクにしてAl−Si膜29をリン酸:硝酸:酢酸:水系のエッチング液を使用したウエットエッチングにより加工したのち、Cr膜28をCF4+O2ガスを使用したドライエッチングにより加工し、画素電極24と接続されたソース電極31、映像信号線(図示せず)と接続されたドレイン電極32を形成する。つぎに、N+型非晶質Si膜をSF6+HClガスを使用したドライエッチングにより加工し、N+型半導体層27を形成したのち、レジストを剥離し、ゲート電極22、i型半導体層26、ソース電極31、ドレイン電極32等からなるTFT33を設ける。つぎに、図1(f)に示すように、プラズマCVD法によりSiN膜を成膜し、SiN膜をホトエッチングプロセスによりパターン化し、保護膜30を形成する。

【0008】このTFT基板の製造方法においては、Cr膜28をドライエッチングにより加工するから、図3に示すように、Al−Si膜29がCr膜28よりも突き出した構造となることがないので、空洞が形成されることがない。このため、保護膜30にピンホールがあったとしても、広範囲のCr膜28、Al−Si膜29が損傷することがなく、また保護膜30にクラックが発生することがなく、さらに製造コストを低減するために保護膜30の厚さを小さくしたたとしても、保護膜30を全面に形成することができるから、保護膜30を薄くして製造コストが安価にすることができる。

【0009】なお、上述実施の形態においては、第1の金属膜としてCr膜28を用いたが、第1の金属膜としてCr−Mo膜等を用いてもよい。また、上述実施の形態においては、第2の金属膜としてAl−Si膜29を用いたが、第2の金属膜としてMo膜、Ti膜等を用いてもよい。また、上述実施の形態においては、N+型非晶質Si膜をSF6+HClガスを使用したドライエッチングにより加工し、N+型半導体層27を形成したが、N+型非晶質Si膜をCF4+O2ガスを使用したドライエッチングにより加工し、N+型半導体層27を形成してもよい。

【0010】

【発明の効果】以上説明したように、本発明に係るTFT基板の製造方法においては、第2の金属膜が第1の金属膜よりも突き出した構造となることがないから、空洞が形成されることがないので、TFT基板の品質が良好であり、また保護膜を薄くすることができるため、TFT基板の製造コストが安価になる。

【図面の簡単な説明】

【図1】本発明に係るTFT基板の製造方法の説明図である。

【図2】本発明に係るTFT基板の製造方法の説明図である。

【図3】本発明に係るTFT基板の製造方法で製造したTFT基板の一部を示す断面図である。

【図4】従来のTFT基板の製造方法の説明図である。

【図5】従来のTFT基板の製造方法の説明図である。

【図6】従来のTFT基板の製造方法で製造したTFT基板の一部を示す断面図である。

【図7】従来のTFT基板の製造方法で製造した他のTFT基板の一部を示す断面図である。

【図8】従来のTFT基板の製造方法で製造した他のTFT基板の一部を示す断面図である。

【符号の説明】

27…N+型半導体層

28…Cr膜

29…Al−Si膜

31…ソース電極

32…ドレイン電極

【特許請求の範囲】

【請求項1】ソース電極、ドレイン電極が第1、第2の金属膜から形成されたTFT基板を製造する方法において、上記第1、第2の金属膜を連続成膜したのち、上記第2の金属膜をウエットエッチングにより加工し、上記第1の金属膜をドライエッチングにより加工することを特徴とするTFT基板の製造方法。

【請求項2】上記第1の金属膜をドライエッチングにより加工したのち、N+型非晶質Si膜をドライエッチングにより加工することを特徴とする請求項1に記載のTFT基板の製造方法。

【請求項1】ソース電極、ドレイン電極が第1、第2の金属膜から形成されたTFT基板を製造する方法において、上記第1、第2の金属膜を連続成膜したのち、上記第2の金属膜をウエットエッチングにより加工し、上記第1の金属膜をドライエッチングにより加工することを特徴とするTFT基板の製造方法。

【請求項2】上記第1の金属膜をドライエッチングにより加工したのち、N+型非晶質Si膜をドライエッチングにより加工することを特徴とする請求項1に記載のTFT基板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開平10−27910

【公開日】平成10年(1998)1月27日

【国際特許分類】

【出願番号】特願平8−181787

【出願日】平成8年(1996)7月11日

【出願人】(000005108)株式会社日立製作所 (27,607)

【公開日】平成10年(1998)1月27日

【国際特許分類】

【出願日】平成8年(1996)7月11日

【出願人】(000005108)株式会社日立製作所 (27,607)

[ Back to top ]