USB下位ユニットおよびUSBシステム

【課題】USB上位ユニットから送出されるVBUS電源を利用してリセットおよび電源オン/オフが可能であることに加え、電源オフ時の消費電力がゼロであるUSB下位ユニットを提供する。

【解決手段】 VBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部40を有している。レジューム制御部40は、オンになったVBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段としてのFET43を備えている。

【解決手段】 VBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部40を有している。レジューム制御部40は、オンになったVBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段としてのFET43を備えている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、USB(Universal Serial Bus)インターフェースを介してUSB上位ユニットに接続されるセルフパワード方式のUSB下位ユニットに関し、特に、USBインターフェースを介してUSB上位ユニットから供給される動作指示に応じてリセット、セルフパワー電源のオフおよびレジュームを行うUSB下位ユニットに関する。

【背景技術】

【0002】

例えばPOS(Point Of Sales)システムにおいて、POSホストと接続されるレジスタやチケット発券器等のPOS端末は、その動作を制御するコンピュータ本体(マザーボード)等の上位ユニットと、インターフェースを介して上位ユニットに接続され、上位ユニットからのコマンドに基づいてレシートやチケットを印刷するプリンタ等の下位ユニット(ファンクションとも呼ばれる)とを有している。近年、そのインターフェースとして、USBインターフェースが採用されることが多い。本明細書においては、USBインターフェースを介して相互に接続される上位ユニットおよび下位ユニットを、USB上位ユニットおよびUSB下位ユニットと呼ぶ。また、USBインターフェースを介して接続されたUSB上位ユニットとUSB下位ユニットとの組み合わせを、USBシステムと呼ぶ。尚、POS端末を例とした場合、プリンタ等のUSB下位ユニットとしては、USB上位ユニットと共に共通の筐体に収容された一体型と、USB上位ユニットとは個別の筐体に収容された周辺機器型とがある。

【0003】

一体型または周辺機器型のどちらであっても、プリンタ等のUSB下位ユニットは、用紙送りや用紙切断等のためのモータや印字ヘッドの熱源などの比較的大電力を要する構成要素を有しているため、消費電力が大きい。ここで、USB下位ユニットに電力を供給する電源方式としては、USBインターフェースの一ラインであるVBUSラインを通してUSB上位ユニットからVBUS電源(直流5V)を供給するバスライン方式と、USBインターフェースとは個別に商用電源からACアダプタ等ならびにセルフパワー電源コネクタを介してUSB下位ユニットに電力を供給するセルフパワード方式とがある。バスライン方式は供給可能な電力が比較的小さいため、プリンタ等の消費電力が大きいUSB下位ユニットにはセルフパワード方式が適用されるのが通常である。

【0004】

ところで、USB下位ユニットに動作異常が発生した場合、USB下位ユニットに備えられ、その動作を制御するUSBコントローラやユニットCPUにおける一時記憶データを初期化するリセットが必要である。また、USB下位ユニットを保守などで交換する際には、少なくともUSB下位ユニットの電源を所定時間以上遮断するセルフパワー電源のオフと、再投入するセルフパワー電源のレジュームとが必要である。尚、通常、レジュームの際には、電源オン時リセット(パワーオンリセット)と呼ばれるリセットが自動的になされる。

【0005】

ところが、USBインターフェースには従前のパラレルインターフェースやRS−232Cインターフェースのように上位ユニットから下位ユニットに対してリセット制御や電源制御を指示するためのラインが存在しない。このため、特にセルフパワード方式のUSB下位ユニットの場合、ユーザが人為的に電源オン時リセットを行うべく、USB下位ユニットの電源オフと、これに続いてレジュームを行う必要があった。しかし、USB上位ユニットと共に共通の筐体に収容された一体型のUSB下位ユニットの場合には、そのセルフパワー電源もUSB上位ユニットと共通のシステム電源であり、ユーザがこのシステム電源を遮断すると、USB上位ユニットへの電源供給も遮断されることになる。USB上位ユニットへの電源供給が遮断されると、オペレーションシステムの再起動処理が必要になる。オペレーションシステムの再起動処理にはかなりの時間を要するため、USB上位ユニットが正常に動作しているにも拘わらずUSB下位ユニットのリセットのみのためにオペレーションシステムの再起動処理が実行されることは、不合理である。一方、USB上位ユニットとは個別の筐体に収容された周辺機器型のUSB下位ユニットの場合には、そのセルフパワー電源は、USB上位ユニット用とは個別のUSB下位ユニットに専用の電源である。このため、USB上位ユニットのオペレーションシステムの再起動を伴うことなく、USB下位ユニットへの電源供給のみを遮断することが可能である。しかし、レシートやチケット用のプリンタなどの場合には、これら下位ユニットに専用の電源ボタンの類を具備していなかったり、具備していたとしてもユーザが容易に操作することができない筐体内部などに配置されていることが多い。

【0006】

このため、一体型または周辺機器型のどちらであっても、USB上位ユニットの電源は入った状態で、セルフパワード方式のUSB下位ユニットのリセットやセルフパワー電源のオフやレジュームをUSB上位ユニットから制御できることが市場から望まれている。

【0007】

このような市場要求の一解法として、例えば、特許文献1には、USBインターフェースを介してUSB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてリセットやセルフパワー電源のオフやレジュームを行うUSB下位ユニットが開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2006−48496号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

特許文献1に開示された技術において、USB下位ユニットは、VBUS電源の所定長のオフ時間に基づいて、省エネモードなるセルフパワー電源のオフ状態に移行可能である。しかし、この省エネモード時には、USB上位ユニットからのセルフパワー電源のレジューム(省エネモードからの復旧)を指示するVBUS電源入力の検知を待機するために、VBUSオン/オフ検知回路、機器制御回路、USBデバイスチップ等が必須に動作を持続している。これら動作を持続している回路には、セルフパワー電源を降圧させた電力が供給されている。つまり、USB下位ユニットのセルフパワー電源は、完全には遮断されない。USB上位ユニットからのセルフパワー電源のレジューム指示は不定期であるため、長時間に亘ってセルフパワー電源が完全には遮断されない状態を維持しなければならない場合もあり得、このことは、省エネルギの観点からは好ましくない。

【0010】

また、USB下位ユニットの電源が完全には遮断されていない状態、即ち、USB下位ユニットの負荷容量がゼロになっていない状態においては、過電流(突入電流)が発生するため、セルフパワー電源コネクタの活栓抜挿を行うことができない。

【0011】

それ故、本発明の課題は、USB上位ユニットから供給されるVBUS電源を利用してリセットおよびセルフパワー電源のオフやレジュームが可能であることに加え、電源オフ時の消費電力がゼロであるUSB下位ユニットを提供することである。

【0012】

本発明の他の課題は、そのようなUSB下位ユニットを有するUSBシステムを提供することである。

【課題を解決するための手段】

【0013】

本発明によれば、USBインターフェースを介してUSB上位ユニットと接続されるセルフパワード方式のUSB下位ユニットであって、USB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてUSB下位ユニットの一時的記憶内容のリセットまたはセルフパワー電源のオフを行うリセット/オフ制御部を有するUSB下位ユニットにおいて、USB上位ユニットから供給されるVBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部と、前記USB下位ユニット全体の動作を制御するユニットCPUとを有し、前記レジューム制御部は、VBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段と、前記スイッチ手段によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器とを備え、前記セルフパワー電源制御器は、VBUS電源を駆動電源として、前記リセット/オフ制御部から出力されるセルフパワー電源のオフを指示する電源オフ指示信号と、VBUS電源のオフからオンへの立ち上がりとの排他制御で前記スイッチ手段を操作し、前記リセット/オフ制御部は、PLDやICの組み合わせによって構成されたコントロールロジックと、VBUS電源のオフ時間長を計測し、所定の時間でタイムアップするタイマとを備え、前記コントロールロジックは、VBUS電源のオン/オフを検出し、前記タイマが所定の時間でタイムアップする前にVBUS電源がオンするか否かに応じて、前記リセットを行うVBUSリセット信号または前記電源オフ指示信号を出力することを特徴とするUSB下位ユニットが得られる。

【0014】

尚、前記スイッチ手段は、FETによって構成されていてもよい。

【0015】

また、前記レジューム制御部は、前記スイッチ手段によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器をさらに備えており、該セルフパワー電源制御器は、VBUS電源を駆動電源として、前記リセット/オフ制御部から出力されるセルフパワー電源のオフを指示する電源オフ指示信号と、VBUS電源のオフからオンへの立ち上がりとの排他制御で前記スイッチ手段を操作するものであってもよい。

【0016】

さらに、VBUS電源のオフからオンへの立ち上がりに基づいてUSB下位ユニットの一時的記憶内容の電源オン時リセットを行うリセットICを有していてもよい。

【0017】

また、前記レジューム制御部は、VBUS電源を駆動電源とするか、または、駆動電源不要で、VBUS電源の立ち上がりを遅延させて前記スイッチ手段に送出する遅延回路をさらに備えていてもよい。

【0018】

さらに、前記リセット/オフ制御部から出力されるリセットを指示するリセット信号と、前記リセットICから出力される電源オン時リセットを指示する電源オン時リセット信号との排他制御を行うリセット制御器を有していてもよい。

【0019】

また、本発明によれば、前記USB下位ユニットと、前記USB上位ユニットとを有することを特徴とするUSBシステムが得られる。

【発明の効果】

【0020】

本発明によるUSB下位ユニットは、USB上位ユニットから送出されるVBUS電源を利用してリセットおよびセルフパワー電源のオフやレジュームが可能であることに加え、電源オフ時の消費電力がゼロである。

【図面の簡単な説明】

【0021】

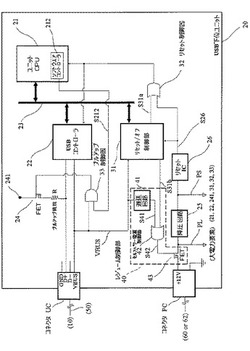

【図1】本発明の実施例によるUSBシステムの構成を示すブロック図である。

【図2】本発明の実施例によるUSB下位ユニットの構成を示すブロック図である。

【図3】図2に示されたUSB下位ユニットにおけるリセット/オフ制御部の一構成例を示すブロック図である。

【図4】図2に示されたUSB下位ユニットにおけるレジューム制御部の一構成例を示す図である。

【図5】(a)および(b)は、図4に示されたレジューム制御部における遅延回路のより具体的な構成例を示す図である。

【図6】図2に示されたUSB下位ユニットの動作を示すフロー図である。

【図7】図2に示されたUSB下位ユニットの動作を示すフロー図である。

【図8】図2に示されたUSB下位ユニットの動作を示すタイミング図である。

【図9】図2に示されたUSB下位ユニットの動作を示すタイミング図である。

【図10】図2に示されたUSB下位ユニットの動作を示すフロー図である。

【図11】図2に示されたUSB下位ユニットの動作を示すタイミング図である。

【図12】本発明の実施例によるUSBシステムの変形例を示すブロック図である。

【発明を実施するための形態】

【0022】

本発明によるUSB下位ユニットは、USBインターフェースを介してUSB上位ユニットと接続されるセルフパワード方式のUSB下位ユニットであって、USB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてリセットならびにセルフパワー電源のオフを行うリセット/オフ制御部を有している。

【0023】

特に、本USB下位ユニットは、VBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部を有している。レジューム制御部は、オンになったVBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段を備えている。

【0024】

このような構成により、本発明によるUSB下位ユニットは、USB上位ユニットから送出されるレジュームの指示に対して待機するときに電源を必要としない。よって、電源オフ時の消費電力がゼロである。

【実施例】

【0025】

以下、図面を参照して、本発明によるUSB下位ユニットおよびUSBシステムのより具体的な実施例を詳細に説明する。

【0026】

図1を参照すると、本発明の実施例によるUSBシステムは、POS端末であり、POS端末の動作を制御するマザーボードであるUSB上位ユニット10と、USBインターフェース50を介してUSB上位ユニット10に接続されたレシートプリンタであり、セルフパワード方式のUSB下位ユニット20とを有している。USB上位ユニット10およびUSB下位ユニット20は、共通の直流電源60から電源供給される。USB上位ユニット10、USB下位ユニット20、および直流電源60は、図示しない共通の筐体に収容されている。即ち、USB下位ユニット20は、一体型である。尚、符号UCはUSBコネクタを示し、符号PCはセルフパワー電源コネクタを示している。

【0027】

さらに図2を参照すると、本発明の実施例によるUSB下位ユニット20は、従来のUSB下位ユニットと同様に、USB下位ユニット20全体の動作を制御するユニットCPU21と、USBインターフェースに関連する動作を制御するUSBコントローラ22と、USB下位ユニット20内部のバスラインであるユニット内インターフェース(CPUインターフェース)23と、USBインターフェースにおけるD+信号用のプルアップ抵抗Rの有効/無効を切り替えるFET(Field Effect Transistor)24と、直流電源60から大電力要素に適した電圧(例えば12V)で供給されるセルフパワー電源(電源PL)をユニットCPU21やUSBコントローラ22等のロジック回路に適した電圧(例えば5V)の電源PSに降圧する降圧回路25と、レジューム時に電源オン時リセット信号S26を出力するリセットIC26と、USBコネクタUCと、セルフパワー電源コネクタPCと、図示しない電気モータや印字ヘッド等の大電力要素とを有している。

【0028】

USB下位ユニット20はまた、USB上位ユニット10から供給されるVBUS電源のオフ時間長に基づいてUSB下位ユニット20の一時的記憶内容のリセットまたはセルフパワー電源のオフを行うリセット/オフ制御部31と、リセット制御器32と、プルアップ制御器33とを有している。

【0029】

さらに図3を参照すると、リセット/オフ制御部31は、例えば、プリンタ(Programmable Logic Device)やIC(Integrated Circuit)の組み合わせによって構成されたコントロールロジック311と、VBUS電源のオフ時間長t1を計測するタイマ312とを備えている。コントロールロジック311は、VBUS電源のオフ/オン(立ち下がり/立ち上がり)を検出し、VBUS電源のオフ時間長により、VBUSリセット信号S31aまたは電源オフ指示信号S31bを出力する。VBUS電源を物理的リセット信号に生成し直すことをリセット/オフ制御部31で行う。タイマ312は、VBUS電源のオフ時間長t1を計時する。即ち、VBUS電源の立ち下がりでカウント開始し、VBUS電源の立ち上がりでカウントを停止する。しきい時間T1以内にコネクタUCからのVBUS電源の立ち上がりを検出した場合は、タイマ312を停止してVBUSリセット信号S31aを出力する。VBUSリセット信号S31aによりUSB下位ユニット20にリセットがかかる。尚、USB上位ユニット10のVBUS電源オン/オフ制御部11(図1)には、ユーザの操作に応じてリセット要求すべく、VBUS電源のオフ時間長がしきい時間T1以内となる様に設定されている。VBUS電源のオフ時間長がしきい時間T1を超過した場合、即ち、しきい時間T1以内にコネクタUCからのVBUS電源の立ち上がりを検出できなかった場合、電源オフ指示信号S31bを出力する。電源オフ指示を出力することにより電源コネクタPCからの電源供給を遮断し、USB下位ユニット20のセルフパワー電源をオフする。VBUS電源に連動して後述する遅延回路41から出力される遅延済VBUS電源S41は、電源オフ指示信号S31bと同様に、電源コネクタPCからの電源供給のオフオンを制御(スイッチ)するための指示信号である。しきい時間T1は、一般的にUSB下位ユニット20において通信障害等となった場合にUSBケーブルの抜き差しによる復旧処理を行うが、その一般的な抜き差し時間以上に設定される。このため、しきい時間T1は秒単位となり、一例として、しきい時間T1は5秒とする。リセット要求のためのVBUS電源のオフ時間長は、例えば、3秒に設定される。尚、しきい時間T1は、レジスタ設定等によって変更可能に設定される。

【0030】

尚、従来と同様にUSBケーブルの抜き差しにおけるサスペンド/レジューム処理に対応するため、コネクタUCからのVBUS電源は、リセット/オフ制御部31だけではなく、USBコントローラ22にも入力される。また、D+信号用のプルアップ抵抗Rの制御手段として、VBUS電源によるハードウエア制御のプルアップ制御器33だけではなく、ファームウエア制御が可能なソフトウェアコントローラ212も設けられている。

【0031】

さて、本発明によるUSB下位ユニット20は特に、USB上位ユニット10から供給されるVBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部40を有している。

【0032】

レジューム制御部40は、VBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段としてのFET43を備えている。

【0033】

レジューム制御部40はまた、FET43によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器42を備えている。セルフパワー電源制御器42は、VBUS電源を駆動電源として、リセット/オフ制御部31から出力されるセルフパワー電源のオフを指示する電源オフ指示信号S31bと、VBUS電源のオフからオンへの立ち上がりとの排他制御でFET43を操作する。したがって、電源オフ指示信号S31bがアサートされていても、VBUS電源の立ち上がりがあれば、FET43がオンされる。つまり、セルフパワー電源制御器42は、遅延済VBUS電源S41と電源オフ指示信号S31bとが共にアサートのときにセルフパワー電源がオフとなる一方、どちらか一方の信号がアサートかつ他方の信号がネゲートのときにセルフパワー電源がオンとなるように、FET43を操作する。そして、USB下位ユニット20にセルフパワー電源が供給されると、電源PLがモータや印字ヘッドなどの消費電力が大きい構成要素に供給されると共に、降圧回路25を経た電源PSがリセットIC26や、ユニットCPU21、USBコントローラ22、プルアップ抵抗Rの吊り電圧点241、リセット/オフ制御部31、リセット制御器32、プルアップ制御器33等のロジック回路に供給される。

【0034】

レジューム制御部40はさらに、VBUS電源を駆動電源とするか、または、駆動電源不要で、VBUS電源の立ち上がりを遅延させてFET43に送出する遅延回路41を備えている。遅延回路41は、電源オフ処理とコネクタUCからのVBUS電源の立ち上がりが同時に発生した場合に、VBUS電源の立ち上がりを検出し損なって電源オンしない、または、電源オン時リセットしないことを防止するための構成である。電源オフ指示信号S31bによってUSB下位ユニット20への電源が確実にオフされる(電源オン時リセットが発生する)までの時間以上の遅延時間を、遅延回路41は確保するものである。この遅延回路41により、遅延済VBUS電源S41による電源オンは、必ず電源オフ指示信号S31bによって電源オフされた後に電源オンするというタイミングシーケンスが確立される。

【0035】

さらに図4を参照すると、セルフパワー電源制御器42は、例えば、2つのFETによって構成される。また、遅延回路41は、図5(a)に示されるようなRC回路によって構成される(遅延回路41)。または、図5(b)に示されるようなVBUS電源を駆動電源とするリセットICによって構成される(遅延回路41’)。

【0036】

即ち、レジューム制御部40における遅延回路41、セルフパワー電源制御器42、およびスイッチ手段としてのFET43は、駆動電源が不要であるか、もしくは、オフからオンに立ち上がったVBUS電源を駆動電源として動作する回路である。このため、USB下位ユニット20は、USB上位ユニット10からレジュームを指示するVBUS電源の供給を待機する際、消費電力がゼロであり、完全に電源がオフにされる。よって、セルフパワー電源コネクタPCの活栓抜挿を行うことが可能である。

【0037】

尚、USB上位ユニット10(図1)からUSB下位ユニット20に対して通信を行おうとする場合、USB上位ユニット10からUSBインターフェース50を介してVBUS電源を供給してから、通信が開始される。

【0038】

前述のリセット制御器32は、リセット/オフ制御部31から出力されるリセットを指示するリセット信号S31aと、リセットIC26から出力される電源オン時リセット信号S26との排他制御を行う。つまり、リセット制御器32は、リセットIC26からの電源オン時リセット信号S26と、リセット/オフ制御部31からのVBUSリセット信号S31aとの論理和とする。尚、VBUSリセット信号S31aおよび電源オン時リセット信号S26のどちらも、一定時間長を持つパルス信号である。

【0039】

次に、USB下位ユニット20の動作を説明する。

【0040】

[1.VBUSリセットならびにセルフパワー電源オフ処理]

図2、図6、ならびに図8および図9を参照すると、USB上位ユニット10のVBUS電源オン/オフ制御部11(図1)による制御により、USBインターゲース50およびUSBコネクタUCを介したVBUS電源がオフになると(ステップn11)、USBコントローラ22へのVBUS電源がオフになる(ステップn12)。USBコントローラ22は、ユニットCPU21に対し、VBUS電源オフの旨をユニット内インテーフェース23を介して通知する(ステップn13)。

【0041】

VBUS電源オフを通知されたユニットCPU21は、USBインターフェース50をデタッチする(ステップn14)。

【0042】

ユニットCPU21のソウトウエアコントローラ212は、プルアップ信号S212を出力される(ステップn15)。

【0043】

VBUS電源オフを受けて、プルアップ制御器33は、FET24をオンからオフになるように操作する(ステップn16)。FET24はオンからオフに切り替わり、プルアップ抵抗Rへの通電が遮断される(ステップn17)。

【0044】

リセット/オフ制御部31に供給されるVBUS電源もオフになる(ステップn18)。このとき、リセット/オフ制御部31のコントロールロジック311は、VBUS電源の立ち下りを検出し(ステップn19)、計時開始の旨のタイマ操作信号S311を出力する(ステップn20)。タイマ操作信号S311を受け、リセット/オフ制御部31のタイマ312は、計時を開始する(ステップn21)。

【0045】

[1−1.VBUSリセット処理]

図2、図7、ならびに図8および図9を参照すると、VBUS電源がオンになる(VBUS電源のオフ時間長t1≦しきい時間T1である)と(ステップn22)、プルアップ制御器33の一方にVBUS電源が入力されると共に(ステップn31)、コントロールロジック311が計時停止の旨のタイマ操作信号S311を出力する(ステップn23)。タイマ操作信号S311を受け、タイマ312は、計時を停止すると共に、タイマクリアを実行する(ステップn24)。

【0046】

リセット/オフ制御部31(コントロールロジック311)は、リセット信号S31a(アサート)を出力する。なおかつ、リセット/オフ制御部31のリセットが実行される(ステップn25)。リセット信号S31aアサートを受けたリセット制御器32からのリセット信号S32により、ユニットCPU21、USB制御器22のリセットが実行される(ステップn26)。

【0047】

リセット終了後、ユニットCPU21のソウトウエアコントローラ212は、プルアップ信号S212を出力する(ステップn27)。プルアップ信号S212を受けたプルアップ制御器33は、FET24をオン操作する(ステップn28)。よって、プルアップ抵抗Rへの通電が再開し(ステップn29)、USB通信(エミュレーション)が開始される(ステップn30)。

【0048】

一方、ステップn22においてVBUS電源がオフのままであると、タイマ312がタイムカウントアップする(ステップn32)。

【0049】

[1−2.セルフパワー電源オフ処理]

VBUS電源のオフ時間t1がしきい時間1を超える(t1>T1)と(ステップn33)、タイマ312からのタイムアップ信号S312がコントロールロジック311に入力される(ステップn34)。

【0050】

タイムアップ信号S312を受け、リセット/オフ制御部31(コントロールロジック311)は、電源オフ指示信号S31bを出力する(ステップn35)。

【0051】

電源オフ指示信号S31bを受けたセルフパワー電源制御器42は、FET43をオフ操作し(ステップn36)、FET43がオフに切り替わる(ステップn37)。

【0052】

FET43がオフに切り替わることにより、大電力電源PLと、降圧回路25を経た小電力電源PSとが遮断される(ステップn38)。よって、USB下位ユニット20の電源が完全オフになり、消費電力がゼロの状態になる(ステップn39)。

【0053】

尚、図8および図9における※印が付されたシーケンスは、USB標準で規定された動作である。

【0054】

[2.セルフパワー電源レジューム処理]

[2A.セルフパワー電源レジューム処理]

図2、図10、ならびに図11を参照すると、VBUS電源がオフの時に、USB上位ユニット10のVBUS電源オン/オフ制御部11(図1)による制御により、USBインターゲース50およびUSBコネクタUCを介したVBUS電源がオンになると(ステップn41)、VBUS電源S41を受けて、プルアップ制御器33がFET24をオン操作する(ステップn42)。

【0055】

これと共に、VBUS電源オンを受けて、遅延回路41は、遅延済VBUS電源S41を出力する(ステップn43)。

【0056】

遅延済VBUS電源S41を受けて、セルフパワー電源制御器42は、FET43をオン操作する(ステップn44)。セルフパワー電源制御器42の操作により、操作FET43がオフからオンに切り替わり、大電力電源PL、小電力電源PSが供給再開される(ステップn45)。

【0057】

[2B.セルフパワー電源レジューム処理]

小電力電源PSが供給されると、リセットIC26は、電源オン時リセット信号S26を出力する(ステップn46)。

【0058】

電源オン時リセット信号S26を受けたリセット/オフ制御部31がリセットを実行する。具体的には、VBUSリセット信号をオフとすると共に、セルフパワー電源オフ指示信号をネゲートにする(ステップn47)。電源オン時リセット信号S26を受け、リセット制御器32は、リセット信号S32を出力する(ステップn48)。電源オン時リセット信号S26を受けたユニットCPU21、USBコントローラがリセットを実行する(ステップn49)。

【0059】

リセット終了後、ソウトウエアコントローラ212がプルアップ信号S212を出力する(ステップn50)。プルアップ信号S212を受けたプルアップ制御器33がFET24をオン操作する(ステップn51)。よって、プルアップ抵抗Rへの通電が再開し(ステップn52)、USB通信(エミュレーション)が開始される(ステップn53)。

【0060】

図11における※印が付されたシーケンスは、USB標準で規定された動作である。

【0061】

尚、以上の実施例において、本発明の実施例によるUSBシステムにおいて、USB上位ユニット10およびUSB下位ユニット20は共通の直流電源60から電源供給され、USB上位ユニット10、USB下位ユニット20、および直流電源60が図示しない共通の筐体に収容されていたが、本発明は、図12に示すように、USB上位ユニット10とUSB下位ユニット20とが個別のDC電源61とACアダプタ62とから電源供給され、USB上位ユニット10およびDC電源61と、USB下位ユニット20と、ACアダプタ60とが個別の筐体に収容されるものであってもよい。

【産業上の利用可能性】

【0062】

以上説明した実施例に限定されることなく、本発明は、当該特許請求の範囲に記載された技術範囲内であれば、種々の変形が可能であることは云うまでもない。例えば、本発明は、USBシステムインターフェースを介してUSB上位ユニットに接続されるI/O機器などのセルフパワード方式の各種USB下位ユニットに適用可能である。

【符号の説明】

【0063】

10 USB上位ユニット

11 VBUS電源オン/オフ制御部

20 USB下位ユニット

21 ユニットCPU

212 ソフトウェアコントローラ

22 USBコントローラ

23 CPUインターフェース(ユニット内インターフェース)

24 FET

25 降圧回路

26 リセットIC

31 リセット/オフ制御部

311 コントロールロジック

312 タイマ

32 リセット制御器

33 プルアップ制御器

40 レジューム制御部

41 遅延回路

42 セルフパワー電源制御器

43 FET

50 USBインターフェース

60 直流電源

R プルアップ抵抗

UC USBコネクタ

PC セルフパワー電源コネクタ

【技術分野】

【0001】

本発明は、USB(Universal Serial Bus)インターフェースを介してUSB上位ユニットに接続されるセルフパワード方式のUSB下位ユニットに関し、特に、USBインターフェースを介してUSB上位ユニットから供給される動作指示に応じてリセット、セルフパワー電源のオフおよびレジュームを行うUSB下位ユニットに関する。

【背景技術】

【0002】

例えばPOS(Point Of Sales)システムにおいて、POSホストと接続されるレジスタやチケット発券器等のPOS端末は、その動作を制御するコンピュータ本体(マザーボード)等の上位ユニットと、インターフェースを介して上位ユニットに接続され、上位ユニットからのコマンドに基づいてレシートやチケットを印刷するプリンタ等の下位ユニット(ファンクションとも呼ばれる)とを有している。近年、そのインターフェースとして、USBインターフェースが採用されることが多い。本明細書においては、USBインターフェースを介して相互に接続される上位ユニットおよび下位ユニットを、USB上位ユニットおよびUSB下位ユニットと呼ぶ。また、USBインターフェースを介して接続されたUSB上位ユニットとUSB下位ユニットとの組み合わせを、USBシステムと呼ぶ。尚、POS端末を例とした場合、プリンタ等のUSB下位ユニットとしては、USB上位ユニットと共に共通の筐体に収容された一体型と、USB上位ユニットとは個別の筐体に収容された周辺機器型とがある。

【0003】

一体型または周辺機器型のどちらであっても、プリンタ等のUSB下位ユニットは、用紙送りや用紙切断等のためのモータや印字ヘッドの熱源などの比較的大電力を要する構成要素を有しているため、消費電力が大きい。ここで、USB下位ユニットに電力を供給する電源方式としては、USBインターフェースの一ラインであるVBUSラインを通してUSB上位ユニットからVBUS電源(直流5V)を供給するバスライン方式と、USBインターフェースとは個別に商用電源からACアダプタ等ならびにセルフパワー電源コネクタを介してUSB下位ユニットに電力を供給するセルフパワード方式とがある。バスライン方式は供給可能な電力が比較的小さいため、プリンタ等の消費電力が大きいUSB下位ユニットにはセルフパワード方式が適用されるのが通常である。

【0004】

ところで、USB下位ユニットに動作異常が発生した場合、USB下位ユニットに備えられ、その動作を制御するUSBコントローラやユニットCPUにおける一時記憶データを初期化するリセットが必要である。また、USB下位ユニットを保守などで交換する際には、少なくともUSB下位ユニットの電源を所定時間以上遮断するセルフパワー電源のオフと、再投入するセルフパワー電源のレジュームとが必要である。尚、通常、レジュームの際には、電源オン時リセット(パワーオンリセット)と呼ばれるリセットが自動的になされる。

【0005】

ところが、USBインターフェースには従前のパラレルインターフェースやRS−232Cインターフェースのように上位ユニットから下位ユニットに対してリセット制御や電源制御を指示するためのラインが存在しない。このため、特にセルフパワード方式のUSB下位ユニットの場合、ユーザが人為的に電源オン時リセットを行うべく、USB下位ユニットの電源オフと、これに続いてレジュームを行う必要があった。しかし、USB上位ユニットと共に共通の筐体に収容された一体型のUSB下位ユニットの場合には、そのセルフパワー電源もUSB上位ユニットと共通のシステム電源であり、ユーザがこのシステム電源を遮断すると、USB上位ユニットへの電源供給も遮断されることになる。USB上位ユニットへの電源供給が遮断されると、オペレーションシステムの再起動処理が必要になる。オペレーションシステムの再起動処理にはかなりの時間を要するため、USB上位ユニットが正常に動作しているにも拘わらずUSB下位ユニットのリセットのみのためにオペレーションシステムの再起動処理が実行されることは、不合理である。一方、USB上位ユニットとは個別の筐体に収容された周辺機器型のUSB下位ユニットの場合には、そのセルフパワー電源は、USB上位ユニット用とは個別のUSB下位ユニットに専用の電源である。このため、USB上位ユニットのオペレーションシステムの再起動を伴うことなく、USB下位ユニットへの電源供給のみを遮断することが可能である。しかし、レシートやチケット用のプリンタなどの場合には、これら下位ユニットに専用の電源ボタンの類を具備していなかったり、具備していたとしてもユーザが容易に操作することができない筐体内部などに配置されていることが多い。

【0006】

このため、一体型または周辺機器型のどちらであっても、USB上位ユニットの電源は入った状態で、セルフパワード方式のUSB下位ユニットのリセットやセルフパワー電源のオフやレジュームをUSB上位ユニットから制御できることが市場から望まれている。

【0007】

このような市場要求の一解法として、例えば、特許文献1には、USBインターフェースを介してUSB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてリセットやセルフパワー電源のオフやレジュームを行うUSB下位ユニットが開示されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2006−48496号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

特許文献1に開示された技術において、USB下位ユニットは、VBUS電源の所定長のオフ時間に基づいて、省エネモードなるセルフパワー電源のオフ状態に移行可能である。しかし、この省エネモード時には、USB上位ユニットからのセルフパワー電源のレジューム(省エネモードからの復旧)を指示するVBUS電源入力の検知を待機するために、VBUSオン/オフ検知回路、機器制御回路、USBデバイスチップ等が必須に動作を持続している。これら動作を持続している回路には、セルフパワー電源を降圧させた電力が供給されている。つまり、USB下位ユニットのセルフパワー電源は、完全には遮断されない。USB上位ユニットからのセルフパワー電源のレジューム指示は不定期であるため、長時間に亘ってセルフパワー電源が完全には遮断されない状態を維持しなければならない場合もあり得、このことは、省エネルギの観点からは好ましくない。

【0010】

また、USB下位ユニットの電源が完全には遮断されていない状態、即ち、USB下位ユニットの負荷容量がゼロになっていない状態においては、過電流(突入電流)が発生するため、セルフパワー電源コネクタの活栓抜挿を行うことができない。

【0011】

それ故、本発明の課題は、USB上位ユニットから供給されるVBUS電源を利用してリセットおよびセルフパワー電源のオフやレジュームが可能であることに加え、電源オフ時の消費電力がゼロであるUSB下位ユニットを提供することである。

【0012】

本発明の他の課題は、そのようなUSB下位ユニットを有するUSBシステムを提供することである。

【課題を解決するための手段】

【0013】

本発明によれば、USBインターフェースを介してUSB上位ユニットと接続されるセルフパワード方式のUSB下位ユニットであって、USB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてUSB下位ユニットの一時的記憶内容のリセットまたはセルフパワー電源のオフを行うリセット/オフ制御部を有するUSB下位ユニットにおいて、USB上位ユニットから供給されるVBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部と、前記USB下位ユニット全体の動作を制御するユニットCPUとを有し、前記レジューム制御部は、VBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段と、前記スイッチ手段によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器とを備え、前記セルフパワー電源制御器は、VBUS電源を駆動電源として、前記リセット/オフ制御部から出力されるセルフパワー電源のオフを指示する電源オフ指示信号と、VBUS電源のオフからオンへの立ち上がりとの排他制御で前記スイッチ手段を操作し、前記リセット/オフ制御部は、PLDやICの組み合わせによって構成されたコントロールロジックと、VBUS電源のオフ時間長を計測し、所定の時間でタイムアップするタイマとを備え、前記コントロールロジックは、VBUS電源のオン/オフを検出し、前記タイマが所定の時間でタイムアップする前にVBUS電源がオンするか否かに応じて、前記リセットを行うVBUSリセット信号または前記電源オフ指示信号を出力することを特徴とするUSB下位ユニットが得られる。

【0014】

尚、前記スイッチ手段は、FETによって構成されていてもよい。

【0015】

また、前記レジューム制御部は、前記スイッチ手段によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器をさらに備えており、該セルフパワー電源制御器は、VBUS電源を駆動電源として、前記リセット/オフ制御部から出力されるセルフパワー電源のオフを指示する電源オフ指示信号と、VBUS電源のオフからオンへの立ち上がりとの排他制御で前記スイッチ手段を操作するものであってもよい。

【0016】

さらに、VBUS電源のオフからオンへの立ち上がりに基づいてUSB下位ユニットの一時的記憶内容の電源オン時リセットを行うリセットICを有していてもよい。

【0017】

また、前記レジューム制御部は、VBUS電源を駆動電源とするか、または、駆動電源不要で、VBUS電源の立ち上がりを遅延させて前記スイッチ手段に送出する遅延回路をさらに備えていてもよい。

【0018】

さらに、前記リセット/オフ制御部から出力されるリセットを指示するリセット信号と、前記リセットICから出力される電源オン時リセットを指示する電源オン時リセット信号との排他制御を行うリセット制御器を有していてもよい。

【0019】

また、本発明によれば、前記USB下位ユニットと、前記USB上位ユニットとを有することを特徴とするUSBシステムが得られる。

【発明の効果】

【0020】

本発明によるUSB下位ユニットは、USB上位ユニットから送出されるVBUS電源を利用してリセットおよびセルフパワー電源のオフやレジュームが可能であることに加え、電源オフ時の消費電力がゼロである。

【図面の簡単な説明】

【0021】

【図1】本発明の実施例によるUSBシステムの構成を示すブロック図である。

【図2】本発明の実施例によるUSB下位ユニットの構成を示すブロック図である。

【図3】図2に示されたUSB下位ユニットにおけるリセット/オフ制御部の一構成例を示すブロック図である。

【図4】図2に示されたUSB下位ユニットにおけるレジューム制御部の一構成例を示す図である。

【図5】(a)および(b)は、図4に示されたレジューム制御部における遅延回路のより具体的な構成例を示す図である。

【図6】図2に示されたUSB下位ユニットの動作を示すフロー図である。

【図7】図2に示されたUSB下位ユニットの動作を示すフロー図である。

【図8】図2に示されたUSB下位ユニットの動作を示すタイミング図である。

【図9】図2に示されたUSB下位ユニットの動作を示すタイミング図である。

【図10】図2に示されたUSB下位ユニットの動作を示すフロー図である。

【図11】図2に示されたUSB下位ユニットの動作を示すタイミング図である。

【図12】本発明の実施例によるUSBシステムの変形例を示すブロック図である。

【発明を実施するための形態】

【0022】

本発明によるUSB下位ユニットは、USBインターフェースを介してUSB上位ユニットと接続されるセルフパワード方式のUSB下位ユニットであって、USB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてリセットならびにセルフパワー電源のオフを行うリセット/オフ制御部を有している。

【0023】

特に、本USB下位ユニットは、VBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部を有している。レジューム制御部は、オンになったVBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段を備えている。

【0024】

このような構成により、本発明によるUSB下位ユニットは、USB上位ユニットから送出されるレジュームの指示に対して待機するときに電源を必要としない。よって、電源オフ時の消費電力がゼロである。

【実施例】

【0025】

以下、図面を参照して、本発明によるUSB下位ユニットおよびUSBシステムのより具体的な実施例を詳細に説明する。

【0026】

図1を参照すると、本発明の実施例によるUSBシステムは、POS端末であり、POS端末の動作を制御するマザーボードであるUSB上位ユニット10と、USBインターフェース50を介してUSB上位ユニット10に接続されたレシートプリンタであり、セルフパワード方式のUSB下位ユニット20とを有している。USB上位ユニット10およびUSB下位ユニット20は、共通の直流電源60から電源供給される。USB上位ユニット10、USB下位ユニット20、および直流電源60は、図示しない共通の筐体に収容されている。即ち、USB下位ユニット20は、一体型である。尚、符号UCはUSBコネクタを示し、符号PCはセルフパワー電源コネクタを示している。

【0027】

さらに図2を参照すると、本発明の実施例によるUSB下位ユニット20は、従来のUSB下位ユニットと同様に、USB下位ユニット20全体の動作を制御するユニットCPU21と、USBインターフェースに関連する動作を制御するUSBコントローラ22と、USB下位ユニット20内部のバスラインであるユニット内インターフェース(CPUインターフェース)23と、USBインターフェースにおけるD+信号用のプルアップ抵抗Rの有効/無効を切り替えるFET(Field Effect Transistor)24と、直流電源60から大電力要素に適した電圧(例えば12V)で供給されるセルフパワー電源(電源PL)をユニットCPU21やUSBコントローラ22等のロジック回路に適した電圧(例えば5V)の電源PSに降圧する降圧回路25と、レジューム時に電源オン時リセット信号S26を出力するリセットIC26と、USBコネクタUCと、セルフパワー電源コネクタPCと、図示しない電気モータや印字ヘッド等の大電力要素とを有している。

【0028】

USB下位ユニット20はまた、USB上位ユニット10から供給されるVBUS電源のオフ時間長に基づいてUSB下位ユニット20の一時的記憶内容のリセットまたはセルフパワー電源のオフを行うリセット/オフ制御部31と、リセット制御器32と、プルアップ制御器33とを有している。

【0029】

さらに図3を参照すると、リセット/オフ制御部31は、例えば、プリンタ(Programmable Logic Device)やIC(Integrated Circuit)の組み合わせによって構成されたコントロールロジック311と、VBUS電源のオフ時間長t1を計測するタイマ312とを備えている。コントロールロジック311は、VBUS電源のオフ/オン(立ち下がり/立ち上がり)を検出し、VBUS電源のオフ時間長により、VBUSリセット信号S31aまたは電源オフ指示信号S31bを出力する。VBUS電源を物理的リセット信号に生成し直すことをリセット/オフ制御部31で行う。タイマ312は、VBUS電源のオフ時間長t1を計時する。即ち、VBUS電源の立ち下がりでカウント開始し、VBUS電源の立ち上がりでカウントを停止する。しきい時間T1以内にコネクタUCからのVBUS電源の立ち上がりを検出した場合は、タイマ312を停止してVBUSリセット信号S31aを出力する。VBUSリセット信号S31aによりUSB下位ユニット20にリセットがかかる。尚、USB上位ユニット10のVBUS電源オン/オフ制御部11(図1)には、ユーザの操作に応じてリセット要求すべく、VBUS電源のオフ時間長がしきい時間T1以内となる様に設定されている。VBUS電源のオフ時間長がしきい時間T1を超過した場合、即ち、しきい時間T1以内にコネクタUCからのVBUS電源の立ち上がりを検出できなかった場合、電源オフ指示信号S31bを出力する。電源オフ指示を出力することにより電源コネクタPCからの電源供給を遮断し、USB下位ユニット20のセルフパワー電源をオフする。VBUS電源に連動して後述する遅延回路41から出力される遅延済VBUS電源S41は、電源オフ指示信号S31bと同様に、電源コネクタPCからの電源供給のオフオンを制御(スイッチ)するための指示信号である。しきい時間T1は、一般的にUSB下位ユニット20において通信障害等となった場合にUSBケーブルの抜き差しによる復旧処理を行うが、その一般的な抜き差し時間以上に設定される。このため、しきい時間T1は秒単位となり、一例として、しきい時間T1は5秒とする。リセット要求のためのVBUS電源のオフ時間長は、例えば、3秒に設定される。尚、しきい時間T1は、レジスタ設定等によって変更可能に設定される。

【0030】

尚、従来と同様にUSBケーブルの抜き差しにおけるサスペンド/レジューム処理に対応するため、コネクタUCからのVBUS電源は、リセット/オフ制御部31だけではなく、USBコントローラ22にも入力される。また、D+信号用のプルアップ抵抗Rの制御手段として、VBUS電源によるハードウエア制御のプルアップ制御器33だけではなく、ファームウエア制御が可能なソフトウェアコントローラ212も設けられている。

【0031】

さて、本発明によるUSB下位ユニット20は特に、USB上位ユニット10から供給されるVBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部40を有している。

【0032】

レジューム制御部40は、VBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段としてのFET43を備えている。

【0033】

レジューム制御部40はまた、FET43によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器42を備えている。セルフパワー電源制御器42は、VBUS電源を駆動電源として、リセット/オフ制御部31から出力されるセルフパワー電源のオフを指示する電源オフ指示信号S31bと、VBUS電源のオフからオンへの立ち上がりとの排他制御でFET43を操作する。したがって、電源オフ指示信号S31bがアサートされていても、VBUS電源の立ち上がりがあれば、FET43がオンされる。つまり、セルフパワー電源制御器42は、遅延済VBUS電源S41と電源オフ指示信号S31bとが共にアサートのときにセルフパワー電源がオフとなる一方、どちらか一方の信号がアサートかつ他方の信号がネゲートのときにセルフパワー電源がオンとなるように、FET43を操作する。そして、USB下位ユニット20にセルフパワー電源が供給されると、電源PLがモータや印字ヘッドなどの消費電力が大きい構成要素に供給されると共に、降圧回路25を経た電源PSがリセットIC26や、ユニットCPU21、USBコントローラ22、プルアップ抵抗Rの吊り電圧点241、リセット/オフ制御部31、リセット制御器32、プルアップ制御器33等のロジック回路に供給される。

【0034】

レジューム制御部40はさらに、VBUS電源を駆動電源とするか、または、駆動電源不要で、VBUS電源の立ち上がりを遅延させてFET43に送出する遅延回路41を備えている。遅延回路41は、電源オフ処理とコネクタUCからのVBUS電源の立ち上がりが同時に発生した場合に、VBUS電源の立ち上がりを検出し損なって電源オンしない、または、電源オン時リセットしないことを防止するための構成である。電源オフ指示信号S31bによってUSB下位ユニット20への電源が確実にオフされる(電源オン時リセットが発生する)までの時間以上の遅延時間を、遅延回路41は確保するものである。この遅延回路41により、遅延済VBUS電源S41による電源オンは、必ず電源オフ指示信号S31bによって電源オフされた後に電源オンするというタイミングシーケンスが確立される。

【0035】

さらに図4を参照すると、セルフパワー電源制御器42は、例えば、2つのFETによって構成される。また、遅延回路41は、図5(a)に示されるようなRC回路によって構成される(遅延回路41)。または、図5(b)に示されるようなVBUS電源を駆動電源とするリセットICによって構成される(遅延回路41’)。

【0036】

即ち、レジューム制御部40における遅延回路41、セルフパワー電源制御器42、およびスイッチ手段としてのFET43は、駆動電源が不要であるか、もしくは、オフからオンに立ち上がったVBUS電源を駆動電源として動作する回路である。このため、USB下位ユニット20は、USB上位ユニット10からレジュームを指示するVBUS電源の供給を待機する際、消費電力がゼロであり、完全に電源がオフにされる。よって、セルフパワー電源コネクタPCの活栓抜挿を行うことが可能である。

【0037】

尚、USB上位ユニット10(図1)からUSB下位ユニット20に対して通信を行おうとする場合、USB上位ユニット10からUSBインターフェース50を介してVBUS電源を供給してから、通信が開始される。

【0038】

前述のリセット制御器32は、リセット/オフ制御部31から出力されるリセットを指示するリセット信号S31aと、リセットIC26から出力される電源オン時リセット信号S26との排他制御を行う。つまり、リセット制御器32は、リセットIC26からの電源オン時リセット信号S26と、リセット/オフ制御部31からのVBUSリセット信号S31aとの論理和とする。尚、VBUSリセット信号S31aおよび電源オン時リセット信号S26のどちらも、一定時間長を持つパルス信号である。

【0039】

次に、USB下位ユニット20の動作を説明する。

【0040】

[1.VBUSリセットならびにセルフパワー電源オフ処理]

図2、図6、ならびに図8および図9を参照すると、USB上位ユニット10のVBUS電源オン/オフ制御部11(図1)による制御により、USBインターゲース50およびUSBコネクタUCを介したVBUS電源がオフになると(ステップn11)、USBコントローラ22へのVBUS電源がオフになる(ステップn12)。USBコントローラ22は、ユニットCPU21に対し、VBUS電源オフの旨をユニット内インテーフェース23を介して通知する(ステップn13)。

【0041】

VBUS電源オフを通知されたユニットCPU21は、USBインターフェース50をデタッチする(ステップn14)。

【0042】

ユニットCPU21のソウトウエアコントローラ212は、プルアップ信号S212を出力される(ステップn15)。

【0043】

VBUS電源オフを受けて、プルアップ制御器33は、FET24をオンからオフになるように操作する(ステップn16)。FET24はオンからオフに切り替わり、プルアップ抵抗Rへの通電が遮断される(ステップn17)。

【0044】

リセット/オフ制御部31に供給されるVBUS電源もオフになる(ステップn18)。このとき、リセット/オフ制御部31のコントロールロジック311は、VBUS電源の立ち下りを検出し(ステップn19)、計時開始の旨のタイマ操作信号S311を出力する(ステップn20)。タイマ操作信号S311を受け、リセット/オフ制御部31のタイマ312は、計時を開始する(ステップn21)。

【0045】

[1−1.VBUSリセット処理]

図2、図7、ならびに図8および図9を参照すると、VBUS電源がオンになる(VBUS電源のオフ時間長t1≦しきい時間T1である)と(ステップn22)、プルアップ制御器33の一方にVBUS電源が入力されると共に(ステップn31)、コントロールロジック311が計時停止の旨のタイマ操作信号S311を出力する(ステップn23)。タイマ操作信号S311を受け、タイマ312は、計時を停止すると共に、タイマクリアを実行する(ステップn24)。

【0046】

リセット/オフ制御部31(コントロールロジック311)は、リセット信号S31a(アサート)を出力する。なおかつ、リセット/オフ制御部31のリセットが実行される(ステップn25)。リセット信号S31aアサートを受けたリセット制御器32からのリセット信号S32により、ユニットCPU21、USB制御器22のリセットが実行される(ステップn26)。

【0047】

リセット終了後、ユニットCPU21のソウトウエアコントローラ212は、プルアップ信号S212を出力する(ステップn27)。プルアップ信号S212を受けたプルアップ制御器33は、FET24をオン操作する(ステップn28)。よって、プルアップ抵抗Rへの通電が再開し(ステップn29)、USB通信(エミュレーション)が開始される(ステップn30)。

【0048】

一方、ステップn22においてVBUS電源がオフのままであると、タイマ312がタイムカウントアップする(ステップn32)。

【0049】

[1−2.セルフパワー電源オフ処理]

VBUS電源のオフ時間t1がしきい時間1を超える(t1>T1)と(ステップn33)、タイマ312からのタイムアップ信号S312がコントロールロジック311に入力される(ステップn34)。

【0050】

タイムアップ信号S312を受け、リセット/オフ制御部31(コントロールロジック311)は、電源オフ指示信号S31bを出力する(ステップn35)。

【0051】

電源オフ指示信号S31bを受けたセルフパワー電源制御器42は、FET43をオフ操作し(ステップn36)、FET43がオフに切り替わる(ステップn37)。

【0052】

FET43がオフに切り替わることにより、大電力電源PLと、降圧回路25を経た小電力電源PSとが遮断される(ステップn38)。よって、USB下位ユニット20の電源が完全オフになり、消費電力がゼロの状態になる(ステップn39)。

【0053】

尚、図8および図9における※印が付されたシーケンスは、USB標準で規定された動作である。

【0054】

[2.セルフパワー電源レジューム処理]

[2A.セルフパワー電源レジューム処理]

図2、図10、ならびに図11を参照すると、VBUS電源がオフの時に、USB上位ユニット10のVBUS電源オン/オフ制御部11(図1)による制御により、USBインターゲース50およびUSBコネクタUCを介したVBUS電源がオンになると(ステップn41)、VBUS電源S41を受けて、プルアップ制御器33がFET24をオン操作する(ステップn42)。

【0055】

これと共に、VBUS電源オンを受けて、遅延回路41は、遅延済VBUS電源S41を出力する(ステップn43)。

【0056】

遅延済VBUS電源S41を受けて、セルフパワー電源制御器42は、FET43をオン操作する(ステップn44)。セルフパワー電源制御器42の操作により、操作FET43がオフからオンに切り替わり、大電力電源PL、小電力電源PSが供給再開される(ステップn45)。

【0057】

[2B.セルフパワー電源レジューム処理]

小電力電源PSが供給されると、リセットIC26は、電源オン時リセット信号S26を出力する(ステップn46)。

【0058】

電源オン時リセット信号S26を受けたリセット/オフ制御部31がリセットを実行する。具体的には、VBUSリセット信号をオフとすると共に、セルフパワー電源オフ指示信号をネゲートにする(ステップn47)。電源オン時リセット信号S26を受け、リセット制御器32は、リセット信号S32を出力する(ステップn48)。電源オン時リセット信号S26を受けたユニットCPU21、USBコントローラがリセットを実行する(ステップn49)。

【0059】

リセット終了後、ソウトウエアコントローラ212がプルアップ信号S212を出力する(ステップn50)。プルアップ信号S212を受けたプルアップ制御器33がFET24をオン操作する(ステップn51)。よって、プルアップ抵抗Rへの通電が再開し(ステップn52)、USB通信(エミュレーション)が開始される(ステップn53)。

【0060】

図11における※印が付されたシーケンスは、USB標準で規定された動作である。

【0061】

尚、以上の実施例において、本発明の実施例によるUSBシステムにおいて、USB上位ユニット10およびUSB下位ユニット20は共通の直流電源60から電源供給され、USB上位ユニット10、USB下位ユニット20、および直流電源60が図示しない共通の筐体に収容されていたが、本発明は、図12に示すように、USB上位ユニット10とUSB下位ユニット20とが個別のDC電源61とACアダプタ62とから電源供給され、USB上位ユニット10およびDC電源61と、USB下位ユニット20と、ACアダプタ60とが個別の筐体に収容されるものであってもよい。

【産業上の利用可能性】

【0062】

以上説明した実施例に限定されることなく、本発明は、当該特許請求の範囲に記載された技術範囲内であれば、種々の変形が可能であることは云うまでもない。例えば、本発明は、USBシステムインターフェースを介してUSB上位ユニットに接続されるI/O機器などのセルフパワード方式の各種USB下位ユニットに適用可能である。

【符号の説明】

【0063】

10 USB上位ユニット

11 VBUS電源オン/オフ制御部

20 USB下位ユニット

21 ユニットCPU

212 ソフトウェアコントローラ

22 USBコントローラ

23 CPUインターフェース(ユニット内インターフェース)

24 FET

25 降圧回路

26 リセットIC

31 リセット/オフ制御部

311 コントロールロジック

312 タイマ

32 リセット制御器

33 プルアップ制御器

40 レジューム制御部

41 遅延回路

42 セルフパワー電源制御器

43 FET

50 USBインターフェース

60 直流電源

R プルアップ抵抗

UC USBコネクタ

PC セルフパワー電源コネクタ

【特許請求の範囲】

【請求項1】

USBインターフェースを介してUSB上位ユニットと接続されるセルフパワード方式のUSB下位ユニットであって、USB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてUSB下位ユニットの一時的記憶内容のリセットまたはセルフパワー電源のオフを行うリセット/オフ制御部を有するUSB下位ユニットにおいて、

USB上位ユニットから供給されるVBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部と、前記USB下位ユニット全体の動作を制御するユニットCPUとを有し、

前記レジューム制御部は、

VBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段と、

前記スイッチ手段によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器とを備え、

前記セルフパワー電源制御器は、VBUS電源を駆動電源として、前記リセット/オフ制御部から出力されるセルフパワー電源のオフを指示する電源オフ指示信号と、VBUS電源のオフからオンへの立ち上がりとの排他制御で前記スイッチ手段を操作し、

前記リセット/オフ制御部は、

PLDやICの組み合わせによって構成されたコントロールロジックと、

VBUS電源のオフ時間長を計測し、所定の時間でタイムアップするタイマとを備え、

前記コントロールロジックは、VBUS電源のオン/オフを検出し、前記タイマが所定の時間でタイムアップする前にVBUS電源がオンするか否かに応じて、前記リセットを行うVBUSリセット信号または前記電源オフ指示信号を出力することを特徴とするUSB下位ユニット。

【請求項2】

前記コントロールロジックは、

VBUS電源の立ち下がりを検出して前記タイマに計時開始の信号を出力し、

前記タイマが所定の時間でタイムアップする前にVBUS電源がオンすると、前記タイマに計時停止の信号を出力して前記リセット信号を出力し、

前記タイマが所定の時間でタイムアップしてタイムアップ信号を受け取ると、前記電源オフ指示信号を出力する請求項1に記載のUSB下位ユニット。

【請求項3】

前記スイッチ手段は、FETによって構成されている請求項1または2に記載のUSB下位ユニット。

【請求項4】

VBUS電源のオフからオンへの立ち上がりによってセルフパワー電源がオンされたことに基づいてUSB下位ユニットの一時的記憶内容の電源オン時リセットを行うリセットICを有する請求項1乃至3のいずれか1つに記載のUSB下位ユニット。

【請求項5】

前記レジューム制御部は、VBUS電源を駆動電源とするか、または、駆動電源不要で、VBUS電源の立ち上がりを遅延させて前記スイッチ手段に送出する遅延回路をさらに備えている請求項1に記載のUSB下位ユニット。

【請求項6】

前記リセット/オフ制御部から出力されるリセットを指示するリセット信号と、前記リセットICから出力される電源オン時リセットを指示する電源オン時リセット信号との排他制御を行うリセット制御器を有する請求項4に記載のUSB下位ユニット。

【請求項7】

前記遅延回路は、駆動電源不要なRC回路によって構成されている請求項5に記載のUSB下位ユニット。

【請求項8】

前記遅延回路は、VBUS電源を駆動電源とするリセットICによって構成されている請求項5に記載のUSB下位ユニット。

【請求項9】

前記USB下位ユニットは、プリンタである請求項1乃至8のいずれか一項に記載のUSB下位ユニット。

【請求項10】

請求項1乃至9のいずれか1つに記載のUSB下位ユニットと、前記USB上位ユニットとを有することを特徴とするUSBシステム。

【請求項1】

USBインターフェースを介してUSB上位ユニットと接続されるセルフパワード方式のUSB下位ユニットであって、USB上位ユニットから供給されるVBUS電源のオフ時間長に基づいてUSB下位ユニットの一時的記憶内容のリセットまたはセルフパワー電源のオフを行うリセット/オフ制御部を有するUSB下位ユニットにおいて、

USB上位ユニットから供給されるVBUS電源のオフからオンへの立ち上がりに基づいてセルフパワー電源のレジュームを行うレジューム制御部と、前記USB下位ユニット全体の動作を制御するユニットCPUとを有し、

前記レジューム制御部は、

VBUS電源を駆動電源としてセルフパワー電源をオフからオンに切り替えるスイッチ手段と、

前記スイッチ手段によるセルフパワー電源のオフとオンを操作するセルフパワー電源制御器とを備え、

前記セルフパワー電源制御器は、VBUS電源を駆動電源として、前記リセット/オフ制御部から出力されるセルフパワー電源のオフを指示する電源オフ指示信号と、VBUS電源のオフからオンへの立ち上がりとの排他制御で前記スイッチ手段を操作し、

前記リセット/オフ制御部は、

PLDやICの組み合わせによって構成されたコントロールロジックと、

VBUS電源のオフ時間長を計測し、所定の時間でタイムアップするタイマとを備え、

前記コントロールロジックは、VBUS電源のオン/オフを検出し、前記タイマが所定の時間でタイムアップする前にVBUS電源がオンするか否かに応じて、前記リセットを行うVBUSリセット信号または前記電源オフ指示信号を出力することを特徴とするUSB下位ユニット。

【請求項2】

前記コントロールロジックは、

VBUS電源の立ち下がりを検出して前記タイマに計時開始の信号を出力し、

前記タイマが所定の時間でタイムアップする前にVBUS電源がオンすると、前記タイマに計時停止の信号を出力して前記リセット信号を出力し、

前記タイマが所定の時間でタイムアップしてタイムアップ信号を受け取ると、前記電源オフ指示信号を出力する請求項1に記載のUSB下位ユニット。

【請求項3】

前記スイッチ手段は、FETによって構成されている請求項1または2に記載のUSB下位ユニット。

【請求項4】

VBUS電源のオフからオンへの立ち上がりによってセルフパワー電源がオンされたことに基づいてUSB下位ユニットの一時的記憶内容の電源オン時リセットを行うリセットICを有する請求項1乃至3のいずれか1つに記載のUSB下位ユニット。

【請求項5】

前記レジューム制御部は、VBUS電源を駆動電源とするか、または、駆動電源不要で、VBUS電源の立ち上がりを遅延させて前記スイッチ手段に送出する遅延回路をさらに備えている請求項1に記載のUSB下位ユニット。

【請求項6】

前記リセット/オフ制御部から出力されるリセットを指示するリセット信号と、前記リセットICから出力される電源オン時リセットを指示する電源オン時リセット信号との排他制御を行うリセット制御器を有する請求項4に記載のUSB下位ユニット。

【請求項7】

前記遅延回路は、駆動電源不要なRC回路によって構成されている請求項5に記載のUSB下位ユニット。

【請求項8】

前記遅延回路は、VBUS電源を駆動電源とするリセットICによって構成されている請求項5に記載のUSB下位ユニット。

【請求項9】

前記USB下位ユニットは、プリンタである請求項1乃至8のいずれか一項に記載のUSB下位ユニット。

【請求項10】

請求項1乃至9のいずれか1つに記載のUSB下位ユニットと、前記USB上位ユニットとを有することを特徴とするUSBシステム。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2011−233177(P2011−233177A)

【公開日】平成23年11月17日(2011.11.17)

【国際特許分類】

【出願番号】特願2011−183720(P2011−183720)

【出願日】平成23年8月25日(2011.8.25)

【分割の表示】特願2008−249532(P2008−249532)の分割

【原出願日】平成20年9月29日(2008.9.29)

【出願人】(000227205)NECインフロンティア株式会社 (1,047)

【Fターム(参考)】

【公開日】平成23年11月17日(2011.11.17)

【国際特許分類】

【出願日】平成23年8月25日(2011.8.25)

【分割の表示】特願2008−249532(P2008−249532)の分割

【原出願日】平成20年9月29日(2008.9.29)

【出願人】(000227205)NECインフロンティア株式会社 (1,047)

【Fターム(参考)】

[ Back to top ]