VLIWプロセッサと命令構造と命令実行方法

【課題】VLIWプロセッサにおいて、小さな回路規模で複雑な条件判定処理を効率良く実行する。

【解決手段】第1の演算器130は、第1の制御信号ctr1に応じて、第1の比較演算器122の出力、該出力とレジスタ50が既に保持している値の論理積、論理和のうちの1つを第1の演算結果CR1として出力する。第2の演算器140は、第2の制御信号ctr2に応じて、第2の比較演算器124の出力と、該出力とレジスタ50が既に保持している値の論理積、論理和の3つのうちの1つを第2の演算結果CR2として出力する。第3の演算器150は、第3の制御信号ctr3に応じて、第1の演算結果CR1、第1の演算結果CR1と第2の演算結果CR2の論理積、論理和のうちの1つを実行結果としてレジスタ50に出力する。レジスタ50は、第3の演算器150からの実行結果を新たに保持し、出力する。

【解決手段】第1の演算器130は、第1の制御信号ctr1に応じて、第1の比較演算器122の出力、該出力とレジスタ50が既に保持している値の論理積、論理和のうちの1つを第1の演算結果CR1として出力する。第2の演算器140は、第2の制御信号ctr2に応じて、第2の比較演算器124の出力と、該出力とレジスタ50が既に保持している値の論理積、論理和の3つのうちの1つを第2の演算結果CR2として出力する。第3の演算器150は、第3の制御信号ctr3に応じて、第1の演算結果CR1、第1の演算結果CR1と第2の演算結果CR2の論理積、論理和のうちの1つを実行結果としてレジスタ50に出力する。レジスタ50は、第3の演算器150からの実行結果を新たに保持し、出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数の比較命令を含むVLIW命令、及び該VLIW命令を実行する技術に関する。

【背景技術】

【0002】

1サイクルで複数の命令を実行することができることから、VLIW(Very Long Instruction Word)命令を利用するプロセッサ(VLIWプロセッサ)が様々な分野で用いられている。

【0003】

例えば、画像処理の際に、エッジ検出など、隣接画素間で画素値の比較を行って注目画素の画素値を決定する処理では、複雑な条件判定が必要である。式(1)は、エッジ検出フィルタの処理例を示す。

res=(val>c && (val>b || val==b && (sc==0 || sc==2)))?1:0; (1)

【0004】

式(1)における「?」の前において、各英字は引数を示し、数字

は即値を示す。また、「&&」、「||」は、「論理積」と「論理和」を夫々示す。また、各等号と不等号は、比較処理を示す。また、式(1)の右辺において、「?」前の部分をXとすれば、式(1)は、Xが真であれば、resの値を1とし、Xが偽であれば、resの値を0とする処理を示す。

【0005】

図18は、分岐命令を利用して、式(1)に示す処理をVLIWプロセッサへ実装する際のプログラム例を示す。

【0006】

また、例えば、分岐命令を利用して、図19のプログラムが示すように、下記の式(2)に示す処理をVLIWプロセッサに実装することもできる。

res=((d01==0)&&(d11!=0))&&(((d02!=0)&&(d12==0))||((d00!=0)&&(d10==0))) (2)

【0007】

例えば、図18のプログラムにおける2行目〜5行目、図19のプログラムにおける2行目〜5行目に示すように、1つの分岐命令(brf)と1つの比較命令(cmp)が並列に実行される。そのため、1サイクルで1命令しか実行できないプロセッサより処理効率を高めることができる。

【0008】

しかしながら、一般的に、分岐命令は、時間がかかるという問題がある。例えば、分岐ペナルティが2であるとした場合、図18に示すプログラムの実行に9サイクルがかかり、図19に示すプログラムの実行に12サイクルがかかってしまう。

【0009】

VLIWプロセッサに関して、様々な視点からの技術が提案されている。

例えば、特許文献1には、プレディケイトレジスタを用いることにより条件分岐を取り除く手法が開示されている。

【0010】

この手法を適用したVLIWプロセッサは、1つのVLIW命令に含まれる複数の演算命令フィールドの1つ以上の演算命令フィールドに対応して設けられた複数の演算器を有する。各演算器は、対応する1つ以上の演算命令フィールドが示す演算を行う演算回路と、該演算回路の演算を実行するか否かを決定する値を格納するレジスタ(プレディケイトレジスタ)と、予め定められた命令について、その命令の演算結果を評価した値を全ての演算器内の上記レジスタに書き込む格納手段を備える。各演算器内の演算回路は、上記プレディケイトレジスタを指定された演算命令について、当該プレディケイトレジスタに書き込まれた値に応じて当該演算命令を実行するか否かを決定する。

【0011】

また、特許文献2には、VLIWプロセッサに汎用的な積和回路を並列に設け、1サイクルで複雑な条件判定(複合テスト)を行い条件分岐する手法が開示されている。

【0012】

また、特許文献3には、複数サイクルに分けて演算した複数の条件コードを単一の条件コードセットにまとめる手法が開示されている。

【0013】

また、特許文献4には、現在の比較命令と前のサイクルの比較命令から生成される状態情報のブール組合せの結果を求める手法が開示されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開平10−27102号公報

【特許文献2】特開平7−302199号公報

【特許文献3】特開2008−146544号公報

【特許文献4】特表2003−520360号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

特許文献1による手法は、プレディケイトレジスタを条件分岐の代わりに利用したものであり、演算器間のレジスタファイルの転送の回数を減らすためには有用であるが、式(1)と式(2)に示すような、階層の構成が複雑な条件判定文の場合には、効率向上の効果が限定されている。

【0016】

特許文献2による手法は、積和標準形で表すことができるあらゆる条件の組合せを1サイクルで評価できるようにするものであり、画像処理など、条件の組合せがある程度限定されていてもよい場合にはハードウェアが必要以上に肥大化する問題がある。

【0017】

特許文献3に開示された手法は、複数ビットから成る条件コードセットにより複数の分岐先への分岐を効率的に実現することができるが、例えば、式(1)に示すエッジ検出フィルタのような、分岐先が1つしかない場合には非効率的である。

【0018】

特許文献4に開示された手法は、現在の比較命令と前のサイクルの比較命令から生成される状態情報のブール組合せの結果を求めることができる。しかし、例えば、式(1)と式(2)に示すような処理は、複数の比較命令の結果の組合せ(例えば論理演算)をする必要があり、特許文献4の手法による効率化が困難である。

【0019】

1サイクルに複数の命令を実行可能であるVLIWプロセッサの特性を生かし、小さな回路規模で、式(1)と式(2)が示すような、複雑な条件判定処理を効率良く実行できる技術が望まれている。

【課題を解決するための手段】

【0020】

本発明の1つの態様は、VLIWプロセッサである。該VLIWプロセッサは、第1の比較演算器、第2の比較演算器、第1の演算器、第2の演算器、第3の演算器、レジスタを備える。

【0021】

第1の比較演算器は、第1の比較演算信号と第1の入力信号と第2の入力信号とが入力され、該第1の入力信号と該第2の入力信号に対して第1の比較演算信号が示す比較を行い、該比較の結果を出力する。

【0022】

第2の比較演算器は、第2の比較演算信号と第3の入力信号と第4の入力信号とが入力され、該第3の入力信号と該第4の入力信号に対して第2の比較演算信号が示す比較を行い、該比較の結果を出力する。

【0023】

第1の演算器は、第1の制御信号と、第1の比較演算器による比較の結果と、レジスタが既に保持している値とが入力され、第1の制御信号に応じて、第1の比較演算器による比較の結果と、該比較の結果とレジスタの値の論理積と、該比較の結果とレジスタの値の論理和とのいずれか1つを第1の演算結果として出力する。

【0024】

第2の演算器は、第2の制御信号と、第2の比較演算器による比較の結果と、レジスタが既に保持している値とが入力され、第2の制御信号に応じて、第2の比較演算器による比較の結果と、該比較の結果とレジスタの値の論理積と、該比較の結果とレジスタの値の論理和とのいずれか1つを第2の演算結果として出力する。

【0025】

第3の演算器は、第3の制御信号と、第1の演算結果と、第2の演算結果とが入力され、第3の制御信号に応じて、第1の演算結果と、第1の演算結果と第2の演算結果の論理積と、第1の演算結果と第2の演算結果の論理和とのいずれか1つを実行結果としてレジスタに出力する。

レジスタは、第3の演算器からの実行結果を新たに保持し、出力する。

【0026】

本発明の別の態様は、VLIW命令の命令構造である。この命令構造は、第1の比較命令を格納する第1の比較命令フィールドと、第1の合成指定を格納する第1の合成指定フィールドと、第2の比較命令を格納する第2の比較命令フィールドと、第2の合成指定を格納する第2の合成指定フィールドと、第3の合成指定を格納する第3の合成指定フィールドを含む。

【0027】

第1の合成指定は、第1の比較命令が示す比較の結果と、該比較の結果と1つ前のVLIW命令の実行結果の論理積と、該比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第1の演算結果とするかを示すものである。

【0028】

第2の合成指定は、第2の比較命令が示す比較の結果と、該比較の結果と1つ前のVLIW命令の実行結果の論理積と、該比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第2の演算結果とするかを示すものである。

【0029】

第3の合成指定は、第1の演算結果と、第1の演算結果と第2の演算結果の論理積と、第1の演算結果と第2の演算結果の論理和とのいずれを今回のVLIW命令の実行結果とするかを示すものである。

【0030】

本発明のさらなる別の態様は、第1の比較命令と、第2の比較命令と、「合成しない」、「論理積」、「論理和」のいずれか1つを示す第1と第2の合成指定と、「論理積」と「論理和」のいずれかを示す第3の合成指定とを含むVLIW命令が入力され、レジスタを備えるVLIWプロセッサにおけるVLIW命令の実行方法である。

【0031】

該実行方法は、第1の合成指定が「合成しない」を示す場合には、第1の比較命令が示す比較の結果を第1の演算結果として出力し、他の場合には、第1の合成指定が示す論理演算を、第1の比較命令が示す比較の結果とレジスタが既に保持している値とに対して行って得た値を第1の演算結果として出力する。

【0032】

また、第2の合成指定が「合成しない」を示す場合には、第2の比較命令が示す比較の結果を第2の演算結果として出力し、他の場合には、第2の合成指定が示す論理演算を、第2の比較命令が示す比較の結果とレジスタが既に保持している値とに対して行って得た値を第2の演算結果として出力する。

【0033】

さらに、第3の合成指定が示す論理演算を、第1の演算結果と第2の演算結果に対して行って得た値を今回のVLIW命令の実行結果としてレジスタに出力する。レジスタにより、該実行結果を新たに保持し、出力する。

【0034】

なお、上記態様のVLIWプロセッサを装置やシステムに置換えて表現したものや、上記態様の命令構造を有するVLIW命令や、該VLIW命令を含むプログラムや、該VLIW命令及び上記態様の方法を実行するVLIWプロセッサなども、本発明の態様としては有効である。

【発明の効果】

【0035】

本発明にかかる技術によれば、VLIWプロセッサにおいて、小さな回路規模で複雑な条件判定処理を効率良く実行することができる。

【図面の簡単な説明】

【0036】

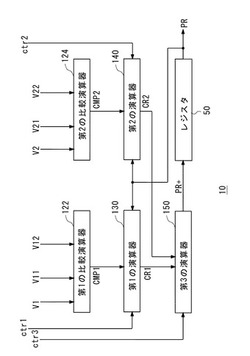

【図1】本発明にかかる技術の原理を説明するためのVLIWプロセッサを示す図である。

【図2】図1に示すVLIWプロセッサが対応するVLIW命令の構造を示す図である。

【図3】図2に示すVLIW命令における比較命令に含まれる比較演算子の例を示す図である。

【図4】図2に示すVLIW命令と図1に示すVLIWプロセッサにおける各信号との対応関係を示す図である(その1)。

【図5】図2に示すVLIW命令と図1に示すVLIWプロセッサにおける各信号との対応関係を示す図である(その2)。

【図6】本発明の実施の形態にかかるVLIWプロセッサを示す図である。

【図7】図6に示すVLIWプロセッサにおける第1の演算器を示す図である。

【図8】図6に示すVLIWプロセッサにおける第2の比較演算器を示す図である。

【図9】図6に示すVLIWプロセッサにおける第3の演算器を示す図である。

【図10】パターンAの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図11】パターンBの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図12】パターンCの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図13】パターンDの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図14】式(1)に示す処理を図6に示すVLIWプロセッサへ実装する際の分割例を示す図である。

【図15】式(1)に示す処理を図6に示すVLIWプロセッサへ実装する際のプログラム例を示す図である。

【図16】式(2)に示す処理を図6に示すVLIWプロセッサへ実装する際の分割例を示す図である。

【図17】式(1)に示す処理を図6に示すVLIWプロセッサへ実装する際のプログラム例を示す図である。

【図18】式(1)に示す処理を従来のVLIWプロセッサへの実装例を示す図である。

【図19】式(2)に示す処理を従来のVLIWプロセッサへの実装例を示す図である。

【発明を実施するための形態】

【0037】

以下、図面を参照して本発明の実施の形態について説明する。説明の明確化のため、以下の記載及び図面は、適宜、省略、及び簡略化がなされている。なお、各図面において、同一の要素には同一の符号が付されており、必要に応じて重複説明は省略されている。

【0038】

本発明の具体的な実施の形態を説明する前に、まず、図1〜図5を参照して本発明にかかる技術の原理を説明する。

【0039】

図1に示すVLIWプロセッサ10は、第1の比較演算器122、第2の比較演算器124、第1の演算器130、第2の演算器140、第3の演算器150、レジスタ50を備える。第1の比較演算器122と第2の比較演算器124は、通常のプロセッサに備えられた、算術演算のための加減算器やALU(Arithmetic Logic Unit)であってもよい。

【0040】

第1の比較演算器122は、第1の比較演算信号V1、第1の入力信号V11、第2の入力信号V12が入力され、第1の入力信号V11と第2の入力信号V12に対して第1の比較演算信号V1が示す比較を行い、該比較の結果を出力する。第1の比較演算器122による比較の結果を、第1の比較結果CMP1という。

【0041】

第2の比較演算器124は、第2の比較演算信号V2、第3の入力信号V21、第4の入力信号V22が入力され、第3の入力信号V21と第4の入力信号V22に対して第2の比較演算信号V2が示す比較を行い、該比較の結果を出力する。第2の比較演算器124による比較の結果を、第2の比較結果CMP2という。

【0042】

第1の演算器130は、第1の制御信号ctr1と、第1の比較結果CMP1と、レジスタ50が既に保持している値(PR)とが入力され、第1の制御信号ctr1に応じて、第1の比較結果CMP1、第1の比較結果CMP1とレジスタ50の値PRの論理積と、第1の比較結果CMP1とレジスタの値PRの論理和とのいずれか1つを第1の演算結果CR1として出力する。

【0043】

第2の演算器140は、第2の制御信号ctr2と、第2の比較結果CMP2と、レジスタ50の値PRとが入力され、第2の制御信号ctr2に応じて、第2の比較結果CMP2、第2の比較結果CMP2とレジスタ50の値PRの論理積と、第2の比較結果CMP2とレジスタの値PRの論理和とのいずれか1つを第2の演算結果CR2として出力する。

【0044】

第3の演算器150は、第3の制御信号ctr3と、第1の演算結果CR1と、第2の演算結果CR2とが入力され、第3の制御信号ctr3に応じて、第1の演算結果CR1と、第1の演算結果CR1と第2の演算結果CR2の論理積と、第1の演算結果CR1と第2の演算結果CR2の論理和とのいずれか1つを実行結果(PR+)としてレジスタ50に出力する。

【0045】

レジスタ50は、第3の演算器150からの実行結果PR+を新たに保持し、必要に応じて出力する。レジスタ50に保持していた値PRは、この実行結果PR+により上書される。

【0046】

VLIWプロセッサ10は、図2に示す構造のVLIW命令を実行することができる。ここで、図2〜図3を参照して、VLIWプロセッサ10が実行するVLIW命令の構造を説明する。

【0047】

図2に示すように、該VLIW命令は、第1の比較命令COMPARE1を格納する第1比較命令フィールド、該第1の比較命令COMPARE1に対応する第1の合成指定CMB1を格納する第1の合成指定フィールド、第2の比較命令COMPARE2を格納する第2の比較命令フィールド、該第2の比較命令COMPARE2に対応する第2の合成指定CMB2を格納する第2の合成指定フィールド、第3の合成指定CMB3を格納する第3の合成指定フィールド含む。

【0048】

第1の比較命令COMPARE1と第2の比較命令COMPARE2は、通常の比較命令であり、2つの入力オペランドと1つの比較演算子opにより構成される。2つの入力オペランドは、該1つの比較演算子opが示す比較演算の比較対象に該当する。

【0049】

図3は、第1の比較命令COMPARE1と第2の比較命令COMPARE2に含まれる比較演算子opの例を示す。図示のように、比較演算子opは、「LT」、「LE」、「EQ」、「NE」、「GT」、「GE」などがあり、夫々「Little Than」、「Little Than or Equal To」、「Equal To」、「Not Equal To」、「Greater Than」、「Greater Than or Equal To」を意味する。

【0050】

第1の比較命令COMPARE1による比較の結果は、図1に示すVLIWプロセッサ10における第1の比較結果CMP1に対応し、第2の比較命令COMPARE2による比較の結果は、図1に示すVLIWプロセッサ10における第2の比較結果CMP2に対応する。また、第1の比較命令COMPARE1と第1の合成指定CMB1により決まる演算結果は、VLIWプロセッサ10における第1の演算結果CR1に対応し、第2の比較命令COMPARE2と第2の合成指定CMB2により決まる演算結果は、VLIWプロセッサ10における第2の演算結果CR2に対応する。今回のVLIW命令の実行結果は、VLIWプロセッサ10における実行結果PR+に対応し、1つ前のVLIW命令の実行結果は、VLIWプロセッサ10における実行結果PRに対応する。これに関して、後に図4と図5を参照して詳細に説明する。

【0051】

第1の合成指定CMB1は、第1の比較命令COMPARE1が示す比較の結果(第1の比較結果CMP1)と、該第1の比較結果CMP1と実行結果PRの論理積と、該第1の比較結果CMP1と実行結果PRの論理和とのいずれを演算結果(第1の演算結果CR1)とするかを示す。

【0052】

第2の合成指定CMB2は、第2の比較命令COMPARE2が示す比較の結果(第2の比較結果CMP2)と、該第2の比較結果CMP2と実行結果PRの論理積と、該第2の比較結果CMP2と実行結果PRの論理和とのいずれを演算結果(第2の演算結果CR2)とするかを示す。

【0053】

第3の合成指定CMB3は、第1の演算結果CR1と第2の演算結果CR2の論理積と、第1の演算結果CR1と第2の演算結果CR2の論理和とのいずれを今回のVLIW命令の実行結果(実行結果PR+)とするかを示す。

【0054】

図4と図5は、図2に示すVLIW命令の各構成要素の具体例と、VLIWプロセッサ10が夫々の具体例のVLIW命令を実行する際における各信号との対応関係を示す。図4は、VLIW命令に関して、第3の合成指定CMB3を除いた部分を示し、VLIWプロセッサ10に関しては、第1の制御信号ctr1と第2の制御信号ctr2を示す。図5は、LIW命令とVLIWプロセッサ10に、第3の合成指定CMB3と第3の制御信号ctr3を示す。

【0055】

第1の比較命令COMPARE1は、前述したように、通常の比較命令と同様に、1つの比較演算子と2つの入力オペランドから構成される。VLIWプロセッサ10において、第1の比較命令COMPARE1に含まれる比較演算子が示す比較演算を指示する信号は、第1の比較演算信号V1として第1の比較演算器122に入力される。また、第1の比較命令COMPARE1に含まれる2つのオペランドは、第1の入力信号V11と第2の入力信号V12として、第1の比較演算器122に入力される。

【0056】

第1の合成指定CMB1は、「合成しない」、「論理積(AND)」、「論理和(OR)」のいずれかを示す。「合成しない」は、第1の比較結果CMP1を第1の演算結果CR1とすることを示す。なお、「合成をしない」を示す第1の合成指定CMB1は、「合成をしない」を示すことができれば、如何なる文字であってもよく、図4の例では、空である第1の合成指定CMB1により、「合成しない」を示す。

【0057】

第1の合成指定CMB1が「合成しない」を示すときに、VLIWプロセッサ10において、第1の比較結果CMP1を第1の演算結果CR1として出力するよう指示第1の制御信号ctr1が第1の演算器130に入力される。

【0058】

第1の合成指定CMB1が「合成しない」以外、すなわち論理積と論理和のいずれかの論理演算を示すときに、VLIWプロセッサ10において、第1の比較結果CMP1と前回の実行結果PRに対して、第1の合成指定CMB1が示す論理演算を行って得た結果を第1の演算結果CR1として出力するよう指示する第1の制御信号ctr1が第1の演算器130に入力される。

【0059】

第2の比較命令COMPARE2も、前述したように、通常の比較命令と同様に、1つの比較演算子と2つの入力オペランドから構成される。VLIWプロセッサ10において、第2の比較命令COMPARE2に含まれる比較演算子が示す比較演算を指示する信号は、第2の比較演算信号V2として第2の比較演算器124に入力される。また、第2の比較命令COMPARE2に含まれる2つのオペランドは、第3の入力信号V21と第4の入力信号V22として、第2の比較演算器124に入力される。

【0060】

第2の合成指定CMB2は、第1の合成指定CMB1と同様に、「合成しない」、「論理積(AND)」、「論理和(OR)」のいずれかを示す。「合成しない」は、第2の比較結果CMP2を第2の演算結果CR2とすることを示す。なお、「合成をしない」を示す第2の合成指定CMB2も、「合成をしない」を示すことができれば、如何なる文字であってもよく、図4の例では、空である第2の合成指定CMB2により、「合成しない」を示す。

【0061】

第2の合成指定CMB2が「合成しない」を示すときに、VLIWプロセッサ10において、第2の比較結果CMP2を第2の演算結果CR2として出力するよう指示第2の制御信号ctr2が第2の演算器140に入力される。

【0062】

第2の合成指定CMB2が「合成しない」以外、すなわち論理積と論理和のいずれかの論理演算を示すときに、VLIWプロセッサ10において、第2の比較結果CMP2と前回の実行結果PRに対して、第2の合成指定CMB2が示す論理演算を行って得た結果を第2の演算結果CR2として出力するよう指示する第2の制御信号ctr2が第2の演算器140に入力される。

【0063】

第3の合成指定CMB3は、「論理積(AND)」、「論理和(OR)」のいずれかの論理演算を示す。VLIWプロセッサ10において、第1の演算結果CR1と第2の演算結果CR2に対して、第3の合成指定CMB3が示す論理演算の結果を実行結果PR+として出力するように指示する第3の制御信号ctr3が第3の演算器150に入力される。

【0064】

なお、第2の比較命令フィールドと、第3の合成指定フィールドは、空である場合もある。図5に示すように、COMPARE命令が1つしかないとき、すなわち第2に比較命令フィールドが空であるときに、第3の合成指定CMB3が参照されず、第1の演算結果CR1を今回の命令の実行結果PR+として出力するよう指示する第3の制御信号ctr3が第3の演算器150に入力される。また、第3の合成指定CMB3が無いときにも同様に、第1の演算結果CR1を今回の命令の実行結果PR+として出力するよう指示する第3の制御信号ctr3が第3の演算器150に入力される。この2つの場合において、第2の比較演算器124、第2の演算器140による演算がなされない。

【0065】

図2に示すVLIW命令に対応するVLIWプロセッサ10によれば、小さな回路規模で、複数の比較処理が含まれる条件判定処理を効率良く行うことができる。これに関して、以下の実施の形態を用いて詳細に説明する。

【0066】

図6は、本発明の実施の形態にかかるVLIWプロセッサ100を示す。重複を避けるため、図6において、図1に示す構成要素(信号を含む)と同様のものについて同様の符号を付与しており、これらの構成要素に関しては、必要があるときにのみ説明する。

【0067】

VLIWプロセッサ100は、制御部110、第1の比較演算器122、第2の比較演算器124、第1の演算器130、第2の演算器140、第3の演算器150、プレディケイトレジスタ160を備える。

【0068】

制御部110は、入力されたVLIW命令を格納する命令レジスタ(図示せず)を有し、該命令レジスタに格納されたVLIW命令に基づいて、第1の比較演算信号V1、第1の入力信号V11、第2の入力信号V12、第2の比較演算信号V2、第3の入力信号V21、第4の入力信号V22、第1の制御信号ctr1、第2の制御信号ctr2、第3の制御信号ctr3を出力する。

【0069】

具体的には、制御部110は、第1の比較命令COMPARE1に含まれる比較演算子と2つのオペランドを夫々示す第1の比較演算信号V1、第1の入力信号V11、第2の入力信号V12を第1の比較演算器122に出力する。

【0070】

また、制御部110は、第2の比較命令COMPARE2に含まれる比較演算子と2つのオペランドを夫々示す第2の比較演算信号V2、第3の入力信号V21、第4の入力信号V22を第2の比較演算器124に出力する。

【0071】

また、制御部110は、第1の合成指定CMB1に応じた第1の制御信号ctr1、第2の合成指定CMB2に応じた第2の制御信号ctr2、第3の合成指定CMB3に応じた第3の制御信号ctr3を、第1の演算器130、第2の演算器140、第3の演算器150に夫々出力する。なお、第2の比較命令COMPARE2及び第2の合成指定CMB2が空であるときと、第3の合成指定CMB3が空であるときのいずれか一方に該当する場合には、制御部110は、第3の合成指定CMB3を「合成しない」であると理解してその旨を示す第3の制御信号ctr3信号を第3の演算器150に出力する。

【0072】

第1の比較演算器122は、比較演算を行って第1の比較結果CMP1を第1の演算器130に出力する。第2の比較演算器124は、比較演算を行って第2の比較結果CMP2を第2の演算器140に出力する。

【0073】

図7は、第1の演算器130を示す。第1の演算器130は、ANDゲート132、ORゲート134、セレクタ136を備える。

【0074】

ANDゲート132とORゲート134は、第1の比較演算器122からの第1の比較結果CMP1と、プレディケイトレジスタ160からの実行結果PRが入力され、夫々論理積と論理和をセレクタ136に出力する。

【0075】

セレクタ136には、ANDゲート132からの論理積、ORゲート134からの論理和、第1の比較結果CMP1、制御部110からの第1の制御信号ctr1が入力され、第1の制御信号ctr1に従って、入力された3つの値のうちの1つを選択して第3の演算器150に出力する。セレクタ136の出力は、第1の演算結果CR1となる。

【0076】

具体的には、第1の演算器130は、第1の制御信号ctr1が「合成しない」を示すときに、第1の比較結果CMP1を第1の演算結果CR1として出力する。一方、第1の制御信号ctr1が「論理積」を示すときには、ANDゲート132の出力を第1の演算結果CR1として出力し、第1の制御信号ctr1が「論理和」を示すときには、ORゲート134の出力を第1の演算結果CR1として出力する。

【0077】

図8は、第2の演算器140を示す。第2の演算器140は、ANDゲート142、ORゲート144、セレクタ146を備える。

【0078】

ANDゲート142とORゲート144は、第2の比較演算器124からの第2の比較結果CMP2と、プレディケイトレジスタ160からの実行結果PRが入力され、夫々論理積と論理和をセレクタ146に出力する。

【0079】

セレクタ146には、ANDゲート142からの論理積、ORゲート144からの論理和、第2の比較結果CMP2、制御部110からの第2の制御信号ctr2が入力され、第2の制御信号ctr2に従って、入力された3つの値のうちの1つを選択して第3の演算器150に出力する。セレクタ146の出力は、第2の演算結果CR2となる。

【0080】

具体的には、第2の演算器140は、第2の制御信号ctr2が「合成しない」を示すときに、第2の比較結果CMP2を第2の演算結果CR2として出力する。一方、第2の制御信号ctr2が「論理積」を示すときには、ANDゲート142の出力を第2の演算結果CR2として出力し、第2の制御信号ctr2が「論理和」を示すときには、ORゲート144の出力を第2の演算結果CR2として出力する。

【0081】

図9は、第3の演算器150を示す。第3の演算器150は、ANDゲート152、ORゲート154、セレクタ156を備える。

【0082】

ANDゲート152とORゲート154は、第1の演算器130からの第1の演算結果CR1と第2の演算器140からの第2の演算結果CR2が入力され、夫々論理積と論理和をセレクタ156に出力する。

【0083】

セレクタ156には、ANDゲート152からの論理積、ORゲート154からの論理和、第1の演算結果CR1、制御部110からの第3の制御信号ctr3が入力され、第3の制御信号ctr3に従って、入力された3つの値のうちの1つを選択してプレディケイトレジスタ160に出力する。セレクタ156の出力は、実行結果PR+となる。

【0084】

具体的には、第3の演算器150は、第3の制御信号ctr3が「合成しない」を示すときに、第1の演算結果CR1を実行結果PR+として出力する。一方、第3の制御信号ctr3が「論理積」を示すときには、ANDゲート152の出力を実行結果PR+として出力し、第3の制御信号ctr3が「論理和」を示すときには、ORゲート154の出力を実行結果PR+として出力する。

【0085】

プレディケイトレジスタ160は、第3の演算器150からの最新の実行結果PR+を保持する。すなわち、今回のVLIW命令の実行結果の実行結果PR+は、次のVLIW命令の実行時には、実行結果PRとなる。

【0086】

図10〜図13を参照して、図2に示すVLIW命令における各比較命令と合成指定の組合せのパターン毎に、VLIWプロセッサ100が実行する処理を説明する。

【0087】

<パターンA>

パターンAは、VLIW命令に第1の比較命令COMPARE1と第2の比較命令COMPARE2が共にあると共に、全ての合成指定(CMB1、CMB2、CMB3)が、「論理積」と「論理和」のいずれかを示すパターンである。パターンAは、パターンA(1)〜パターンA(4)の4つが含まれる。

【0088】

図10に示すように、パターンA(1)は、全ての合成指定が「AND」を示すVLIW命令「COMPARE1_AND COMPARE2_AND AND」の場合である。

【0089】

該パターンA(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理積と、実行結果PR(1つ前の実行結果)との論理積である。

【0090】

パターンA(2)は、全ての合成指定が「OR」を示すVLIW命令「COMPARE1_OR COMPARE2_OR OR」の場合である。

【0091】

該パターンA(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理和と、実行結果PRとの論理和である。

【0092】

パターンA(3)は、第1の合成指定CMB1と第2の合成指定CMB2が共に「AND」を示し、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_AND COMPARE2_AND OR」の場合である。

【0093】

該パターンA(3)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理和と、実行結果PRとの論理積である。

【0094】

パターンA(4)は、第1の合成指定CMB1と第2の合成指定CMB2が共に「OR」を示し、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_OR COMPARE2_OR AND」の場合である。

【0095】

該パターンA(4)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理積と、実行結果PRとの論理和である。

【0096】

すなわち、該パターンAの命令の場合に、VLIWプロセッサ100は、1サイクルで、2つの比較命令の実行と、第1の比較命令が示す比較の結果と実行結果PRとの論理演算と、第2の比較命令が示す比較の結果と実行結果PRとの論理演算と、該2つの論理演算の結果のさらなる論理演算を行うことができる。

【0097】

<パターンB>

パターンBは、VLIW命令に第1の比較命令COMPARE1と第2の比較命令COMPARE2が共にあり、第1の合成指定CMB1と第2の合成指定CMB2のいずれか一方が空であり、第3の合成指定CMB3が「論理積」と「論理和」のいずれかを示すパターンである。パターンBは、パターンB(1)〜パターンB(4)の4つが含まれる。

【0098】

図11に示すように、パターンB(1)は、第1の合成指定CMB1が「AND」を示し、第2の合成指定CMB2が空であり、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_AND COMPARE2_ OR」の場合である。

【0099】

該パターンB(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRとの論理積と、第2の比較結果CMP2との論理和である。

【0100】

パターンB(2)は、第1の合成指定CMB1が空であり、第2の合成指定CMB2が「AND」を示し、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_ COMPARE2_AND OR」の場合である。

【0101】

該パターンB(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第2の比較結果CMP2と実行結果PRの論理積と、第1の比較結果CMP1との論理和である。

【0102】

パターンB(3)は、第1の合成指定CMB1が「OR」であり、第2の合成指定CMB2が空であり、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_OR COMPARE2_ AND」の場合である。

【0103】

該パターンB(3)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRとの論理和と、第2の比較結果CMP2との論理積である。

【0104】

パターンB(4)は、第1の合成指定CMB1が空であり、第2の合成指定CMB2が「OR」を示し、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_ COMPARE2_OR AND」の場合である。

【0105】

該パターンB(4)のときに、VLIWプロセッサ100が得た実行結果PR+は、第2の比較結果CMP2と実行結果PRの論理積と、第1の比較結果CMP1との論理和である。

【0106】

すなわち、該パターンBの命令の場合に、VLIWプロセッサ100は、1サイクルで、2つの比較命令の実行と、片方の比較命令が示す比較の結果と実行結果PRの論理演算と、該論理演算の結果と他方の比較命令の実行結果の更なる論理演算を行うことができる。

【0107】

<パターンC>

パターンCは、VLIW命令に第1の比較命令COMPARE1と第2の比較命令COMPARE2が共にあり、第1の合成指定CMB1と第2の合成指定CMB2のいずれも空であり、第3の合成指定CMB3が「論理積」と「論理和」のいずれかを示すパターンである。パターンCは、パターンC(1)〜パターンC(2)の4つが含まれる。

【0108】

図12に示すように、パターンC(1)は、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_ COMPARE2_ AND」の場合である。

【0109】

該パターンC(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理積である。

【0110】

パターンC(2)は、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_ COMPARE2_ OR」の場合である。

【0111】

該パターンC(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理和である。

【0112】

すなわち、該パターンCの命令の場合に、VLIWプロセッサ100は、1サイクルで、2つの比較命令の実行と、該2つの比較命令が夫々示す比較の結果の論理演算を行うことができる。

【0113】

<パターンD>

上述したパターンA〜Cのいずれの場合においても、VLIW命令に2つの比較命令が含まれる。本パターンDは、1つの比較命令(第1の比較命令COMPARE1)のみを含むVLIW命令の場合である。パターンDは、パターンD(1)〜パターンD(3)の3つが含まれる。

【0114】

図13に示すように、パターンD(1)は、第1の比較命令COMPARE1に対応する第1の合成指定CMB1が「AND」を示すVLIW命令「COMPARE1_AND」の場合である。

【0115】

該パターンD(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRの論理積である。

【0116】

パターンD(2)は、第1の比較命令COMPARE1に対応する第1の合成指定CMB1が「OR」を示すVLIW命令「COMPARE1_OR」の場合である。

【0117】

該パターンD(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRの論理和である。

【0118】

パターンD(3)は、第1の比較命令COMPARE1に対応する第1の合成指定CMB1が空であるVLIW命令「COMPARE1」の場合である。

【0119】

該パターンD(3)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1である。

【0120】

すなわち、該パターンDの命令の場合に、VLIWプロセッサ100は、1サイクルで、1つの比較命令の実行を行うことができる。

【0121】

ここで、VLIWプロセッサ100への実装例を説明する。なお、以下において、プログラムの具体例の中で、分かりやすいように、「論理積」と「論理和」を示す第3の合成指定CMB3を夫々「Fand」と「For」で表わす。また、各プログラムの例において、1ラインは1サイクルの処理を示す。

【0122】

図14に示すように、式(1)が示す処理を、5つの比較演算A1〜A5、4つの論理演算B1〜B4、処理の結果をセットするC1に分割することができる。本実施の形態におけるVLIW命令及びVLIWプロセッサ100によれば、1サイクルにおいて、2つの比較命令の並列実行、夫々の比較命令が示す比較の結果と1つ前の実行結果PR(プログラムの視点からは1ライン前の処理結果)との論理演算、2つの論理演算のさらなる論理演算が可能であるため、式(1)に示す処理を図14に示すように分割し、分岐命令を使用せずにVLIWプロセッサ100へ実装することができる。

【0123】

図15は、式(1)に示す処理をVLIWプロセッサ100へ実装する際のプログラムの例を示す。

【0124】

該プログラムの1ライン目が示す処理は、第1の比較「SC==0」と、第2の比較「SC==2」を並列に行うと共に、2つの比較結果を論理和演算して、該論理和演算の結果をプレディケイトレジスタ160に格納する処理である。なお、2つの「compare」は、第1の比較命令と第2の比較命令であり、第1の合成指定CMB1と第2の合成指定CMB2のいずれも空であり、「合成をしない」を示す。これは、図12に示すパターンC(2)の処理である。

【0125】

2ライン目が示す処理は、第1の比較「val==b」と、第2の比較「val>b」を並列に実行すると共に、第1の比較結果と1ライン目の実行結果(プレディケイトレジスタ160の値)の論理積と、第2の比較結果との論理和を得てプレディケイトレジスタ160に格納する処理である。これは、図11に示すパターンB(1)の処理である。

【0126】

3ライン目が示す処理は、第1の比較(val>c)を実行すると共に、第1の比較結果と2ライン目の実行結果との論理積を得てプレディケイトレジスタ160に格納する処理である。これは、図13に示すパターンD(1)の処理である。

【0127】

4ライン目が示す処理は、プレディケイトレジスタ160の値に応じて引数resに1を格納する命令「mset」を実行する処理である。

【0128】

このように、本実施の形態のVLIWプロセッサ100によれば、式(1)が示す処理を4サイクルで完了することができる。

【0129】

前述したように、式(1)が示す処理を従来のVLIWプロセッサに分岐命令により実装する際に、分岐ペナルティを2サイクルである場合には、9サイクルが必要である(図18)。

【0130】

また、図16は、式(2)が示す処理を分割した態様を示す。図示のように、式(2)が示す処理を、6つの比較演算A1〜A6、5つの論理演算B1〜B5、処理の結果をセットする処理C1に分割することができる。

【0131】

図17は、式(2)が示す処理を図16に示すように分割して、VLIWプロセッサ100へ実装する際のプログラムの例を示す。

【0132】

該プログラムの1ライン目が示す処理は、第1の比較「d02≠0」と、第2の比較「d12==0」を並列に行うと共に、2つの比較結果を論理積演算して、該論理積演算の結果をプレディケイトレジスタ160に格納する処理である。これは、図12に示すパターンC(1)の処理である。

【0133】

2ライン目が示す処理は、第1の比較「d00≠0」と、第2の比較「d10=0」を並列に実行すると共に、第1の比較結果と1ライン目の実行結果の論理和と、第2の比較結果と1ライン目の実行結果の論理和との論理積を得てプレディケイトレジスタ160に格納する処理である。これは、図10に示すパターンA(4)の処理である。

【0134】

3ライン目が示す処理は、第1の比較(d11≠0)と、第2の比較(d01=0)を並列に実行すると共に、第1の比較結果と2ライン目の実行結果の論理積と、第2の比較結果と2ライン目の実行結果の論理積との論理積を得てプレディケイトレジスタ160に格納する処理である。これは、図10に示すパターンA(1)の処理である。

【0135】

4ライン目が示す処理は、プレディケイトレジスタ160の値に応じて引数resに1を格納する命令「mset」を実行する処理である。

【0136】

このように、本実施の形態のVLIWプロセッサ100によれば、式(2)が示す処理を4サイクルで完了することができる。

【0137】

前述したように、式(2)に示す処理を従来のVLIWプロセッサに分岐命令により実行する際に、分岐ペナルティを2サイクルである場合には、12サイクルが必要である(図19)。

【0138】

このように、本実施の形態のVLIWプロセッサ100によれば、複数の比較処理が含まれる条件判定処理を効率良く行うことができる。

【0139】

本願発明者は、画像に対するエッジ検出処理における条件判定処理をVLIWプロセッサ100に実行させた結果、通常のVLIWプロセッサの2倍ほどの速度を得ることを確認した。

【0140】

以上、実施の形態をもとに本発明を説明した。実施の形態は例示であり、本発明の主旨から逸脱しない限り、上述した実施の形態に対してさまざまな変更、増減、組合せを行ってもよい。これらの変更、増減、組合せが行われた変形例も本発明の範囲にあることは当業者に理解されるところである。

【0141】

例えば、VLIWプロセッサ100において、最新の実行結果PR+を保持するレジスタとしてプレディケイトレジスタ160が用いられている。一般的に、プレディケイトレジスタは1ビットであり、汎用レジスタは16ビットまたは32ビットである。VLIWプロセッサ100において、VLIW命令の実行結果が1ビットであるため、プレディケイトレジスタ160を用いることにより、さらに回路規模を抑制することができる。勿論、最新の実行結果PR+を保持するレジスタとして汎用レジスタを用いてもよい。

【0142】

また、例えば、上述したように、1つの比較命令のみを実行する場合には、第3の合成指定CMB3が空であってもよい。この場合、第3の合成指定フィールドを空にせず、他の命令の即値フィールドなどの別の用途に用いてもよい。

【符号の説明】

【0143】

10 VLIWプロセッサ

50 レジスタ

100 VLIWプロセッサ

110 制御部

122 第1の比較演算器

124 第2の比較演算器

130 第1の演算器

132 ANDゲート

134 ORゲート

136 セレクタ

140 第2の演算器

142 ANDゲート

144 ORゲート

146 セレクタ

150 第3の演算器

152 ANDゲート

154 ORゲート

156 セレクタ

160 プレディケイトレジスタ

ctr1 第1の制御信号

ctr2 第2の制御信号

ctr3 第3の制御信号

COMPARE1 第1の比較命令

E2 第2の比較命令

CMB1 第1の合成指定

CMB2 第2の合成指定

CMB3 第3の合成指定

CMP1 第1の比較結果

CMP2 第2の比較結果

CR1 第1の演算結果

CR2 第2の演算結果

PR 前回の実行結果

PR+ 今回の実行結果

V1 第1の比較演算信号

V11 第1の入力信号

V12 第2の入力信号

V2 第2の比較演算信号

V21 第3の入力信号

V22 第4の入力信号

【技術分野】

【0001】

本発明は、複数の比較命令を含むVLIW命令、及び該VLIW命令を実行する技術に関する。

【背景技術】

【0002】

1サイクルで複数の命令を実行することができることから、VLIW(Very Long Instruction Word)命令を利用するプロセッサ(VLIWプロセッサ)が様々な分野で用いられている。

【0003】

例えば、画像処理の際に、エッジ検出など、隣接画素間で画素値の比較を行って注目画素の画素値を決定する処理では、複雑な条件判定が必要である。式(1)は、エッジ検出フィルタの処理例を示す。

res=(val>c && (val>b || val==b && (sc==0 || sc==2)))?1:0; (1)

【0004】

式(1)における「?」の前において、各英字は引数を示し、数字

は即値を示す。また、「&&」、「||」は、「論理積」と「論理和」を夫々示す。また、各等号と不等号は、比較処理を示す。また、式(1)の右辺において、「?」前の部分をXとすれば、式(1)は、Xが真であれば、resの値を1とし、Xが偽であれば、resの値を0とする処理を示す。

【0005】

図18は、分岐命令を利用して、式(1)に示す処理をVLIWプロセッサへ実装する際のプログラム例を示す。

【0006】

また、例えば、分岐命令を利用して、図19のプログラムが示すように、下記の式(2)に示す処理をVLIWプロセッサに実装することもできる。

res=((d01==0)&&(d11!=0))&&(((d02!=0)&&(d12==0))||((d00!=0)&&(d10==0))) (2)

【0007】

例えば、図18のプログラムにおける2行目〜5行目、図19のプログラムにおける2行目〜5行目に示すように、1つの分岐命令(brf)と1つの比較命令(cmp)が並列に実行される。そのため、1サイクルで1命令しか実行できないプロセッサより処理効率を高めることができる。

【0008】

しかしながら、一般的に、分岐命令は、時間がかかるという問題がある。例えば、分岐ペナルティが2であるとした場合、図18に示すプログラムの実行に9サイクルがかかり、図19に示すプログラムの実行に12サイクルがかかってしまう。

【0009】

VLIWプロセッサに関して、様々な視点からの技術が提案されている。

例えば、特許文献1には、プレディケイトレジスタを用いることにより条件分岐を取り除く手法が開示されている。

【0010】

この手法を適用したVLIWプロセッサは、1つのVLIW命令に含まれる複数の演算命令フィールドの1つ以上の演算命令フィールドに対応して設けられた複数の演算器を有する。各演算器は、対応する1つ以上の演算命令フィールドが示す演算を行う演算回路と、該演算回路の演算を実行するか否かを決定する値を格納するレジスタ(プレディケイトレジスタ)と、予め定められた命令について、その命令の演算結果を評価した値を全ての演算器内の上記レジスタに書き込む格納手段を備える。各演算器内の演算回路は、上記プレディケイトレジスタを指定された演算命令について、当該プレディケイトレジスタに書き込まれた値に応じて当該演算命令を実行するか否かを決定する。

【0011】

また、特許文献2には、VLIWプロセッサに汎用的な積和回路を並列に設け、1サイクルで複雑な条件判定(複合テスト)を行い条件分岐する手法が開示されている。

【0012】

また、特許文献3には、複数サイクルに分けて演算した複数の条件コードを単一の条件コードセットにまとめる手法が開示されている。

【0013】

また、特許文献4には、現在の比較命令と前のサイクルの比較命令から生成される状態情報のブール組合せの結果を求める手法が開示されている。

【先行技術文献】

【特許文献】

【0014】

【特許文献1】特開平10−27102号公報

【特許文献2】特開平7−302199号公報

【特許文献3】特開2008−146544号公報

【特許文献4】特表2003−520360号公報

【発明の概要】

【発明が解決しようとする課題】

【0015】

特許文献1による手法は、プレディケイトレジスタを条件分岐の代わりに利用したものであり、演算器間のレジスタファイルの転送の回数を減らすためには有用であるが、式(1)と式(2)に示すような、階層の構成が複雑な条件判定文の場合には、効率向上の効果が限定されている。

【0016】

特許文献2による手法は、積和標準形で表すことができるあらゆる条件の組合せを1サイクルで評価できるようにするものであり、画像処理など、条件の組合せがある程度限定されていてもよい場合にはハードウェアが必要以上に肥大化する問題がある。

【0017】

特許文献3に開示された手法は、複数ビットから成る条件コードセットにより複数の分岐先への分岐を効率的に実現することができるが、例えば、式(1)に示すエッジ検出フィルタのような、分岐先が1つしかない場合には非効率的である。

【0018】

特許文献4に開示された手法は、現在の比較命令と前のサイクルの比較命令から生成される状態情報のブール組合せの結果を求めることができる。しかし、例えば、式(1)と式(2)に示すような処理は、複数の比較命令の結果の組合せ(例えば論理演算)をする必要があり、特許文献4の手法による効率化が困難である。

【0019】

1サイクルに複数の命令を実行可能であるVLIWプロセッサの特性を生かし、小さな回路規模で、式(1)と式(2)が示すような、複雑な条件判定処理を効率良く実行できる技術が望まれている。

【課題を解決するための手段】

【0020】

本発明の1つの態様は、VLIWプロセッサである。該VLIWプロセッサは、第1の比較演算器、第2の比較演算器、第1の演算器、第2の演算器、第3の演算器、レジスタを備える。

【0021】

第1の比較演算器は、第1の比較演算信号と第1の入力信号と第2の入力信号とが入力され、該第1の入力信号と該第2の入力信号に対して第1の比較演算信号が示す比較を行い、該比較の結果を出力する。

【0022】

第2の比較演算器は、第2の比較演算信号と第3の入力信号と第4の入力信号とが入力され、該第3の入力信号と該第4の入力信号に対して第2の比較演算信号が示す比較を行い、該比較の結果を出力する。

【0023】

第1の演算器は、第1の制御信号と、第1の比較演算器による比較の結果と、レジスタが既に保持している値とが入力され、第1の制御信号に応じて、第1の比較演算器による比較の結果と、該比較の結果とレジスタの値の論理積と、該比較の結果とレジスタの値の論理和とのいずれか1つを第1の演算結果として出力する。

【0024】

第2の演算器は、第2の制御信号と、第2の比較演算器による比較の結果と、レジスタが既に保持している値とが入力され、第2の制御信号に応じて、第2の比較演算器による比較の結果と、該比較の結果とレジスタの値の論理積と、該比較の結果とレジスタの値の論理和とのいずれか1つを第2の演算結果として出力する。

【0025】

第3の演算器は、第3の制御信号と、第1の演算結果と、第2の演算結果とが入力され、第3の制御信号に応じて、第1の演算結果と、第1の演算結果と第2の演算結果の論理積と、第1の演算結果と第2の演算結果の論理和とのいずれか1つを実行結果としてレジスタに出力する。

レジスタは、第3の演算器からの実行結果を新たに保持し、出力する。

【0026】

本発明の別の態様は、VLIW命令の命令構造である。この命令構造は、第1の比較命令を格納する第1の比較命令フィールドと、第1の合成指定を格納する第1の合成指定フィールドと、第2の比較命令を格納する第2の比較命令フィールドと、第2の合成指定を格納する第2の合成指定フィールドと、第3の合成指定を格納する第3の合成指定フィールドを含む。

【0027】

第1の合成指定は、第1の比較命令が示す比較の結果と、該比較の結果と1つ前のVLIW命令の実行結果の論理積と、該比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第1の演算結果とするかを示すものである。

【0028】

第2の合成指定は、第2の比較命令が示す比較の結果と、該比較の結果と1つ前のVLIW命令の実行結果の論理積と、該比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第2の演算結果とするかを示すものである。

【0029】

第3の合成指定は、第1の演算結果と、第1の演算結果と第2の演算結果の論理積と、第1の演算結果と第2の演算結果の論理和とのいずれを今回のVLIW命令の実行結果とするかを示すものである。

【0030】

本発明のさらなる別の態様は、第1の比較命令と、第2の比較命令と、「合成しない」、「論理積」、「論理和」のいずれか1つを示す第1と第2の合成指定と、「論理積」と「論理和」のいずれかを示す第3の合成指定とを含むVLIW命令が入力され、レジスタを備えるVLIWプロセッサにおけるVLIW命令の実行方法である。

【0031】

該実行方法は、第1の合成指定が「合成しない」を示す場合には、第1の比較命令が示す比較の結果を第1の演算結果として出力し、他の場合には、第1の合成指定が示す論理演算を、第1の比較命令が示す比較の結果とレジスタが既に保持している値とに対して行って得た値を第1の演算結果として出力する。

【0032】

また、第2の合成指定が「合成しない」を示す場合には、第2の比較命令が示す比較の結果を第2の演算結果として出力し、他の場合には、第2の合成指定が示す論理演算を、第2の比較命令が示す比較の結果とレジスタが既に保持している値とに対して行って得た値を第2の演算結果として出力する。

【0033】

さらに、第3の合成指定が示す論理演算を、第1の演算結果と第2の演算結果に対して行って得た値を今回のVLIW命令の実行結果としてレジスタに出力する。レジスタにより、該実行結果を新たに保持し、出力する。

【0034】

なお、上記態様のVLIWプロセッサを装置やシステムに置換えて表現したものや、上記態様の命令構造を有するVLIW命令や、該VLIW命令を含むプログラムや、該VLIW命令及び上記態様の方法を実行するVLIWプロセッサなども、本発明の態様としては有効である。

【発明の効果】

【0035】

本発明にかかる技術によれば、VLIWプロセッサにおいて、小さな回路規模で複雑な条件判定処理を効率良く実行することができる。

【図面の簡単な説明】

【0036】

【図1】本発明にかかる技術の原理を説明するためのVLIWプロセッサを示す図である。

【図2】図1に示すVLIWプロセッサが対応するVLIW命令の構造を示す図である。

【図3】図2に示すVLIW命令における比較命令に含まれる比較演算子の例を示す図である。

【図4】図2に示すVLIW命令と図1に示すVLIWプロセッサにおける各信号との対応関係を示す図である(その1)。

【図5】図2に示すVLIW命令と図1に示すVLIWプロセッサにおける各信号との対応関係を示す図である(その2)。

【図6】本発明の実施の形態にかかるVLIWプロセッサを示す図である。

【図7】図6に示すVLIWプロセッサにおける第1の演算器を示す図である。

【図8】図6に示すVLIWプロセッサにおける第2の比較演算器を示す図である。

【図9】図6に示すVLIWプロセッサにおける第3の演算器を示す図である。

【図10】パターンAの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図11】パターンBの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図12】パターンCの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図13】パターンDの命令の場合に図6に示すVLIWプロセッサが実行する処理を説明するための図である。

【図14】式(1)に示す処理を図6に示すVLIWプロセッサへ実装する際の分割例を示す図である。

【図15】式(1)に示す処理を図6に示すVLIWプロセッサへ実装する際のプログラム例を示す図である。

【図16】式(2)に示す処理を図6に示すVLIWプロセッサへ実装する際の分割例を示す図である。

【図17】式(1)に示す処理を図6に示すVLIWプロセッサへ実装する際のプログラム例を示す図である。

【図18】式(1)に示す処理を従来のVLIWプロセッサへの実装例を示す図である。

【図19】式(2)に示す処理を従来のVLIWプロセッサへの実装例を示す図である。

【発明を実施するための形態】

【0037】

以下、図面を参照して本発明の実施の形態について説明する。説明の明確化のため、以下の記載及び図面は、適宜、省略、及び簡略化がなされている。なお、各図面において、同一の要素には同一の符号が付されており、必要に応じて重複説明は省略されている。

【0038】

本発明の具体的な実施の形態を説明する前に、まず、図1〜図5を参照して本発明にかかる技術の原理を説明する。

【0039】

図1に示すVLIWプロセッサ10は、第1の比較演算器122、第2の比較演算器124、第1の演算器130、第2の演算器140、第3の演算器150、レジスタ50を備える。第1の比較演算器122と第2の比較演算器124は、通常のプロセッサに備えられた、算術演算のための加減算器やALU(Arithmetic Logic Unit)であってもよい。

【0040】

第1の比較演算器122は、第1の比較演算信号V1、第1の入力信号V11、第2の入力信号V12が入力され、第1の入力信号V11と第2の入力信号V12に対して第1の比較演算信号V1が示す比較を行い、該比較の結果を出力する。第1の比較演算器122による比較の結果を、第1の比較結果CMP1という。

【0041】

第2の比較演算器124は、第2の比較演算信号V2、第3の入力信号V21、第4の入力信号V22が入力され、第3の入力信号V21と第4の入力信号V22に対して第2の比較演算信号V2が示す比較を行い、該比較の結果を出力する。第2の比較演算器124による比較の結果を、第2の比較結果CMP2という。

【0042】

第1の演算器130は、第1の制御信号ctr1と、第1の比較結果CMP1と、レジスタ50が既に保持している値(PR)とが入力され、第1の制御信号ctr1に応じて、第1の比較結果CMP1、第1の比較結果CMP1とレジスタ50の値PRの論理積と、第1の比較結果CMP1とレジスタの値PRの論理和とのいずれか1つを第1の演算結果CR1として出力する。

【0043】

第2の演算器140は、第2の制御信号ctr2と、第2の比較結果CMP2と、レジスタ50の値PRとが入力され、第2の制御信号ctr2に応じて、第2の比較結果CMP2、第2の比較結果CMP2とレジスタ50の値PRの論理積と、第2の比較結果CMP2とレジスタの値PRの論理和とのいずれか1つを第2の演算結果CR2として出力する。

【0044】

第3の演算器150は、第3の制御信号ctr3と、第1の演算結果CR1と、第2の演算結果CR2とが入力され、第3の制御信号ctr3に応じて、第1の演算結果CR1と、第1の演算結果CR1と第2の演算結果CR2の論理積と、第1の演算結果CR1と第2の演算結果CR2の論理和とのいずれか1つを実行結果(PR+)としてレジスタ50に出力する。

【0045】

レジスタ50は、第3の演算器150からの実行結果PR+を新たに保持し、必要に応じて出力する。レジスタ50に保持していた値PRは、この実行結果PR+により上書される。

【0046】

VLIWプロセッサ10は、図2に示す構造のVLIW命令を実行することができる。ここで、図2〜図3を参照して、VLIWプロセッサ10が実行するVLIW命令の構造を説明する。

【0047】

図2に示すように、該VLIW命令は、第1の比較命令COMPARE1を格納する第1比較命令フィールド、該第1の比較命令COMPARE1に対応する第1の合成指定CMB1を格納する第1の合成指定フィールド、第2の比較命令COMPARE2を格納する第2の比較命令フィールド、該第2の比較命令COMPARE2に対応する第2の合成指定CMB2を格納する第2の合成指定フィールド、第3の合成指定CMB3を格納する第3の合成指定フィールド含む。

【0048】

第1の比較命令COMPARE1と第2の比較命令COMPARE2は、通常の比較命令であり、2つの入力オペランドと1つの比較演算子opにより構成される。2つの入力オペランドは、該1つの比較演算子opが示す比較演算の比較対象に該当する。

【0049】

図3は、第1の比較命令COMPARE1と第2の比較命令COMPARE2に含まれる比較演算子opの例を示す。図示のように、比較演算子opは、「LT」、「LE」、「EQ」、「NE」、「GT」、「GE」などがあり、夫々「Little Than」、「Little Than or Equal To」、「Equal To」、「Not Equal To」、「Greater Than」、「Greater Than or Equal To」を意味する。

【0050】

第1の比較命令COMPARE1による比較の結果は、図1に示すVLIWプロセッサ10における第1の比較結果CMP1に対応し、第2の比較命令COMPARE2による比較の結果は、図1に示すVLIWプロセッサ10における第2の比較結果CMP2に対応する。また、第1の比較命令COMPARE1と第1の合成指定CMB1により決まる演算結果は、VLIWプロセッサ10における第1の演算結果CR1に対応し、第2の比較命令COMPARE2と第2の合成指定CMB2により決まる演算結果は、VLIWプロセッサ10における第2の演算結果CR2に対応する。今回のVLIW命令の実行結果は、VLIWプロセッサ10における実行結果PR+に対応し、1つ前のVLIW命令の実行結果は、VLIWプロセッサ10における実行結果PRに対応する。これに関して、後に図4と図5を参照して詳細に説明する。

【0051】

第1の合成指定CMB1は、第1の比較命令COMPARE1が示す比較の結果(第1の比較結果CMP1)と、該第1の比較結果CMP1と実行結果PRの論理積と、該第1の比較結果CMP1と実行結果PRの論理和とのいずれを演算結果(第1の演算結果CR1)とするかを示す。

【0052】

第2の合成指定CMB2は、第2の比較命令COMPARE2が示す比較の結果(第2の比較結果CMP2)と、該第2の比較結果CMP2と実行結果PRの論理積と、該第2の比較結果CMP2と実行結果PRの論理和とのいずれを演算結果(第2の演算結果CR2)とするかを示す。

【0053】

第3の合成指定CMB3は、第1の演算結果CR1と第2の演算結果CR2の論理積と、第1の演算結果CR1と第2の演算結果CR2の論理和とのいずれを今回のVLIW命令の実行結果(実行結果PR+)とするかを示す。

【0054】

図4と図5は、図2に示すVLIW命令の各構成要素の具体例と、VLIWプロセッサ10が夫々の具体例のVLIW命令を実行する際における各信号との対応関係を示す。図4は、VLIW命令に関して、第3の合成指定CMB3を除いた部分を示し、VLIWプロセッサ10に関しては、第1の制御信号ctr1と第2の制御信号ctr2を示す。図5は、LIW命令とVLIWプロセッサ10に、第3の合成指定CMB3と第3の制御信号ctr3を示す。

【0055】

第1の比較命令COMPARE1は、前述したように、通常の比較命令と同様に、1つの比較演算子と2つの入力オペランドから構成される。VLIWプロセッサ10において、第1の比較命令COMPARE1に含まれる比較演算子が示す比較演算を指示する信号は、第1の比較演算信号V1として第1の比較演算器122に入力される。また、第1の比較命令COMPARE1に含まれる2つのオペランドは、第1の入力信号V11と第2の入力信号V12として、第1の比較演算器122に入力される。

【0056】

第1の合成指定CMB1は、「合成しない」、「論理積(AND)」、「論理和(OR)」のいずれかを示す。「合成しない」は、第1の比較結果CMP1を第1の演算結果CR1とすることを示す。なお、「合成をしない」を示す第1の合成指定CMB1は、「合成をしない」を示すことができれば、如何なる文字であってもよく、図4の例では、空である第1の合成指定CMB1により、「合成しない」を示す。

【0057】

第1の合成指定CMB1が「合成しない」を示すときに、VLIWプロセッサ10において、第1の比較結果CMP1を第1の演算結果CR1として出力するよう指示第1の制御信号ctr1が第1の演算器130に入力される。

【0058】

第1の合成指定CMB1が「合成しない」以外、すなわち論理積と論理和のいずれかの論理演算を示すときに、VLIWプロセッサ10において、第1の比較結果CMP1と前回の実行結果PRに対して、第1の合成指定CMB1が示す論理演算を行って得た結果を第1の演算結果CR1として出力するよう指示する第1の制御信号ctr1が第1の演算器130に入力される。

【0059】

第2の比較命令COMPARE2も、前述したように、通常の比較命令と同様に、1つの比較演算子と2つの入力オペランドから構成される。VLIWプロセッサ10において、第2の比較命令COMPARE2に含まれる比較演算子が示す比較演算を指示する信号は、第2の比較演算信号V2として第2の比較演算器124に入力される。また、第2の比較命令COMPARE2に含まれる2つのオペランドは、第3の入力信号V21と第4の入力信号V22として、第2の比較演算器124に入力される。

【0060】

第2の合成指定CMB2は、第1の合成指定CMB1と同様に、「合成しない」、「論理積(AND)」、「論理和(OR)」のいずれかを示す。「合成しない」は、第2の比較結果CMP2を第2の演算結果CR2とすることを示す。なお、「合成をしない」を示す第2の合成指定CMB2も、「合成をしない」を示すことができれば、如何なる文字であってもよく、図4の例では、空である第2の合成指定CMB2により、「合成しない」を示す。

【0061】

第2の合成指定CMB2が「合成しない」を示すときに、VLIWプロセッサ10において、第2の比較結果CMP2を第2の演算結果CR2として出力するよう指示第2の制御信号ctr2が第2の演算器140に入力される。

【0062】

第2の合成指定CMB2が「合成しない」以外、すなわち論理積と論理和のいずれかの論理演算を示すときに、VLIWプロセッサ10において、第2の比較結果CMP2と前回の実行結果PRに対して、第2の合成指定CMB2が示す論理演算を行って得た結果を第2の演算結果CR2として出力するよう指示する第2の制御信号ctr2が第2の演算器140に入力される。

【0063】

第3の合成指定CMB3は、「論理積(AND)」、「論理和(OR)」のいずれかの論理演算を示す。VLIWプロセッサ10において、第1の演算結果CR1と第2の演算結果CR2に対して、第3の合成指定CMB3が示す論理演算の結果を実行結果PR+として出力するように指示する第3の制御信号ctr3が第3の演算器150に入力される。

【0064】

なお、第2の比較命令フィールドと、第3の合成指定フィールドは、空である場合もある。図5に示すように、COMPARE命令が1つしかないとき、すなわち第2に比較命令フィールドが空であるときに、第3の合成指定CMB3が参照されず、第1の演算結果CR1を今回の命令の実行結果PR+として出力するよう指示する第3の制御信号ctr3が第3の演算器150に入力される。また、第3の合成指定CMB3が無いときにも同様に、第1の演算結果CR1を今回の命令の実行結果PR+として出力するよう指示する第3の制御信号ctr3が第3の演算器150に入力される。この2つの場合において、第2の比較演算器124、第2の演算器140による演算がなされない。

【0065】

図2に示すVLIW命令に対応するVLIWプロセッサ10によれば、小さな回路規模で、複数の比較処理が含まれる条件判定処理を効率良く行うことができる。これに関して、以下の実施の形態を用いて詳細に説明する。

【0066】

図6は、本発明の実施の形態にかかるVLIWプロセッサ100を示す。重複を避けるため、図6において、図1に示す構成要素(信号を含む)と同様のものについて同様の符号を付与しており、これらの構成要素に関しては、必要があるときにのみ説明する。

【0067】

VLIWプロセッサ100は、制御部110、第1の比較演算器122、第2の比較演算器124、第1の演算器130、第2の演算器140、第3の演算器150、プレディケイトレジスタ160を備える。

【0068】

制御部110は、入力されたVLIW命令を格納する命令レジスタ(図示せず)を有し、該命令レジスタに格納されたVLIW命令に基づいて、第1の比較演算信号V1、第1の入力信号V11、第2の入力信号V12、第2の比較演算信号V2、第3の入力信号V21、第4の入力信号V22、第1の制御信号ctr1、第2の制御信号ctr2、第3の制御信号ctr3を出力する。

【0069】

具体的には、制御部110は、第1の比較命令COMPARE1に含まれる比較演算子と2つのオペランドを夫々示す第1の比較演算信号V1、第1の入力信号V11、第2の入力信号V12を第1の比較演算器122に出力する。

【0070】

また、制御部110は、第2の比較命令COMPARE2に含まれる比較演算子と2つのオペランドを夫々示す第2の比較演算信号V2、第3の入力信号V21、第4の入力信号V22を第2の比較演算器124に出力する。

【0071】

また、制御部110は、第1の合成指定CMB1に応じた第1の制御信号ctr1、第2の合成指定CMB2に応じた第2の制御信号ctr2、第3の合成指定CMB3に応じた第3の制御信号ctr3を、第1の演算器130、第2の演算器140、第3の演算器150に夫々出力する。なお、第2の比較命令COMPARE2及び第2の合成指定CMB2が空であるときと、第3の合成指定CMB3が空であるときのいずれか一方に該当する場合には、制御部110は、第3の合成指定CMB3を「合成しない」であると理解してその旨を示す第3の制御信号ctr3信号を第3の演算器150に出力する。

【0072】

第1の比較演算器122は、比較演算を行って第1の比較結果CMP1を第1の演算器130に出力する。第2の比較演算器124は、比較演算を行って第2の比較結果CMP2を第2の演算器140に出力する。

【0073】

図7は、第1の演算器130を示す。第1の演算器130は、ANDゲート132、ORゲート134、セレクタ136を備える。

【0074】

ANDゲート132とORゲート134は、第1の比較演算器122からの第1の比較結果CMP1と、プレディケイトレジスタ160からの実行結果PRが入力され、夫々論理積と論理和をセレクタ136に出力する。

【0075】

セレクタ136には、ANDゲート132からの論理積、ORゲート134からの論理和、第1の比較結果CMP1、制御部110からの第1の制御信号ctr1が入力され、第1の制御信号ctr1に従って、入力された3つの値のうちの1つを選択して第3の演算器150に出力する。セレクタ136の出力は、第1の演算結果CR1となる。

【0076】

具体的には、第1の演算器130は、第1の制御信号ctr1が「合成しない」を示すときに、第1の比較結果CMP1を第1の演算結果CR1として出力する。一方、第1の制御信号ctr1が「論理積」を示すときには、ANDゲート132の出力を第1の演算結果CR1として出力し、第1の制御信号ctr1が「論理和」を示すときには、ORゲート134の出力を第1の演算結果CR1として出力する。

【0077】

図8は、第2の演算器140を示す。第2の演算器140は、ANDゲート142、ORゲート144、セレクタ146を備える。

【0078】

ANDゲート142とORゲート144は、第2の比較演算器124からの第2の比較結果CMP2と、プレディケイトレジスタ160からの実行結果PRが入力され、夫々論理積と論理和をセレクタ146に出力する。

【0079】

セレクタ146には、ANDゲート142からの論理積、ORゲート144からの論理和、第2の比較結果CMP2、制御部110からの第2の制御信号ctr2が入力され、第2の制御信号ctr2に従って、入力された3つの値のうちの1つを選択して第3の演算器150に出力する。セレクタ146の出力は、第2の演算結果CR2となる。

【0080】

具体的には、第2の演算器140は、第2の制御信号ctr2が「合成しない」を示すときに、第2の比較結果CMP2を第2の演算結果CR2として出力する。一方、第2の制御信号ctr2が「論理積」を示すときには、ANDゲート142の出力を第2の演算結果CR2として出力し、第2の制御信号ctr2が「論理和」を示すときには、ORゲート144の出力を第2の演算結果CR2として出力する。

【0081】

図9は、第3の演算器150を示す。第3の演算器150は、ANDゲート152、ORゲート154、セレクタ156を備える。

【0082】

ANDゲート152とORゲート154は、第1の演算器130からの第1の演算結果CR1と第2の演算器140からの第2の演算結果CR2が入力され、夫々論理積と論理和をセレクタ156に出力する。

【0083】

セレクタ156には、ANDゲート152からの論理積、ORゲート154からの論理和、第1の演算結果CR1、制御部110からの第3の制御信号ctr3が入力され、第3の制御信号ctr3に従って、入力された3つの値のうちの1つを選択してプレディケイトレジスタ160に出力する。セレクタ156の出力は、実行結果PR+となる。

【0084】

具体的には、第3の演算器150は、第3の制御信号ctr3が「合成しない」を示すときに、第1の演算結果CR1を実行結果PR+として出力する。一方、第3の制御信号ctr3が「論理積」を示すときには、ANDゲート152の出力を実行結果PR+として出力し、第3の制御信号ctr3が「論理和」を示すときには、ORゲート154の出力を実行結果PR+として出力する。

【0085】

プレディケイトレジスタ160は、第3の演算器150からの最新の実行結果PR+を保持する。すなわち、今回のVLIW命令の実行結果の実行結果PR+は、次のVLIW命令の実行時には、実行結果PRとなる。

【0086】

図10〜図13を参照して、図2に示すVLIW命令における各比較命令と合成指定の組合せのパターン毎に、VLIWプロセッサ100が実行する処理を説明する。

【0087】

<パターンA>

パターンAは、VLIW命令に第1の比較命令COMPARE1と第2の比較命令COMPARE2が共にあると共に、全ての合成指定(CMB1、CMB2、CMB3)が、「論理積」と「論理和」のいずれかを示すパターンである。パターンAは、パターンA(1)〜パターンA(4)の4つが含まれる。

【0088】

図10に示すように、パターンA(1)は、全ての合成指定が「AND」を示すVLIW命令「COMPARE1_AND COMPARE2_AND AND」の場合である。

【0089】

該パターンA(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理積と、実行結果PR(1つ前の実行結果)との論理積である。

【0090】

パターンA(2)は、全ての合成指定が「OR」を示すVLIW命令「COMPARE1_OR COMPARE2_OR OR」の場合である。

【0091】

該パターンA(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理和と、実行結果PRとの論理和である。

【0092】

パターンA(3)は、第1の合成指定CMB1と第2の合成指定CMB2が共に「AND」を示し、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_AND COMPARE2_AND OR」の場合である。

【0093】

該パターンA(3)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理和と、実行結果PRとの論理積である。

【0094】

パターンA(4)は、第1の合成指定CMB1と第2の合成指定CMB2が共に「OR」を示し、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_OR COMPARE2_OR AND」の場合である。

【0095】

該パターンA(4)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理積と、実行結果PRとの論理和である。

【0096】

すなわち、該パターンAの命令の場合に、VLIWプロセッサ100は、1サイクルで、2つの比較命令の実行と、第1の比較命令が示す比較の結果と実行結果PRとの論理演算と、第2の比較命令が示す比較の結果と実行結果PRとの論理演算と、該2つの論理演算の結果のさらなる論理演算を行うことができる。

【0097】

<パターンB>

パターンBは、VLIW命令に第1の比較命令COMPARE1と第2の比較命令COMPARE2が共にあり、第1の合成指定CMB1と第2の合成指定CMB2のいずれか一方が空であり、第3の合成指定CMB3が「論理積」と「論理和」のいずれかを示すパターンである。パターンBは、パターンB(1)〜パターンB(4)の4つが含まれる。

【0098】

図11に示すように、パターンB(1)は、第1の合成指定CMB1が「AND」を示し、第2の合成指定CMB2が空であり、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_AND COMPARE2_ OR」の場合である。

【0099】

該パターンB(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRとの論理積と、第2の比較結果CMP2との論理和である。

【0100】

パターンB(2)は、第1の合成指定CMB1が空であり、第2の合成指定CMB2が「AND」を示し、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_ COMPARE2_AND OR」の場合である。

【0101】

該パターンB(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第2の比較結果CMP2と実行結果PRの論理積と、第1の比較結果CMP1との論理和である。

【0102】

パターンB(3)は、第1の合成指定CMB1が「OR」であり、第2の合成指定CMB2が空であり、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_OR COMPARE2_ AND」の場合である。

【0103】

該パターンB(3)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRとの論理和と、第2の比較結果CMP2との論理積である。

【0104】

パターンB(4)は、第1の合成指定CMB1が空であり、第2の合成指定CMB2が「OR」を示し、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_ COMPARE2_OR AND」の場合である。

【0105】

該パターンB(4)のときに、VLIWプロセッサ100が得た実行結果PR+は、第2の比較結果CMP2と実行結果PRの論理積と、第1の比較結果CMP1との論理和である。

【0106】

すなわち、該パターンBの命令の場合に、VLIWプロセッサ100は、1サイクルで、2つの比較命令の実行と、片方の比較命令が示す比較の結果と実行結果PRの論理演算と、該論理演算の結果と他方の比較命令の実行結果の更なる論理演算を行うことができる。

【0107】

<パターンC>

パターンCは、VLIW命令に第1の比較命令COMPARE1と第2の比較命令COMPARE2が共にあり、第1の合成指定CMB1と第2の合成指定CMB2のいずれも空であり、第3の合成指定CMB3が「論理積」と「論理和」のいずれかを示すパターンである。パターンCは、パターンC(1)〜パターンC(2)の4つが含まれる。

【0108】

図12に示すように、パターンC(1)は、第3の合成指定CMB3が「AND」を示すVLIW命令「COMPARE1_ COMPARE2_ AND」の場合である。

【0109】

該パターンC(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理積である。

【0110】

パターンC(2)は、第3の合成指定CMB3が「OR」を示すVLIW命令「COMPARE1_ COMPARE2_ OR」の場合である。

【0111】

該パターンC(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と第2の比較結果CMP2の論理和である。

【0112】

すなわち、該パターンCの命令の場合に、VLIWプロセッサ100は、1サイクルで、2つの比較命令の実行と、該2つの比較命令が夫々示す比較の結果の論理演算を行うことができる。

【0113】

<パターンD>

上述したパターンA〜Cのいずれの場合においても、VLIW命令に2つの比較命令が含まれる。本パターンDは、1つの比較命令(第1の比較命令COMPARE1)のみを含むVLIW命令の場合である。パターンDは、パターンD(1)〜パターンD(3)の3つが含まれる。

【0114】

図13に示すように、パターンD(1)は、第1の比較命令COMPARE1に対応する第1の合成指定CMB1が「AND」を示すVLIW命令「COMPARE1_AND」の場合である。

【0115】

該パターンD(1)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRの論理積である。

【0116】

パターンD(2)は、第1の比較命令COMPARE1に対応する第1の合成指定CMB1が「OR」を示すVLIW命令「COMPARE1_OR」の場合である。

【0117】

該パターンD(2)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1と実行結果PRの論理和である。

【0118】

パターンD(3)は、第1の比較命令COMPARE1に対応する第1の合成指定CMB1が空であるVLIW命令「COMPARE1」の場合である。

【0119】

該パターンD(3)のときに、VLIWプロセッサ100が得た実行結果PR+は、第1の比較結果CMP1である。

【0120】

すなわち、該パターンDの命令の場合に、VLIWプロセッサ100は、1サイクルで、1つの比較命令の実行を行うことができる。

【0121】

ここで、VLIWプロセッサ100への実装例を説明する。なお、以下において、プログラムの具体例の中で、分かりやすいように、「論理積」と「論理和」を示す第3の合成指定CMB3を夫々「Fand」と「For」で表わす。また、各プログラムの例において、1ラインは1サイクルの処理を示す。

【0122】

図14に示すように、式(1)が示す処理を、5つの比較演算A1〜A5、4つの論理演算B1〜B4、処理の結果をセットするC1に分割することができる。本実施の形態におけるVLIW命令及びVLIWプロセッサ100によれば、1サイクルにおいて、2つの比較命令の並列実行、夫々の比較命令が示す比較の結果と1つ前の実行結果PR(プログラムの視点からは1ライン前の処理結果)との論理演算、2つの論理演算のさらなる論理演算が可能であるため、式(1)に示す処理を図14に示すように分割し、分岐命令を使用せずにVLIWプロセッサ100へ実装することができる。

【0123】

図15は、式(1)に示す処理をVLIWプロセッサ100へ実装する際のプログラムの例を示す。

【0124】

該プログラムの1ライン目が示す処理は、第1の比較「SC==0」と、第2の比較「SC==2」を並列に行うと共に、2つの比較結果を論理和演算して、該論理和演算の結果をプレディケイトレジスタ160に格納する処理である。なお、2つの「compare」は、第1の比較命令と第2の比較命令であり、第1の合成指定CMB1と第2の合成指定CMB2のいずれも空であり、「合成をしない」を示す。これは、図12に示すパターンC(2)の処理である。

【0125】

2ライン目が示す処理は、第1の比較「val==b」と、第2の比較「val>b」を並列に実行すると共に、第1の比較結果と1ライン目の実行結果(プレディケイトレジスタ160の値)の論理積と、第2の比較結果との論理和を得てプレディケイトレジスタ160に格納する処理である。これは、図11に示すパターンB(1)の処理である。

【0126】

3ライン目が示す処理は、第1の比較(val>c)を実行すると共に、第1の比較結果と2ライン目の実行結果との論理積を得てプレディケイトレジスタ160に格納する処理である。これは、図13に示すパターンD(1)の処理である。

【0127】

4ライン目が示す処理は、プレディケイトレジスタ160の値に応じて引数resに1を格納する命令「mset」を実行する処理である。

【0128】

このように、本実施の形態のVLIWプロセッサ100によれば、式(1)が示す処理を4サイクルで完了することができる。

【0129】

前述したように、式(1)が示す処理を従来のVLIWプロセッサに分岐命令により実装する際に、分岐ペナルティを2サイクルである場合には、9サイクルが必要である(図18)。

【0130】

また、図16は、式(2)が示す処理を分割した態様を示す。図示のように、式(2)が示す処理を、6つの比較演算A1〜A6、5つの論理演算B1〜B5、処理の結果をセットする処理C1に分割することができる。

【0131】

図17は、式(2)が示す処理を図16に示すように分割して、VLIWプロセッサ100へ実装する際のプログラムの例を示す。

【0132】

該プログラムの1ライン目が示す処理は、第1の比較「d02≠0」と、第2の比較「d12==0」を並列に行うと共に、2つの比較結果を論理積演算して、該論理積演算の結果をプレディケイトレジスタ160に格納する処理である。これは、図12に示すパターンC(1)の処理である。

【0133】

2ライン目が示す処理は、第1の比較「d00≠0」と、第2の比較「d10=0」を並列に実行すると共に、第1の比較結果と1ライン目の実行結果の論理和と、第2の比較結果と1ライン目の実行結果の論理和との論理積を得てプレディケイトレジスタ160に格納する処理である。これは、図10に示すパターンA(4)の処理である。

【0134】

3ライン目が示す処理は、第1の比較(d11≠0)と、第2の比較(d01=0)を並列に実行すると共に、第1の比較結果と2ライン目の実行結果の論理積と、第2の比較結果と2ライン目の実行結果の論理積との論理積を得てプレディケイトレジスタ160に格納する処理である。これは、図10に示すパターンA(1)の処理である。

【0135】

4ライン目が示す処理は、プレディケイトレジスタ160の値に応じて引数resに1を格納する命令「mset」を実行する処理である。

【0136】

このように、本実施の形態のVLIWプロセッサ100によれば、式(2)が示す処理を4サイクルで完了することができる。

【0137】

前述したように、式(2)に示す処理を従来のVLIWプロセッサに分岐命令により実行する際に、分岐ペナルティを2サイクルである場合には、12サイクルが必要である(図19)。

【0138】

このように、本実施の形態のVLIWプロセッサ100によれば、複数の比較処理が含まれる条件判定処理を効率良く行うことができる。

【0139】

本願発明者は、画像に対するエッジ検出処理における条件判定処理をVLIWプロセッサ100に実行させた結果、通常のVLIWプロセッサの2倍ほどの速度を得ることを確認した。

【0140】

以上、実施の形態をもとに本発明を説明した。実施の形態は例示であり、本発明の主旨から逸脱しない限り、上述した実施の形態に対してさまざまな変更、増減、組合せを行ってもよい。これらの変更、増減、組合せが行われた変形例も本発明の範囲にあることは当業者に理解されるところである。

【0141】

例えば、VLIWプロセッサ100において、最新の実行結果PR+を保持するレジスタとしてプレディケイトレジスタ160が用いられている。一般的に、プレディケイトレジスタは1ビットであり、汎用レジスタは16ビットまたは32ビットである。VLIWプロセッサ100において、VLIW命令の実行結果が1ビットであるため、プレディケイトレジスタ160を用いることにより、さらに回路規模を抑制することができる。勿論、最新の実行結果PR+を保持するレジスタとして汎用レジスタを用いてもよい。

【0142】

また、例えば、上述したように、1つの比較命令のみを実行する場合には、第3の合成指定CMB3が空であってもよい。この場合、第3の合成指定フィールドを空にせず、他の命令の即値フィールドなどの別の用途に用いてもよい。

【符号の説明】

【0143】

10 VLIWプロセッサ

50 レジスタ

100 VLIWプロセッサ

110 制御部

122 第1の比較演算器

124 第2の比較演算器

130 第1の演算器

132 ANDゲート

134 ORゲート

136 セレクタ

140 第2の演算器

142 ANDゲート

144 ORゲート

146 セレクタ

150 第3の演算器

152 ANDゲート

154 ORゲート

156 セレクタ

160 プレディケイトレジスタ

ctr1 第1の制御信号

ctr2 第2の制御信号

ctr3 第3の制御信号

COMPARE1 第1の比較命令

E2 第2の比較命令

CMB1 第1の合成指定

CMB2 第2の合成指定

CMB3 第3の合成指定

CMP1 第1の比較結果

CMP2 第2の比較結果

CR1 第1の演算結果

CR2 第2の演算結果

PR 前回の実行結果

PR+ 今回の実行結果

V1 第1の比較演算信号

V11 第1の入力信号

V12 第2の入力信号

V2 第2の比較演算信号

V21 第3の入力信号

V22 第4の入力信号

【特許請求の範囲】

【請求項1】

VLIW(Very Long Instruction Word)プロセッサであって、

第1の比較演算器と、第2の比較演算器と、第1の演算器と、第2の演算器と、第3の演算器と、レジスタとを備え、

前記第1の比較演算器は、第1の比較演算信号と第1の入力信号と第2の入力信号とが入力され、該第1の入力信号と該第2の入力信号に対して前記第1の比較演算信号が示す比較を行い、該比較の結果を出力し、

前記第2の比較演算器は、第2の比較演算信号と第3の入力信号と第4の入力信号とが入力され、該第3の入力信号と該第4の入力信号に対して前記第2の比較演算信号が示す比較を行い、該比較の結果を出力し、

前記第1の演算器は、第1の制御信号と、前記第1の比較演算器による比較の結果と、前記レジスタが既に保持している値とが入力され、前記第1の制御信号に応じて、前記第1の比較演算器による比較の結果と、該比較の結果と前記レジスタの値の論理積と、該比較の結果と前記レジスタの値の論理和とのいずれか1つを第1の演算結果として出力し、

前記第2の演算器は、第2の制御信号と、前記第2の比較演算器による比較の結果と、前記レジスタが既に保持している値とが入力され、前記第2の制御信号に応じて、前記第2の比較演算器による比較の結果と、該比較の結果と前記レジスタの値の論理積と、該比較の結果と前記レジスタの値の論理和とのいずれか1つを第2の演算結果として出力し、

前記第3の演算器は、第3の制御信号と、前記第1の演算結果と、前記第2の演算結果とが入力され、前記第3の制御信号に応じて、前記第1の演算結果と、前記第1の演算結果と前記第2の演算結果の論理積と、前記第1の演算結果と前記第2の演算結果の論理和とのいずれか1つを実行結果として前記レジスタに出力し、

前記レジスタは、前記第3の演算器からの前記実行結果を新たに保持し、出力することを特徴とするVLIWプロセッサ。

【請求項2】

第1の比較命令と、前記第1の比較命令に対応し、「合成しない」、「論理積」、「論理和」のいずれかを示す第1の合成指定と、第2の比較命令と、前記第2の比較命令に対応し、「合成しない」、「論理積」、「論理和」のいずれかを示す第2の合成指定と、「論理積」、「論理和」のいずれかを示す第3の合成指定とを含む1つのVLIW命令を実行するものであって、

前記第1の比較命令に含まれる比較演算子と2つの入力オペランドを夫々示す信号を、前記第1の比較演算信号と前記第1の入力信号と前記第2の入力信号として前記第1の比較演算器に入力し、

前記第2の比較命令に含まれる比較演算子と2つの入力オペランドを夫々示す信号を、前記第2の比較演算信号と前記第3の入力信号と前記第4の入力信号として前記第2の比較演算器に入力し、

前記第1の合成指定に応じた前記第1の制御信号と、前記第2の合成指定に応じた前記第2の制御信号と、前記第3の合成指定に応じた前記第3の制御信号とを、前記第1の演算器と、前記第2の演算器と、前記第3の演算器とに夫々入力する制御部をさらに備えることを特徴とする請求項1に記載のVLIWプロセッサ。

【請求項3】

前記制御部は、

前記第2の比較命令が空であるときと、前記第3の合成指定が空であるときのいずれか一方に該当する場合に、

前記第1の比較命令に応じた前記第1の比較演算信号と前記第1の入力信号と前記第2の入力信号を前記第1の比較演算器に入力し、

前記第1の演算結果を前記実行結果として出力することを示す前記第3の制御信号を前記第3の演算器に入力することを特徴とする請求項2に記載のVLIWプロセッサ。

【請求項4】

前記第1の演算器は、

前記第1の比較演算器による比較の結果と前記レジスタが既に保持している値が入力される第1のANDゲートと第1のORゲートと、

前記第1の制御信号と、前記第1の比較演算器による比較の結果と、前記第1のANDゲートの出力と、前記第1のORゲートの出力とが入力される第1のセレクタとを有し、

前記第1のセレクタは、前記第1の制御信号に応じて、3つの入力のうちの1つを前記第1の演算結果に選択して出力することを特徴とする請求項1から3のいずれか1項に記載のVLIWプロセッサ。

【請求項5】

前記第2の演算器は、

前記第2の比較演算器による比較の結果と前記レジスタが既に保持している値が入力される第2のANDゲートと第2のORゲートと、

前記第2の制御信号と、前記第2の比較演算器による比較の結果と、前記第2のANDゲートの出力と、前記第2のORゲートの出力とが入力される第2のセレクタとを有し、

前記第2のセレクタは、前記第2の制御信号に応じて、3つの入力のうちの1つを前記第2の演算結果に選択して出力することを特徴とする請求項1から4のいずれか1項に記載のVLIWプロセッサ。

【請求項6】

前記第3の演算器は、

前記第1の演算結果と前記第2の演算結果が入力される第3のANDゲートと第3のORゲートと、

前記第3の制御信号と、前記第1の演算結果と、前記第3のANDゲートの出力と、前記第3のORゲートの出力とが入力される第3のセレクタとを有し、

前記第3のセレクタは、前記第3の制御信号に応じて、3つの入力のうちの1つを前記実行結果に選択して出力することを特徴とする請求項1から5のいずれか1項に記載のVLIWプロセッサ。

【請求項7】

前記レジスタは、プレディケイトレジスタであることを特徴とする請求項1から6のいずれか1項に記載のVLIWプロセッサ。

【請求項8】

VLIW命令の命令構造であって

第1の比較命令を格納する第1の比較命令フィールドと、

第1の合成指定を格納する第1の合成指定フィールドと、

第2の比較命令を格納する第2の比較命令フィールドと、

第2の合成指定を格納する第2の合成指定フィールドと、

第3の合成指定を格納する第3の合成指定フィールドとを含み、

前記第1の合成指定は、前記第1の比較命令が示す比較の結果と、前記比較の結果と1つ前のVLIW命令の実行結果の論理積と、前記比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第1の演算結果とするかを示すものであり、

前記第2の合成指定は、前記第2の比較命令が示す比較の結果と、前記比較の結果と1つ前のVLIW命令の実行結果の論理積と、前記比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第2の演算結果とするかを示すものであり、

前記第3の合成指定は、前記第1の演算結果と、前記第1の演算結果と前記第2の演算結果の論理積と、前記第1の演算結果と前記第2の演算結果の論理和とのいずれを今回のVLIW命令の実行結果とするかを示すものであることを特徴とする命令構造。

【請求項9】

前記第2の比較命令フィールドと、前記第3の合成指定フィールドとのいずれか一方が空であることは、前記第1の演算結果を今回のVLIW命令の実行結果とすることを示すことを特徴とする請求項8に記載のVLIW命令。

【請求項10】

第1の比較命令と、第2の比較命令と、「合成しない」、「論理積」、「論理和」のいずれか1つを示す第1と第2の合成指定と、「論理積」と「論理和」のいずれかを示す第3の3つの合成指定とを含むVLIW命令が入力され、レジスタを備えるVLIWプロセッサにおけるVLIW命令の実行方法であって、

前記第1の合成指定が「合成しない」を示す場合には、前記第1の比較命令が示す比較の結果を第1の演算結果として出力し、他の場合には、前記第1の合成指定が示す論理演算を、前記第1の比較命令が示す比較の結果と前記レジスタが既に保持している値とに対して行って得た値を前記第1の演算結果として出力し、

前記第2の合成指定が「合成しない」を示す場合には、前記第2の比較命令が示す比較の結果を第2の演算結果として出力し、他の場合には、前記第2の合成指定が示す論理演算を、前記第2の比較命令が示す比較の結果と前記レジスタが既に保持している値とに対して行って得た値を前記第2の演算結果として出力し、

前記第3の合成指定が示す論理演算を、前記第1の演算結果と前記第2の演算結果に対して行って得た値を今回のVLIW命令の実行結果として前記レジスタに出力し、

前記レジスタにより前記実行結果を新たに保持し、出力することを特徴とする実行方法。

【請求項11】

前記第2の比較命令と、前記第3の合成指定とのいずれか一方が空であるときに、前記第1の演算結果を今回のVLIW命令の実行結果として前記レジスタに出力することを特徴とする請求項10に記載の実行方法。

【請求項1】

VLIW(Very Long Instruction Word)プロセッサであって、

第1の比較演算器と、第2の比較演算器と、第1の演算器と、第2の演算器と、第3の演算器と、レジスタとを備え、

前記第1の比較演算器は、第1の比較演算信号と第1の入力信号と第2の入力信号とが入力され、該第1の入力信号と該第2の入力信号に対して前記第1の比較演算信号が示す比較を行い、該比較の結果を出力し、

前記第2の比較演算器は、第2の比較演算信号と第3の入力信号と第4の入力信号とが入力され、該第3の入力信号と該第4の入力信号に対して前記第2の比較演算信号が示す比較を行い、該比較の結果を出力し、

前記第1の演算器は、第1の制御信号と、前記第1の比較演算器による比較の結果と、前記レジスタが既に保持している値とが入力され、前記第1の制御信号に応じて、前記第1の比較演算器による比較の結果と、該比較の結果と前記レジスタの値の論理積と、該比較の結果と前記レジスタの値の論理和とのいずれか1つを第1の演算結果として出力し、

前記第2の演算器は、第2の制御信号と、前記第2の比較演算器による比較の結果と、前記レジスタが既に保持している値とが入力され、前記第2の制御信号に応じて、前記第2の比較演算器による比較の結果と、該比較の結果と前記レジスタの値の論理積と、該比較の結果と前記レジスタの値の論理和とのいずれか1つを第2の演算結果として出力し、

前記第3の演算器は、第3の制御信号と、前記第1の演算結果と、前記第2の演算結果とが入力され、前記第3の制御信号に応じて、前記第1の演算結果と、前記第1の演算結果と前記第2の演算結果の論理積と、前記第1の演算結果と前記第2の演算結果の論理和とのいずれか1つを実行結果として前記レジスタに出力し、

前記レジスタは、前記第3の演算器からの前記実行結果を新たに保持し、出力することを特徴とするVLIWプロセッサ。

【請求項2】

第1の比較命令と、前記第1の比較命令に対応し、「合成しない」、「論理積」、「論理和」のいずれかを示す第1の合成指定と、第2の比較命令と、前記第2の比較命令に対応し、「合成しない」、「論理積」、「論理和」のいずれかを示す第2の合成指定と、「論理積」、「論理和」のいずれかを示す第3の合成指定とを含む1つのVLIW命令を実行するものであって、

前記第1の比較命令に含まれる比較演算子と2つの入力オペランドを夫々示す信号を、前記第1の比較演算信号と前記第1の入力信号と前記第2の入力信号として前記第1の比較演算器に入力し、

前記第2の比較命令に含まれる比較演算子と2つの入力オペランドを夫々示す信号を、前記第2の比較演算信号と前記第3の入力信号と前記第4の入力信号として前記第2の比較演算器に入力し、

前記第1の合成指定に応じた前記第1の制御信号と、前記第2の合成指定に応じた前記第2の制御信号と、前記第3の合成指定に応じた前記第3の制御信号とを、前記第1の演算器と、前記第2の演算器と、前記第3の演算器とに夫々入力する制御部をさらに備えることを特徴とする請求項1に記載のVLIWプロセッサ。

【請求項3】

前記制御部は、

前記第2の比較命令が空であるときと、前記第3の合成指定が空であるときのいずれか一方に該当する場合に、

前記第1の比較命令に応じた前記第1の比較演算信号と前記第1の入力信号と前記第2の入力信号を前記第1の比較演算器に入力し、

前記第1の演算結果を前記実行結果として出力することを示す前記第3の制御信号を前記第3の演算器に入力することを特徴とする請求項2に記載のVLIWプロセッサ。

【請求項4】

前記第1の演算器は、

前記第1の比較演算器による比較の結果と前記レジスタが既に保持している値が入力される第1のANDゲートと第1のORゲートと、

前記第1の制御信号と、前記第1の比較演算器による比較の結果と、前記第1のANDゲートの出力と、前記第1のORゲートの出力とが入力される第1のセレクタとを有し、

前記第1のセレクタは、前記第1の制御信号に応じて、3つの入力のうちの1つを前記第1の演算結果に選択して出力することを特徴とする請求項1から3のいずれか1項に記載のVLIWプロセッサ。

【請求項5】

前記第2の演算器は、

前記第2の比較演算器による比較の結果と前記レジスタが既に保持している値が入力される第2のANDゲートと第2のORゲートと、

前記第2の制御信号と、前記第2の比較演算器による比較の結果と、前記第2のANDゲートの出力と、前記第2のORゲートの出力とが入力される第2のセレクタとを有し、

前記第2のセレクタは、前記第2の制御信号に応じて、3つの入力のうちの1つを前記第2の演算結果に選択して出力することを特徴とする請求項1から4のいずれか1項に記載のVLIWプロセッサ。

【請求項6】

前記第3の演算器は、

前記第1の演算結果と前記第2の演算結果が入力される第3のANDゲートと第3のORゲートと、

前記第3の制御信号と、前記第1の演算結果と、前記第3のANDゲートの出力と、前記第3のORゲートの出力とが入力される第3のセレクタとを有し、

前記第3のセレクタは、前記第3の制御信号に応じて、3つの入力のうちの1つを前記実行結果に選択して出力することを特徴とする請求項1から5のいずれか1項に記載のVLIWプロセッサ。

【請求項7】

前記レジスタは、プレディケイトレジスタであることを特徴とする請求項1から6のいずれか1項に記載のVLIWプロセッサ。

【請求項8】

VLIW命令の命令構造であって

第1の比較命令を格納する第1の比較命令フィールドと、

第1の合成指定を格納する第1の合成指定フィールドと、

第2の比較命令を格納する第2の比較命令フィールドと、

第2の合成指定を格納する第2の合成指定フィールドと、

第3の合成指定を格納する第3の合成指定フィールドとを含み、

前記第1の合成指定は、前記第1の比較命令が示す比較の結果と、前記比較の結果と1つ前のVLIW命令の実行結果の論理積と、前記比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第1の演算結果とするかを示すものであり、

前記第2の合成指定は、前記第2の比較命令が示す比較の結果と、前記比較の結果と1つ前のVLIW命令の実行結果の論理積と、前記比較の結果と1つ前のVLIW命令の実行結果の論理和とのいずれを第2の演算結果とするかを示すものであり、

前記第3の合成指定は、前記第1の演算結果と、前記第1の演算結果と前記第2の演算結果の論理積と、前記第1の演算結果と前記第2の演算結果の論理和とのいずれを今回のVLIW命令の実行結果とするかを示すものであることを特徴とする命令構造。

【請求項9】

前記第2の比較命令フィールドと、前記第3の合成指定フィールドとのいずれか一方が空であることは、前記第1の演算結果を今回のVLIW命令の実行結果とすることを示すことを特徴とする請求項8に記載のVLIW命令。

【請求項10】

第1の比較命令と、第2の比較命令と、「合成しない」、「論理積」、「論理和」のいずれか1つを示す第1と第2の合成指定と、「論理積」と「論理和」のいずれかを示す第3の3つの合成指定とを含むVLIW命令が入力され、レジスタを備えるVLIWプロセッサにおけるVLIW命令の実行方法であって、

前記第1の合成指定が「合成しない」を示す場合には、前記第1の比較命令が示す比較の結果を第1の演算結果として出力し、他の場合には、前記第1の合成指定が示す論理演算を、前記第1の比較命令が示す比較の結果と前記レジスタが既に保持している値とに対して行って得た値を前記第1の演算結果として出力し、

前記第2の合成指定が「合成しない」を示す場合には、前記第2の比較命令が示す比較の結果を第2の演算結果として出力し、他の場合には、前記第2の合成指定が示す論理演算を、前記第2の比較命令が示す比較の結果と前記レジスタが既に保持している値とに対して行って得た値を前記第2の演算結果として出力し、

前記第3の合成指定が示す論理演算を、前記第1の演算結果と前記第2の演算結果に対して行って得た値を今回のVLIW命令の実行結果として前記レジスタに出力し、

前記レジスタにより前記実行結果を新たに保持し、出力することを特徴とする実行方法。

【請求項11】

前記第2の比較命令と、前記第3の合成指定とのいずれか一方が空であるときに、前記第1の演算結果を今回のVLIW命令の実行結果として前記レジスタに出力することを特徴とする請求項10に記載の実行方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【公開番号】特開2013−114608(P2013−114608A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262706(P2011−262706)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(302062931)ルネサスエレクトロニクス株式会社 (8,021)

【Fターム(参考)】

[ Back to top ]