n−FET用途のためのHfSiN金属を形成する方法

【課題】 高k誘電体及び界面層を含むゲート・スタック上に、熱的に安定した新しい金属化合物を提供すること。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

【解決手段】 高k誘電体及び界面層を含むゲート・スタック上に、約4.0eVから約4.5eVまで、好ましくは約4.3eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む金属化合物である。さらに、(約1000℃のオーダーの)高温でHfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価酸化物厚(伝統的には、12Å)をもたらす。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体デバイス、及びこれを製造する方法に関する。より具体的には、本発明は、高誘電率k/界面層のスタック上の、熱的に安定したn型金属を含む相補型金属酸化膜半導体(CMOS)に関する。本発明はまた、CMOS処理の流れと統合することができる、熱的に安定したn型金属を形成するプロセスも提供する。

【背景技術】

【0002】

標準的なCMOSデバイスにおいては、一般に、ポリシリコンが、標準的なゲート材料である。ポリシリコン・ゲートを用いてCMOSデバイスを製造する技術は、絶えず発展した状態にあり、現在、半導体産業において広く用いられている。ポリシリコン・ゲートを用いる1つの利点は、これらが高温に耐え得ることである。しかしながら、ポリシリコン・ゲートの使用と関連した幾つかの問題もある。例えば、ポリ空乏効果及び相対的に高い電気シート抵抗(約150オーム/スクェア)のために、CMOSデバイスにおいて一般的に使用されるポリSiゲートは、0.1ミクロン以下のチャネル長についての、チップ性能のゲート要因になりつつある。ポリSiゲートに関連する別の問題は、ボロンのようなポリSiゲート内のドーパントが、薄いゲート誘電体を通って容易に拡散し、デバイス性能をさらに低下させ得ることである。

【0003】

ポリSiゲートに関連した問題を回避するために、ポリSiゲートを単一の金属と置き換えることが提案された。高k誘電体を用いるCMOS技術のために、異なる仕事関数(pFETについての仕事関数とnFETについての仕事関数)を有する金属が必要とされる。金属/高k誘電体スタックに、ソース/ドレインの自己整合された注入の活性化のために必要とされる(約1000℃のオーダーの)高温アニールを施す必要がある。ゲート・スタックの反応は、材料の選択を制限するこの高温アニール中に生じる。例えば、W及び高k誘電体を含むゲート・スタックにおいて、SiO2の再成長は、反転層のスケーラビリティを制限する界面で行われる。例えば、非特許文献1を参照されたい。

【0004】

金属化合物は、より安定したものにしてもよいが、依然として適切な仕事関数を目標とすることに関する問題がある。例えば、nFETの候補としてTaSiNが提案されたが、依然としてその仕事関数に関する幾つかの問題が存在し、nFETデバイスにおいて移動度の減少が観察される。さらに、TaSiNを用いると、反転層厚のスケーラビリティが幾分制限されるように見える。

【0005】

【非特許文献1】A.Callegari他、IEDM2004、p.825、S.Francisco Ca.,2004年12月13日―15日

【非特許文献2】S.M.Sze、Physics of Semiconductor Devaices、第2版、395−397ページ、J.Wiley&Sons

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記を鑑みて、高k誘電体を含むゲート・スタック上に熱的に安定した新しい金属化合物を提供する必要性がある。特定的には、nFETデバイスにおいて有用な新しい金属化合物を提供する必要性がある。

【課題を解決するための手段】

【0007】

本発明は、高k誘電体及び界面層を含むゲート・スタック上に、約3.7eVから約4.5eVまで、好ましくは約4.0eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む新しい金属化合物を提供するものである。さらに、(約1000℃のオーダーの)高温で、HfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価の酸化物厚(伝統的には、12Å)をもたらす。

【0008】

大まかに言うと、本発明は、

半導体基板と、

半導体基板上に配置された界面層と、

界面層上に配置された高k誘電体と、

高k誘電体上に配置されたHfSiNゲート金属と

を含む、半導体構造体、即ち薄膜スタックを提供する。

【0009】

さらに、本発明は、

半導体基板と、

少なくとも、基板の一部に配置された界面層、界面層上に配置された高k誘電体及び高ゲート誘電体上に配置されたHfSiN金属を含む、パターン形成されたゲート領域と

を含む、半導体構造体を提供する。

【0010】

上述の薄膜スタック及び半導体構造体に加えて、本発明は、

Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを準備するステップと、

前述の雰囲気中でHfターゲットからHfSiN膜をスパッタリングするステップと

を含む、HfSiN金属化合物を製造する方法も提供する。

【0011】

本発明によると、Si源の活性度を制限する、Heで希釈されたSi源は、膜の品質を向上させる。HfSiN膜の抵抗率は、プロセス・ガスの濃度によって変わり得る。一般的に、窒素濃度及び/又はSi濃度が高いほど、抵抗率が高くなる。

【0012】

本発明はまた、HfSiN膜を形成するために本発明のプロセスを用いる、上述の半導体構造体を製造する方法も提供する。一般論として、最初に、基板の表面上に高k誘電体及び界面層を含むスタックを提供し、その後、上述した処理ステップを用いてスタック上にHfSiN膜を形成することによって、即ち、Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを提供し、雰囲気中でHfターゲットからHfSiN膜をスパッタリングすることによって、半導体構造体が形成される。

【0013】

本発明の幾つかの実施形態においては、HfSiN金属ゲートは、ゲート電極として単独で、又はその上面にシリサイド・コンタクトを含むSi含有ゲート電極と併せて、用いることができる。後者の構造体は、ここでは、デュアル・ポリSi/HfSiN含有FETと呼ばれる。

【0014】

高k誘電体という用語は、本出願の全体を通じて、その誘電率kが、例えば4.0より大きいといった、SiO2よりも大きい絶縁体材料を示すように用いられることが留意される。高k誘電体は、約7.0又はそれより大きいkを有することが好ましい。

【0015】

「界面層」という用語は、本出願の全体を通じて、例えばSiO2及びSiONを含む、少なくともSi原子又はO原子を含む絶縁体材料を示すように用いられる。

【発明を実施するための最良の形態】

【0016】

ここで、高k誘電体及び界面層を含むスタック上の、熱的に安定したn−金属ゲートとして用い得るHfSiN金属化合物と、これを製造する方法とを提供する本発明が、本出願に添付される図面を参照することによって、より詳細に説明される。本発明の図面は、説明のために提供されるものであり、よって、これらの図面は縮尺通りに描かれていないことが留意される。

【0017】

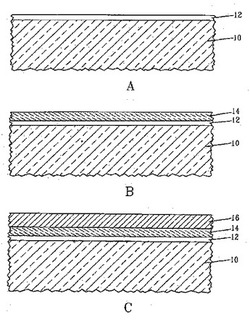

最初に、高k誘電体及び界面層を含むスタック上に本発明のHfSiN金属化合物を含む薄膜スタック構造体を形成する際に用いられる基本的な処理ステップを示す、図1(A)−図1(C)を参照する。図1(A)は、半導体基板10の表面上に界面層12を含む、最初の薄膜スタック構造体を示す。

【0018】

本発明に用いられる半導体基板10は、これらに限られないが、Si、Ge、SiGe、SiC、SiGeC、Ga、GaAs、InAs、InP及び他の全てのIV/IV族、III/V族又はII/VI族化合物半導体を含む、いずれかの半導体材料からなる。半導体基板10はまた、有機半導体、或いはSi/SiGe、シリコン・オン・インシュレータ(silicon-on-insulator、SOI)、又はSiGeオン・インシュレータ(SiGe-on-insulator、SGOI)などの層状半導体を含むこともできる。本発明の幾つかの実施形態においては、半導体基板10が、Si含有半導体材料、即ちシリコンを含む半導体材料からなることが好ましい。半導体基板10は、ドープされたものであってもよく、ドープされていないものであってもよく、或いは内部にドープ領域と非ドープ領域とを含むものであってもよい。

【0019】

半導体基板10はまた、第1のドープ(n−又はp−)領域及び第2のドープ(n−又はp−)領域を含むこともできる。明確にするために、本出願の図面中にドープ領域は具体的に示されていない。第1のドープ領域及び第2のドープ領域は、同じものであってもよく、又はそれらが異なる導電率及び/又はドーピング濃度を有するものであってもよい。これらのドープ領域は、「ウェル」として知られている。半導体基板10は、歪ませてもよく、歪ませなくてもよく、或いは、各々が内部に歪み領域と非歪み領域とを含んでもよい。さらに、半導体基板10は、例えば、100、110、111、又はこれらの組み合わせを含む、任意の結晶配向を有することができる。代替的に、半導体基板10は、異なる結晶配向の少なくとも2つの平坦な面を含むハイブリッド基板とすることができる。

【0020】

次いで、少なくとも1つの分離領域(図示せず)が、一般的には、半導体基板10内に形成される。分離領域は、トレンチ分離領域又はフィールド酸化物分離領域とすることができる。トレンチ分離領域は、当業者に公知の従来のトレンチ分離プロセスを用いて形成される。例えば、トレンチ分離領域を形成するのに、リソグラフィ、エッチング、及びトレンチ誘電体によるトレンチの充填を用いることができる。随意的に、トレンチの充填前に、トレンチ内にライナを形成することができ、トレンチの充填後に緻密化ステップを行うことができ、トレンチの充填に続いて平坦化プロセスを行うこともできる。フィールド酸化物は、いわゆる局所的なシリコン酸化プロセスを用いて形成することができる。少なくとも1つの分離領域が、典型的には、隣接するゲートが反対の導電性をもつときに必要とされる分離を、隣接するゲート領域間に与えることに留意されたい。隣接するゲート領域は、同じ導電性(即ち、両方がn型又はp型)をもつことができ、又は代替的に、それらが異なる導電性(即ち、一方がn型で他方がp型)をもつこともできる。

【0021】

次いで、界面層12が、酸化又は酸窒化のような熱プロセス、化学気相堆積(CVD)、プラズマ強化CVD、原子層堆積(ALD)、蒸着、スパッタリング及び化学溶液堆積、又はこれらの組み合わせのような堆積プロセスを用いて、半導体基板10の表面の上に形成される。代替的に、堆積プロセス及び窒化を用いて、界面層12を形成することができる。界面層12は、少なくともSi原子及びO原子を含み、N原子は随意的なものである。したがって、界面層12は、SiO2、SiON、これらのシリケート、又はこれらの多層構造を含むことができる。幾つかの実施形態において、界面層12はSiO2を含み、他の実施形態において、界面層12はSiONを含む。界面層12は、約1原子百分率から約80原子百分率まで、典型的には約1原子百分率から約30原子百分率までのSiを含む。残りはO及び/又はNである。Siは、界面層12の全体にわたって恒常的に存在することができ、又はSiを勾配付けすることができる。

【0022】

界面層12は、典型的には、約4.0から約20までの誘電率を有し、約4.5から約18までの誘電率がさらにより典型的である。界面層12は、典型的には、約0.1nmから約5nmまでの厚さを有し、約0.2nmから約2.5nmまでの厚さがより典型的である。

【0023】

次に、図1(B)に示されるように、高k誘電体14が、界面層12の表面上に形成される。「高k」という用語は、誘電率が、4.0より大きい、典型的には約7.0又はそれより大きい絶縁体を示す。高k誘電体14は、例えば、酸化、窒化、又は酸窒化のような熱成長プロセスによって形成することができる。代替的には、高k誘電体14は、例えば、化学気相堆積(CVD)、プラズマ強化CVD、金属・有機化学気相堆積(MOCVD)、原子層堆積(ALD)、蒸着、反応性スパッタリング、化学溶液堆積及び他の同様の堆積プロセスのような堆積プロセスによって形成することができる。誘電体14はまた、上記プロセスのいずれかの組み合わせを用いて形成することもできる。

【0024】

例証として、本発明に用いられる高k誘電体14は、これらに限られないが、酸化物、窒化物、酸窒化物、及び/又はシリケート(金属シリケート及び窒化金属シリケートを含む)を含む。1つの実施形態においては、高k誘電体14は、例えば、HfO2、ZrO2、Al2O3、TiO2、La2O3、SrTiO3、LaAlO3、Y2O3、Ga2O3、GdGaO及びこれらの混合物のような酸化物からなることが好ましい。高k誘電体14の非常に好ましい例は、HfO2、ハフニウム・シリケート、又は酸窒化ハフニウム・シリコンを含む。

【0025】

高k誘電体14の物理的厚さは変わり得るが、典型的には、高k誘電体14は、約0.5nmから約10nmまでの厚さを有し、約0.5nmから約3nmまでの厚さがより典型的である。

【0026】

図1(B)に示されるスタック構造体を提供した後、次に、HfSiN金属化合物層16が、高k誘電体14の上に形成され、例えば図1(C)に示される構造体を提供する。本発明によると、HfSiN金属化合物層16は、Hfターゲットと、He中で希釈されたAr/N2/Si源を含む雰囲気とを準備し、次いで、該雰囲気中でHfターゲットからHfSiN膜をスパッタリングすることによって形成される。スパッタリング・プロセスは、任意の従来のスパッタリング装置の反応炉のチャンバ内で行われる。上述のように、Heは、Si源を希釈するために用いられる。一般に、Si源を希釈するために用いられるHeの量は、約70%から約99%までであり、約95%から約99%までのHeの量がさらにより典型的である。幾つかの実施形態においては、Si源は、98%のHeを含む。

【0027】

本発明に用いられるHfターゲットは、いずれかのHf固体源を含む。HfSiN膜のスパッタリングの際に雰囲気中で用いられるシリコン(Si)源は、例えば、SiH4−nRnを含む、任意の有機含有Si化合物を含み、ここで、nは、0、1、2、3、又は4であり、Rは、1から約18までの炭素原子、好ましくは約1から約8までの炭素原子を含む脂肪族部分(即ち、アルカン、アルケン、アルキン、又はこれらの組み合わせ)である。脂肪族部分は、直鎖型又は分枝型とすることができる。nは0であり、Si源はSiH4であることが好ましい。Si源は、固体、液体、又は気体とすることができ、ガス状のSi源が非常に好ましい。

【0028】

本発明に用いられるAr/N2/Si源の流量比は、それぞれ、約1−100/1−100/1−100sccmであり、約10−20/5−15/10−30sccmの流量比がさらにより典型的である。幾つかの好ましい実施形態においては、それぞれ約5−50/5−50/5−50sccmのAr/N2/Si源の流量比を用いることができる。

【0029】

温度、圧力及び時間のような他のスパッタリング条件は、通常のものであり、当業者には公知である。

【0030】

上述のように、HfSiN膜の抵抗率は、プロセス・ガスの濃度によって決まり、窒素濃度及び/又はSi濃度が高いほど、HfSiN膜16の抵抗率が高くなる。典型的には、HfSiN膜の抵抗率は、約105マイクロ・オーム/cm又はそれより小さく、約100マイクロ・オーム/cmから約130マイクロ・オーム/cmまでの抵抗率がさらにより典型的である。

【0031】

形成されるHfSiN膜16の厚さは、用いられるスパッタリング条件及び製造されるデバイスのタイプによって変わり得る。典型的には、HfSiN膜16は、スパッタリング後、約2nmからから約200nmまでの厚さを有し、約5nmから約40nmまでの厚さがさらにより典型的である。

【0032】

次いで、図1(C)に示される構造体を、任意の従来のCMOS処理の流れを用いて、例えばFETなどのCMOSデバイス内に形成することができる。幾つかの実施形態において、図1(C)に示されるスタック構造体は、そのままで処理することができ、又は代替的に、HfSiN層16の上に、Si含有ゲート材料18を形成することができる。後者の実施形態が、図2(A)−図2(D)に示される。図2(A)−図2(D)は、Si含有材料18の存在を示すが、一般に、Si含有材料が形成されないときも、次の処理ステップはうまく働く。一般に、HfSiN層16だけを含むパターン形成されたゲート領域20は、後でシリサイド化されないことに留意されたい。

【0033】

図2(A)に示される実施形態において、ポリシリコン、SiGe及びSiGeCのようなSi含有材料18が、HfSiN層16の上に形成される。したがって、この実施形態において、Si含有材料18及びHfSiN層16は、多層のゲートを形成する。別の実施形態において、HfSiNは、単一の金属ゲートとして用いられる。用いられるSi含有材料18は、単結晶、多結晶又はアモルファスのいずれかの形であるか、或いはそうした形の混合物からなる。

【0034】

Si含有材料は、典型的には、その場堆積プロセスを用いて、又は堆積、イオン注入及びアニールによってドープされる。HfSiNはn型金属であるので、ドーパントは、n型ドーパントである。本発明のこの時点で形成されたSi含有材料18の厚さ、即ち高さは、用いられるプロセスによって変わり得る。典型的には、Si含有材料は、約20nmから約180nmまでの垂直方向厚さを有し、約40nmから約150nmまでの厚さがより典型的である。

【0035】

示される処理の実施形態においては、次に、Si含有材料18、HfSiN層16及び随意的な高k誘電体14、並びに界面層12が、リソグラフィ及びエッチングによってパターン形成され、パターン形成されたゲート領域又はスタック20を形成する。単一のパターン形成されたゲート領域(又はスタック)20が示されているが、本発明は、複数のパターン形成されたゲート領域(又はスタック)20の形成も考慮する。複数のパターン形成されたゲート領域(又はスタック)が形成されるとき、ゲート領域(又はスタック)は、同じ寸法、即ち長さを有してもよく、又はデバイス性能を向上させるために可変の寸法を有することもできる。本発明のこの時点でのパターン形成されたゲート・スタック(又は領域)20の各々は、少なくともパターン形成されたHfSiN層16を含む。図2(B)は、パターン形成されたゲート領域(又はスタック)20を形成した後の構造体を示す。示される実施形態においては、本発明のこのステップ中に、Si含有材料18、HfSiN層16、高k誘電体14及び界面層12が、エッチングされる、即ちパターン形成される。

【0036】

リソグラフィ・ステップは、図2(A)又は図1(C)のいずれかに示されるブランケット層状構造体の上面に、フォトレジストを適用するステップと、フォトレジストを所望の放射パターンに露光させるステップと、従来のレジスト現像液を用いて、露光されたフォトレジストを現像するステップとを含む。次に、1つ又は複数の乾式エッチング・ステップを用いて、フォトレジストのパターンが、構造体に転写される。幾つかの実施形態においては、ブランケット層状構造体の層の1つにパターンが転写された後、パターン形成されたフォトレジストを除去することができる。他の実施形態においては、エッチングが完了した後、パターン形成されたフォトレジストが除去される。

【0037】

パターン形成されたゲート領域(又はスタック)20を形成する際に本発明に用いることができる適切な乾式エッチング・プロセスは、これらに限られないが、反応性イオン・エッチング、イオン・ビーム・エッチング、プラズマ・エッチング、又はレーザ・アブレーションを含む。用いられる乾式エッチング・プロセスは、一般に、必ずしもというわけではないが、下にある高k誘電体14に対して選択的であり、よって、こうしたエッチング・ステップは、一般に、高k誘電体14及び界面層12を含むスタックを除去するものではない。しかしながら、幾つかの実施形態においては、図2(B)に示されるように、こうしたエッチング・ステップを用いて、前にエッチングされたゲート領域(又はスタック)の材料層によって保護されていない、高k誘電体14及び界面層12の一部を除去することができる。

【0038】

次に、少なくとも1つのスペーサ22が、一般的に、必ずしもというわけではないが、パターン形成されたゲート領域(又はスタック)20の各々の露出された側壁上に形成される。例えば、図2(C)を参照されたい。少なくとも1つのスペーサ22は、酸化物、窒化物、酸窒化物、及び/又はこれらの任意の組み合わせのような絶縁体からなる。少なくとも1つのスペーサ22は、堆積及びエッチングによって形成される。

【0039】

少なくとも1つのスペーサ22の幅は、ソース及びドレインのシリサイド・コンタクト(後に形成される)がゲート領域(又はスタック)20の縁部の下に侵入しないように、十分に広いものでなければならない。典型的には、少なくとも1つのスペーサ22が、約20nmから約80nmまでの底部で測定された幅を有するとき、ソース/ドレイン・シリサイドは、ゲート領域(又はスタック)20の縁部の下に侵入しない。

【0040】

ゲート領域(又はスタック)20は、スペーサを形成する前に、これに熱酸化、窒化、又は酸窒化処理を施すことによって非活性化することもできる。非活性化ステップは、ゲート領域(又はスタック)20の周りに非活性化材料の薄層(図示せず)を形成する。このステップは、前のスペーサ形成ステップの代わりに、又はそれと併せて用いることができる。スペーサ形成ステップと共に用いられるとき、ゲート領域(又はスタック)20非活性化プロセスの後に、スペーサ形成が行われる。

【0041】

次いで、ソース/ドレイン拡散領域24(スペーサの存在の有無にかかわらず)が、基板内に形成される。ソース/ドレイン拡散領域24は、イオン注入及びアニール・ステップを用いて形成される。アニール・ステップは、前の注入ステップによって注入されたドーパントを活性化させるように働く。イオン注入及びアニールのための条件は、当業者には公知である。イオン注入及びアニールの後に形成される構造体が、図2(D)に表される。

【0042】

ソース/ドレイン拡散領域24は、従来の延長注入を用いてソース/ドレイン注入を行う前に形成された延長注入領域(別個に表記されていない)を含むこともできる。延長注入に続いて、活性化アニールを行うか、又は代替的に延長注入中にドーパントを注入することができ、同じ活性化アニール・サイクルを用いて、ソース/ドレイン注入を活性化させることができる。ここでは、ハロ注入(図示せず)も考慮される。ソース/ドレイン延長部は、一般に、深いソース/ドレイン領域より浅く、パターン形成されたゲート領域(又はスタック)20の縁部と整合された縁部を含む。

【0043】

次に、前に除去されなかった場合には、これらの絶縁材料を選択的に除去する化学エッチング・プロセスを用いて、高k誘電体14及び下にある界面層12の露出された部分が除去される。このエッチング・ステップは、半導体基板10の上面で停止する。高k誘電体14及び下にある界面層12の露出された部分を除去する際に、いずれかの化学エッチング液を用いることができるが、1つの実施形態においては、希フッ化水素酸(dilute hydrofluoric aid、DHF)が用いられる。

【0044】

図2(D)は、ソース/ドレイン拡散領域24、及び(存在する場合には)Si含有材料の上のシリサイド領域26の存在も示す。Si含有材料18の上のシリサイドは、随意的なものであり、ゲート領域(又はスタック)20の上にSi含有材料が存在しない場合には形成されない。シリサイド領域26は、任意の従来のシリサイド化プロセスを用いて形成される。幾つかの実施形態において、Si含有材料が少なくともソース/ドレイン領域24上に存在しないとき、シリサイド化の前に、エピタキシャルSi又はアモルファスSiのようなSi含有材料を形成することができる。

【0045】

シリサイド化プロセスは、シリサイド化される領域の上に、C、Ge、Si等のような他の合金化添加剤を用いて、Co、Ti、W、Ni、Pt、又はこれらの合金のような、導電性の高融点金属を形成するステップを含む。CVD、PECVD、スパッタリング、蒸着、又はめっきのような従来の堆積プロセスを用いることができる。随意的に、金属の酸化を防ぐ金属層の上に、障壁層を形成することができる。随意的な障壁層の例は、例えば、SiN、TiN、TaN、TiON及びこれらの組み合わせを含む。金属の堆積に続いて、堆積された金属とSiの間に反応を引き起こし、続いて金属シリサイドを形成させる少なくとも第1のアニールが、構造体に施される。アニールは、典型的には、約250°から約800℃までの温度で行われ、約400°から約550℃までの第1のアニール温度がより典型的である。

【0046】

幾つかの実施形態においては、第1のアニールは、選択的エッチング・プロセスに対して大きく耐性がある金属リッチなシリサイド相を形成する。金属リッチ相が生成されると、低抵抗率のシリサイドを形成するために、第2の高温アニールが必要とされる。他の実施形態においては、第1のアニールは、低抵抗率のシリサイドを形成するのに十分なものである。

【0047】

第1のアニールに続いて、堆積された金属の未反応の残りの部分が、湿式エッチング、反応性イオン・エッチング(RIE)、イオン・ビーム・エッチング、又はプラズマ・エッチングのような従来のエッチング・プロセスを用いて除去される。

【0048】

必要な場合には、エッチング・プロセスの後に、第2のアニールが行われる。第2のアニールは、一般に、第1のアニールにより高温で行われる。随意的な第2のアニールについての典型的な温度範囲は、約550°から約900℃までである。

【0049】

金属相互接続部を用いるBEOL(back-end-of-line)相互接続レベルの形成のような、さらなるCMOS処理を、当業者には公知の処理ステップを用いて形成することができる。

【0050】

以下の例は、本発明のプロセスの説明、及びHfSiN含有ゲート・スタックを形成する際に本発明のプロセスを使用することから得ることができる幾つかの利点を提供する。

【実施例】

【0051】

この例において、HfSiN/HfO2/SiO2スタックが、Siウェハの表面上に形成された。SiO2界面層が、Siウェハの酸化によって形成された。SiO2界面層の厚さは、約1nmであった。次に、ALDによって、約3nmの厚さを有するHfO2誘電体が、SiO2界面層上に形成された。次に、Hfターゲットと、Ar:N2:SiH4(He中に2%)の流量比がそれぞれ20:10:20sccmである、Ar:N2:SiH4(He中に2%)を含む雰囲気とを準備することによって、HfSiN層が形成された。HfSiN層は、約40nmの厚さを有していた。スタックを形成した後、スタックに、1000℃のアニールを行い、続いて450℃で行われる形成ガス・アニールを行った。比較のために、類似したHfO2/SiO2スタックの周りに、TaSiN金属化合物が形成された。図3は、n−基板上のこれらのスタックの、10kHzにおけるCV特性を示す。HfSiNを含むスタックについての仕事関数は、nMOSデバイスについて一般的である約4.3eVであり、TaSiN含有スタックは、約4.7eV(ミッド・ギャップ)の仕事関数を有していたことに留意されたい。仕事関数は、非特許文献2に従って算出された。また、HfSiNを含むスタックの等価酸化物厚は、約12Åにすぎなかったことに留意されたい。したがって、ゲート・スタック内に実装された高k誘電体のために、このスタックを用いて製造されたnFETは、実質的にゲート漏れが減少した約12Åの反転層厚で機能すべきである。現在のSio2技術は、ゲート漏れがずっと大きい約19Åの反転層厚を有する。

【0052】

図4は、p−基板上のHfSiN/HfO2/SiO2ゲート・スタックの300kHzで取られたCV特性をさらに示す。このゲート・スタックは、MOCVDによって堆積されたHfO2(3nm)を除いて、図3に示されるものと類似している。このスタックは、5秒間、N2中で1000℃で急速アニールされ、次いで、450℃で形成ガス雰囲気中でアニールされた。この場合、非特許文献2に従って算出された仕事関数は、約3.7eVである。このことは、HfSiNについてのn−FETの性質をさらに示す。

【0053】

本発明は、特にその好ましい実施形態に関して示され、説明されたが、当業者であれば、本発明の精神及び範囲から逸脱することなく、形態及び細部における上記の及び他の変更を行い得ることを理解するであろう。したがって、本発明は、説明され、示された正確な形態及び細部に限定されるものでなく、添付の特許請求の範囲に含まれることが意図されている。

【図面の簡単な説明】

【0054】

【図1】(A)高k誘電体及び界面層を含むスタック上にn型金属ゲートとしてHfSiN金属化合物を含む薄膜スタック構造体を形成するのに用いられる、種々の処理ステップを示す(断面図による)図形的な図である。 (B)高k誘電体及び界面層を含むスタック上にn型金属ゲートとしてHfSiN金属化合物を含む薄膜スタック構造体を形成するのに用いられる、種々の処理ステップを示す(断面図による)図形的な図である。 (C)高k誘電体及び界面層を含むスタック上にn型金属ゲートとしてHfSiN金属化合物を含む薄膜スタック構造体を形成するのに用いられる、種々の処理ステップを示す(断面図による)図形的な図である。

【図2】(A)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。 (B)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。 (C)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。 (D)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。

【図3】同じゲート・スタック(30ÅのHfO2/SiO2)上の、類似したプロセスにおける、TaSiNと比較したHfSiNの容量・電圧(CV、n−基板)特性を示す。TaSiN(ミッド・ギャップ)についての4.7eVと比較すると、HfSiNは、約4.3eVの仕事関数を有する(nFET)ことに留意されたい。

【図4】1000℃でアニールされ、次いで、形成ガス雰囲気中で450℃でアニールされた、HfO2/SiO2スタック上のHfSiNの容量・電圧(CV、p−基板)特性を示す。仕事関数は、約3.7eVである。

【技術分野】

【0001】

本発明は、半導体デバイス、及びこれを製造する方法に関する。より具体的には、本発明は、高誘電率k/界面層のスタック上の、熱的に安定したn型金属を含む相補型金属酸化膜半導体(CMOS)に関する。本発明はまた、CMOS処理の流れと統合することができる、熱的に安定したn型金属を形成するプロセスも提供する。

【背景技術】

【0002】

標準的なCMOSデバイスにおいては、一般に、ポリシリコンが、標準的なゲート材料である。ポリシリコン・ゲートを用いてCMOSデバイスを製造する技術は、絶えず発展した状態にあり、現在、半導体産業において広く用いられている。ポリシリコン・ゲートを用いる1つの利点は、これらが高温に耐え得ることである。しかしながら、ポリシリコン・ゲートの使用と関連した幾つかの問題もある。例えば、ポリ空乏効果及び相対的に高い電気シート抵抗(約150オーム/スクェア)のために、CMOSデバイスにおいて一般的に使用されるポリSiゲートは、0.1ミクロン以下のチャネル長についての、チップ性能のゲート要因になりつつある。ポリSiゲートに関連する別の問題は、ボロンのようなポリSiゲート内のドーパントが、薄いゲート誘電体を通って容易に拡散し、デバイス性能をさらに低下させ得ることである。

【0003】

ポリSiゲートに関連した問題を回避するために、ポリSiゲートを単一の金属と置き換えることが提案された。高k誘電体を用いるCMOS技術のために、異なる仕事関数(pFETについての仕事関数とnFETについての仕事関数)を有する金属が必要とされる。金属/高k誘電体スタックに、ソース/ドレインの自己整合された注入の活性化のために必要とされる(約1000℃のオーダーの)高温アニールを施す必要がある。ゲート・スタックの反応は、材料の選択を制限するこの高温アニール中に生じる。例えば、W及び高k誘電体を含むゲート・スタックにおいて、SiO2の再成長は、反転層のスケーラビリティを制限する界面で行われる。例えば、非特許文献1を参照されたい。

【0004】

金属化合物は、より安定したものにしてもよいが、依然として適切な仕事関数を目標とすることに関する問題がある。例えば、nFETの候補としてTaSiNが提案されたが、依然としてその仕事関数に関する幾つかの問題が存在し、nFETデバイスにおいて移動度の減少が観察される。さらに、TaSiNを用いると、反転層厚のスケーラビリティが幾分制限されるように見える。

【0005】

【非特許文献1】A.Callegari他、IEDM2004、p.825、S.Francisco Ca.,2004年12月13日―15日

【非特許文献2】S.M.Sze、Physics of Semiconductor Devaices、第2版、395−397ページ、J.Wiley&Sons

【発明の開示】

【発明が解決しようとする課題】

【0006】

上記を鑑みて、高k誘電体を含むゲート・スタック上に熱的に安定した新しい金属化合物を提供する必要性がある。特定的には、nFETデバイスにおいて有用な新しい金属化合物を提供する必要性がある。

【課題を解決するための手段】

【0007】

本発明は、高k誘電体及び界面層を含むゲート・スタック上に、約3.7eVから約4.5eVまで、好ましくは約4.0eVの仕事関数を有する、熱的に安定したn型金属であるHfSiNを含む新しい金属化合物を提供するものである。さらに、(約1000℃のオーダーの)高温で、HfSiN/高k誘電体/界面層のスタックをアニールした後、界面層が減少され、よって、ゲート・スタックは、TaSiNを用いて達成することができない、非常に薄い等価の酸化物厚(伝統的には、12Å)をもたらす。

【0008】

大まかに言うと、本発明は、

半導体基板と、

半導体基板上に配置された界面層と、

界面層上に配置された高k誘電体と、

高k誘電体上に配置されたHfSiNゲート金属と

を含む、半導体構造体、即ち薄膜スタックを提供する。

【0009】

さらに、本発明は、

半導体基板と、

少なくとも、基板の一部に配置された界面層、界面層上に配置された高k誘電体及び高ゲート誘電体上に配置されたHfSiN金属を含む、パターン形成されたゲート領域と

を含む、半導体構造体を提供する。

【0010】

上述の薄膜スタック及び半導体構造体に加えて、本発明は、

Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを準備するステップと、

前述の雰囲気中でHfターゲットからHfSiN膜をスパッタリングするステップと

を含む、HfSiN金属化合物を製造する方法も提供する。

【0011】

本発明によると、Si源の活性度を制限する、Heで希釈されたSi源は、膜の品質を向上させる。HfSiN膜の抵抗率は、プロセス・ガスの濃度によって変わり得る。一般的に、窒素濃度及び/又はSi濃度が高いほど、抵抗率が高くなる。

【0012】

本発明はまた、HfSiN膜を形成するために本発明のプロセスを用いる、上述の半導体構造体を製造する方法も提供する。一般論として、最初に、基板の表面上に高k誘電体及び界面層を含むスタックを提供し、その後、上述した処理ステップを用いてスタック上にHfSiN膜を形成することによって、即ち、Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを提供し、雰囲気中でHfターゲットからHfSiN膜をスパッタリングすることによって、半導体構造体が形成される。

【0013】

本発明の幾つかの実施形態においては、HfSiN金属ゲートは、ゲート電極として単独で、又はその上面にシリサイド・コンタクトを含むSi含有ゲート電極と併せて、用いることができる。後者の構造体は、ここでは、デュアル・ポリSi/HfSiN含有FETと呼ばれる。

【0014】

高k誘電体という用語は、本出願の全体を通じて、その誘電率kが、例えば4.0より大きいといった、SiO2よりも大きい絶縁体材料を示すように用いられることが留意される。高k誘電体は、約7.0又はそれより大きいkを有することが好ましい。

【0015】

「界面層」という用語は、本出願の全体を通じて、例えばSiO2及びSiONを含む、少なくともSi原子又はO原子を含む絶縁体材料を示すように用いられる。

【発明を実施するための最良の形態】

【0016】

ここで、高k誘電体及び界面層を含むスタック上の、熱的に安定したn−金属ゲートとして用い得るHfSiN金属化合物と、これを製造する方法とを提供する本発明が、本出願に添付される図面を参照することによって、より詳細に説明される。本発明の図面は、説明のために提供されるものであり、よって、これらの図面は縮尺通りに描かれていないことが留意される。

【0017】

最初に、高k誘電体及び界面層を含むスタック上に本発明のHfSiN金属化合物を含む薄膜スタック構造体を形成する際に用いられる基本的な処理ステップを示す、図1(A)−図1(C)を参照する。図1(A)は、半導体基板10の表面上に界面層12を含む、最初の薄膜スタック構造体を示す。

【0018】

本発明に用いられる半導体基板10は、これらに限られないが、Si、Ge、SiGe、SiC、SiGeC、Ga、GaAs、InAs、InP及び他の全てのIV/IV族、III/V族又はII/VI族化合物半導体を含む、いずれかの半導体材料からなる。半導体基板10はまた、有機半導体、或いはSi/SiGe、シリコン・オン・インシュレータ(silicon-on-insulator、SOI)、又はSiGeオン・インシュレータ(SiGe-on-insulator、SGOI)などの層状半導体を含むこともできる。本発明の幾つかの実施形態においては、半導体基板10が、Si含有半導体材料、即ちシリコンを含む半導体材料からなることが好ましい。半導体基板10は、ドープされたものであってもよく、ドープされていないものであってもよく、或いは内部にドープ領域と非ドープ領域とを含むものであってもよい。

【0019】

半導体基板10はまた、第1のドープ(n−又はp−)領域及び第2のドープ(n−又はp−)領域を含むこともできる。明確にするために、本出願の図面中にドープ領域は具体的に示されていない。第1のドープ領域及び第2のドープ領域は、同じものであってもよく、又はそれらが異なる導電率及び/又はドーピング濃度を有するものであってもよい。これらのドープ領域は、「ウェル」として知られている。半導体基板10は、歪ませてもよく、歪ませなくてもよく、或いは、各々が内部に歪み領域と非歪み領域とを含んでもよい。さらに、半導体基板10は、例えば、100、110、111、又はこれらの組み合わせを含む、任意の結晶配向を有することができる。代替的に、半導体基板10は、異なる結晶配向の少なくとも2つの平坦な面を含むハイブリッド基板とすることができる。

【0020】

次いで、少なくとも1つの分離領域(図示せず)が、一般的には、半導体基板10内に形成される。分離領域は、トレンチ分離領域又はフィールド酸化物分離領域とすることができる。トレンチ分離領域は、当業者に公知の従来のトレンチ分離プロセスを用いて形成される。例えば、トレンチ分離領域を形成するのに、リソグラフィ、エッチング、及びトレンチ誘電体によるトレンチの充填を用いることができる。随意的に、トレンチの充填前に、トレンチ内にライナを形成することができ、トレンチの充填後に緻密化ステップを行うことができ、トレンチの充填に続いて平坦化プロセスを行うこともできる。フィールド酸化物は、いわゆる局所的なシリコン酸化プロセスを用いて形成することができる。少なくとも1つの分離領域が、典型的には、隣接するゲートが反対の導電性をもつときに必要とされる分離を、隣接するゲート領域間に与えることに留意されたい。隣接するゲート領域は、同じ導電性(即ち、両方がn型又はp型)をもつことができ、又は代替的に、それらが異なる導電性(即ち、一方がn型で他方がp型)をもつこともできる。

【0021】

次いで、界面層12が、酸化又は酸窒化のような熱プロセス、化学気相堆積(CVD)、プラズマ強化CVD、原子層堆積(ALD)、蒸着、スパッタリング及び化学溶液堆積、又はこれらの組み合わせのような堆積プロセスを用いて、半導体基板10の表面の上に形成される。代替的に、堆積プロセス及び窒化を用いて、界面層12を形成することができる。界面層12は、少なくともSi原子及びO原子を含み、N原子は随意的なものである。したがって、界面層12は、SiO2、SiON、これらのシリケート、又はこれらの多層構造を含むことができる。幾つかの実施形態において、界面層12はSiO2を含み、他の実施形態において、界面層12はSiONを含む。界面層12は、約1原子百分率から約80原子百分率まで、典型的には約1原子百分率から約30原子百分率までのSiを含む。残りはO及び/又はNである。Siは、界面層12の全体にわたって恒常的に存在することができ、又はSiを勾配付けすることができる。

【0022】

界面層12は、典型的には、約4.0から約20までの誘電率を有し、約4.5から約18までの誘電率がさらにより典型的である。界面層12は、典型的には、約0.1nmから約5nmまでの厚さを有し、約0.2nmから約2.5nmまでの厚さがより典型的である。

【0023】

次に、図1(B)に示されるように、高k誘電体14が、界面層12の表面上に形成される。「高k」という用語は、誘電率が、4.0より大きい、典型的には約7.0又はそれより大きい絶縁体を示す。高k誘電体14は、例えば、酸化、窒化、又は酸窒化のような熱成長プロセスによって形成することができる。代替的には、高k誘電体14は、例えば、化学気相堆積(CVD)、プラズマ強化CVD、金属・有機化学気相堆積(MOCVD)、原子層堆積(ALD)、蒸着、反応性スパッタリング、化学溶液堆積及び他の同様の堆積プロセスのような堆積プロセスによって形成することができる。誘電体14はまた、上記プロセスのいずれかの組み合わせを用いて形成することもできる。

【0024】

例証として、本発明に用いられる高k誘電体14は、これらに限られないが、酸化物、窒化物、酸窒化物、及び/又はシリケート(金属シリケート及び窒化金属シリケートを含む)を含む。1つの実施形態においては、高k誘電体14は、例えば、HfO2、ZrO2、Al2O3、TiO2、La2O3、SrTiO3、LaAlO3、Y2O3、Ga2O3、GdGaO及びこれらの混合物のような酸化物からなることが好ましい。高k誘電体14の非常に好ましい例は、HfO2、ハフニウム・シリケート、又は酸窒化ハフニウム・シリコンを含む。

【0025】

高k誘電体14の物理的厚さは変わり得るが、典型的には、高k誘電体14は、約0.5nmから約10nmまでの厚さを有し、約0.5nmから約3nmまでの厚さがより典型的である。

【0026】

図1(B)に示されるスタック構造体を提供した後、次に、HfSiN金属化合物層16が、高k誘電体14の上に形成され、例えば図1(C)に示される構造体を提供する。本発明によると、HfSiN金属化合物層16は、Hfターゲットと、He中で希釈されたAr/N2/Si源を含む雰囲気とを準備し、次いで、該雰囲気中でHfターゲットからHfSiN膜をスパッタリングすることによって形成される。スパッタリング・プロセスは、任意の従来のスパッタリング装置の反応炉のチャンバ内で行われる。上述のように、Heは、Si源を希釈するために用いられる。一般に、Si源を希釈するために用いられるHeの量は、約70%から約99%までであり、約95%から約99%までのHeの量がさらにより典型的である。幾つかの実施形態においては、Si源は、98%のHeを含む。

【0027】

本発明に用いられるHfターゲットは、いずれかのHf固体源を含む。HfSiN膜のスパッタリングの際に雰囲気中で用いられるシリコン(Si)源は、例えば、SiH4−nRnを含む、任意の有機含有Si化合物を含み、ここで、nは、0、1、2、3、又は4であり、Rは、1から約18までの炭素原子、好ましくは約1から約8までの炭素原子を含む脂肪族部分(即ち、アルカン、アルケン、アルキン、又はこれらの組み合わせ)である。脂肪族部分は、直鎖型又は分枝型とすることができる。nは0であり、Si源はSiH4であることが好ましい。Si源は、固体、液体、又は気体とすることができ、ガス状のSi源が非常に好ましい。

【0028】

本発明に用いられるAr/N2/Si源の流量比は、それぞれ、約1−100/1−100/1−100sccmであり、約10−20/5−15/10−30sccmの流量比がさらにより典型的である。幾つかの好ましい実施形態においては、それぞれ約5−50/5−50/5−50sccmのAr/N2/Si源の流量比を用いることができる。

【0029】

温度、圧力及び時間のような他のスパッタリング条件は、通常のものであり、当業者には公知である。

【0030】

上述のように、HfSiN膜の抵抗率は、プロセス・ガスの濃度によって決まり、窒素濃度及び/又はSi濃度が高いほど、HfSiN膜16の抵抗率が高くなる。典型的には、HfSiN膜の抵抗率は、約105マイクロ・オーム/cm又はそれより小さく、約100マイクロ・オーム/cmから約130マイクロ・オーム/cmまでの抵抗率がさらにより典型的である。

【0031】

形成されるHfSiN膜16の厚さは、用いられるスパッタリング条件及び製造されるデバイスのタイプによって変わり得る。典型的には、HfSiN膜16は、スパッタリング後、約2nmからから約200nmまでの厚さを有し、約5nmから約40nmまでの厚さがさらにより典型的である。

【0032】

次いで、図1(C)に示される構造体を、任意の従来のCMOS処理の流れを用いて、例えばFETなどのCMOSデバイス内に形成することができる。幾つかの実施形態において、図1(C)に示されるスタック構造体は、そのままで処理することができ、又は代替的に、HfSiN層16の上に、Si含有ゲート材料18を形成することができる。後者の実施形態が、図2(A)−図2(D)に示される。図2(A)−図2(D)は、Si含有材料18の存在を示すが、一般に、Si含有材料が形成されないときも、次の処理ステップはうまく働く。一般に、HfSiN層16だけを含むパターン形成されたゲート領域20は、後でシリサイド化されないことに留意されたい。

【0033】

図2(A)に示される実施形態において、ポリシリコン、SiGe及びSiGeCのようなSi含有材料18が、HfSiN層16の上に形成される。したがって、この実施形態において、Si含有材料18及びHfSiN層16は、多層のゲートを形成する。別の実施形態において、HfSiNは、単一の金属ゲートとして用いられる。用いられるSi含有材料18は、単結晶、多結晶又はアモルファスのいずれかの形であるか、或いはそうした形の混合物からなる。

【0034】

Si含有材料は、典型的には、その場堆積プロセスを用いて、又は堆積、イオン注入及びアニールによってドープされる。HfSiNはn型金属であるので、ドーパントは、n型ドーパントである。本発明のこの時点で形成されたSi含有材料18の厚さ、即ち高さは、用いられるプロセスによって変わり得る。典型的には、Si含有材料は、約20nmから約180nmまでの垂直方向厚さを有し、約40nmから約150nmまでの厚さがより典型的である。

【0035】

示される処理の実施形態においては、次に、Si含有材料18、HfSiN層16及び随意的な高k誘電体14、並びに界面層12が、リソグラフィ及びエッチングによってパターン形成され、パターン形成されたゲート領域又はスタック20を形成する。単一のパターン形成されたゲート領域(又はスタック)20が示されているが、本発明は、複数のパターン形成されたゲート領域(又はスタック)20の形成も考慮する。複数のパターン形成されたゲート領域(又はスタック)が形成されるとき、ゲート領域(又はスタック)は、同じ寸法、即ち長さを有してもよく、又はデバイス性能を向上させるために可変の寸法を有することもできる。本発明のこの時点でのパターン形成されたゲート・スタック(又は領域)20の各々は、少なくともパターン形成されたHfSiN層16を含む。図2(B)は、パターン形成されたゲート領域(又はスタック)20を形成した後の構造体を示す。示される実施形態においては、本発明のこのステップ中に、Si含有材料18、HfSiN層16、高k誘電体14及び界面層12が、エッチングされる、即ちパターン形成される。

【0036】

リソグラフィ・ステップは、図2(A)又は図1(C)のいずれかに示されるブランケット層状構造体の上面に、フォトレジストを適用するステップと、フォトレジストを所望の放射パターンに露光させるステップと、従来のレジスト現像液を用いて、露光されたフォトレジストを現像するステップとを含む。次に、1つ又は複数の乾式エッチング・ステップを用いて、フォトレジストのパターンが、構造体に転写される。幾つかの実施形態においては、ブランケット層状構造体の層の1つにパターンが転写された後、パターン形成されたフォトレジストを除去することができる。他の実施形態においては、エッチングが完了した後、パターン形成されたフォトレジストが除去される。

【0037】

パターン形成されたゲート領域(又はスタック)20を形成する際に本発明に用いることができる適切な乾式エッチング・プロセスは、これらに限られないが、反応性イオン・エッチング、イオン・ビーム・エッチング、プラズマ・エッチング、又はレーザ・アブレーションを含む。用いられる乾式エッチング・プロセスは、一般に、必ずしもというわけではないが、下にある高k誘電体14に対して選択的であり、よって、こうしたエッチング・ステップは、一般に、高k誘電体14及び界面層12を含むスタックを除去するものではない。しかしながら、幾つかの実施形態においては、図2(B)に示されるように、こうしたエッチング・ステップを用いて、前にエッチングされたゲート領域(又はスタック)の材料層によって保護されていない、高k誘電体14及び界面層12の一部を除去することができる。

【0038】

次に、少なくとも1つのスペーサ22が、一般的に、必ずしもというわけではないが、パターン形成されたゲート領域(又はスタック)20の各々の露出された側壁上に形成される。例えば、図2(C)を参照されたい。少なくとも1つのスペーサ22は、酸化物、窒化物、酸窒化物、及び/又はこれらの任意の組み合わせのような絶縁体からなる。少なくとも1つのスペーサ22は、堆積及びエッチングによって形成される。

【0039】

少なくとも1つのスペーサ22の幅は、ソース及びドレインのシリサイド・コンタクト(後に形成される)がゲート領域(又はスタック)20の縁部の下に侵入しないように、十分に広いものでなければならない。典型的には、少なくとも1つのスペーサ22が、約20nmから約80nmまでの底部で測定された幅を有するとき、ソース/ドレイン・シリサイドは、ゲート領域(又はスタック)20の縁部の下に侵入しない。

【0040】

ゲート領域(又はスタック)20は、スペーサを形成する前に、これに熱酸化、窒化、又は酸窒化処理を施すことによって非活性化することもできる。非活性化ステップは、ゲート領域(又はスタック)20の周りに非活性化材料の薄層(図示せず)を形成する。このステップは、前のスペーサ形成ステップの代わりに、又はそれと併せて用いることができる。スペーサ形成ステップと共に用いられるとき、ゲート領域(又はスタック)20非活性化プロセスの後に、スペーサ形成が行われる。

【0041】

次いで、ソース/ドレイン拡散領域24(スペーサの存在の有無にかかわらず)が、基板内に形成される。ソース/ドレイン拡散領域24は、イオン注入及びアニール・ステップを用いて形成される。アニール・ステップは、前の注入ステップによって注入されたドーパントを活性化させるように働く。イオン注入及びアニールのための条件は、当業者には公知である。イオン注入及びアニールの後に形成される構造体が、図2(D)に表される。

【0042】

ソース/ドレイン拡散領域24は、従来の延長注入を用いてソース/ドレイン注入を行う前に形成された延長注入領域(別個に表記されていない)を含むこともできる。延長注入に続いて、活性化アニールを行うか、又は代替的に延長注入中にドーパントを注入することができ、同じ活性化アニール・サイクルを用いて、ソース/ドレイン注入を活性化させることができる。ここでは、ハロ注入(図示せず)も考慮される。ソース/ドレイン延長部は、一般に、深いソース/ドレイン領域より浅く、パターン形成されたゲート領域(又はスタック)20の縁部と整合された縁部を含む。

【0043】

次に、前に除去されなかった場合には、これらの絶縁材料を選択的に除去する化学エッチング・プロセスを用いて、高k誘電体14及び下にある界面層12の露出された部分が除去される。このエッチング・ステップは、半導体基板10の上面で停止する。高k誘電体14及び下にある界面層12の露出された部分を除去する際に、いずれかの化学エッチング液を用いることができるが、1つの実施形態においては、希フッ化水素酸(dilute hydrofluoric aid、DHF)が用いられる。

【0044】

図2(D)は、ソース/ドレイン拡散領域24、及び(存在する場合には)Si含有材料の上のシリサイド領域26の存在も示す。Si含有材料18の上のシリサイドは、随意的なものであり、ゲート領域(又はスタック)20の上にSi含有材料が存在しない場合には形成されない。シリサイド領域26は、任意の従来のシリサイド化プロセスを用いて形成される。幾つかの実施形態において、Si含有材料が少なくともソース/ドレイン領域24上に存在しないとき、シリサイド化の前に、エピタキシャルSi又はアモルファスSiのようなSi含有材料を形成することができる。

【0045】

シリサイド化プロセスは、シリサイド化される領域の上に、C、Ge、Si等のような他の合金化添加剤を用いて、Co、Ti、W、Ni、Pt、又はこれらの合金のような、導電性の高融点金属を形成するステップを含む。CVD、PECVD、スパッタリング、蒸着、又はめっきのような従来の堆積プロセスを用いることができる。随意的に、金属の酸化を防ぐ金属層の上に、障壁層を形成することができる。随意的な障壁層の例は、例えば、SiN、TiN、TaN、TiON及びこれらの組み合わせを含む。金属の堆積に続いて、堆積された金属とSiの間に反応を引き起こし、続いて金属シリサイドを形成させる少なくとも第1のアニールが、構造体に施される。アニールは、典型的には、約250°から約800℃までの温度で行われ、約400°から約550℃までの第1のアニール温度がより典型的である。

【0046】

幾つかの実施形態においては、第1のアニールは、選択的エッチング・プロセスに対して大きく耐性がある金属リッチなシリサイド相を形成する。金属リッチ相が生成されると、低抵抗率のシリサイドを形成するために、第2の高温アニールが必要とされる。他の実施形態においては、第1のアニールは、低抵抗率のシリサイドを形成するのに十分なものである。

【0047】

第1のアニールに続いて、堆積された金属の未反応の残りの部分が、湿式エッチング、反応性イオン・エッチング(RIE)、イオン・ビーム・エッチング、又はプラズマ・エッチングのような従来のエッチング・プロセスを用いて除去される。

【0048】

必要な場合には、エッチング・プロセスの後に、第2のアニールが行われる。第2のアニールは、一般に、第1のアニールにより高温で行われる。随意的な第2のアニールについての典型的な温度範囲は、約550°から約900℃までである。

【0049】

金属相互接続部を用いるBEOL(back-end-of-line)相互接続レベルの形成のような、さらなるCMOS処理を、当業者には公知の処理ステップを用いて形成することができる。

【0050】

以下の例は、本発明のプロセスの説明、及びHfSiN含有ゲート・スタックを形成する際に本発明のプロセスを使用することから得ることができる幾つかの利点を提供する。

【実施例】

【0051】

この例において、HfSiN/HfO2/SiO2スタックが、Siウェハの表面上に形成された。SiO2界面層が、Siウェハの酸化によって形成された。SiO2界面層の厚さは、約1nmであった。次に、ALDによって、約3nmの厚さを有するHfO2誘電体が、SiO2界面層上に形成された。次に、Hfターゲットと、Ar:N2:SiH4(He中に2%)の流量比がそれぞれ20:10:20sccmである、Ar:N2:SiH4(He中に2%)を含む雰囲気とを準備することによって、HfSiN層が形成された。HfSiN層は、約40nmの厚さを有していた。スタックを形成した後、スタックに、1000℃のアニールを行い、続いて450℃で行われる形成ガス・アニールを行った。比較のために、類似したHfO2/SiO2スタックの周りに、TaSiN金属化合物が形成された。図3は、n−基板上のこれらのスタックの、10kHzにおけるCV特性を示す。HfSiNを含むスタックについての仕事関数は、nMOSデバイスについて一般的である約4.3eVであり、TaSiN含有スタックは、約4.7eV(ミッド・ギャップ)の仕事関数を有していたことに留意されたい。仕事関数は、非特許文献2に従って算出された。また、HfSiNを含むスタックの等価酸化物厚は、約12Åにすぎなかったことに留意されたい。したがって、ゲート・スタック内に実装された高k誘電体のために、このスタックを用いて製造されたnFETは、実質的にゲート漏れが減少した約12Åの反転層厚で機能すべきである。現在のSio2技術は、ゲート漏れがずっと大きい約19Åの反転層厚を有する。

【0052】

図4は、p−基板上のHfSiN/HfO2/SiO2ゲート・スタックの300kHzで取られたCV特性をさらに示す。このゲート・スタックは、MOCVDによって堆積されたHfO2(3nm)を除いて、図3に示されるものと類似している。このスタックは、5秒間、N2中で1000℃で急速アニールされ、次いで、450℃で形成ガス雰囲気中でアニールされた。この場合、非特許文献2に従って算出された仕事関数は、約3.7eVである。このことは、HfSiNについてのn−FETの性質をさらに示す。

【0053】

本発明は、特にその好ましい実施形態に関して示され、説明されたが、当業者であれば、本発明の精神及び範囲から逸脱することなく、形態及び細部における上記の及び他の変更を行い得ることを理解するであろう。したがって、本発明は、説明され、示された正確な形態及び細部に限定されるものでなく、添付の特許請求の範囲に含まれることが意図されている。

【図面の簡単な説明】

【0054】

【図1】(A)高k誘電体及び界面層を含むスタック上にn型金属ゲートとしてHfSiN金属化合物を含む薄膜スタック構造体を形成するのに用いられる、種々の処理ステップを示す(断面図による)図形的な図である。 (B)高k誘電体及び界面層を含むスタック上にn型金属ゲートとしてHfSiN金属化合物を含む薄膜スタック構造体を形成するのに用いられる、種々の処理ステップを示す(断面図による)図形的な図である。 (C)高k誘電体及び界面層を含むスタック上にn型金属ゲートとしてHfSiN金属化合物を含む薄膜スタック構造体を形成するのに用いられる、種々の処理ステップを示す(断面図による)図形的な図である。

【図2】(A)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。 (B)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。 (C)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。 (D)ポリSi/ゲート金属の自己整合されたFET構造体を形成するための、本発明の基本的な処理ステップを示す(断面図による)図形的な図である。

【図3】同じゲート・スタック(30ÅのHfO2/SiO2)上の、類似したプロセスにおける、TaSiNと比較したHfSiNの容量・電圧(CV、n−基板)特性を示す。TaSiN(ミッド・ギャップ)についての4.7eVと比較すると、HfSiNは、約4.3eVの仕事関数を有する(nFET)ことに留意されたい。

【図4】1000℃でアニールされ、次いで、形成ガス雰囲気中で450℃でアニールされた、HfO2/SiO2スタック上のHfSiNの容量・電圧(CV、p−基板)特性を示す。仕事関数は、約3.7eVである。

【特許請求の範囲】

【請求項1】

半導体構造体であって、

半導体基板と、

前記半導体基板上に配置された界面層と、

前記界面層上に配置された高k誘電体と、

前記高k誘電体上に配置されたHfSiNゲート金属と

を備える、半導体構造体。

【請求項2】

前記半導体基板が、Si、Ge、SiGe、SiC、SiGeC、Ga、GaAs、InAs、InP、他のII/IV族又はIII/VI族化合物半導体、有機半導体、或いは層状半導体の1つを含む、請求項1に記載の半導体構造体。

【請求項3】

前記半導体基板がSi含有半導体材料である、請求項2に記載の半導体構造体。

【請求項4】

前記界面層は、Si原子及びO原子、随意的にN原子を含む、請求項1に記載の半導体構造体。

【請求項5】

前記界面層は、SiO2、SiON、又はこれらのシリケートを含む、請求項4に記載の半導体構造体。

【請求項6】

前記界面層は、約4.0から約20までの誘電率と、約0.1nmから約5nmまでの厚さとを有する、請求項1に記載の半導体構造体。

【請求項7】

前記界面層は、約1原子百分率から約80原子百分率までのSi含有量を有する、請求項1に記載の半導体構造体。

【請求項8】

前記界面層は、勾配付けされているSi含有量を有する、請求項1に記載の半導体構造体。

【請求項9】

前記高k誘電体は、4.0より大きい誘電率と、約0.5nmから約10nmまでの厚さとを有する、請求項1に記載の半導体構造体。

【請求項10】

前記高k誘電体は、酸化物、窒化物、酸窒化物、シリケート、又はこれらの混合物を含む、請求項1に記載の半導体構造体。

【請求項11】

前記高k誘電体は、Hfベースの材料である、請求項1に記載の半導体構造体。

【請求項12】

前記界面層はSiO2又はSiONを含み、前記高k誘電体は、HfO2、Hfシリケート、又はHf酸窒化物を含む、請求項1に記載の半導体構造体。

【請求項13】

前記HfSiNは、4.0eVから4.5eVまでの間の仕事関数を有する、請求項1に記載の半導体構造体。

【請求項14】

前記HfSiN層の上にSi含有導電性材料をさらに含む、請求項1に記載の半導体構造体。

【請求項15】

前記界面層、前記高k誘電体及び前記HfSiNゲート金属が、ゲート領域内にパターン形成される、請求項1に記載の半導体構造体。

【請求項16】

HfSiN金属化合物を製造する方法であって、

Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを準備するステップと、

前記雰囲気中で前記HfターゲットからHfSiN膜をスパッタリングするステップと

を含む、方法。

【請求項17】

nが0、1、2、3、又は4であり、Rが1から約18までの炭素分子を含む脂肪部分である場合に、前記Si源は、式SiH4−nRnを有する、請求項16に記載の方法。

【請求項18】

nが0であり、前記Si源がSiH4である、請求項17に記載の方法。

【請求項19】

前記Si源は、固体、液体、又は気体である、請求項16に記載の方法。

【請求項20】

前記Si源は、約70%から約99%までのHeで希釈される、請求項16に記載の方法。

【請求項21】

前記Ar/N2/Si源は、それぞれ、約1−100/1−100/1−100sccmの流量比を有する、請求項16に記載の方法。

【請求項22】

半導体構造体を形成する方法であって、

基板の表面上に、高k誘電体及び界面層を含むスタックを準備するステップと、

前記スタック上にHfSiN膜を形成するステップと

を含み、前記HfSiN膜は、Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを準備し、前記雰囲気中で前記HfターゲットからHfSiN膜をスパッタリングすることによって形成される、方法。

【請求項23】

nが0、1、2、3、又は4であり、Rが1から約18までの炭素分子を含む脂肪部分である場合に、前記Si源は、式SiH4−nRnを有する、請求項22に記載の方法。

【請求項24】

nが0であり、前記Si源がSiH4である、請求項23に記載の方法。

【請求項25】

前記Si源が、固体、液体、又は気体である、請求項22に記載の方法。

【請求項26】

前記Si源は、約70%から約99%までのHeで希釈される、請求項22に記載の方法。

【請求項27】

前記Ar/N2/Si源は、それぞれ、約1−100/1−100/1−100sccmの流量比を有する、請求項22に記載の方法。

【請求項28】

前記HfSiN層の上にSi含有導電性材料を形成するステップをさらに含む、請求項22に記載の半導体構造体。

【請求項29】

パターン形成されたゲート領域内に、前記HfSiN膜と、前記高k誘電体及び前記界面層を含む前記スタックとをパターン形成するステップをさらに含む、請求項22に記載の方法。

【請求項30】

パターン形成されたゲート領域内に、前記Si含有導電性材料と、前記HfSiN膜と、前記高k誘電体及び前記界面層を含む前記スタックとをパターン形成するステップをさらに含む、請求項28に記載の方法。

【請求項1】

半導体構造体であって、

半導体基板と、

前記半導体基板上に配置された界面層と、

前記界面層上に配置された高k誘電体と、

前記高k誘電体上に配置されたHfSiNゲート金属と

を備える、半導体構造体。

【請求項2】

前記半導体基板が、Si、Ge、SiGe、SiC、SiGeC、Ga、GaAs、InAs、InP、他のII/IV族又はIII/VI族化合物半導体、有機半導体、或いは層状半導体の1つを含む、請求項1に記載の半導体構造体。

【請求項3】

前記半導体基板がSi含有半導体材料である、請求項2に記載の半導体構造体。

【請求項4】

前記界面層は、Si原子及びO原子、随意的にN原子を含む、請求項1に記載の半導体構造体。

【請求項5】

前記界面層は、SiO2、SiON、又はこれらのシリケートを含む、請求項4に記載の半導体構造体。

【請求項6】

前記界面層は、約4.0から約20までの誘電率と、約0.1nmから約5nmまでの厚さとを有する、請求項1に記載の半導体構造体。

【請求項7】

前記界面層は、約1原子百分率から約80原子百分率までのSi含有量を有する、請求項1に記載の半導体構造体。

【請求項8】

前記界面層は、勾配付けされているSi含有量を有する、請求項1に記載の半導体構造体。

【請求項9】

前記高k誘電体は、4.0より大きい誘電率と、約0.5nmから約10nmまでの厚さとを有する、請求項1に記載の半導体構造体。

【請求項10】

前記高k誘電体は、酸化物、窒化物、酸窒化物、シリケート、又はこれらの混合物を含む、請求項1に記載の半導体構造体。

【請求項11】

前記高k誘電体は、Hfベースの材料である、請求項1に記載の半導体構造体。

【請求項12】

前記界面層はSiO2又はSiONを含み、前記高k誘電体は、HfO2、Hfシリケート、又はHf酸窒化物を含む、請求項1に記載の半導体構造体。

【請求項13】

前記HfSiNは、4.0eVから4.5eVまでの間の仕事関数を有する、請求項1に記載の半導体構造体。

【請求項14】

前記HfSiN層の上にSi含有導電性材料をさらに含む、請求項1に記載の半導体構造体。

【請求項15】

前記界面層、前記高k誘電体及び前記HfSiNゲート金属が、ゲート領域内にパターン形成される、請求項1に記載の半導体構造体。

【請求項16】

HfSiN金属化合物を製造する方法であって、

Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを準備するステップと、

前記雰囲気中で前記HfターゲットからHfSiN膜をスパッタリングするステップと

を含む、方法。

【請求項17】

nが0、1、2、3、又は4であり、Rが1から約18までの炭素分子を含む脂肪部分である場合に、前記Si源は、式SiH4−nRnを有する、請求項16に記載の方法。

【請求項18】

nが0であり、前記Si源がSiH4である、請求項17に記載の方法。

【請求項19】

前記Si源は、固体、液体、又は気体である、請求項16に記載の方法。

【請求項20】

前記Si源は、約70%から約99%までのHeで希釈される、請求項16に記載の方法。

【請求項21】

前記Ar/N2/Si源は、それぞれ、約1−100/1−100/1−100sccmの流量比を有する、請求項16に記載の方法。

【請求項22】

半導体構造体を形成する方法であって、

基板の表面上に、高k誘電体及び界面層を含むスタックを準備するステップと、

前記スタック上にHfSiN膜を形成するステップと

を含み、前記HfSiN膜は、Hfターゲットと、Ar/N2/Heで希釈されたSi源を含む雰囲気とを準備し、前記雰囲気中で前記HfターゲットからHfSiN膜をスパッタリングすることによって形成される、方法。

【請求項23】

nが0、1、2、3、又は4であり、Rが1から約18までの炭素分子を含む脂肪部分である場合に、前記Si源は、式SiH4−nRnを有する、請求項22に記載の方法。

【請求項24】

nが0であり、前記Si源がSiH4である、請求項23に記載の方法。

【請求項25】

前記Si源が、固体、液体、又は気体である、請求項22に記載の方法。

【請求項26】

前記Si源は、約70%から約99%までのHeで希釈される、請求項22に記載の方法。

【請求項27】

前記Ar/N2/Si源は、それぞれ、約1−100/1−100/1−100sccmの流量比を有する、請求項22に記載の方法。

【請求項28】

前記HfSiN層の上にSi含有導電性材料を形成するステップをさらに含む、請求項22に記載の半導体構造体。

【請求項29】

パターン形成されたゲート領域内に、前記HfSiN膜と、前記高k誘電体及び前記界面層を含む前記スタックとをパターン形成するステップをさらに含む、請求項22に記載の方法。

【請求項30】

パターン形成されたゲート領域内に、前記Si含有導電性材料と、前記HfSiN膜と、前記高k誘電体及び前記界面層を含む前記スタックとをパターン形成するステップをさらに含む、請求項28に記載の方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公表番号】特表2008−530770(P2008−530770A)

【公表日】平成20年8月7日(2008.8.7)

【国際特許分類】

【出願番号】特願2007−551254(P2007−551254)

【出願日】平成17年12月2日(2005.12.2)

【国際出願番号】PCT/US2005/043555

【国際公開番号】WO2006/076087

【国際公開日】平成18年7月20日(2006.7.20)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MASCHINES CORPORATION

【Fターム(参考)】

【公表日】平成20年8月7日(2008.8.7)

【国際特許分類】

【出願日】平成17年12月2日(2005.12.2)

【国際出願番号】PCT/US2005/043555

【国際公開番号】WO2006/076087

【国際公開日】平成18年7月20日(2006.7.20)

【出願人】(390009531)インターナショナル・ビジネス・マシーンズ・コーポレーション (4,084)

【氏名又は名称原語表記】INTERNATIONAL BUSINESS MASCHINES CORPORATION

【Fターム(参考)】

[ Back to top ]