新電元工業株式会社により出願された特許

41 - 50 / 776

半導体装置及びその製造方法

【課題】絶縁層の電気的絶縁特性が損なわれることなく、かつ良好な放熱性を確保する。

【解決手段】導電性を有する板状のダイパッド10と、ダイパッドの一面に固定される半導体チップ20と、導電性を有しかつ帯板状に形成されて、その長手方向の一端部が前記半導体チップに電気接続されるリード30と、ダイパッドの他面に接合される放熱部材40と、少なくともリードの他端部が露出するように、リードの一端部、ダイパッド及び半導体チップを封止するモールド樹脂50とを備える。放熱部材は、ダイパッドの他面に接合材を介して接合される金属箔41、半導体チップから生じる熱を放散する放熱部42、及び放熱部と金属箔との間に介装される絶縁層43を有する。

(もっと読む)

電流検出回路、およびモータ制御装置

【課題】プリント配線基板上に搭載されるFETに流れる電流を、FETオン時のオン抵抗Ronと配線パターン抵抗Rpによる電圧降下VDGを基に検出する際に、配線パターンの抵抗Rpにより発生する電圧降下分(オフセット分)をキャンセルして、FET(Qo)のドレイン・ソース間電圧VDSを検出する。

【解決手段】本発明の電流検出回路1は、FET(Qo)のドレイン端子Dと回路グランドGとの間に、第1の抵抗Rdと第2の抵抗Roの抵抗直列回路を接続する。そして、第2の抵抗Ronと第1の抵抗Rdの抵抗値の比(Ro/Rd)が、FET(Qo)のオン抵抗Ronと配線パターンRpの抵抗値の比(Ron/Rp)に一致するように設定する。そして、この第1の抵抗Rdと第2の抵抗Roとの接続点(ノードN1)と回路グランドGとの間の電圧VRoを、FET(Qo)に流れる電流の検出信号として出力する。

(もっと読む)

半導体装置

【課題】表面実装型の半導体装置を回路基板の搭載面に実装した状態において、半導体チップの熱を効率よく外部に逃がせるようにする。

【解決手段】導電性を有する板状のダイパッド10と、ダイパッドの上面に固定される半導体チップ20と、導電性を有する帯板状に形成されて、その長手方向の一端部が半導体チップに電気接続されるリード30,40と、ダイパッドの下面に重ねて固定される放熱基板50と、リードの他端部42及び放熱基板の下面50bが露出するように、ダイパッド、半導体チップ、リード及び放熱基板を封止するモールド樹脂60とを備え、放熱基板が、その下面をなして導電性を有する金属板51、電気的な絶縁性を有する絶縁層52、及び、金属板よりも薄い導電性層53を順番に積層して構成され、放熱基板の下面が、リードの他端部のうち回路基板の搭載面に対向させる接合面32b,42bと同一方向に向いている半導体装置1を提供する。

(もっと読む)

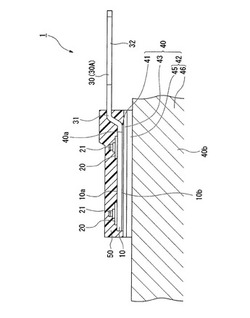

半導体装置

【課題】絶縁層の電気的絶縁特性が損なわれることなく、かつ良好な放熱性を確保する。

【解決手段】半導体チップ20と、導電性を有しかつ帯板状に形成されて、その長手方向の一端部が半導体チップに電気接続されるリード30と、半導体チップから生じる熱を放散する放熱部材40と、少なくともリードの他端部が露出するように、リードの一端部及び半導体チップを封止するモールド樹脂50とを備える。放熱部材40は、半導体チップ及びリードにそれぞれ電気接続される金属箔41、半導体チップから生じる熱を放散する放熱部42、及び放熱部と金属箔との間に介装される絶縁層43を有する。金属箔41は、半導体チップが搭載されかつリードに電気接続されるチップ搭載部41Aと、半導体チップ及びリードにそれぞれ電気接続されるリード接続部41Bに分離して形成される。

(もっと読む)

半導体装置

【課題】汎用性に優れているうえ、外観不良や電気接続不良を招き難い高品質な半導体装置を提供すること。

【解決手段】半導体チップに対して電気接続された端子板12、13と、半導体チップ及び端子板の一端部を内部に封入するように成形された第1モールド樹脂15と、を具備する本体ユニット2と、上端面にナット21を組み込む収納凹部23が形成された第2モールド樹脂20を具備し、本体ユニットに対して着脱自在に組み合わされる分離ユニット3と、を備え、端子板の他端部は、第1モールド樹脂から突出すると共に、その突出方向の先端部13dが第1モールド樹脂の上方を覆うように折曲形成され、端子板の先端部にはねじ孔17が形成され、分離ユニットは、スライド移動により第1モールド樹脂の上端面と端子板の先端部との間に位置すると共にナットがねじ孔に対して対向配置されるように本体ユニットに対して組み合わされる半導体装置1を提供する。

(もっと読む)

半導体装置

【課題】薄型化を図ることができる半導体装置を提供すること。

【解決手段】ベース基板2と、該ベース基板の上面側に形成された回路パターン部3、4と、該回路パターン部上に搭載された半導体チップ5と、回路パターン部上に取り付けられ、該回路パターン部を介して半導体チップに電気接続された端子部材6、7と、ベース基板の上面に成形され、回路パターン部、半導体チップ及び端子部材を内部に封入したモールド樹脂8と、を備え、端子部材は、上端面がモールド樹脂の外面に露出していると共に該上端面に開口したねじ孔6a、7aを有する筒状に形成されている半導体装置1を提供する。

(もっと読む)

半導体装置

【課題】本体部の外面上に複数の外部端子を配置した半導体装置において、本体部を大型化させたり部品点数を増加させることなく外部端子間の絶縁距離の増大を図る。

【解決手段】複数の外部端子12の少なくとも一つに、他の外部端子側を向く部位を切り欠く切り欠き部17が設けられ、この切り欠き部17によって、前記一つの外部端子12のネジ挿通孔16が前記他の外部端子側に向けて開放される。

(もっと読む)

スイッチング電源装置及びサージ吸収回路

【課題】少ない部品点数で構成することができ、電源効率を有効に改善することができるスイッチング電源装置を提供する。

【解決手段】本発明によるスイッチング電源装置(10)は、直流入力を交流に変換するスイッチング回路をなすトランジスタ(Q1)と、前記交流が入力された非絶縁型トランス(T)と、非絶縁型トランスから出力された交流を整流するダイオード(D2)と、ダイオード(D2)の出力部から非絶縁型トランス(T)の入力部に向かう電流方向を順方向として、ダイオード(D2)の出力部と非絶縁型トランス(T)の入力部との間に接続されたダイオード(D3)とを備える。スイッチング動作の過程でダイオード(D2)のカソード側に発生したサージが、ダイオード(D3)を介して非絶縁型トランス(T)の1次側に吸収される。

(もっと読む)

半導体装置及びその製造方法

【課題】高い逆方向耐圧VR及び低いリーク電流IRを維持したまま、順方向降下電圧VFを低くしたり、逆回復時間trrを短くしたりすることが可能な半導体装置を提供する。

【解決手段】n+型半導体層112とn−型半導体層114とを有する半導体基体110と、n−型半導体層114の表面に選択的に形成されたp+型拡散領域120と、n−型半導体層114及びp+型拡散領域120の表面上に形成され、n−型半導体層114との間でショットキー接合を形成し、p+型拡散領域120との間でオーミック接合を形成するバリアメタル層130とを備える半導体装置であって、半導体基体110には、n−型半導体層114の表面で濃度が最も高くなるように重金属としての白金が拡散されている。

(もっと読む)

半導体装置

【課題】サイリスタ構造を有し、従来よりもオン抵抗の低い半導体装置を提供する。

【解決手段】第1のp型半導体層120,122と、第1のn型半導体層110と、第2のp型半導体層130,132と、第2のn型半導体層140と、第1のp型半導体層120,122に接続されたアノード電極Aと、第2のn型半導体層140に接続されたカソード電極Kと、第2のp型半導体層130,132に接続されたゲート電極Gとを備え、第2のn型半導体層、第2のp型半導体層及び第1のn型半導体層からなる第1のトランジスタTR1と、第1のp型半導体層、第1のn型半導体層及び第2のp型半導体層からなる第2のトランジスタTR2とが組み合わされたサイリスタ構造を有する半導体装置であって、第1のn型半導体層110,150に接続され、第1のトランジスタTR1のコレクタ電流を外部に取り出すための第4の電極Sをさらに備える半導体装置。

(もっと読む)

41 - 50 / 776

[ Back to top ]