セイコーエプソン株式会社により出願された特許

50,271 - 50,280 / 51,324

半導体装置及びその製造方法、LCDドライバ用パッケージ

【課題】 メタル配線の屑が残留し兼ねない簡便なダイシングを容認でき、かつ、バンプ電極の高さを低くしつつ、フィルムキャリアのインナリードのショートを防止できる半導体装置及びその製造方法、LCDドライバ用パッケージを提供する。

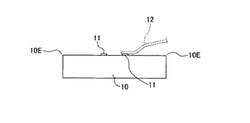

【解決手段】バンプ電極11は、半導体チップ10の半導体集積回路との接続関係を有し、半導体チップ10主表面上において相互にチップ端部より中央側に寄って配置されている。これにより、バンプ電極11と破線で示すリード12が接続されるとすると、リード12は、チップ端部10E上にさしかかるまでに有利に変形できる余裕が生じる。すなわち、リード12は、チップ端部10E上において離れた位置に置くことができる。これにより、半導体チップ10は、バンプ電極11の高さを低くしても、チップ端部10Eと接触し難いリード12との接続形態を得ることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 製造工程を簡略化して製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】 本発明に係る半導体装置は、シリコン基板1上に形成された第1及び第2のオフセット絶縁膜2a,2bと、第1のオフセット絶縁膜2aと第2のオフセット絶縁膜2bとの間に位置するシリコン基板1上に形成されたゲート酸化膜5と、ゲート酸化膜5上、第1のオフセット絶縁膜2aの一部上及び第2のオフセット絶縁膜2bの一部上に形成されたN型のゲート電極6と、ゲート電極6の外側に位置し且つ第1のオフセット絶縁膜2aに隣接するシリコン基板1に形成されたP型のソース領域の不純物層7aと、ゲート電極6の外側に位置し且つ第2のオフセット絶縁膜2bに隣接するシリコン基板1に形成されたP型のドレイン領域の不純物層7bとを具備する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】素子分離膜が埋め込まれる溝の側壁に形成される熱酸化膜を厚くすることなく、半導体素子のハンプを抑制する。

【解決手段】 基板1上にシリコン層3を形成し、その上に下地膜4及び窒化シリコン膜5を形成する。窒化シリコン膜5及び下地膜4に開口部5aを形成し、開口部5a内に位置するシリコン層3の表面に第1の熱酸化膜6を形成する。第1の熱酸化膜6を、例えばウェットエッチングにより除去する。窒化シリコン膜5をマスクとしてシリコン層3をエッチングすることにより、開口部5a内に位置するシリコン層3に、溝を形成する。溝の表面に第2の熱酸化膜を形成し、その後、溝に、素子分離膜を埋め込む。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 半導体層の結晶品質を良好に保ちつつ、互いに異なる膜厚を有する半導体層を絶縁層上に形成する。

【解決手段】 厚膜半導体領域R2の第1単結晶半導体層12a、12bをエッチング除去するとともに、薄膜半導体領域R3の第1単結晶半導体層12c、12dをエッチング除去し、厚膜半導体領域R2の第2単結晶半導体層13aおよび薄膜半導体領域R3の第2単結晶半導体層13cが消失するまで、半導体基板11、第2単結晶半導体層13a〜13dおよび支持体16の熱酸化を行うことにより、厚膜半導体領域R2の第2単結晶半導体層13bおよび薄膜半導体領域R3の第2単結晶半導体層13d下に絶縁層を形成する。

(もっと読む)

配線の形成方法及び、電子デバイスの製造方法

【課題】 レジストパターンと反射防止膜との寸法変換差を小さくすることができるようにした配線の形成方法及び電子デバイスの製造方法を提供する。

【解決手段】

シリコン基板1上に形成されたポリシリコン膜13及びWS膜15を配線形状にパターニングして当該ポリシリコン膜13及びWS膜15からなるゲート配線10を形成する方法であって、ポリシリコン膜13及びWS膜15の上方にBARC膜21を形成し、このBARC膜21上にフォトレジストを塗布し、このフォトレジストを配線形状に露光し、現像処理してレジストパターン32を形成し、このレジストパターン32をマスクにBARC膜21をCHF3ガスとCF4ガスとO2ガスとからなる第1混合ガスでドライエッチングする。BARC膜21をドライエッチングする際に、BARC膜21のレジストパターン32で覆われた部分の側面にポリマー41を形成することができる。

(もっと読む)

フレキシブルプリント基板の実装方法及び、電気光学装置の製造方法

【課題】 基板の端子部を覆っている有機膜を剥離する工程を簡略化し、製造コストの低減化を実現する、フレキシブルプリント基板の実装方法及び、電気光学装置の製造方法を提供する。

【解決手段】 基板20上に、半導体素子と、半導体素子と外部とに電気的に接続する第1の端子部35と、を形成し、第1の端子部35を覆うように有機膜37を形成する工程と、基板20に電気的に接続されるフレキシブルプリント基板50の第2の端子部55を有機膜37上から第1の端子部35に向けて加圧し、第1の端子部35と導通させる。第2の端子部55と有機膜37との間に異方性導電ペースト61又は異方性導電フィルム60を介在する。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 互いに異なる膜厚を有する絶縁層上に半導体層を形成する。

【解決手段】 第2単結晶半導体層13a、13b間の第1単結晶半導体層12a、12bを除去することにより、第2単結晶半導体層13a、13b間に空洞部17を形成した後、厚膜化BOX層領域R2の第2単結晶半導体層13aが消失するまで、半導体基板11、第2単結晶半導体層13a、13bおよび支持体16の熱酸化を行うことにより、第2単結晶半導体層13b下に絶縁層18を形成し、厚膜化BOX層領域R2と薄膜化BOX層領域R3とで第2単結晶半導体層13b下の絶縁層18の膜厚を異ならせる。

(もっと読む)

電子デバイスの評価素子及び電子デバイスの評価方法

【課題】 電子デバイス内の所定構造体の抵抗ばらつきをその電子デバイスの形成位置毎に評価することができるようにした電子デバイスの評価素子及び電子デバイスの評価方法を提供する。

【解決手段】 シリコンウエーハW上に形成されるフラッシュメモリ300のセル内におけるコンタクト抵抗のばらつきを評価するための評価素子100であって、セル内のコンタクト部位と同じような構造を持ったユニットを複数個含むホールチェーン20を備え、第1、第2の電極パッド2a,2b間の抵抗値を測定する。次に、第1、第3の電極パッド2a,2c間の抵抗値を測定し、第1、第4の電極パッド2a,2d間の抵抗値を測定し、その後、第1、第5の電極パッド2a,2e間の抵抗値を測定する。ユニット数に対するホールチェーンの抵抗値の増加度合いから、フラッシュメモリ300セル内におけるコンタクト抵抗のばらつきを知ることができる。

(もっと読む)

薄膜トランジスタ回路基板及び薄膜トランジスタ回路基板の検査方法、電気光学装置、電子機器

【課題】 CMOS回路において、例えば基板が収縮してしまっても、チャネルドープの打ち分け位置(境界位置)を特定できるようにした、薄膜トランジスタ回路基板と、この薄膜トランジスタ回路基板の検査方法、及び電気光学装置、電子機器を提供する。

【解決手段】 基板上にN型トランジスタ8Nを形成するNチャネル領域9Nと、P型トランジスタを形成するPチャネル領域8Pとが形成され、Nチャネル領域9NとPチャネル領域9Pとの少なくとも一方の半導体層にチャネルドープがなされた薄膜トランジスタ回路基板である。Nチャネル領域9NとPチャネル領域9Pとの境界部に、Nチャネル領域9N又はPチャネル領域9Pの部分的な抵抗を測定するための検査要素の集合体である検査要素グループ20が、少なくともNチャネル領域9NとPチャネル領域9Pとの境界線10の両側に位置するようにして設けられている。

(もっと読む)

半導体基板、半導体装置、半導体基板の製造方法および半導体装置の製造方法

【課題】 導体層の表面の平坦性を向上させることを可能としつつ、絶縁層および半導体層の双方の膜厚がそれぞれ異なるようにする。

【解決手段】 溝M2を介してエッチングガスまたはエッチング液を第1単結晶半導体層12a〜12cに接触させることにより、第1単結晶半導体層12a〜12cをエッチング除去し、第2単結晶半導体層13a、13bが消失するまで、半導体基板11、第2単結晶半導体層13a〜13cおよび支持体16の熱酸化を行うことにより、第2単結晶半導体層13c下に絶縁層18を形成する。

(もっと読む)

50,271 - 50,280 / 51,324

[ Back to top ]