株式会社東芝により出願された特許

53,511 - 53,520 / 54,554

半導体装置及びその製造方法

【課題】メッキ膜厚のウェハ面内均一性を向上させる。

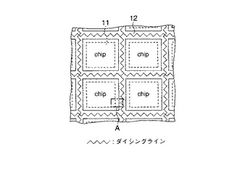

【解決手段】本発明の例に関わる半導体装置は、メタル配線を用いた多層配線構造を有する半導体集積回路が形成され、各々が独立したチップになる複数のチップ領域11と、メタル配線を用いた多層配線構造を有し、複数のチップ領域の各々を取り囲む複数のチップリング12とを備え、複数のチップリング12は、互いに電気的に接続される。

(もっと読む)

携帯端末装置

【課題】筐体を薄型に保ちつつ印刷配線基板の強度を高く維持し、これにより装置の信頼性向上を図る。

【解決手段】印刷配線基板3にメモリカード用コネクタ4を避けるための切欠部31を形成すると共に、印刷配線基板3の両面側に上記切欠部31を間において相対向するように第1及び第2の補強板5,6を配置する。そして、上記メモリカード用コネクタ4を、上記切欠部31を通して上記第1の補強板5上に載置固定した状態で、当該第1補強板5と上記第2の補強板6とで上記印刷配線基板3をその両面から挟み込んだ状態でネジ7,8により固定する。

(もっと読む)

半導体記憶装置、半導体記憶装置の製造方法

【課題】完全CMOS型SRAMセルとして、セル面積とコストを大きく増やすことなくソフトエラー耐性を向上すること。

【解決手段】第1(2)の駆動用および負荷用MISFETのゲート電極が、第1(2)の転送用MISFETのゲート電極と別に一体型のN型ポリシリコンで形成され、該N型ポリシリコン中の不純物濃度が制御されて第1(2)の抵抗素子が形成されており、第1および第2の抵抗素子が、それぞれ、第1または第2の負荷用MISFETのゲート電極の先であって、第1または第2の駆動用MISFETとは逆方向側に形成されており、第2(1)のインバータの出力ノードからの配線が、第1(2)の抵抗素子となるN型ポリシリコンの上部に形成されたコンタクト電極に繋がり、第1および第2の負荷用MISFETが、N型ゲート電極をもつ。

(もっと読む)

プリント配線板、該プリント配線板を用いた情報処理装置、該プリント配線板の製造方法、該プリント配線板の半田付け方法

【課題】プリント配線板の一部領域をノズルで覆い、その部分を、溶解した半田で過熱して半田付けする上で、スルーホール部における半田付け品質を向上する。

【解決手段】ノートPC20は、表面と裏面に配置された銅箔2a,2bを導通させるために設けた貫通口に金属メッキ加工を施したスルーホール4,13を形成したガラスエポキシ樹脂板1aと、このガラスエポキシ樹脂板1aの銅箔2bに積層し、スルーホール13を含むように形成され、表面からスルーホール13に挿入されたリード6を半田付けするための端子パッド12bと、この端子パッド12bとは分離して裏面の銅箔2bに積層形成され、裏面の銅箔2bを介してスルーホール13に熱を伝える熱伝導パッド10とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】 寄生抵抗を低減して駆動能力を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】 ゲート絶縁膜40を介して形成されたゲート電極50と、ゲート電極側壁55A及び55Bと、半導体基板20の表面部分において、チャネル領域60の両側に、ゲート電極側壁55A及び55Bの下方にそれぞれ形成された第1のソース領域70B及び第1のドレイン領域70Aと、第1のソース領域70Bより接合深さが深い第2のソース領域90B、及び第1のドレイン領域70Aより接合深さが深い第2のドレイン領域90Aと、チャネル領域60の両側にチャネル領域60を挟むように、第1のソース領域70B及び第1のドレイン領域70Aより深い領域まで形成された所定の半導体材料を不純物として含む層80B及び80Aとを備えることを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 本発明は、寄生トランジスタ動作、ゲート電極とソース領域及びドレイン領域との間のリーク電流及び容量の増大を防止することができる半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 半導体基板上に第1の絶縁膜を介して形成された凸型形状の半導体層と、第1の絶縁膜上に形成され、半導体層の底部から所定の高さまで埋没する程度の膜厚を有する絶縁膜と、半導体層の側面のうち、チャネル領域を流れる電流の方向と略平行に形成されている各側面に、ゲート絶縁膜を介して形成されたゲート電極と、半導体層内において、ゲート電極が形成されていない領域に形成されたソース領域及びドレイン領域とを備えることを特徴とする。

(もっと読む)

超電導限流素子およびその製造方法

【課題】超電導体と超電導体の保護抵抗とを並列接続した構成を有し、超電導体と保護抵抗の損傷を防止できる超電導限流素子を提供する。

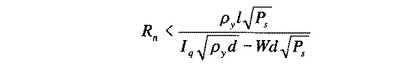

【解決手段】基材上に設けられた超電導体と、超電導体の保護抵抗とを並列接続した超電導限流素子であって、冷却温度における保護抵抗の値Rnが下記の式

【数1】

(ここで、ρyは臨界温度直上における超電導体の抵抗率、dは超電導体の厚さ、Wは超電導体の幅、lは超電導体が常伝導転移した領域の長さ、Iqは限流開始電流値、Psは超電導体が設けられた基材が破壊しない最大熱負荷である。)

を満足する超電導限流素子。

(もっと読む)

半導体装置の製造方法

【課題】 SRAMセルのサイズが縮小化された場合、ゲート電極配線の抵抗要素の抵抗値を調整してSRAMセルを形成できるようにする。

【解決手段】 SRAMセルの製造時において、1回目に不純物イオンを注入するときにはイオン濃度を比較的高く低加速電圧の条件でイオン注入し、ソース/ドレイン拡散層13を形成する。2回目に不純物イオンを注入するときには、イオン濃度を比較的低く高加速電圧の条件でイオン注入し、第1の多結晶シリコン膜6の抵抗値を調整する。

(もっと読む)

半導体装置

【課題】 信頼性の高い半導体装置を実現するために、寄生容量の大きな半導体装置を提供する。

【解決手段】 半導体装置は、第1方向に延在する突出部1bを有する半導体基板1を含む。ゲート絶縁膜11は、突出部の上面上および第1方向に沿う側面上に配設される。ゲート電極12は、第1部分12aと第2部分12bを有する。第1部分は、突出部と交差し、且つ突出部の上面上のゲート絶縁膜上に配設される。第2部分は、突出部の側面上のゲート絶縁膜上に配設され、且つ第1方向における長さが第1部分の第1方向における長さより長い。1対のソース/ドレイン領域13が、ゲート電極の第1部分の下方の領域を挟むように突出部の表面に形成される。

(もっと読む)

半導体装置

【課題】 ゲート−ドレイン間の容量が小さく、尚且つ、オン抵抗の低いパワー半導体装置を提供する。

【解決手段】

半導体装置100は、N型の半導体層20と、半導体層20の表面に形成されたP型のソース30およびP型のドレイン40と、ソース30とドレイン40との間のチャネル領域上にゲート絶縁膜60を介して設けられたゲート電極70であって、チャネル領域のチャネル長方向の長さがLgであるゲート電極70と、チャネル領域にイオン注入して形成されたボディ領域80であって、深さがXj、ゲート絶縁膜60を介してゲート電極70と対向するイオン注入された部分のチャネル長方向の長さがLaであるボディ領域80とを備え、La≦Lg−Xjを満たすことを特徴とする。

(もっと読む)

53,511 - 53,520 / 54,554

[ Back to top ]