株式会社村田製作所により出願された特許

191 - 200 / 3,635

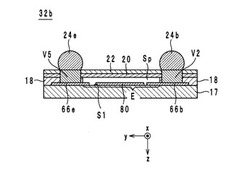

回路モジュール及び複合回路モジュール

【課題】加熱時に、装置内部における接続に破損が発生することを抑制できる回路モジュール及び複合回路モジュールを提供することである。

【解決手段】SAWフィルタ32bは、圧電基板17と、圧電基板17の主面上に設けられている縦結合部と、縦結合部上に空隙Spを形成した状態で圧電基板17の主面を覆う支持層18及びカバー層20,22と、カバー層22上に設けられ、かつ、縦結合部と電気的に接続されているバンプ24a〜24fと、を含んでいる。実装基板は、マザー基板上に実装され、バンプ24a〜24fを介してSAWフィルタ32bが実装される。

(もっと読む)

積層セラミックコンデンサおよびこれを用いたジャンパ実装構造

【課題】 従来の積層セラミックコンデンサを用いると、両面回路基板の表面に実装された、電源およびグランド接続端子が信号線接続端子よりも内側に配置された負荷ICへ、両面回路基板の裏面において電源配線をジャンパ接続することができない。

【解決手段】 積層セラミックコンデンサ31の胴体部分の長さが、負荷IC41の信号線接続端子群42aにつながる基板裏面に形成された信号線配線パターンの形成領域を跨ぐ長さに単に設定されることで、胴体部分が信号線配線パターンに電気接触することなく、長手方向両側の一方の外部電極34a,34bが、基板裏面の電源配線パターン51と、負荷IC41の電源接続端子42につながるビアホールとに接続される。また、長手方向両側の他方の外部電極35a,35bが、基板裏面のグランド配線パターン52と、負荷IC41のグランド接続端子42につながるビアホールとに接続される。

(もっと読む)

電極の製造方法および電極製造装置

【課題】生産ラインの運転と停止によって電極の矯正度合いが箇所によってばらつくという問題を解消することが可能な電極の製造方法と電極製造装置を提供する。

【解決手段】電極製造装置1は、電極合材が塗工された塗工部と、電極合材が塗工されていない未塗工部とを含む集電体を押圧する圧延ロール13a、13bと、圧延ロール13a、13bによる押圧の後、未塗工部を選択的に押圧するパンチプレス14a、14bとを備える。

(もっと読む)

電歪センサ

【課題】素子の変形により電気的変化を生じるセンサであって、時間が経過しても感度が低下しないセンサを提供する。

【解決手段】電歪素子の変形により静電容量変化を生じる電歪センサ(40)において、第1の電歪材料層(1)およびその両面に各々配置された一対の電極(3a、3b)より構成される第1の電歪素子(10)と、第2の電歪材料層(11)およびその両面に各々配置された一対の電極(13a、13b)より構成される第2の電歪素子(20)と、これら電歪素子間に挟持された基材(25)とを含む受感部(30)を設ける。受感部(30)は、外力の作用を受けることにより変形である。第1および第2の電歪材料層(1、11)の静電容量をそれぞれ測定可能なように、各電極に引出し線(5a、5b、15a、15b)が接続される。第1および第2の電歪材料層(1、11)は、10μm以下の厚みおよび20以上の比誘電率を各々有するものとする。

(もっと読む)

弾性波装置

【課題】周波数の調整を安定して行なうことが可能な弾性波装置を提供する。

【解決手段】弾性波装置は、主面を有する圧電基板100と、圧電基板100の主面上に形成され、所定の周波数で圧電基板100を励振させるIDT電極200と、圧電基板100に所定の応力を生じさせて所定の周波数を変化させる加圧部600とを備える。

(もっと読む)

セラミック電子部品

【課題】金属端子が外れにくいセラミック電子部品を提供する。

【解決手段】セラミック電子部品1は、2個の電子部品本体50と1対の金属端子10Aとを備えている。金属端子10Aは、基部12と、基部12の左右にそれぞれ設けられたリブ部14,16と、基部12の下に設けられた実装部18と、を備えている。矩形状の基部は、2個の電子部品本体の外部電極60,62のそれぞれに接合されるべき2つの接合部20,22と、接合部20,22のそれぞれの下方に形成された閉形状の切欠き部24,26と、を有している。リブ部14,16は、基部の幅方向の左右両側部から、電子部品本体側に直角に折り曲げられている。リブ部14,16の長さは、基部の高さ方向の上端部から実装部まで至っておらず、実装側に位置する電子部品本体の実装側の主面50b近傍まで延在している。実装部は、基部の下方端部から電子部品本体側に直角に折り曲げられている。

(もっと読む)

インダクタンス素子

【課題】 異なる複数の幅のランド電極のいずれにも実装可能なインダクタンス素子を提供する。

【解決手段】 インダクタンス素子100は、巻芯部の両端部に形成された上鍔部2および下鍔部3を備えたコア1と、巻芯部に巻回された導線4と、下鍔部3に形成された1対の端子電極5を備え、下鍔部3は、内面と、底面3aと、1対の側面3bと、1対の端面3cを備え、端子電極5は、主電極領域5aと、主電極領域5aから1対の側面3b方向にそれぞれ延びた少なくとも1対の延長電極領域5bを備え、導線4の両端部4aは、それぞれ、下鍔部3の側面3bおよび底面3aを経由して、端子電極5に接続され、下鍔部3の底面3aの、導線4の両端部4aが経由する領域には、端子電極5の延長電極領域5bが形成されないようにした。

(もっと読む)

蓄電デバイスの製造方法および製造装置

【課題】外包材が可撓性を有する材料からなる蓄電デバイスの製造方法および製造装置において、セパレータを介在して正極と負極とが積層または巻回されることにより形成された電極構造体の間隙に電解液を含浸させる時間を短くすることが可能な蓄電デバイスの製造方法および製造装置を提供する。

【解決手段】可撓性を有する外包材20を用いて電極構造体10を収容するラミネート型リチウムイオン二次電池の製造方法において、外包材20で囲まれた内側空間に、電極構造体10を収容し、外包材20の開口を通じて電解液を注入した後、外包材20が拘束された状態で圧力容器に収容し、外包材20の内側空間と外側空間の圧力を大気圧から真空状態になるように減少させ、外包材20の外側空間の圧力を真空状態から大気圧になるように増加させることを繰り返し行って、電極構造体10の間隙に電解液を含浸させる。

(もっと読む)

スイッチング電源

【課題】出力電圧に基づく出力検出回路による検出信号を、スイッチング素子を制御する制御回路に正確にフィードバックすることができる技術を提供する。

【解決手段】平滑用チョークコイル10a,10bが励磁するのに伴い、出力検出回路8の検出信号をフィードバックする出力検出配線17に設けられた2つの配線部18a,18bにそれぞれ互いに逆の向きに誘導起電力が生じるため、2つの配線部18a,18bにそれぞれ生じる誘導起電力は互いに打ち消される。したがって、平滑用チョークコイル10,10bの励磁に伴う誘導起電力による電圧変動が、出力検出配線17によりフィードバックされる出力検出回路8の検出信号に与える影響を抑制することができ、平滑回路7の出力電圧に基づく出力検出回路8による検出信号を、スイッチング素子4を制御する制御回路5に出力検出配線17により正確にフィードバックすることができる。

(もっと読む)

多孔質金属膜、電極、集電体、電気化学センサ、蓄電デバイス及び摺動部材並びに多孔質金属膜の製造方法

【課題】比表面積の大きな多孔質金属膜を提供する。

【解決手段】多孔質金属膜10は、基材20の上に形成される多孔質金属膜である。多孔質金属膜10は、複数の筒状体11を備えている。複数の筒状体11は、基材20の上に配されている。

(もっと読む)

191 - 200 / 3,635

[ Back to top ]