株式会社村田製作所により出願された特許

3,591 - 3,600 / 3,635

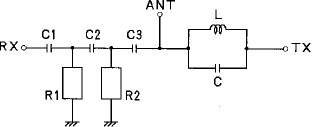

アンテナ共用器

【目的】部品点数を削減し、製造工数を低減して、安価でかつ小型化のできるアンテナ共用器を提供する。

【構成】送信部側フィルタまたは受信部側フィルタのいずれか一方のフィルタをインダクタンスLと容量Cの並列共振回路からなるバンドエリミネーションフィルタで構成し、他方のフィルタを誘電体共振器R1、R2を用いたバンドパスフィルタで構成する。バンドエリミネーションフィルタはLC並列共振回路のみで構成されるので、部品点数を削減できる。

(もっと読む)

圧電共振子

【目的】フィルタの群遅延時間特性の乱れを低減し、スプリアス特性の悪化を防止し、さらに、ディスクリミネータの歪率特性に乱れが生じない小型の圧電共振子を提供することにある。

【構成】略四角形状板の圧電基板の両表面に、振動電極を対向して設け、振動部を形成してなるエネルギー閉じ込め形厚み縦振動の圧電共振ユニットからなる圧電共振子において、前記振動部の外部で、圧電基板内の一部に、未分極部を設けたことを特徴とする。

(もっと読む)

ストリップ線路とそれを用いる伝送線路,共振器およびフィルタ

【構成】 誘電体基板12の主面上に形成するU字状のストリップ線路16の長さ方向にスリット18を形成する。

【効果】 うず電流の悪影響による実質的な断面積の減少および損失が抑えられ、Qを大きくできる。

(もっと読む)

DC/DCコンバータ

【目的】 負荷短絡時や出力待機時に出力電流を遮断して電子部品が破損されるのを防止する。

【構成】 入力電圧Viを制御用IC1に供給して、制御用IC1の発振出力に応じてスイッチングトランジスタQ1をスイッチングし、コイルLに蓄積されたエネルギを整流用ダイオードDiを介して出力するDC/DCコンバータにおいて、整流用ダイオードDiと出力端との間にトランジスタQ2を接続し、このトランジスタのオン,オフのしきい値電圧差と入力および出力電圧差を利用し、出力短絡時または待機時にトランジスタQ2を非導通にし、過大な短絡電流が流れるのを防止する。

(もっと読む)

縦型焼成炉

【目的】高温焼成室内で排ガス処理を行い得る構成の縦型焼成炉を提供する。

【構成】炉体1の上下位置に配置されて連続した高温焼成室2及び低温脱脂室3と、仕切り板4を介して高温焼成室2を囲むヒータ室5と、低温脱脂室3内に装入され、かつ、低温脱脂室3及び高温焼成室2間を移動動作する移動部材7とを備えた縦型焼成炉であって、仕切り板4には高温焼成室2とヒータ室5とを連通させる通気路20が設けられており、高温焼成室2には焼成用ガスG1及び焼却用ガスG3を切り換えて供給する第1ガス供給配管21が遮断弁22を介して接続され、ヒータ室5には脱脂用ガスG2を排出する第1ガス排出配管23が遮断弁24を介して接続されていると共に、低温脱脂室3には脱脂用ガスG2を供給する第2ガス供給配管25と焼成用ガスG1を排出する第2ガス排出配管26とが遮断弁27,28を介して接続されている。

(もっと読む)

ストリップ線路、該ストリップ線路を備えたマイクロ波回路及び該マイクロ波回路の周波数調整方法

【目的】 ストリップ線路及び該ストリップ線路を用いたマイクロ波回路の小型化を可能にする。

【構成】 電力分配器1は誘電体基板2の両端面に第1ポートP1と第2,第3ポートP2,P3とを形成し、かつ、第1ポートP1と第2,第3ポートP2,P3間をそれぞれ波状に屈曲させた波長ストリップ電極7,8で結合して構成されている。ストリップ電極7,8の線路上にそれぞれ凹溝21〜23,21′〜23′を設け、該ストリップ電極7,8を誘電体基板2の高さ方向にも屈曲させることにより第1ポートP1と第2,第3ポートP2,P3間の直線距離L1を短縮し、電力分配器1の小形化を可能にした。

(もっと読む)

非還元性誘電体磁器組成物

非還元性誘電体磁器組成物

【目的】 還元性雰囲気中で焼成しても半導体化せず、しかも結晶粒径が小さいにもかかわらず、大きな誘電率が得られ、これを用いることによって積層セラミックコンデンサを小型化することができる、非還元性誘電体磁器組成物を提供する。

【構成】 この発明は、その主成分が次の組成式、{ (Ba1-x-y-z Srx Cay Rez ) O1+z/2 }m ( Ti1-o-p-q Zro Hfp Nbq ) O2+q/2 で表され、x,y,z,o,p,qおよびmが、0<x≦0.32、0≦y≦0.20、0<z≦0.02、0<o≦0.24、0<p≦0.16、0<q≦0.015、1.00≦m≦1.03、0<z+q≦0.025の関係を満足し、前記主成分100モルに対して、Mn,Fe,Cr,Co,Niの各酸化物をMnO2 ,Fe2 O3 ,Cr2 O3 ,CoO,NiOと表したとき、各酸化物の少なくとも一種類を0.02〜2.0モル含む、非還元性誘電体磁器組成物である。

(もっと読む)

表面波素子

表面波素子

【目的】 本発明は、主共振の横0次モードの近似関数COS- 1 (|αX|)に、縦0次モードの近似関数COS(βX)を乗じることによって、交さ幅重み付けIDT電極を構成して、高次モードの影響を減少させ、共振周波数付近のスプリアスを抑制することを目的とする。

【構成】 圧電基板上に、交さ幅重み付けを施したIDT電極と、その前後に反射器電極とを、形成した表面波素子において、IDT電極の中心を原点とし、表面波の伝播方向にX軸、その垂直方向にY軸を仮定し、X軸方向のIDT電極の範囲を−X0 /2≦X≦X0 /2としたとき、IDT電極の交さ幅重み付け包絡線がY=±COS- 1 (|αX|)・COS(βX)

但し、0<α≦π/X0 0<β≦π/X0を満たすように形成されていることを特徴とする表面波素子

(もっと読む)

3,591 - 3,600 / 3,635

[ Back to top ]