コーセル株式会社により出願された特許

11 - 20 / 80

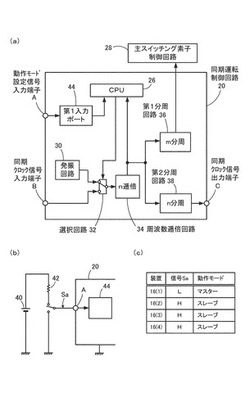

スイッチング電源装置及びそれを用いたスイッチング電源システム

【課題】低周波のビートノイズの発生を防止する同期運転の機能を備え、電源システムの形態に対応できる汎用性を備えたスイッチング電源装置及びそれを用いたスイッチング電源システムを提供する。

【解決手段】主スイッチング素子22aとそのオンタイミングを決定するスイッチング素子制御回路28を有する電力変換部18と、同期運転制御回路20とから成る。同期運転制御回路20は、外部入力用の動作モード設定信号入力端子Aと、システムクロック信号を分周数nで分周した同期クロック信号Sbが入力される同期クロック信号入力端子Bを備える。所定周波数の発振クロック信号を出力する発振回路30と、同期クロック信号Sb又は発振クロック信号を出力する選択回路32と、その出力信号をn逓倍したシステムクロック信号を出力する周波数逓倍回路34を備える。システムクロック信号をm分周した駆動クロック信号を生成する第1分周回路36を備える

(もっと読む)

半導体放熱装置

【課題】半導体素子の発熱を効率的に安定して放熱するための半導体放熱装置を安価に製造して提供する。

【解決手段】半導体2を収納した収納部3及び貫通孔4を有した固定部5で構成され、収納部3及び固定部5の同一側に形成される第1放熱面8と、収納部3の第1放熱面の反対側に形成される第2放熱面9とを設けた半導体素子1に装着される半導体放熱装置10に於いて、第1放熱面8に接触する第1放熱部材11と、第1放熱部材11との接合部25を支点として固定部5に接触せずに第2放熱面9に弾性的に接触する第2放熱部材21と、貫通孔4に挿通して第1放熱部材11及び第2放熱部材21に係合し、第1放熱部材11と第2放熱部材21とで半導体素子1を挟持させる固定部材28とを備える。

(もっと読む)

電源用チョークコイル

【課題】2つのインダクタを共有するコアで実現し、相互干渉の無い電源用チョークコイルを提供する。

【解決手段】直方体状の磁気コア12と、直方体状の磁気コア12に巻回する第1コイル14と、第1コイルと直交する方向に、コイルに重ねて直方体状の磁気コアに巻回する第2コイル16とを備え、第1コイル14と第2コイル16に交互に電流を流して、1つの磁気コアを共有した2つのチョークコイルとして機能させることを特徴とする電源用チョークコイルである。磁気コアのコア材は、ダストコア、磁気異方性コア、ギャップ付コア、アモルファスコア又は鉄系合金、あるいは、それぞれのコア材を組み合わせてもよい。第1コイル14及び第2コイル16は絶縁被膜で被覆された線状コイルであり、磁気コア12に複数回巻回されている。

(もっと読む)

スイッチング電源装置

【課題】コンパクトで安価に構成できる制御回路により、理想的なアクティブクランプ動作を行うことができるフライバック式のスイッチング電源装置を提供する。

【解決手段】フライバック式のインバータ回路30を有する。ローサイドの主スイッチング素子16にトランス14の一次巻線14aが接続されている。クランプ素子32とクランプコンデンサ34,36で成るクランプ回路40を有する。主スイッチング素子16を制御するインバータ動作制御回路18を有する。クランプ素子32を制御するクランプ動作制御回路44を有する。クランプ動作制御回路44は、クランプコンデンサ34,36の中点からクランプ素子32のゲートに向かう第1ダイオード46、クランプ素子32のソース端子からクランプコンデンサ34,36の中点に向かう第2ダイオード48、及びクランプ素子32のゲートから主スイッチング素子16のドレインに向かう第3ダイオードを備える。

(もっと読む)

スイッチング電源装置

【課題】入力電圧の増加に対し同期整流器を確実に保護すると共に電源停止時の回生電流の増加を回避して保護する。

【解決手段】同期整流型フライバックコンバ−タを用いたスイッチング電源装置に、スイッチングFET20をオフした場合に出力トランス12の駆動コイル18に発生する負極性の誘起電圧から生成した駆動信号の同期整流FET24のゲートへの供給を阻止すると共に、電源停止によりスイッチングFET20をオフした場合に駆動コイル18に発生する正極性の誘起電圧から生成した駆動信号を減少させて所定時間後に同期整流FET24をオフする同期整流駆動回路30を設ける。

(もっと読む)

ノイズフィルタ

【課題】狭いスペースに搭載可能なねじなし端子を組み込み、導通チェックの容易なノイズフィルタを提供する。

【解決手段】ケース本体82と、複数の回路部品を覆った状態でケース本体に装着されるケースカバー92と、ケース本体82にケース本体と一体に形成されるAC入力端子台86とAC出力端子台88と、AC入力端子台とAC出力端子台に、ケース本体の側面部内壁に面して配置された接続板と、ケース本体側面部に対抗して配置された電線固定用の屈曲した平板状の接圧ばねと、ケース本体側面部に対して接続する電線と略平行な位置に配置された接圧ばねの端部側を押下するリリースボタン50−1〜50−6と、回路部品に電気的に接続される導体板とで構成されるねじなし端子と、電線挿入のための開口部16−1〜16−10とリリースボタンをガイドする開口部とを備えた端子カバーとを備えたノイズフィルタ80である。

(もっと読む)

スイッチング電源装置

【課題】入力電圧を昇圧または降圧した直流電圧を自在に出力でき、回路構成がシンプルで損失も小さいスイッチング電源装置を提供する。

【解決手段】双方向に導通可能な第1、第2スイッチングトランジスタ28,30が直列接続された第1アーム32と、第3、第4スイッチングトランジスタ34,36が直列接続された第2アームを備える。第1アーム32の中点と第2アーム38の中点との間に入力電圧Viを供給する第1インダクタ40を備える。第1、第2アーム32,38の並列回路の両端間に接続された第1コンデンサ42及び第2インダクタ44の直列回路を備える。第2インダクタ44に発生する矩形電圧を整流して出力する整流素子46と、整流素子46の出力を平滑する第2コンデンサ48を備える。各スイッチングトランジスタ28,30,34,36のオン・オフを制御して出力電圧を安定化するスイッチング制御回路を備える。

(もっと読む)

スイッチング電源装置

【課題】負荷の重軽によらず高い電源効率を実現し、主スイッチング素子が停止したとき、トランス巻線駆動される整流側及び転流側スイッチング素子を安全に停止させる。

【解決手段】フォワード型のインバータ回路を有し、出力整流部に整流側スイッチング素子32及びダイオード32a、転流側スイッチング素子34及びダイオード34aを備える。転流側スイッチング素子34のゲートに転流側駆動コンデンサ32cと放電抵抗54を備える。主トランス16は補助巻線16cを有する。主スイッチング素子14のターンオフ時の、補助巻線16cの電圧変化を観測する微分回路58を備える。微分出力をソースフォロアで出力する駆動トランジスタ60と、転流側スイッチング素子34のゲートに出力するホールドダイオード62を備える。転流側スイッチング素子34のゲートと補助巻線16cの間に電圧差を生じさせる電圧降下回路66を備える。

(もっと読む)

力率改善回路およびその起動動作制御方法

【課題】入力投入時の出力電圧のオーバーシュート及びアンダーシュートを所定の電圧範囲内に抑えることができ、定数の設計も容易な力率改善回路を提供する。

【解決手段】入力電圧信号Vs1の瞬時値が、第2基準電圧Via未満であることを示す脈流監視信号を出力する脈流監視手段40を備える。出力電圧信号Vo1が、入力電圧信号Vs1の波高値よりも第3基準電圧Vobだけ低い電圧に達したことを示す差電圧監視信号を出力する差電圧監視手段42を備える。出力電圧信号Vo1が、第4基準電圧Vocに達したことを示す第1出力監視信号を出力する第1出力監視手段44を備える。出力電圧信号Vo1が、第5基準電圧Vodに達したことを示す第2出力監視信号を出力する第2出力監視手段46を備える。各監視信号に基づき、駆動パルスVgを出力可能な状態にするか否かの判断結果を、駆動パルス生成回路38に出力する開始・停止判断手段48を備える。

(もっと読む)

力率改善回路

【課題】入力電圧の高低に応じ、昇圧電圧の目標値を容易かつ高精度に自動調整することができる力率改善回路を提供する。

【解決手段】昇圧チョッパ回路16のスイッチング制御回路28と、入力電圧信号Viを出力する入力電圧検出回路44を備える。入力電圧信号Viに応じて時比率が定められる一定周期の基準パルスV46を出力する基準パルス発生器46を備える。基準パルスV46の平均化電圧V48を出力する平均化回路48を備える。平均化電圧V48に応じた目標値補正信号Ibを、昇圧電圧信号Vo1又は基準電圧V34に注入する補正信号注入抵抗50を備える。目標値補正信号Ibによって、昇圧電圧Voが整流電圧Vsの波高値Vspよりも高くなるように、昇圧電圧Voの目標値Vaが補正される。入力電圧Viが高くなるほど昇圧電圧Voが高くになるように目標値Vaが補正される。

(もっと読む)

11 - 20 / 80

[ Back to top ]