ローム株式会社により出願された特許

1,101 - 1,110 / 3,539

MEMSセンサ

【課題】 ダイヤフラムなどの振動膜の振動しやすさを確保しながら、振動膜とバックプレートなどの対向電極との接触による短絡を、簡単な構成で防止することのできるMEMSセンサを提供すること。

【解決手段】 シリコンマイク1において、シリコン基板2の一方側に、シリコン基板2に対して間隔を空けて対向するように、金属電極10が、所定の樹脂材料からなるダイヤフラム被覆膜11に被覆されてなるダイヤフラム8を形成する。また、ダイヤフラム8に対してシリコン基板2の反対側において、ダイヤフラム8に対して間隔を空けて対向するように、導電性材料からなるバックプレート9を形成する。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18上に、SiおよびOを含む絶縁材料からなる犠牲層41が積層される。犠牲層41の積層後、熱処理が行われる。第2絶縁層6および犠牲層41にSiおよびOが含まれるので、熱処理が行われると、第2絶縁層6と合金膜18との界面および合金膜18と犠牲層41との界面において、Si、OおよびMnが結合し、それぞれMnSiOからなる第2バリア膜13および反応生成膜42が形成される。合金膜18に含まれるMnが反応生成膜42の形成に使用されることにより、第2バリア膜13の形成後、その第2バリア膜13の形成に寄与せずに合金膜18に残留するMnの量が減少する。そのため、合金膜18上に積層されるCu層20に拡散するMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体装置

【課題】第1不純物領域−第2不純物領域間(たとえば、ソース−ドレイン間)の電位分布を均一にすることができる半導体装置を提供すること。

【解決手段】半導体装置1のLDMOSFET6において、エピタキシャル層3の表面におけるドレイン領域11とボディ領域7との間の部分に、ボディ領域7と間隔を空けてフィールド絶縁膜12を形成する。フィールド絶縁膜12上に、フローティングプレート17を、V1/D1=V2/D2を満たすように配置するとともに、各フローティングプレート17をそれぞれ一定電位に保持する。上記定義値は、V1:ドレインコンタクトプラグ23とフローティングプレート17との電位差、D1:ドレインコンタクトプラグ23とフローティングプレート17との間隔、V2:ゲート電極14とフローティングプレート17との電位差、D2:ゲート電極14とフローティングプレート17との間隔とする。

(もっと読む)

フォトインタラプタ

【課題】より薄型化を図ることが可能であり、かつ高い検出精度を有するフォトインタラプタを提供する。

【解決手段】発光モジュール1と、受光モジュール2と、第1の方向xに対して直角である第2の方向yにおいて検出用空間31を迂回する連結部32を有する外側モールド体3と、を備えており、受光モジュール2が、受光素子21とワイヤ24と、これらを覆う内側モールド体25と、を具備しているフォトインタラプタA1であって、外側モールド体3は、内側モールド体25の入射面25aに繋がる部分を覆うように形成された遮光部33を有しており、遮光部33は、第1の方向x視においてワイヤ24と重なるように形成されており、かつ、内側モールド体25と接する面が、第2の方向yにおいて連結部33に近い部分ほど、第1の方向xにおける第2のリード23との間隔が小さくなる部分を有する。

(もっと読む)

半導体装置

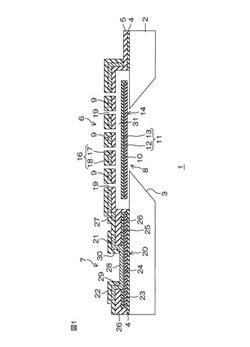

【課題】半導体基板(半導体ウエハ)上に比較的大きな厚さの層間絶縁膜が形成される構成において、半導体基板に反り変形が生じることを抑制できる、半導体装置およびその製造方法を提供する。

【解決手段】半導体基板2上に形成される層間絶縁膜12は、複数の第1絶縁膜13の積層構造を有している。また、半導体基板2上には、トランスを構成する第1コイル10および第2コイル22が層間絶縁膜12を挟んで対向して設けられている。そして、各第1絶縁膜13には、第1絶縁膜13を貫通するビアホール24が形成され、各ビアホール24には、ビア23が埋設されている。

(もっと読む)

カメラモジュール

【課題】防水機能を損なうことなく生産性を容易に高めることができるカメラモジュールを提供する。

【解決手段】カメラモジュールAは、イメージセンサ3を搭載した基板4と、イメージセンサ3に対する結像用のレンズ52,54,56を保持し、上部外周にフランジ53aを有するとともに下部外周にねじ山51aを有するレンズホルダ5と、基板4を収容した状態でレンズホルダ5にネジ山51aを介して直接螺結されるとともに、フランジ53aとの間に環状弾性体6を介してこのフランジ53aに密接させられる上端部を有するホルダケース7とを有している。

(もっと読む)

半導体装置

【課題】ボンディングパッドなどの開口内金属膜と層間絶縁膜上の表面金属膜との導通を確保することができる、半導体装置を提供する。

【解決手段】第2配線13上の層間絶縁膜21には、その表面から第2配線13に達するパッド開口22が形成されている。第2配線13におけるパッド開口22に臨む部分上には、AlCu合金からなるボンディングパッド25が形成されている。また、層間絶縁膜21上には、AlCu合金からなる電磁波シールド膜27が形成されている。そして、パッド開口22の側面上には、ボンディングパッド25と電磁波シールド膜27との導通を確保するための導通確保膜24が形成されている。ボンディングパッド25と電磁波シールド膜27とが直接に接続されなくても、導通確保膜24により、ボンディングパッド25と電磁波シールド膜27との導通を確保することができる。

(もっと読む)

半導体装置

【課題】低消費電流の半導体装置を提供する。

【解決手段】このサーモスタットIC1では、目標温度に応じたレベルの一定の参照電圧Vrefを発生する参照電圧発生回路4と、検出温度に応じたレベルの電圧Vtを出力する温度センサ5と、参照電圧Vrefと電圧Vtの高低を比較し、比較結果を示す信号を出力する比較回路6とを備え、参照電圧発生回路4および比較回路6の活性化/非活性化の制御が可能になっている。したがって、全部の回路を常時活性化させていた従来に比べ、消費電流が小さくて済む。

(もっと読む)

利得調整回路およびD級電力増幅器

【課題】利得調整および広範囲な電圧源にも安定して適用することができる利得調整回路およびD級電力増幅回路を提供する。

【課題を解決するための手段】

利得調整回路100はアナログ入力信号が入力される信号入力端子102、アナログ信号を増幅し電圧源E1が供給される演算増幅器108、演算増幅器108の反転入力端子108aと出力端子108cとの間に接続される第1のT型抵抗回路T123を備える。信号入力端子102と反転入力端子108aとの間に利得調整するための第1の可変抵抗RV1を接続する。演算増幅器108の非反転入力端子108bにはバイアス電圧供給回路130から直流バイアス電圧が供給される。バイアス電圧供給回路130は第1の電圧生成回路132および第2のバイアス電圧生成回路138を備える。第1のバイアス電圧生成回路132は第2の電圧源E2および第2のT型抵抗回路T123aを備え、第2のバイアス電圧生成回路138は第3の電圧源E3および第2の可変抵抗RV2を備える。

(もっと読む)

半導体発光素子

【課題】結晶欠陥の発生を防止し、特性が劣化しない範囲で、TMモード発振が行えるようにした半導体発光素子を提供する。

【解決手段】GaAs基板1上に、n型AlGaAsクラッド層2、n型AlGaAsビーム拡散層3、n型AlGaAs光ガイド層4、MQW活性層5、p型AlGaAs光ガイド層6、p型AlGaAsビーム拡散層7、p型AlGaAs第1クラッド層8、InGaPエッチングストップ層9、p型AlGaAs第2クラッド層10、p型GaAsコンタクト層11が形成されている。MQW活性層5は、バリア層と引っ張り歪を持つ井戸層で構成された多重量子井戸構造を有しており、井戸層の各膜厚がバリア層の各膜厚よりも大きく、井戸層のうち、少なくとも1層の膜厚が他の井戸層とは異なるように構成されている。

(もっと読む)

1,101 - 1,110 / 3,539

[ Back to top ]