ローム株式会社により出願された特許

3,431 - 3,440 / 3,539

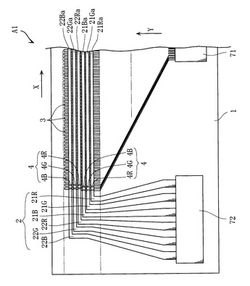

有機EL発光モジュールおよび光プリンタ

【課題】印刷の高精細化を図りつつ、信号電極線の増加を抑制し駆動制御手段への機能負担を軽減することが可能な有機EL発光モジュールを提供すること。

【解決手段】それぞれの主走査方向Xに延びる部分21Ra〜22Baが副走査方向Yに並び、各色用に複数ずつ設けられた走査電極線2と、それぞれの副走査方向Yに延びる部分が複数の走査電極線2と交差するように主走査方向Xに並んだ複数の信号電極線3と、複数の走査電極線2と、複数の信号電極線3との交差部分においてこれらに挟まれた有機層からなる複数ずつの各色用の発光部4と、複数の走査電極線2と複数の信号電極線3とを介して複数ずつの各色用の発光部4を発光駆動させる信号駆動IC71および走査駆動IC72を備えており、各色用の複数の発光部4は、互いの主走査方向Xにおける位置が一定ピッチを隔てて異なり、かつ、各色用の複数の走査電極線2に沿って複数列をなす配置とされている。

(もっと読む)

ピークホールド回路、それを備えるモータ駆動制御回路、及びそれを備えるモータ装置

【課題】 モータ駆動電流検出電圧の保持すべきピーク電圧が微小であっても安定して動作するピークホールド回路の提供。

【解決手段】 このピークホールド回路14は、モータ駆動電流検出電圧を一定電圧だけシフトするレベルシフト回路50と、レベルシフト回路50の出力電圧と出力端子OUTの電圧を入力し、それらの差を増幅して出力する差動増幅回路60と、ベースに差動増幅回路60の出力電圧を入力し、エミッタから充電電流を出力する出力トランジスタ81と、充電電流により充電され出力端子OUTの電圧を保持するコンデンサ82と、レベルシフト回路50の一定電圧と実質的に等しい電圧を生成するバイアス素子84と、バイアス素子84と出力端子OUTの間に設けられコンデンサ82の放電電流を制御する抵抗素子83と、を備えてなる。

(もっと読む)

クロック制御回路

【課題】 クロック信号に起因するEMIを低減する際、ハザードやスパイクを回避するための回路設計が面倒になることがある。

【解決手段】 クロック制御回路10において、遅延回路群100は、入力クロック信号INを段階的に遅延せしめる第1〜第63遅延回路201〜263、および入力クロック信号IN自体を出力する仮の第0の遅延回路を含む。選択回路30は、第0から第63の遅延回路それぞれの出力信号DLY0〜DLY63のいずれかを選択する。制御回路40は、選択回路30によって選択された出力信号の立ち下がりや立ち上がりを契機とし、選択回路30によって異なる信号が選択されるよう制御する。これにより、入力クロック信号INに対し段階的に遅延されたクロック信号を順に出力することができ、入力クロック信号INと周期が異なる信号を出力できる。出力される信号の周波数が変化するため、スペクトルを拡散でき、EMIを低減できる。

(もっと読む)

半導体集積回路

【課題】 内蔵メモリの不良原因の解析時間を短縮することができると共に、内蔵メモリの不良原因解析用の回路規模を小さくすることができる半導体集積回路を提供することを目的とする。

【解決手段】 アドレス・データ生成部5はRAM1〜4の夫々の対象アドレスにテストデータを書き込む。照合部7は、RAM1〜4の夫々の対象アドレスに実際に記憶されたデータを読み出し、記憶データの夫々と期待値としてのテストデータとを照合する。記憶データの何れかとテストデータに相違があった場合、保存データ生成部8は、その相違内容を示すデータと相違の生じているRAMが何れのRAMであるかを表すデータと対象アドレスを表すデータとを含む保存データをRAM1に設けられた保存データ格納領域に保存する。

(もっと読む)

繊維強化複合材料

【課題】温度条件や波長等に影響を受けることなく、常に高い透明性が維持され、かつ、繊維とマトリクス材料との複合化により様々な機能性が付与された繊維強化複合材料を提供する。

【解決手段】繊維集合体と、該繊維集合体に含浸されたマトリクス材料とを備える繊維強化複合材料であって、該繊維集合体の走査電子顕微鏡画像を二値化して得た二値画像から作製した一方向ランレングス画像を統計解析して得られる、該繊維集合体の空孔領域に相当する明所領域の線分長さをLとしたとき、L≧4.5μmの線分の合計長さが、全解析長さの30%以下である繊維強化複合材料。≧4.5μmRL割合が30%以下という、ナノサイズの微細繊維が極めて微細かつ緻密なネットワークを形成した三次元交叉構造体よりなる繊維集合体にマトリクス材料を含浸させたものである。

(もっと読む)

透明積層体

【課題】温度条件や波長等に影響を受けることなく、常に高い透明性が維持され、軽量で、かつ、基材と透明導電膜との線熱膨張係数差に起因する透明導電膜の破損、それによる導電性の低下や、繰り返し応力等によるそれ自体の破損の問題のない透明導電膜形成透明積層体を提供する。

【解決手段】平均繊維径が4〜200nmの繊維とマトリクス材料とを含有し、50μm厚換算における波長400〜700nmの光線透過率が60%以上である繊維強化複合材料よりなる基材の表面に透明導電膜が形成されてなる透明積層体。該繊維がセルロース繊維であり、該透明導電膜が複合金属酸化物であることが好ましい。

(もっと読む)

共有バス調停システム

【課題】 小規模な回路構成で共有バスの調停を実現すると共に、チップサイズの縮小化に寄与し、更に共有バスを共有するCPU等の数の変更に対して簡単に対応できる共有バス調停システムを提供することを目的とする。

【解決手段】 システムクロックを発生するシステムクロック発生回路6と、複数のCPU(1、2及び3)と、各CPUの駆動条件を記憶するレジスタ21、22及び23と、CPU1、2及び3に共有される共有バス8と、システムクロックに同期してカウント値を更新するカウンタ7とが備えられている。各CPUは、カウント値が自身の駆動条件を満たす時に共有バス8の使用権を獲得し、駆動条件の夫々は、同一のカウント値に対して2以上のCPUの駆動条件が同時に満足することがないように定められている。

(もっと読む)

A/D変換装置、およびこれを用いた通信機器

【課題】A/D変換器の直線性誤差、D/A変換器の直線性誤差、A/D変換器とD/A変換器とのマッチング誤差を完全にキャンセルする、オフセットキャンセル機能を有するA/D変換装置を提供すること。

【解決手段】A/D変換器の入力側にアナログオフセットキャンセラーを設け、A/D変換器の出力側にディジタルオフセットキャンセラーを設ける。そして、まず第1段階でアナログオフセットキャンセラーにて、入力レンジをシフトするように大きなオフセットをキャンセルする粗調整を行う。次いで、第2段階でディジタルオフセットキャンセラーにて、残留オフセットをキャンセルする微調整を行う。

(もっと読む)

プリントヘッドの駆動方法およびそれを利用したプリンタ

【課題】 プリンタヘッドを小型化する。

【解決手段】 プリントヘッド10は、走査方向の機構画素のサイズを、本来の印字画素をひとつ印画するために必要なサイズの1/n(nは2以上の整数)の大きさで形成する。ここでは、nを2とするが、2以上の整数であってもよい。データ入力部54は、プリンタ100で印画すべき画像データを図示しないインターフェースを介して入力する。制御部50は、モータ52を介して、プリントヘッド10を走査方向に送る。その際、本来の印字画素をひとつ印画するために必要なサイズの1/nの幅を単位にして、プリントヘッド10を送る。一方、制御部50は、垂直方向に対して、プリントヘッド10を移動させない。

(もっと読む)

半導体装置及びそれを用いた電源回路装置

【課題】グリッドアレイ端子構造の半導体装置において、スイッチ回路がつながる端子の発熱を低減して溶解の危険性を少なくすること。

【解決手段】BGAなどのグリッドアレイ端子構造の半導体装置に内蔵されるスイッチ回路の出力端を、グリッドアレイ端子のうちの複数の端子に接続する。これにより、1つのアレイ端子に流れる電流を許容電流レベル内に低減し、また、ICソケットとの接触抵抗による発熱量を低減する。また、複数の端子の各端子間に1つ以上の他の端子が存在するように配置し、また、複数の端子の全てをグリッドアレイ端子のうちの最外周に配置する。

(もっと読む)

3,431 - 3,440 / 3,539

[ Back to top ]