ローム株式会社により出願された特許

31 - 40 / 3,539

発光素子の駆動回路およびそれを用いた発光装置および電子機器

【課題】スキャニング動作時の発光素子の輝度を安定化する。

【解決手段】誤差増幅器10は、n個のLED端子それぞれの電圧VLED1〜VLEDnのうち最も低い電圧と所定の基準電圧VREFの誤差にもとづき、基準電圧VREFの方が高いときに誤差に応じたソース電流ISRCを生成し、基準電圧VREFの方が低いときに誤差に応じたシンク電流ISINKを生成し、FB端子に生ずるフィードバック電圧VFBを変化させる。誤差増幅器10は、ソース電流ISRCとシンク電流ISINKの両方を生成可能な第1状態φ1と、ソース電流ISRCのみ生成可能な第2状態φ2と、が切りかえ可能に構成される。

(もっと読む)

角速度検出装置

【課題】本発明は、振動子から検出した信号に含まれる不正振動ノイズの影響を抑え、予め定められた値以上のSN比を確保して歩留まりを改善することができる角速度検出装置を提供する。

【解決手段】本発明は、コリオリ力に応じた電気信号SR,SLと、コリオリ力に応じて変化しない基準信号FBとを検出することが可能な振動子と、振動子を駆動する駆動回路2と、振動子から検出した電気信号SR,SLに対して予め定められた処理を行ない角速度を検出する検出回路1とを備える角速度検出装置である。検出回路1は、振動子から検出した電気信号SR,SLと基準信号FBとの差分演算を行ない、電気信号SR,SLから振動子に生じている不正振動によるノイズを除去する駆動ノイズキャンセル回路12を有している。

(もっと読む)

オーディオ信号処理回路およびそれを用いた電子機器

【課題】オーディオ信号処理回路100のノイズを抑制する。

【解決手段】非反転アンプ14は、第3演算増幅器OA3および分圧回路R1、R2を含み、第1バッファ10の出力電圧を非反転増幅する。スイッチSW2は、第3演算増幅器OA3の出力端子とその反転入力端子の間に設けられる。制御回路20は、第2電源電圧VCC2が所定のしきい値電圧より低いときにスイッチSW2をオンし、第2電源電圧VCC2がしきい値電圧より高いときにスイッチSW2をオフする。

(もっと読む)

光検出装置

【課題】近接センサ及び照度センサを1チップ化する場合、チップ面積を削減することができる光検出装置を提供することを目的としている。

【解決手段】受光部は、第1の受光素子50と第2の受光素子51が半導体を用いて一体的形成されている。第1の受光素子50と第2の受光素子51に共通なp型基板1を備えている。第1の受光素子50では、第1のフォトダイオードPD1、第2のフォトダイオードPD2、第3のフォトダイオードPD3が受光面から異なる深さに形成されている。第2の受光素子51は赤外線透過フィルタ20を備え、第4のフォトダイオードPD11、第5のフォトダイオードPD12、第6のフォトダイオードPD13が受光面から異なる深さに形成される。可視光領域に感度ピークを有する第1の受光素子50から出力される光電流と赤外線領域に感度ピークを有する第2の受光素子から出力される光電流から周囲光の照度を測定する。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極の微細化と表面電極の縮小化とを両立することができる半導体装置、および表面電極の大きさに関わらず、表面電極に対して貫通電極を確実にコンタクトさせることができる半導体装置の製造方法を提供すること。

【解決手段】Si基板29の表面13に複数の絶縁膜リング32を選択的に形成し、絶縁膜リング32の開口42に対向するように表面パッド33を形成する。次に、Si基板29を裏面14からエッチングすることにより、絶縁膜リング32の開口42を通過して表面パッド33に達する貫通孔56を形成し、貫通孔56の側面にビア絶縁膜35を形成した後、貫通孔56に電極材料を充填することにより、表面パッド33に電気的に接続されるように貫通電極17を形成する。

(もっと読む)

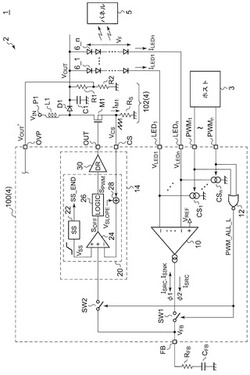

発光素子の駆動回路およびそれを用いた発光装置および電子機器

【課題】バースト調光の再点灯時の突入電流を抑制する。

【解決手段】PWM_ALL_L信号がアサートされるタイミングにて、第1サンプルホールド回路40は、フィードバック電圧VFBをサンプルホールドして電圧VFB_Hを生成し、第2サンプルホールド回路50は、検出電圧VOUT’をサンプルホールドしてしきい値電圧VTHを生成する。パルス変調器20は、(i)PWM_ALL_L信号がネゲートされるときFB端子に生ずるフィードバック電圧VFBにもとづき、(ii)PWM_ALL_L信号がアサートされるときサンプルホールドされたフィードバック電圧VFB_Hにもとづき、パルス信号SPWMを生成する。スイッチングトランジスタM1は、VOUT’<VTHのとき、またはPWM_ALL_L信号がネゲートされるとき、パルス信号SPWMにもとづいて駆動され、それ以外のときオフする。

(もっと読む)

タッチパネルの制御回路、制御方法およびそれらを用いたタッチパネル入力装置、電子機器

【課題】抵抗膜方式タッチパネルにおいて、フリック入力を検出する。

【解決手段】座標検出部110は、第1端子P1から第4端子P4の状態にもとづき、ユーザが接触した座標を検出する。第1容量検出回路30xは、第1端子P1および第2端子P2のひとつである第1検出端子と接続され、第1検出端子からみたパネルの容量を検出する。フリック入力判定部120は、第1検出端子の容量の時間波形にもとづき、第2方向に対するフリック入力の有無を判定する。

(もっと読む)

過電流保護回路及びこれを用いたスイッチング電源装置

【課題】過電流保護値に適切な負の温度特性を持たせる。

【解決手段】過電流保護回路18は、抵抗値の異なる抵抗A1、A2を含む抵抗部Aと、抵抗A1、A2に現れる電圧V1、V2を比較して過電流保護信号S1を生成する比較部Bと、抵抗A1、A2にスイッチ素子12の降下電圧(SW−PGND)を印加する入力部Cと、電流値の等しい電流I1、I2を生成して抵抗A1、A2に供給する電流生成部Dとを有し、電流生成部Dは、抵抗A1、A2と同一の温度特性を有しており、温度特性のフラットな基準電圧BGから基準電流Ixを生成する抵抗D10と;スイッチ素子12と同一の温度特性を有しており、基準電流Ixから基準電圧Vxを生成する抵抗D7と;負の温度特性を有しており、基準電圧Vxから基準電流Iyを生成する抵抗D8と;基準電流Iyから電流I1、I2を生成するカレントミラー(D1〜D4)と;を含む。

(もっと読む)

半導体装置およびその製造方法、電子部品

【課題】貫通電極におけるボイドの発生を防止することができ、従来に比べて信頼性の高い半導体装置およびその製造方法、ならびに電子部品を提供すること。

【解決手段】Si基板29上のゲート絶縁膜30上に電極層51を形成する。ゲート絶縁膜30上に層間絶縁膜31を形成した後、ダマシン法により電極層51と同一パターンの下側配線42と、反対パターンの下側絶縁膜43を含む下側パッド40を形成する。次に、貫通孔59を形成し、同時に、貫通孔59内に下側絶縁膜43と同一パターンの突出部60が形成された第1層間絶縁膜32を露出させる。そして、突出部60の一部がエッチング残渣として残るように第1層間絶縁膜32をエッチングした後、ビア絶縁膜38を形成し、貫通孔59の底面のビア絶縁膜38をエッチングする。次に、貫通孔59のビア絶縁膜38の内側に電極材料をめっき成長させることにより、貫通電極17を形成する。

(もっと読む)

半導体装置およびそれを備えた電子機器

【課題】小型化が可能な構成で、静電容量を正確に検出することができる半導体装置およびそれを備えた電子機器を提供する。

【解決手段】半導体装置1は、チップサイズパッケージ型半導体チップ2と、実装基板3と、検出対象物との間の静電容量を検出するための検出電極20と、検出電極20を取り囲むシールドとを含む。半導体チップ2は、内部回路8を構成する素子が作り込まれた半導体基板4と、半導体基板4の表面を封止する樹脂6と、樹脂6の表面から突出し、内部回路8に電気的に接続された突起電極7とを有する。実装基板3は、半導体チップ2の樹脂6の表面に対向して配置され、半導体チップ2がフリップチップ接合によって実装される実装面21を有する。検出電極20は、半導体チップ2または実装基板3に設けられており、シールドの少なくとも一部が実装基板3に設けられている。

(もっと読む)

31 - 40 / 3,539

[ Back to top ]