東芝マイクロエレクトロニクス株式会社により出願された特許

1 - 10 / 376

半導体装置の製造方法

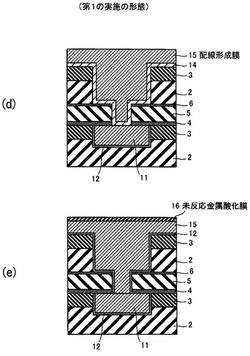

【課題】配線中に残留した不純物金属の濃度が少ない半導体装置の製造方法を提供する。

【解決手段】半導体基板上に絶縁膜を形成し、絶縁膜に凹部を形成し、凹部の形成された絶縁膜の表面に所定の金属元素を含む前駆体膜を形成し、前駆体膜上に配線形成膜を堆積させ、酸化雰囲気下で熱処理を施すことにより、前駆体膜と絶縁膜を反応させ、その境界面に所定の金属元素と絶縁膜の構成元素を含む化合物を主成分とする自己形成バリア膜を形成し、未反応の所定の金属元素を配線形成膜内に拡散移動させて配線形成膜表面で雰囲気中の酸素と反応させ、未反応金属酸化膜として析出させ、未反応金属酸化膜を除去し、未反応金属酸化膜を除去する工程の後、配線形成膜上に、配線形成膜と同一の材料を堆積させて、配線形成膜を積み増した後、凹部外の絶縁膜が露出するまで配線形成膜を平坦化して配線構造を形成する。

(もっと読む)

低消費電力回路

【課題】起動動作時における電流の増大を必要最小限に抑え、安定した起動動作が可能で、小型な低消費電力回路を提供する。

【解決手段】第1発振トランジスタP31、第1発振トランジスタP31のドレイン端子にドレイン端子を接続した第2発振トランジスタN31、第1容量C2、第1容量C2に一方を接続し、他方を第1発振トランジスタP31と第2発振トランジスタN31の接続ノードに接続した圧電振動子Q1、一方を圧電振動子Q1に接続し、他方を第1発振トランジスタP31のゲート端子に接続した帰還抵抗回路Z3、第1発振トランジスタP31のゲート端子VP1に第1端子を接続し、接続ノードに第2端子を接続した第1振幅制限素子P32、第2発振トランジスタN31のゲート端子VN1に第2端子を接続し、接続ノードに第1端子を接続した第2振幅制限素子N32とを備える。

(もっと読む)

記憶装置

【課題】不揮発性メモリに格納された情報が外部へ漏洩するのを防ぐことによりセキュリティ機能を向上させる。

【解決手段】ネットワークを介して管理サーバ300と接続可能な記憶装置1であって、不揮発性メモリ200と、不揮発性メモリ200を制御するコントローラ100とを含む。コントローラ100は、固有のIDを管理サーバ300に送信する送信部142と、IDに応じて管理サーバ300から送信される使用権を判定する判定部143と、使用権が認められない場合に、外部からのアクセスを禁止する禁止処理部144とを含む。

(もっと読む)

半導体装置

【課題】メモリへの書き込みにエラーが発生しても、書き込もうとしたデータが消失することを防ぐことのできる半導体装置を提供する。

【解決手段】キャッシュメモリ1が、キャッシュロック機能と主メモリへの書き込み時にそのデータを有するキャッシュラインをロックする機能を有し、書き込み履歴バッファ2が、キャッシュメモリ1から主メモリ200への書き込みが行われたキャッシュラインの情報を記憶し、メモリコントローラ3が、キャッシュメモリ1から主メモリ200への書き込み時のエラー発生有無を検証して書き込み検証信号を出力し、キャッシュロック制御部4が、書き込み検証信号が主メモリ200への書き込みが正常であることを示すときは、書き込み履歴バッファ2に記憶されているライン情報を検索して、書き込みを行おうとしたデータが格納されているキャッシュラインを特定し、そのキャッシュラインのロック解除をキャッシュメモリ1へ要求する。

(もっと読む)

半導体装置

【課題】半導体チップ上に積層された半導体チップの放熱を改善することが可能な半導体装置を提供する。

【解決手段】周辺部に接続パッド22を有するパッケージ基板21、上面の周辺部に形成された接続パッド12、及び上面の接続パッド12より内側に形成され、接続パッド12に接続された接続パッド13を有し、下面をパッケージ基板21に固定された半導体チップ11、下面の最も外側の周辺部を取り巻く1列が、電源または接地に接続された接続パッド16を有し、下面の接続パッド16の列より内側に、信号線に接続された接続パッド17を有し、接続パッド16及び接続パッド17が半田バンプ25を介して対応する位置の接続パッド13に電気的に接続且つ固定された半導体チップ15、並びに、接続パッド16が半田バンプ25及び接続パッド13を経由して接続された接続パッド12と、接続パッド22とを電気的に接続する金属細線27を備える。

(もっと読む)

電圧制御発振器

【課題】電源電圧が変動した場合でも発振周波数のばらつきを抑制する。

【解決手段】電圧制御発振器4には電圧電流変換回路10、駆動電流補整回路11、及び発振回路20が設けられる。電圧電流変換回路10は制御電圧Vvcoが入力され、制御電圧Vvcoに応じた電圧電流変換された駆動電流を生成する。高電位側電源VDDと低電位側電源VSSの間の電源電圧の変動が発生した場合、駆動電流補整回路11は電圧電流変換回路10から出力される駆動電流の補整を行う。駆動電流補整回路11により補整された駆動電流が発振回路20に供給され、発振回路20で制御電圧Vvcoに応じた発振周波数が生成される。

(もっと読む)

発光素子のドライブ回路

【課題】少ない消費電流で故障検出が行える動作モードを有する発光素子のドライブ回路を提供する。

【解決手段】外部電源11と出力端子12との間に接続される発光素子13を駆動する電流Icを制御する電流制御回路14と、出力端子12の電圧をモニターして、発光素子13の不点灯状態を検出し、検出結果を外部に出力する故障検出回路15と、を具備し、電流制御回路14は、発光素子13をオンおよびオフしてパターンを表示する第1動作モードのときに、発光素子13を第1の電流Ic1で駆動し、発光素子13の故障検出を行う第2動作モードのときに、発光素子13を第1の電流Ic1より小さい第2の電流Ic2で駆動する。

(もっと読む)

スタンダードセルおよびそれを用いた自動配置配線方法

【課題】半導体装置設計時の自動配置配線における配線ショートによるセル再配置を抑制する。

【解決手段】本発明のスタンダードセルおよびそれを用いた自動配置配線方法は、回路素子が配置される矩形の素子領域11と、素子領域11の対向する2辺と同じ幅で対向する2辺に近接して設けられ、上層配線が配置される矩形の追加配線領域12a、12bを有する。

(もっと読む)

半導体装置

【課題】半導体チップを分けることによって性能を引き出すことが可能なスタック形MCPの半導体装置を提供する。

【解決手段】接続パッド32を有する実装基板31、上面に論理回路が形成され、下面を実装基板31上に固定された半導体チップ11、下面に、受動素子を有するPLL20が形成され、下面を、半田バンプ35を介して半導体チップ11の上面に電気的に接続且つ固定された半導体チップ15、及び、半導体チップ11と実装基板31の接続パッド32とを電気的に接続する金属細線37とを備えている。

(もっと読む)

固体撮像装置

【課題】出力信号にリセットノイズが含まれなくなり、信号変換レートを速くしようとした時でもリセットノイズによる制限を受けなくなり、信号変換レートの速い出力信号が得られる固体撮像装置を提供する。

【解決手段】2つの電荷電圧変換部14、18を有し、位相の異なる2相のリセットパルス信号CK1、CK2に基づいて各電荷電圧変換部14、18をリセットし、それぞれの出力信号をスイッチ回路30で交互に切り換えて出力する。

(もっと読む)

1 - 10 / 376

[ Back to top ]