株式会社進化システム総合研究所により出願された特許

1 - 3 / 3

パラメータ調整装置

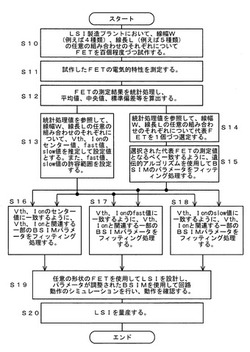

【課題】トランジスタなどの半導体素子の物理モデルの多数のパラメータを短時間で調整可能なパラメータ調整装置を提供すること。

【解決手段】パラメータ調整装置は、BSIM等の半導体素子の物理モデルの複数のパラメータの少なくとも一部を遺伝子とする個体を定義し、FETのゲート幅W、ゲート長Lの複数の組み合わせについてそれぞれ設定されたセンターFET、BEST-FET、WORST-FETのしきい値電圧値Vthおよびオン電流値Ionの設定値に合致し、かつ物理モデルの計算値が設定値の一方の側に来るように遺伝的アルゴリズムを使用して物理モデルのパラメータを最適化するパラメータ調整手段を備える。BEST-FET、WORST-FETのモデルについてはモデルの計算値が設定値より外側になるようにBSIMパラメータを調整することが可能である。

(もっと読む)

遺伝的アルゴリズム実行装置および遺伝的アルゴリズム実行方法

【課題】遺伝的アルゴリズムにおいて最適解に近づく速度の向上を維持しつつ、広域探索による局所解からの離脱可能性の向上を両立させること。

【解決手段】遺伝的アルゴリズム実行装置は、親個体21の収束状態を示す混雑度を求め、更に前記混雑度から突然変異確率を決定する突然変異確率決定手段22と、前記突然変異確率に基づき、前記個体の遺伝子情報に突然変異処理を施す突然変異処理手段23とを備える。母集団20において局所解の固体が支配的になった場合には混雑度が増加するので突然変異確率が増加し、広域探索機能がより強化さる。このような突然変異確率を動的に制御する特殊な突然変異処理によって、最適解に近づく速度の向上という効果を維持しつつ、局所解に捕らわれずに最適解に到達する確率が向上するという効果を両立させることができる。

(もっと読む)

不良救済判定装置および不良救済判定方法

【課題】処理時間を大幅に増加させることが無い、高精度な不良救済判定装置および不良救済判定方法を提供すること。

【解決手段】不良救済判定装置は、記憶回路の行あるいは列と置換可能な複数の冗長回路を備えたメモリチップの不良ビット位置情報に基づき、従来のアルゴリズム及び遺伝的アルゴリズムを併用してメモリチップの救済パターンの探索を行う。探索手段は、遺伝的アルゴリズムにおける各固体の染色体として、行の冗長回路数と対応した数の遺伝子を有する第1の染色体と、列の冗長回路数と対応した数の遺伝子を有する第2の染色体とを備え、第1の染色体の遺伝子はメモリチップの不良行番号を記憶し、第2の染色体の遺伝子はメモリチップの不良列番号を記憶する。従来よりも救済可能なチップ数が増加し、歩留まりが向上する。全体としては救済処理に関する処理時間の増加はわずかである。

(もっと読む)

1 - 3 / 3

[ Back to top ]