ルネサスエレクトロニクス株式会社により出願された特許

91 - 100 / 8,021

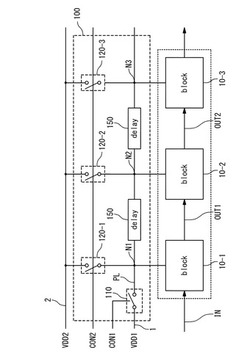

半導体装置

【課題】半導体装置の回路ブロックへの電力供給復帰時に、無駄な充放電を削減すること。

【解決手段】半導体装置は、第1電源電圧を供給する第1電源線と、第1電源電圧よりも高い第2電源電圧を供給する第2電源線と、前段回路ブロックと、前段回路ブロックの出力信号に基づいて動作する後段回路ブロックと、前段回路ブロック及び後段回路ブロックに対する第1電源電圧及び第2電源電圧の供給を制御する電力供給制御回路と、を備える。電力供給制御回路は、後段回路ブロックへの第1電源電圧の供給開始タイミングを前段回路ブロックへの第1電源電圧の供給開始タイミングよりも遅延させる。更に、電力供給制御回路は、前段回路ブロック及び後段回路ブロックに第1電源電圧が供給された後に、第2電源電圧を前段回路ブロックと後段回路ブロックの両方に供給する。

(もっと読む)

半導体装置の製造方法

【課題】電界効果トランジスタを有する半導体装置のトランジスタ性能を向上させることのできる技術を提供する。

【解決手段】ゲート絶縁膜5およびゲート電極6n,6pの側面にサイドウォール9を形成した後、サイドウォール9の両側の半導体基板1に不純物をイオン注入して不純物領域を形成する。続いて、半導体基板1の主面上に第1絶縁膜14、第2絶縁膜15、および第3絶縁膜16を順次形成した後、イオン注入された上記不純物を活性化する熱処理を行う。ここで、第1絶縁膜14は、第2絶縁膜15よりも被覆性のよい膜であり、かつ、第2絶縁膜15とエッチング選択比が異なる膜である。第2絶縁膜15は、第1絶縁膜14よりも水素の拡散を阻止する機能が高い膜である。第3絶縁膜16は、第1絶縁膜14および第2絶縁膜15よりも内部応力の変化が大きい膜である。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

妨害波検出回路、受信装置および妨害波検出方法

【課題】デジタル変調方式に基づく無線通信において、目的電波と比較して低レベルの妨害波を受信信号の中から検出できるようにすること。

【解決手段】妨害波検出回路は、受信したアナログ信号をデジタル復調して得られた時系列信号の各時点における信号点に対する収束点を推定する収束点推定部と、時系列信号と収束点との各時点における差分を誤差信号として算出する誤差算出部と、誤差信号を時間領域から周波数領域へ変換する変換部と、周波数領域に変換された誤差信号に基づいて、時系列信号に含まれる妨害波の成分を検出する検出部と、を備える。

(もっと読む)

周辺機器及びその電源制御方法

【課題】ホスト側のハードウェアの変更を行わずに周辺機器の電源を制御することを可能にする周辺機器及びその電源制御方法を提供すること

【解決手段】本発明にかかるExpressCard10は、PCI Express、USB2.0によるデータ伝送を実行する入出力インタフェース23、24を備えるホスト20との間でデータ伝送を実行する。ExpressCard10は、データを伝送し、処理を実行する制御部12と、PCI Express、USB2.0によるデータ伝送を媒介する入出力インタフェース13、14と、ホスト20から出力されたUSB2.0によるデータを判定し、当該データが電源制御データである場合には制御信号を出力し、当該データが電源制御データでない場合には当該データを入出力インタフェース14に出力するUSBブリッジ回路15と、制御信号に応じて制御部12への電源の供給を制御する電源制御部16を備える。

(もっと読む)

クロックデータリカバリ回路およびそれを内蔵する送受信半導体集積回路

【課題】高いジッタ耐性を有して多相クロックの位相数と消費電力と半導体チップ面積との増大を軽減する。

【解決手段】クロックデータリカバリ回路1のエッジ検出器105の複数のエッジ検出回路105Mの各回路は、第1と第2のエッジ検出回路105M1、2を含む。第1の検出回路105M1は受信データ信号のデータエッジがエッジ検出位相から−1位相よりも進相なことを検出して第1出力信号を生成して、第2の検出回路105M2は受信データ信号のデータエッジがエッジ検出位相から+1位相よりも遅相なことを検出して第2出力信号を生成する。第1または第2の出力信号に応答して、エッジ検出位相が−1位相分または+1位相分変更される。受信データ信号のデータエッジの±1位相の範囲内の存在が検出された場合には、次回のエッジ検出位相は現在の状態に維持される。

(もっと読む)

配線設計装置、配線設計方法、及びプログラム

【課題】半導体集積回路に対し、ダミーパターン配置後に、ダミーパターンを使用したECO(Engineering Change Order)配線設計を行う。

【解決手段】配線設計装置は、半導体集積回路にダミーパターンを配置し、ダミーパターンをECO配線に変更し、ダミーパターンの再配置及び電気的ショートを発生することなくECO配線を行う。これにより、ECO配線を行う時に、ダミーパターン再挿入や、既存配線とのショートを発生せずに、設計TAT(Turn Around Time)増を抑制することを可能とする。

(もっと読む)

マイクロコンピュータおよびデータ処理装置

【課題】マイクロコンピュータにおいて、半導体素子としてのデッドコピーを防止し、また、プログラムやデータなどのメモリの内容を読み取ることができないように秘匿する。

【解決手段】マイクロコンピュータのプログラムおよびデータを、半導体チップが製造された結果である物理的特性に基づいて生成された識別情報を暗号鍵として暗号化する。マイクロコンピュータは、物理的特性に基づいて識別情報を生成する手段とその識別手段を暗号鍵としてプログラムやデータを暗号化する暗号エンジンを備えるものであって、暗号化に用いた暗号鍵の値の読み出しが禁止されている。

(もっと読む)

遅延回路及びそれを用いた半導体装置

【課題】入力信号に精度の高い遅延を付加した出力信号を生成することが可能な遅延回路を提供すること。

【解決手段】本発明にかかる遅延回路は、第1電流I0及び第1電流I0と略同一の第2電流I0を生成する電流ミラー回路と、ゲートに基準電圧Vrが印加されソース−ドレイン間に第1電流I0が流れることにより電圧V0を生成するトランジスタ607と、電圧V0に応じた参照電圧V1を生成する抵抗素子608,609と、コンデンサ613と、第2電流I0の電荷をコンデンサ613に蓄積し、又は、コンデンサ613に蓄積された電荷を放出する充放電部と、充放電部とコンデンサ613との間に設けられ、ゲートに基準電圧Vrが印加されソース−ドレイン間に第2電流I0が流れることにより、比較電圧V2を生成するトランジスタ611と、比較電圧V2と参照電圧V1とを比較し比較結果を出力信号Voutとして出力する電圧比較部619と、を備える。

(もっと読む)

半導体装置の製造方法、及び、リード切断装置

【課題】切断屑の飛散と切断屑の残留とを簡易な構成により抑制する。

【解決手段】半導体装置の製造方法は、半導体装置200の外部リード(リード201)の先端部202をダイ20と押さえ部材40とで挟持した状態で、ダイ20とパンチ50とによる剪断によって先端部202を切断する工程と、ダイ20と押さえ部材40とを離間させる工程を有する。押さえ部材40には、押さえ部材40におけるダイ20側の面よりダイ20側に突出する弾性体(例えば板状弾性体80)が設けられている。ダイ20と押さえ部材40とで外部リードを挟持する際には、弾性体をダイ20により押してダイ20とは反対側へ弾性変形させる。ダイ20と押さえ部材40とを離間させることにより、弾性体をダイ20側へ弾性復帰させ、切断により切断屑203となった先端部202を弾性体によって押さえ部材40及びダイ20から払い除ける。

(もっと読む)

91 - 100 / 8,021

[ Back to top ]