ルネサスエレクトロニクス株式会社により出願された特許

1,061 - 1,070 / 8,021

記憶装置

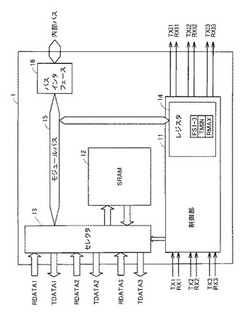

【課題】複数の通信インタフェースによる送受信データを1つのデータバッファにバッファリングすることが可能な記憶装置を提供すること。

【解決手段】TMINレジスタは、複数の通信インタフェースのデータ送受信周期の中の最小周期のサイクル数が設定される。RMAXレジスタは、最小周期のサイクル数から複数の通信インタフェースの中の動作中のチャネル数を差し引いた値が設定される。制御部11は、最小周期中において、複数の通信インタフェースによるSRAM12への受信データの書込み要求およびSRAM12からの送信データの読出し要求を受け付けて順次実行し、バスマスタに対する受信データの読出し要求および送信データの書込み要求の回数がRMAXレジスタに設定される値以下となるようにバスマスタに対する要求を行なう。したがって、TMIN期間内に各チャネルのアクセスを処理することができ、リアルタイム性を確保することが可能となる。

(もっと読む)

半導体装置

【課題】トレンチゲート縦チャネル型パワーMOSFET等は、オン抵抗が低いメリットを有する。しかし、微細化に伴い、オン抵抗のばらつき等が問題となっているほか、構造的問題から微細化の限界が問題となってきている。これらの問題は、単体のパワーMOSFET等のみの問題ではなく、同様の構造を適用しているIGBT等のように、CMOS等とこれらのパワー能動デバイスを単一のチップ上に集積した集積回路装置に於いても重要な問題である。

【解決手段】本願発明は、トレンチゲート縦チャネル型パワーMOSFET等のトレンチゲート縦チャネル型パワー系能動素子を有する半導体装置に於いて、層間絶縁膜の幅とトレンチの幅をほぼ同一にするとともに、ソース領域の一部をポリシリコン部材により構成したものである。

(もっと読む)

半導体装置及びその製造方法

【課題】寄生バイポーラトランジスタのゲインを低下することにより、誤動作や動作特性の変動が少ない半導体装置及びその製造方法を得る。

【解決手段】シリコン層3の上面上には、シリコン酸化膜6が部分的に形成されている。シリコン酸化膜6上には、ポリシリコンから成るゲート電極7が部分的に形成されている。ゲート電極7の下方に存在する部分のシリコン酸化膜6は、ゲート絶縁膜として機能する。ゲート電極7の側面には、シリコン酸化膜8を挟んで、シリコン窒化膜9が形成されている。シリコン酸化膜8及びシリコン窒化膜9は、シリコン酸化膜6上に形成されている。ゲート長方向に関するシリコン酸化膜8の幅W1は、シリコン酸化膜6の膜厚T1よりも大きい。

(もっと読む)

半導体装置

【課題】相変化メモリを低電圧動作および高温の動作又は放置させる場合に、記録保持信頼性を向上させる技術を提供する。

【解決手段】読み出し電圧をセット電圧およびリセット電圧以上として高速動作させ、読み出し後に読み出し前の状態を再書込みする、いわゆる破壊読出しを行う。または、複数個のセルを用いて1ビットの情報を記録する、いわゆるオアセルを用いて、高温時の動作又は放置のける信頼性を向上させる。破壊読出しおよびオアセルを用いた相変化メモリに必要な、回路構成および動作方法を用いる。

(もっと読む)

磁気メモリ

【課題】データ記憶層が強い垂直磁気異方性を有し、かつ、データ記憶層とその下方に設けられた磁化固定層との間の磁気的結合が強い磁気メモリを提供する。

【解決手段】磁気メモリが、垂直磁気異方性を有し、磁化方向が固定された磁化固定層50a、50bと、層間絶縁層60と、磁化固定層50a、50bと層間絶縁層60の上面に形成された下地層40と、下地層40の上面に形成された、垂直磁気異方性を有するデータ記憶層10とを備えている。下地層40は、磁性材料で形成された第1磁性下地層41と、第1磁性下地層41の上に形成された非磁性下地層42とを備えている。第1磁性下地層41の膜厚は、層間絶縁層60の上において第1磁性下地層41が面内磁気異方性を発現しないように調節されている。

(もっと読む)

不揮発性半導体記憶装置

【課題】リードディスターブを効率良く回避するための技術を提供する。

【解決手段】不揮発性半導体記憶装置(1)は、不揮発性記憶部(11)と、上記不揮発性記憶部の消去単位とされるブロック毎のデータを、当該ブロックとは異なるブロックに書き直すためのリフレッシュ処理を制御可能なコントローラ(12)とを含む。上記コントローラは、上記不揮発性記憶部に、第1領域とそれとは異なる第2領域とを設定し、上記第1領域のデータについてのリフレッシュ頻度が、上記第2領域のデータについてのリフレッシュ頻度に比べて高くなるように、リフレッシュトリガが発生される毎に上記第1領域及び上記第2領域についてのリフレッシュ処理を実行する。これにより、リードアクセスが繰り返される場合のリードディスターブを効率良く回避することができる。

(もっと読む)

半導体装置

【課題】より確実に画素間クロストークを抑制することが可能な、固体撮像素子を備える半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に配置された第1導電型の不純物層DPWと、不純物層DPW上に、第1導電型の不純物領域と第2導電型の不純物領域とが互いに接合する構成を含む光電変換素子と、光電変換素子を含む単位画素を構成し、光電変換素子と電気的に接続されるトランジスタM1〜M4とを備えている。平面視において光電変換素子の外周部の少なくとも一部には、内部に空隙AGが含まれ、光電変換素子と、光電変換素子に隣接する光電変換素子とを、互いに電気的に絶縁する分離絶縁層SIが配置されている。上記分離絶縁層SIは、第1導電型の不純物層DPWの最上面に接する。

(もっと読む)

半導体集積回路の設計方法及び半導体集積回路の設計支援装置

【課題】論理回路の面積縮小化を実現しつつ、設計TATの短縮を可能とする技術を提供する。

【解決手段】複合論理マクロセルを、基本マクロセルに置き換えて面積の総和を抽出し、その面積の総和と複合論理マクロセルの面積とを比較して面積縮小化に有効となる複合論理マクロセルを選択する。その選択された複合論理マクロセルにフラグを設定する。フラグを設定したマクロセルと同等の論理を論理情報から検索する論理構造検索処理を行い、置換対象となる基本マクロセルにフラグを設定する。置換対象のフラグを設定した基本マクロセルを、フラグ設定した複合論理マクロセルに置き換える等価論理置換処理を行う。

(もっと読む)

カレントミラー回路およびそれを用いた半導体装置

【課題】プロセス変動があった場合でも広い出力電圧範囲が得られるカレントミラー回路を提供する。

【解決手段】この低電圧カスコードカレントミラー回路は、NチャネルMOSトランジスタQ1〜Q5と抵抗素子1を備える。トランジスタQ3のオーバードライブ電圧Vov_Q3は、トランジスタQ4,Q5のオーバードライブ電圧Vov_Q4,Vov_Q5の和に等しい。定電流Icと抵抗素子1の抵抗値R1との積は、トランジスタQ5の飽和マージンVdsm_Q5となる。したがって、プロセス変動があった場合でも、トランジスタQ5の飽和マージンVdsm_Q5は変化しない。

(もっと読む)

半導体装置

【課題】実装上の自由度を低下させることのない螺旋状インダクタを実現する技術を提供する。

【解決手段】半導体装置100は、実質的に平行に配置された第1半導体基板1及び第2半導体基板2と、第1半導体基板1の第2半導体基板2に対向する面である第1対向面1aに形成され、相互に略平行となる複数の第1パターン3と、第2半導体基板2の第1半導体基板1に対向する面である第2対向面2aに形成され、相互に略平行となる複数の第2パターン4と、複数の第1パターン3と複数の第2パターン4を交互に導通させることで螺旋状インダクタLを形成する複数のバンプ電極5と、を備える。

(もっと読む)

1,061 - 1,070 / 8,021

[ Back to top ]