ルネサスエレクトロニクス株式会社により出願された特許

101 - 110 / 8,021

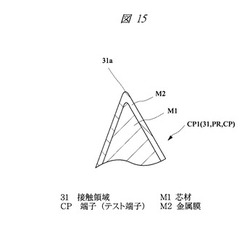

半導体装置の製造方法

【課題】半導体装置の製造効率を向上させる。

【解決手段】半導体チップと電気的に接続された複数の外部端子(リード)と、複数の端子(テスト端子)CPの接触領域31を接触させることで、半導体チップとテスト回路を電気的に接続し、電気的試験を行う。ここで、端子CPは、複数の半導体装置の電気的試験に繰り返し使用するものである。また、端子CPの接触領域31は、第1合金から成る芯材M1と、芯材M1を覆う金属膜M2とを備えている。また、金属膜M2は、第1合金よりも硬度が高い第2合金から成るものである。

(もっと読む)

電流出力回路

【課題】アイドリング電流の影響を受けることなく高精度に電流検出を行うことが可能な電流出力回路を小規模な回路で実現すること。

【解決手段】第1の増幅器と、第1の増幅器の出力を入力するプッシュプル形出力段と、プッシュプル形出力段の第1のトランジスタ及び第2のトランジスタに対して夫々カレントミラー接続した電流検出器の第3のトランジスタ及び第4のトランジスタと、第3のトランジスタのドレインを第1のトランジスタのドレインの電位と等しくするバッファ回路と、第4のトランジスタのドレインに接続された電流検出抵抗と、を備える。プッシュプル形出力段の増幅信号は、負荷を介して第1の増幅器の反転入力端子に接続される。この構成により、電流検出抵抗にアイドリング電流を流さないようにすることができる。

(もっと読む)

不揮発性半導体記憶装置

【課題】低消費電流で正確なデータ読出を行なうことが可能な不揮発性半導体記憶装置を提供する。

【解決手段】このフラッシュメモリでは、4つのメモリマットMAT0〜MAT3の各々にセンスアンプSA0〜SAmを設け、通常の読出動作モードでは、全メモリマットMAT0〜MAT3のセンスアンプSA0〜SAmに参照電圧VRを供給し、低速読出モードでは、選択されたメモリマットMATのセンスアンプSA0〜SAmのみに参照電圧VRを供給する。したがって、低消費電力で正確なデータ読出を行なうことができる。

(もっと読む)

半導体装置

【課題】半導体装置の電気的特性を向上させる。

【解決手段】半導体装置2のパッケージPA内には、パワーMOS・FETが形成された半導体チップ4PH,4PLと、その動作を制御する制御回路が形成された半導体チップ4Dとが内包されている。ハイサイド側の半導体チップ4PHのソース電極用のボンディングパッド12S1,12S2は、金属板8Aを通じてダイパッド7D2に電気的に接続されている。ロウサイド側の半導体チップ4PLのソース電極用のボンディングパッド15S1は、金属板8Bを通じてリード配線7LBに電気的に接続されている。金属板8Bは、半導体チップ4PLのボンディングパッド15S1に接する第1部分8B1と、その第1部分8B1の短辺からリード配線7LBまで延びる第2部分8B2と、第1部分8B2の長辺からリード配線7LBまで延びる第3部分8B3とを有している。

(もっと読む)

不揮発性メモリ及び不揮発性メモリからのデータ読み出し方法

【課題】2つのアンチヒューズ素子を備えるメモリセルから、電流検出によるデータの出力を可能にするセンスアンプを備えた不揮発性メモリが、望まれる。

【解決手段】不揮発性メモリは、一端が、第1の方向に配線された第1の制御線に接続された第1のアンチヒューズ素子と、一端が、第1の方向に配線された第2の制御線に接続され、他の一端が、第1のアンチヒューズ素子と共通接続された第2のアンチヒューズ素子と、第1及び第2のアンチヒューズ素子が共通接続された共通端子と、第1の方向に配線されたビット線との間に接続され、第1の方向と交差する第2の方向に配線されたワード線に印加される電圧により導通非導通が定まるスイッチトランジスタと、からなるメモリセルを複数含むメモリセルアレイと、第1及び第2のアンチヒューズ素子に流れる電流に基づいて、メモリセルに記憶されたデータを出力するセンスアンプと、を備えている。

(もっと読む)

PLL回路

【課題】ディジタル回路で構成されるADPLLにおいて、位相差0近傍における位相差

検出を改善することができる技術を提供する。

【解決手段】基準信号VREFフィードバック信号VDIVとの位相及び周波数を比較するPFDと、PFDの出力をディジタル値に変換するTDCと、TDCの出力から高周波雑音成分を除去するDLFと、DLFの出力に基づいて制御されるDCOと、DCOの出力を分周しフィードバック信号VDIVを出力するDIVによりフィードバックループが構成される。フィードバックループのいずれかの箇所にオフセット値が加算され、フィードバック信号VDIVの位相が制御され、ロック時にもTDCに0ではない値が入力される。

(もっと読む)

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

半導体装置

【課題】外部電源の電圧に応じて、より適切な動作モードや動作周波数を自動的に設定することが可能な半導体装置を提供する。

【解決手段】ある実施の形態に従う半導体装置は、プロセッサと、プロセッサによるアクセスが可能な不揮発性メモリと、少なくともプロセッサおよび不揮発性メモリを駆動するための外部電源の電圧を検出する電圧検出部とを含む。プロセッサは、命令群を実行することで、電圧検出部によって検出された電圧に応じて、プロセッサおよび不揮発性メモリの少なくとも一方についての動作モードおよび/または動作周波数を設定する。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置の内部回路に供給されるクロック信号の周波数が、正常時よりも高くなった場合の上記内部回路の暴走を回避する。

【解決手段】半導体集積回路装置(1)において、内部回路(17)と、水晶振動子を用いた発振動作によりクロック信号を形成する水晶発振回路(11)と、上記内部回路が正常に動作可能な周波数のクロック信号を形成する内蔵発振器(14)とを設ける。また上記水晶発振回路で形成されたクロック信号の周波数が、上記内部回路の正常動作の周波数範囲よりも上昇したことを検出可能な異常高速発振検出回路(13)を設ける。さらに上記異常高速発振検出回路での検出結果に基づいて、上記水晶発振回路で形成されたクロック信号に代えて、上記内蔵発振器で形成されたクロック信号を上記内部回路に供給するための制御回路(16)を設けることで、内部回路の暴走を回避する。

(もっと読む)

半導体装置

【課題】注入元素子から被注入素子への電子の移動を抑制する効果が高く、素子の誤動作を抑制できる半導体装置を提供する。

【解決手段】第1および第2の主表面を有する半導体基板SUB内にはエピタキシャル層EPPと、n型不純物領域NRを含む注入元素子と、注入元素子と間隔を隔てて形成された被注入素子と、注入元素子と被注入素子との間の領域の少なくとも一部に形成され、注入元素子と被注入素子とを結ぶ方向に対して交差する方向に延在する接地電位が印加されたn型領域GNNおよびp型領域GPPを有するバリア層BRとを備える。さらに半導体基板SUB内でエピタキシャル層EPPに接するように形成されたフローティングp型裏面領域FLPを有する。

(もっと読む)

101 - 110 / 8,021

[ Back to top ]