ルネサスエレクトロニクス株式会社により出願された特許

31 - 40 / 8,021

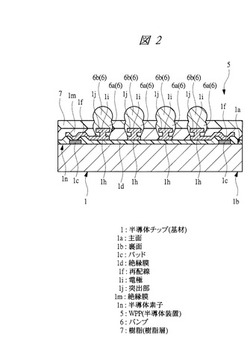

半導体装置及びその製造方法

【課題】半導体装置におけるバンプの接合強度を向上する。

【解決手段】WPP5のバンプ接合において、バンプ6が接合する柱状の電極1iに、水平方向に突出する突出部1jが形成されたことにより、バンプ6の接合強度を向上でき、さらにWPP5の組み立てにおいて、バンプ6の表面を覆うように絶縁膜1m上に樹脂7を配置し、この樹脂7を硬化させた後、樹脂7を研削してバンプ6の一部を露出させることにより、例えばポリイミドからなる絶縁膜1mを樹脂7によって覆うため、耐吸湿性を向上できる。

(もっと読む)

データ処理装置

【課題】高電源電圧で動作する場合に不要な待ち時間を抑制して高速な復帰が可能なデータ処理装置を提供する。

【解決手段】データ処理装置は、演算処理部と協働して動作する周辺部と、第1モードから第2モードへの切り替えの際に起動タイミングを制御するための管理部とを含む。周辺部は、第1モードの際に電源供給が制限されるモジュールと、第1モードから第2モードへの切り替えの際に、モジュールの少なくとも一部の復帰を検知して、検知信号を出力するための復帰検知回路と、電源供給の電圧が低い場合に合わせてモジュール全体が復帰するまで検知信号の管理部への出力を遅延させるための遅延回路とを含む。遅延回路の遅延時間は、電源供給の電圧に従い遅延回路に流れる動作電流に起因して、電源供給の電圧が低い場合よりも電源電圧が高い場合の方が短くなるように調整される。

(もっと読む)

半導体装置

【課題】ハイサイド素子として用いても誤動作が少なく、かつオン耐圧およびオフ耐圧の双方を高く維持することのできる半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBの内部には、p-エピタキシャル領域EP1が、その主表面側にはp-エピタキシャル領域EP2が、その主表面側にはn型ドリフト領域DRIとp型ボディ領域BOとが形成されている。p-エピタキシャル領域EP1とp-エピタキシャル領域EP2との間には、これらの領域を電気的に分離するためにn+埋め込み領域NBが形成されている。n+埋め込み領域NBとp-エピタキシャル領域EP2との間には、p-エピタキシャル領域EP2よりも高いp型不純物濃度を有するp+埋め込み領域PBが形成されている。p+埋め込み領域PBは、n型ドリフト領域DRIとp型ボディ領域BOとの接合部の少なくとも直下に位置し、かつn型ドリフト領域DRIと接するドレイン領域DRAの直下を避けて配置されている。

(もっと読む)

半導体装置の配線構造セルおよび半導体装置のレイアウト設計タイミング調整方法

【課題】複数の動作条件においてもタイミング制約を満たすように遅延時間を調整することを可能にする。

【解決手段】本発明に係る半導体装置の配線構造セルHSCは、M3層に、プロセス基準値bを満たす矩形に形成されたM3層19と、M3層19からプロセス基準値aを満たすよう離間し、口字型に形成されたM3層12と、M3層19の上にプロセス基準値を満たす矩形に形成されたVIA3層15と、M4層にVIA3層15に接して、プロセス基準値cを満たす幅で伸長した矩形に形成されたM4層11と、M3層19の下にVIA3層15と同じ平面形状に形成されたVIA2層16と、M2層にVIA2層16に接して、M4層11と同じ平面形状に形成されたM2層13と、を有するものである。

(もっと読む)

半導体記憶装置

【課題】不揮発性メモリ部内蔵のSRAMの特性の向上を図る。

【解決手段】SRAMを構成するアクセストランジスタAcc1とビット線BLとの間に抵抗変化層Rを有するReRAM部RM1を設け、アクセストランジスタAcc2とビット線/BLとの間に抵抗変化層Rを有するReRAM部RM2を設ける。SRAM通常動作期間の終了時において、例えば、蓄積ノードAに低電位(L=0V)、蓄積ノードBに高電位(H=1.5V)が保持されている場合、ReRAM部RM1をオン状態(ON)とし、ReRAM部RM2をオフ状態(OFF)とすることで、SRAMの保持データをReRAM部へ書き込み、再び、SRAM通常動作となった場合には、蓄積ノードAおよびBに対応するデータ書き戻すとともに、ReRAM部RM1、RM2の双方をオン状態に(リセット)する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

半導体装置

【課題】半導体装置が動作状態から待機状態に移行するとき、内部電源電圧の目標電圧からの上昇を抑制する。

【解決手段】非動作状態の負荷回路への電源電流の供給に用いられる電源回路15において、トランジスタPTRS1は、外部電源電圧を受ける電源ノードと出力ノード18との間に接続される。比較器50は、第1の入力端子および参照電圧が入力される第2の入力端子を有し、第1および第2の入力端子間の電圧差に応じた制御電圧をトランジスタPTRS1の制御電極に出力する。分圧回路40は、出力ノードの電圧を分圧した電圧を比較器50の第1の入力端子に出力する回路であり、分圧比を変更可能である。電源回路15は、負荷回路が動作状態のときに、分圧回路40の分圧比を第1の分圧比から第1の分圧比よりも高い第2の分圧比に変更する。

(もっと読む)

半導体パッケージ

【課題】差動モード信号の反射とコモンモード信号の反射とを個別に制御する。

【解決手段】半導体パッケージ内の整合回路20において、第1および第2の信号端子2p,2nは、半導体チップ10に設けられた差動信号の入出力用の一対のパッド1p,1nとボンディングワイヤでそれぞれ接続され、互いに容量結合するように構成される。第3および第4の信号端子3p,3nは、差動信号伝送用の一対の線路12p,12nとそれぞれ接続され、互いに容量結合するように構成される。第1〜第4の補助端子2g1,2g2,3g1,3g2は、第1〜第4の信号端子2p,2n,3p,3nとそれぞれ容量結合するように構成されるとともに、各々が接地電位と直接またはインダクタを介して接続される。第1のインダクタ5pは、第1および第3の信号端子2p,3p間に設けられる。第2のインダクタ5nは、第2および第4の信号端子2n,3n間に設けられる。

(もっと読む)

デバイス及びホスト装置並びに通信システム

【課題】ホスト装置がデバイスとの間でのデータ転送に関する複数のコマンドを連続してデバイスに送信し、デバイスが該複数のコマンドの実行順を決定する通信システムにおけるデータ転送の効率を高める。

【解決手段】デバイス150は、ホスト装置110が発行した複数のコマンドのうちの、、次に実行するコマンドが決定した時点で、該次に実行するコマンドを通知するための次コマンド情報をホスト装置110に送信すると共に、該次に実行するコマンドに関するデータ転送の準備を行う(S62、S70)。ホスト装置110は、次コマンド情報をデバイス150から受信した際に、該次コマンド情報が示すコマンドの実行準備を開始する(S12、S20)。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極が絶縁膜で被覆されていようがいまいが、貫通電極と配線の接触面積を確保すること。

【解決手段】本実施形態に係る半導体装置は、第1の半導体チップ200と、第1の半導体チップ200上に積層された第2の半導体チップ300と、第1の半導体チップ200と第2の半導体チップ300とを接続する貫通電極120と、を有している。貫通電極120は、第1の貫通電極部122と第2の貫通電極部124を有している。第1の貫通電極部122は、第2の半導体チップ300において、第2の絶縁膜42の上面から第2の配線32の上部まで設けられている。第2の貫通電極部124は、第1の貫通電極部122の下面と繋がっており、かつ第2の配線32と同一層から第2の半導体チップ300の第1の配線30上部まで設けられている。第1の貫通電極部122と第2の貫通電極部124の孔径は、平面視で、第1の貫通電極部122の孔径の方が大きい。

(もっと読む)

31 - 40 / 8,021

[ Back to top ]