旭化成エレクトロニクス株式会社により出願された特許

61 - 70 / 840

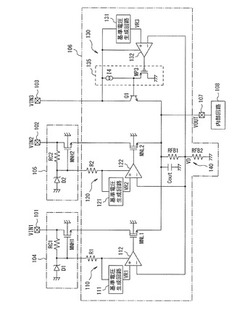

多入力電源回路

【課題】一の電源から他の電源に切り替えるとき、一の入力端子から他の入力端子へ電流が逆流しない多入力電源回路の提供。

【解決手段】この発明は、入力端子101〜103と出力端子104との間に出力安定化部110、120、130を備えている。出力安定化部110は、MOSトランジスタMNL1と、基準電圧生成回路111と、演算増幅器112と、共通の分圧回路140とを備えている。出力安定化部120は、MOSトランジスタMNL2と、基準電圧生成回路112と、演算増幅器122と、共通の分圧回路140とを備えている。出力安定化部130は、バイポーラトランジスタQ1と、基準電圧生成回路131と、演算増幅器132と、レベルシフト回路135と、共通の分圧回路140とを備えている。

(もっと読む)

接続機器の検出回路

【課題】小型、簡易な構成でありながら、マイクロフォン等の周辺機器がデバイスに接続されたことを検出することが可能な接続機器の検出回路を提供する。

【解決手段】

入力端子101と電源検出回路104との間に設けられ、入力端子101と電源検出回路104との間を電気的に離接するNチャネルMOSトランジスタ103と、入力端子101と電源検出回路104との間のノード107に電力を供給する端子111と、端子111とノード117との間に設けられ、入力端子101に接続された接続機器に電流を流す抵抗素子109とによって接続機器の検出回路を構成する。電源検出回路104は、接続機器の抵抗値と抵抗素子109の抵抗値とによって分圧された分圧電圧VSNSの値を検出する。

(もっと読む)

発振器

【課題】 発振器に含まれる複数の遅延反転増幅回路の配線容量を高い精度で一定にすることにより、容易に正確、かつ高周波数の多相クロックを生成できる発振器を提供する。

【解決手段】 リング状に接続された遅延反転増幅回路101〜105を、1列にレイアウトし、かつ、遅延反転増幅回路102の出力端子から103の入力端子までの配線長と、遅延反転増幅回路103の出力端子から104の入力端子までの配線長と、遅延反転増幅回路104の出力端子から105の入力端子までの配線長と、遅延反転増幅回路105の出力端子から101の入力端子までの配線長と、遅延反転増幅回路101〜105の出力端子と接続されている配線の配線長を全て等しくする。

(もっと読む)

半導体装置

【課題】ラテラル・バイポーラトランジスタを有する半導体装置であって、エミッタ、コレクタ間の耐圧をより高めることができる半導体装置を提供する。

【解決手段】HCBT100は、第1の導電層を構成する基板1と、n−hill層11と、素子分離酸化膜6とを備え、n−hill層11は第2の導電層と第3の導電層を含み、第3の導電層は第4の導電層を含み、第4の導電層はエミッタ電極31Aと接続し、コレクタ電極31Bをさらに備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bを備え、n−hill層11はコレクタ電極31Bと電気的に接続し、少なくとも2つのコレクタ電極31Bは、コレクタ電極31B同士を結ぶ直線と、n−hill層11に備わる少なくとも一つの側面の2つの対向する位置を結ぶ直線とが直交する位置にあることを特徴とする。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】圧電素子等の容量性負荷にチャージされたエネルギーを無駄に消費することなく、容量性負荷を低消費電力で駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】スイッチング駆動回路24は、容量性負荷である圧電スピーカ15に転送されたエネルギーを抵抗等でなるべく消費させずに、インダクタ42を介してキャパシタ41に再びチャージし、容量性負荷の駆動に再利用する。これにより、圧電スピーカ駆動用アンプ14は、圧電スピーカ15を低消費電力で駆動することができる。その際、圧電スピーカ15を駆動するために必要なエネルギーは、ダイオード48を介して、電源から自動的にキャパシタ41に補充される。従って、ゲートドライバ23は、スイッチング素子の制御を簡潔に行うことができる。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】ゼロクロス付近においてもスイッチングの動作周期に基づく時間内にエネルギーの転送が終了するような駆動信号を生成して、その駆動信号によって容量性負荷を駆動するための各動作フェーズの動作を本来の動作時間通りに行うことのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】ゲートドライバ回路23は、駆動信号VCN,VCPがゼロクロス付近の範囲RZにあるときに、PMOSトランジスタ47,49およびNMOSトランジスタ50,51の導通状態を切り換える。これによって、圧電スピーカー駆動用アンプ14は、動作状態を、通常動作状態からゼロクロス動作状態にする。そして、その駆動信号VCN,VCPによって圧電スピーカー15を駆動するための各動作フェーズを、本来のスイッチング動作周期に基づく時間通りに行うことができる。

(もっと読む)

半導体装置の評価用TEG、オーバーエッチング率の演算方法および半導体装置の評価方法

【課題】評価用TEGにおいて、ビアエッチングによる層間膜換算におけるオーバーエッチング量を数値化する。

【解決手段】第1の層間絶縁膜12上の、VIA実寸測定用パターン2の形成領域には下部配線を設けずに、VIA抵抗測定用パターン4の形成領域には下部配線14を設け、この上に第2の層間絶縁膜16を生成する。この第2の層間絶縁膜16に、エッチングによりビアホール20aを形成した後、導電性部材を堆積させてビアTEG20を形成する。下層に下部配線14が配置されたビアTEG20(204)のビアホール深さbと下層に下部配線14が配置されないビアTEG20(202)のビアホール深さaとの比からオーバーエッチング率(量)を演算する。

(もっと読む)

スイッチング電源回路

【課題】ΔΣ変調制御を用いた単一インダクタ多出力DC/DC変換回路を備えてさらなる早い応答速度を実現し、かつクロスレギュレーションの影響を小さくするスイッチング電源回路を得ること。

【解決手段】入力電圧が単一インダクタ2出力DC/DC変換回路150に入力されると、その出力電圧が第1及び第2のエラーアンプ151,152と第1及び第2のΔΣ変調回路153,154とドライブ回路155を介してΔΣ変調制御され、単一インダクタ2出力DC/DC変換回路150から出力電圧を得る。このΔΣ変調制御の特徴は、入力信号に比例して出力のパルス密度が変化することである。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】駆動用アンプのゲインが変動するのをなるべく抑えて差動信号の駆動信号を生成して、その駆動信号によって容量性負荷を駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】圧電スピーカー駆動用アンプ14は、キャパシタ41から圧電スピーカー15に転送されたエネルギーを、圧電スピーカー15を駆動するためのエネルギーに再利用する。その際に、PWM回路22のランプ波発生回路61は、圧電スピーカー15の両端子間の電圧変化分ΔVn(V)に含まれる、インダクタ42にエネルギーをチャージする元のキャパシタ41の両端子間の電圧値Vlp(V)の成分と、圧電スピーカー15の両端子間の電圧値Vn−1(V)=Vspk(V)の成分とを打ち消すような傾きkをもち、かつ、その傾きkにチャージ時間t(μS)の二乗が乗じられた二次のランプ波を発生させる。

(もっと読む)

駆動用ドライバ、駆動用アンプおよび情報機器

【課題】なるべく少ない数のスイッチング素子で差動信号の駆動信号を生成して、その駆動信号によって容量性負荷を駆動することのできる駆動用ドライバ、駆動用アンプおよび情報機器を提供する。

【解決手段】圧電スピーカー駆動用アンプ14は、キャパシタ41から圧電スピーカー15に転送されたエネルギーを抵抗等でなるべく消費させずに、圧電スピーカー15を駆動するためのエネルギーに再利用する。その際に、ゲートドライバ回路23は、第1フェーズから第4フェーズまでの各動作フェーズに合わせて、スイッチング駆動回路24のPMOSトランジスタ45〜49の導通状態を切り換える。これによって、圧電スピーカー駆動用アンプ14は、なるべく少ない数のスイッチング素子で、差動信号の駆動信号を生成して、その駆動信号によって圧電スピーカー15を駆動することができる。

(もっと読む)

61 - 70 / 840

[ Back to top ]