富士通セミコンダクター株式会社により出願された特許

991 - 1,000 / 2,507

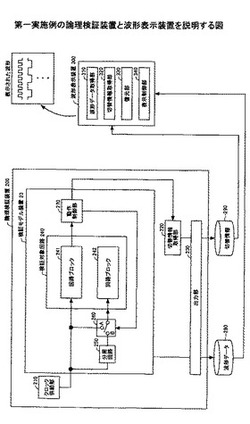

論理検証装置及び論理検証方法

【課題】論理検証の実行速度を高速化し、且つ圧縮されていない本来の波形データを出力することが可能な論理検証装置及び論理検証方法を提供することを目的とする。

【解決手段】周波数の異なる複数のクロック信号で動作する複数の回路ブロックを、該クロック信号を切り替えて論理検証する論理検証装置であって、第1回路ブロックが動作していない期間前記第1回路ブロックの第1クロック信号で第2回路ブロックを動作させるように制御し、前記期間と、前記第1クロック信号と前記第2回路ブロックの第2クロック信号との分周比と、を含む切替情報を出力する動作制御手段と、前記切替情報と、前記第2回路ブロックを動作させた前記第1クロック信号が前記第2クロック信号の周波数に復元される圧縮波形データを含む波形データとを出力する出力手段と、有する。

(もっと読む)

コンタクタ、半導体集積回路の試験方法及び試験装置

【課題】最終試験を所定回数繰り返す毎に行うクリーニング工程を不要とし、半導体集積回路の生産性を向上できるコンタクタ、半導体集積回路の試験方法及び試験装置を提供する。

【解決手段】半導体集積回路11が載置されるIC搭載部20と、コンタクトピン26が立設されるベース部材23との間に研磨シート31を配置する。研磨シート31にはコンタクトピン26が挿通可能なスリットが設けられている。半導体集積回路11を押し下げると研磨シート31によりコンタクトピン26の先端が擦れて研磨され、コンタクトピン26の先端に付着している異物が除去される。その後、更に半導体集積回路11を押し下げると、コンタクトピン26が半導体集積回路11の接続端子に接触する。この状態で半導体集積回路11を駆動し、出力信号により良否を判定する。

(もっと読む)

半導体装置の製造方法

【課題】銅配線とアルミニウム配線との間のバリアを形成するための新規な技術を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板の上方に形成された銅配線上に、絶縁膜を形成する工程と、絶縁膜に凹部を形成し、凹部の底に前記銅配線を露出させる工程と、凹部の底に露出した銅配線上に、250℃〜350℃の範囲の成膜温度で、フッ化タングステンの供給期間と供給停止期間とを交互に繰り返して、CVDでタングステン膜を選択的に成膜する工程と、タングステン膜上方に、アルミニウム配線を形成する工程とを有する。

(もっと読む)

半導体集積回路

【課題】 ラッチアップの発生を防止し、内部回路に所望のストレスを印加する。

【解決手段】 第1電圧生成回路は、電源電圧より高い第1高レベル電圧を生成する。第2電圧生成回路は、電源電圧より高く、第1高レベル電圧より低い第2高レベル電圧を生成し、バーンイン試験時に停止する。第3電圧生成回路は、電源電圧より低い第3高レベル電圧を生成する。複数の内部回路は、第1高レベル電圧を受けて個別に動作するとともに、バーンイン試験中に動作する。電圧制御回路は、バーンイン試験時に第2高レベル電圧線を第3高レベル電圧線に接続する。寄生トランジスタは、第1高レベル電圧をベースで受け、第2高レベル電圧をエミッタで受ける。複数の内部回路の動作により第1高レベル電圧が一時的に低下するときに、第2高レベル電圧を低い値に設定することで、寄生トランジスタがオンすることを防止できる。

(もっと読む)

研磨終点検出方法及び半導体製造装置

【課題】化学機械研磨における終点検出の精度を高めた研磨終点検出方法を提供する。

【解決手段】化学機械研磨における研磨終点検出方法において、前記化学機械研磨がされている基板に光を照射する光照射工程と、前記基板において反射された反射光を受光する受光工程と、前記受光した反射光に基づき光の強度を調節する調節工程と、前記受光した反射光に基づき波長ごとに分光する分光工程と、前記基板に光を照射した場合の基準となる分光特性に対し、前記分光された光の分光特性の比又は差の値を算出する計算工程と、前記算出された値が所定の範囲内にある場合には、前記調節工程において調節された光の分光特性をリファレンスとして用いて終点検出を行うことにより上記課題を解決する。

(もっと読む)

半導体装置、無線タグおよび方向判定方法

【課題】自装置の向きを効率的に取得すること。

【解決手段】遮蔽部4は、入射する電磁波を遮蔽する。アンテナ2は、遮蔽部4の第1面側に設けられている。アンテナ3は、その第1面とは異なる遮蔽部4の第2面側に設けられている。方向判定部1aは、アンテナ2が電磁波を受信して出力される第1の信号と、アンテナ3が遮蔽部4を介した電磁波を受信して出力される第2の信号とに基づいて自装置の向きを判定し、判定結果を出力する。

(もっと読む)

荷電粒子ビーム露光方法及び装置、荷電粒子ビーム露光データ作成方法及びプログラム、並びに、ブロックマスク

【課題】スループットの向上を図ることができる荷電粒子ビーム露光方法を提供する。

【解決手段】電子銃64から放射された電子ビームを所定サイズの矩形に成形する第1アパーチャ65と、該第1アパーチャ65で所定サイズの矩形に成形した電子ビームを任意サイズの矩形に成形する第2アパーチャ66と、該第2アパーチャ66で任意サイズの矩形に成形した電子ビームを一括露光用パターン形状に成形するブロックマスク67とを設ける。

(もっと読む)

半導体装置

【課題】精度の高い負電圧をプログラマブルに生成することが可能な半導体装置を提供すること。

【解決手段】負電圧発生装置の出力電圧VPWを制御する負電圧検出回路に、負電圧の検出値を切り替える切り替えスイッチTGと、補正スイッチTBとを備える。補正スイッチは、切り替えスイッチと同一の構成を有するスイッチとし、オン状態に保つ。これにより、切り替えスイッチのオン抵抗の影響をキャンセルすることができる。そのため、精度の高い負電圧をプログラマブルに生成することが可能である。

(もっと読む)

設計支援プログラム、設計支援装置、および設計支援方法

【課題】回路の内部構成を意識することなく、LSIの消費電力の低減化および面積削減を図ること。

【解決手段】併合回路ABでは、組み合わせ回路LA0〜LA2と組み合わせ回路LB0〜LB2とが排他的な動作をするように、選択回路200〜202を挿入する。そして、選択回路200〜202の出力先にFF0〜FF2を接続する。併合回路ABでは、選択信号S=0のとき、組み合わせ回路LA0〜LA2が動作し、S=1のとき、組み合わせ回路LB0〜LB2が動作する。このように、組み合わせ回路LA0〜LA2,LB0〜LB2とFFA0〜FFA2,FFB0〜FFB2の接続関係さえ分かっていれば、その内部構成を意識する必要はない。

(もっと読む)

半導体装置

【課題】

活性領域と素子分離領域を別個の対象として応力を制御し,半導体装置の性能を向上する。

【解決手段】

半導体装置は、p−MOS領域を有する半導体基板と、半導体基板表面部に形成され、p−MOS領域内にp−MOS活性領域を画定する素子分離領域と、p−MOS活性領域を横断して,半導体基板上方に形成され、下方にp−MOSチャネル領域を画定するp−MOSゲート電極構造と、p−MOSゲート電極構造を覆って、p−MOS活性領域上方に選択的に形成された圧縮応力膜と、p−MOS領域の素子分離領域上方に選択的に形成され,圧縮応力膜の応力を解放している応力解放領域と、を有し、p−MOSチャネル領域にゲート長方向の圧縮応力とゲート幅方向の引張応力を印加する。

(もっと読む)

991 - 1,000 / 2,507

[ Back to top ]