富士通セミコンダクター株式会社により出願された特許

1,021 - 1,030 / 2,507

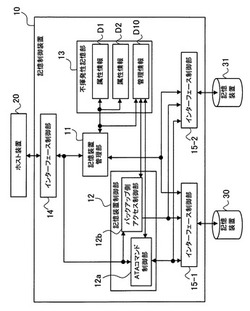

記憶制御装置及び制御方法

【課題】省電力効率高く複数の記憶装置を制御する。

【解決手段】記憶装置管理部11が、複数の記憶装置30,31から、記憶装置30,31の性能または省電力機能に関する情報を含む属性情報D1,D2を取得し、記憶装置30,31間における属性情報D1,D2に応じて、省電力機能を有効とする記憶装置または無効にする記憶装置を決定し、記憶装置制御部12が、決定した各記憶装置30,31の省電力機能の状態に応じて、記憶装置30,31を制御する。

(もっと読む)

ネットワークノード

【課題】

信頼性の高い相互監視と復旧動作を可能にするネットワークノードを提供する。

【解決手段】

複数のノードと共にネットワークに接続されるネットワークノードにおいて,通信サイクル毎にネットワークに送信するフレームに,自身の正常状態を示すアライブデータを書き込んでフレームを送信する一方で、受信した他ノードのアライブ情報を判定し、送信元に対し、自身の送信フレームを介して復帰要求を送信する手段、また、他のノードから自身のノード宛の復旧要求データを,あらかじめ規定した数以上受信したときに,自身のノードに復旧動作を実行させる復旧制御手段とを有する。

(もっと読む)

集積回路の設計方法、集積回路の設計プログラムおよび集積回路の設計装置

【課題】集積回路の設計において、効率よく並列処理を行うこと。

【解決手段】集積回路の設計を行う際に、集積回路内の複数の素子が複数のスレッドに割り当てられる。スレッドごとに素子の状態を解析する処理が複数のスレッドで並列に行われる。ある時刻の各素子の解析状況に基づいて複数の素子が複数のスレッドに再度割り当てられる。例えば、並列に処理されるスレッド間の負荷の偏りがなくなるように各スレッドに素子が再度割り当てられる。次の時刻の解析は、複数の素子が複数のスレッドに再度割り当てられた状態で行われる。

(もっと読む)

ボディバイアス制御回路及びボディバイアス制御方法

【課題】外部からトランジスタの閾値電圧を制御する必要のないボディバイアス制御回路などを提供すること。

【解決手段】制御回路2aは、トランジスタの閾値電圧の基準値を定めるトランジスタTr1と、ボディバイアス発生器BBG1によって制御されるボディバイアスVBBがバックゲート端子に供給され、閾値電圧を可変に制御可能なトランジスタTr2とを備える。また、制御回路2aは、トランジスタTr1の閾値電圧Vth1とトランジスタTr2の閾値電圧Vth2との差電圧ΔVrに応じた制御信号Venを出力する比較器COMP1を備える。ボディバイアス発生器BBG1は、閾値電圧Vth2が閾値電圧Vth1よりも高くなると、ボディバイアス発生器BBG1を停止して、閾値電圧Vth2を低下させる。また、閾値電圧Vth2が閾値電圧Vth1よりも低くなると、ボディバイアス発生器BBG1を動作させ、閾値電圧Vth2を上昇させる。

(もっと読む)

出力バッファ回路

【課題】ハイ・インピーダンスにする際に発生する電源ノイズを低減させる出力バッファ回路を提供する。

【解決手段】出力バッファ回路10は、データ信号DA及び制御信号DCに基づいて、PMOSトランジスタT1をオンからオフさせNMOSトランジスタT2をオフからオンさせて出力端子Poを第1状態に、PMOSトランジスタT1をオフからオンさせNMOSトランジスタT2をオンからオフさせて出力端子Poを第2状態に、又、両トランジスタT1,T2をオフさせて出力端子Poをハイ・インピーダンスとなる。そして、オフ時間制御回路部13によって、第1状態又は第2状態からハイ・インピーダンスにする制御信号が入力された時、オンからオフさせるためにPMOSトランジスタT1又はNMOSトランジスタT2のゲートに供給される信号の立ち上がり波形又は立ち下がり波形を緩やかにする

(もっと読む)

データ処理装置

【課題】リアルタイム性を保証しつつ、DVFSによる低消費電力化を低オーバヘッドで実現するデータ処理装置を提供する。

【解決手段】受信データをフレーム毎に受信する通信システムのデータ処理装置において、フレームの先頭を検出するフレーム先頭検出部と、データ処理部における未処理データ量に基づいてクロック周波数を決定するクロック周波数決定部とを有し、電源・クロック生成部は、フレーム先頭検出部によるフレーム先頭検出のタイミングに応答してデータ処理部が動作可能な最大周波数のクロックとそれに対応する電源電圧とをデータ処理部に供給し、データ処理部が時間制約処理を完了した後、最大周波数のクロックより低い第1の周波数のクロックであって、クロック周波数決定部が当該クロック周波数設定タイミングにおける未処理データ量に基づいて決定した第1の周波数のクロックとそれに対応する電源電圧とをデータ処理部に供給する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

配線設計方法、設計装置及びプログラム

【課題】設計時間の短縮を図ること。

【解決手段】設計装置の記憶装置には、半導体装置を検証ステップの格子にて区画した各領域に含まれるレイアウトパターンの面積がそれぞれ格納されるセル面積テーブルと、移動される検証エリアの位置に対応し、各検証エリアには所定数の領域が含まれ、検証エリアに対してその検証エリアに含まれるレイアウトパターンの占有率が、各検証エリアに対応して格納されるセル占有率テーブルを含む面積DB33が記憶される。図形DB32にはインスタンスの面積テーブルが含まれる。CPUは、配置されたインスタンスの面積テーブルに従って編集対象のセル面積テーブルを変更し、そのセル面積テーブルに従ってセル占有率テーブルを更新し、セル占有率テーブルの値によりレイアウトパターンの占有面積をチェックする。

(もっと読む)

半導体集積回路

【課題】データ信号線の本数を増大させることなくデータ信号を差動信号として構成した半導体集積回路を提供する。

【解決手段】半導体集積回路は、2つのデータ入出力端子と、2つのデータ入出力端子を介してデータを入力するデータ入力回路と、2つのデータ入出力端子を介してデータを出力するデータ出力回路とを含み、データ入力回路及びデータ出力回路の一方の回路は、2つのデータ入出力端子を個々に独立した端子として用いて2つの単相信号を伝送し、データ入力回路及びデータ出力回路の他方の回路は、2つのデータ入出力端子を一対の端子として用いて一対の差動信号を伝送する。

(もっと読む)

ドライバ回路及びドライバ回路の調整方法

【課題】受信状態の劣化を抑制すること。

【解決手段】分圧部32は、出力部31に接続された可変抵抗器VR1と出力部31との間の第1電圧V1を、固定抵抗器R2と可変抵抗器VR3とによる分圧比にて分圧して第3電圧V3を生成する。入力部33は、第2電圧V2から第3電圧V3を減算して第4電圧V4を生成する。極性検出回路35は、第4電圧V4の極性と第3電圧V3の極性を比較し、比較結果に応じた検出信号SR1を出力する。そして、調整回路37は、極性検出回路36から出力される検出信号SR1に基づいて、極性が一致するように分圧部32に含まれる可変抵抗器VR3を調整する。

(もっと読む)

1,021 - 1,030 / 2,507

[ Back to top ]