富士通セミコンダクター株式会社により出願された特許

1,031 - 1,040 / 2,507

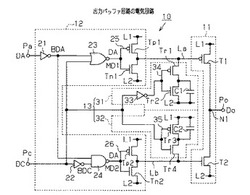

出力バッファ回路

【課題】ハイ・インピーダンスにする際に発生する電源ノイズを低減させる出力バッファ回路を提供する。

【解決手段】出力バッファ回路10は、データ信号DA及び制御信号DCに基づいて、PMOSトランジスタT1をオンからオフさせNMOSトランジスタT2をオフからオンさせて出力端子Poを第1状態に、PMOSトランジスタT1をオフからオンさせNMOSトランジスタT2をオンからオフさせて出力端子Poを第2状態に、又、両トランジスタT1,T2をオフさせて出力端子Poをハイ・インピーダンスとなる。そして、オフ時間制御回路部13によって、第1状態又は第2状態からハイ・インピーダンスにする制御信号が入力された時、オンからオフさせるためにPMOSトランジスタT1又はNMOSトランジスタT2のゲートに供給される信号の立ち上がり波形又は立ち下がり波形を緩やかにする

(もっと読む)

データ処理装置

【課題】リアルタイム性を保証しつつ、DVFSによる低消費電力化を低オーバヘッドで実現するデータ処理装置を提供する。

【解決手段】受信データをフレーム毎に受信する通信システムのデータ処理装置において、フレームの先頭を検出するフレーム先頭検出部と、データ処理部における未処理データ量に基づいてクロック周波数を決定するクロック周波数決定部とを有し、電源・クロック生成部は、フレーム先頭検出部によるフレーム先頭検出のタイミングに応答してデータ処理部が動作可能な最大周波数のクロックとそれに対応する電源電圧とをデータ処理部に供給し、データ処理部が時間制約処理を完了した後、最大周波数のクロックより低い第1の周波数のクロックであって、クロック周波数決定部が当該クロック周波数設定タイミングにおける未処理データ量に基づいて決定した第1の周波数のクロックとそれに対応する電源電圧とをデータ処理部に供給する。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法においてSRAMのセルサイズを縮小することを目的とする。

【解決手段】メモリセルCの活性領域31a、31bが画定されたシリコン基板31と、素子分離絶縁膜32上に形成され、第1の方向に延在するゲート電極35と、シリコン基板31とゲート電極35の上に形成された第1の絶縁膜42と、第1の絶縁膜42を貫通し、ゲート電極35と第1の活性領域31aに重なり、第1の方向に直交する第2の方向に延在する第1の銅プラグ45aと、第2の活性領域35b上の第1の絶縁膜42を貫通する第2の銅プラグ45bと、第1の絶縁膜42上に形成された第2の絶縁膜44と、第2の絶縁膜44に埋め込まれ、第1の銅プラグ45aの側面45xから第2の延在方向に後退して形成され、第1の銅プラグ45aの上面の一部のみを覆う銅配線48aとを有する半導体装置による。

(もっと読む)

スキャンチェーンの生成方法、スキャンチェーンの生成プログラムおよび集積回路

【課題】集積回路の試験に関し、一つの回路を分割した複数の領域間の試験を行えるようにスキャンチェーンを生成すること。

【解決手段】集積回路の試験時に、複数のフリップフロップを含むスキャンシフトを動作させたときの消費電力が許容値を超える場合、スキャンチェーンに含まれる複数のフリップフロップを複数のグループに分割する。分割の際には、集積回路が実際に動作するときの信号の伝達経路に基づいて、複数のフリップフロップのうちの一部のフリップフロップが複数のグループに含まれる。複数のグループに含まれるフリップフロップは、複数のグループのそれぞれに生成されるスキャンチェーンに接続される。

(もっと読む)

受信データ処理回路及び受信データ処理切り替え方法

【課題】複数系統のデインターリーブ処理の処理性能をなるべく高く維持しながらもメモリ容量をなるべく小さく抑えた受信データ処理回路を提供する。

【解決手段】復調処理及び軟判定後の第1の受信データに対してデインターリーブ処理を行なう第1のデインターリーブ部と、第1の受信データとは別の復調処理及び軟判定後の第2の受信データに対してデインターリーブ処理を行なう第2のデインターリーブ部と、第1及び第2のデインターリーブ部により共用され第1及び第2の受信データの各々について硬判定情報と軟判定情報とを分離して格納するメモリと、第1の受信データの硬判定情報、第1の受信データの軟判定情報、第2の受信データの硬判定情報、及び第2の受信データの軟判定情報の各々についてメモリに格納するビット数を動的に変化させるメモリ制御部とを含むことを特徴とする受信データ処理回路が提供される。

(もっと読む)

電子装置及び電子部品

【課題】電子部品を収容した筐体内に発生する不要電波を抑制する。

【解決手段】筐体20内に発生する不要電波の波長λ1に基づき、筐体20に収容される半導体チップ30の内部に、その底面側に配設した金属膜40から、λ1’/4(λ1’は半導体チップ30内を伝播する電波の波長)の位置に、抵抗膜31を配設することによって、当該半導体チップ30をλ/4型電波吸収体とし、筐体20内の不要電波の発生を抑制する。

(もっと読む)

半導体装置及びその製造方法

【課題】高誘電率膜のゲート絶縁膜を含むMISFETを有する半導体装置に関し、メタルゲート材料の仕事関数と半導体基板の仕事関数との間の関係によって閾値電圧を容易且つ浅い値に制御しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上に酸化シリコンを主体とする第1の絶縁膜を形成し、第1の絶縁膜上に酸化ハフニウムを主体とする第2の絶縁膜を形成し、熱処理を行い第2の絶縁膜上にシリコンを析出させ、シリコン上にシリコンに対して酸化作用を有する第3の絶縁膜を形成し、第3の絶縁膜上に金属膜のゲート電極を形成し、熱処理を行い第3の絶縁膜の酸化作用によってシリコンを酸化させる。

(もっと読む)

デカップリング容量決定方法、デカップリング容量決定装置およびプログラム

【課題】簡易に行える、配線のインダクタンスを考慮した高精度のデカップリング容量決定処理方法および装置の実現。

【解決手段】半導体集積回路装置のデカップリング容量決定方法であって、動作周波数f、消費電力P、電源電圧V、許容電源電圧変動量ΔV、パッケージインダクタンス量L、および固有容量Cpを含む設計データを導入しS201、基準ダイ容量Cv1を演算しS203、CpがCv1より小さい時にはCv1とCpの差をデカップリング容量CdとしS205、CpがCv1より大きい時にはCdをゼロとしS206、CpとCdの和である実ダイ容量CvとLから共振周波数Trを演算しS208、比Tr/kTが1より大きいか判定しS209、比が1以下の時にはCdを維持しS212、比が1より大きい時には、さらにCvがCv1Tr/kTより大きい時にはCdを維持し、CvがCv1Tr/kTより小さい時には、CvがCv1Tr/kT以上になるようにCdを決定する。

(もっと読む)

画像処理回路、画像処理方法及び撮像装置

【課題】オートフォーカス後のピントずれの影響を低減することができる画像処理回路を提供する。

【解決手段】画像処理回路は、AF評価値が最大となるピーク位置を合焦位置と判定するAF制御を実行するAF制御部19aを含むシステム制御部19と、AF制御時に各レンズ位置毎にAF評価値を算出し、さらにシャッター時にもAF評価値を算出するAF評価値算出部70を含む信号処理部16とを備える。また、信号処理部16は、合焦位置におけるAF評価値とシャッター時のAF評価値との差分値と、複数のレンズ位置間におけるAF評価値の傾きとに応じて補正値を算出する補正値算出部80と、その補正値により補正されたエッジ強調量に基づいて画像データのエッジ成分を強調するエッジ強調部40とを備える。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10上にトランジスタ34を形成する工程と、半導体基板上及びトランジスタ上に複数の部分膜36a、38a、40a、42を積層することにより、複数の部分膜を有する第1の絶縁層44を形成する工程と、第1の絶縁層上に、第1の絶縁層とエッチング特性が異なる第2の絶縁層46を形成する工程と、第1の絶縁層をエッチングストッパとして、第2の絶縁層をエッチングすることにより、第2の絶縁層にコンタクトホールを形成する工程と、コンタクトホール内に露出する第1の絶縁層をエッチングする工程とを有し、第1の絶縁層を形成する工程では、複数の部分膜のうちの最上層の部分膜以外の部分膜に対して膜を収縮させるキュア処理を行い、複数の部分膜のうちの最上層の部分膜に対してキュア処理を行わない。

(もっと読む)

1,031 - 1,040 / 2,507

[ Back to top ]