富士通セミコンダクター株式会社により出願された特許

1,071 - 1,080 / 2,507

画像処理プログラム、画像処理装置、および画像処理方法

【課題】画像認識を高速かつ低負荷により実現すること。

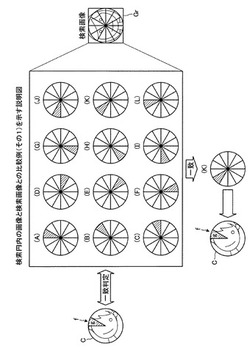

【解決手段】検索円C内の画像のうち代表扇形f内の画像とを比較して一致判定する。具体的には、代表扇形内画像gの特徴量を、(A)〜(L)の12分割された各扇形画像の特徴量とを比較することで一致判定をする。両特徴量は、たとえば、ヒストグラム分析によって得られた輝度を用いることができる。代表扇形内画像gと(K)の扇形画像とは、ともに右目に相当する画像であるため、一致と判定される。これにより、代表扇形内画像gは顔画像候補に決定される。また、一致した扇形内画像により、顔画像候補がどのような傾きを持っているかも把握することができる。

(もっと読む)

半導体装置、半導体装置の製造方法及び配線基板

【課題】配線が露出しない配線基板を備える、信頼性の高い、安定して形成できる半導体装置を提供する。

【解決手段】配線基板20の一主面の外周縁部Xより内側に、配線22、及び配線22を被覆する保護層61を配設し、配線22及び保護層61が配設されない外周縁部Xに、絶縁シート80を周設する。配線基板20の一主面側に半導体素子40を搭載して配線22に電気的に接続し、半導体素子40の搭載面側を封止樹脂90で封止する。

(もっと読む)

半導体装置及び不良箇所情報の書き込み方法

【課題】複数のフューズグループが設けられた構成においてチップ内部の自己修正機能により適切にメモリを修正できる半導体装置を提供する。

【解決手段】半導体装置は、複数のメモリセルと複数の冗長メモリセルとを含むメモリと、メモリを試験し複数のメモリセルのうちの複数の不良箇所を示す不良箇所情報を出力する試験回路と、複数の記憶部と、複数の記憶部の更新前の格納情報と不良箇所情報とに基づいて複数の記憶部の更新後の格納情報を決定する制御回路とを含み、メモリは、複数の記憶部の更新後の格納情報により複数の不良箇所をそれぞれ特定し、該特定された複数の不良箇所のメモリセルをそれぞれ複数の冗長メモリセルで置き換える。

(もっと読む)

差動受信回路

【課題】差動対を備える差動受信回路であって、出力するデータの立ち上がりと立ち下がりの変化タイミングの遅延差を低減した差動受信回路の実現。

【解決手段】差動対を備え、入力される相補入力信号inp,innを増幅して相補出力信号A,Bを出力する差動アンプ回路1と、直列に接続された2個以上のインバータInvA1,InvA2,InvA3を備え、初段に差動アンプ回路の出力する相補出力信号の一方Aが入力される第1のインバータラインと、差動アンプ回路の出力する相補出力信号の一方Bが入力される少なくとも1個のインバータInvB1,InvB2を備え、2個以上のインバータを備える場合には直列に接続され、初段に相補出力信号の一方が入力される第2のインバータラインと、を備え、第1のインバータラインおよび第2のインバータラインの初段からの段数が1段異なる1組の2個のインバータの出力を接続した。

(もっと読む)

フレア補正方法およびフレア補正プログラム

【課題】フレア補正を短時間で正確に行うフレア補正方法を提供すること。

【解決手段】パターンデータに対応するフレア値のパターンデータ上での分布をフレアマップとして算出するフレアマップ算出ステップと、フレアマップを用いて、所定のフレア値を有したパターンのパターンデータ上での占有率をフレア値占有率としてフレア値毎に算出する占有率算出ステップと、フレア値占有率の分布に基づいて、フレア値の基準とする基準フレア値を決定する基準決定ステップと、基準フレア値でのパターン補正量を基準としてフレア値に応じたパターン補正を行うパターン補正ステップと、を含む。

(もっと読む)

半導体回路

【課題】小型で小電力の高速動作するレベルシフト回路を提供する。

【解決手段】基準電圧にソースがそれぞれ接続され、第1の信号と第1の信号の反転信号がゲートにそれぞれ入力される第1導電型の第1と第2のトランジスタと、第2の電源電圧にソースが接続された第2導電型の第3のトランジスタと、第2の電源電圧にソースが接続され、ドレインから第2の信号を出力する第2導電型の第4のトランジスタとを有し、第1と第2の第1導電型トランジスタのドレインに第1と第2の第2導電型トランジスタのドレインがそれぞれ接続され、第3と第4のトランジスタのゲートとドレインはそれぞれ電気的に交差接続され、さらに、交差接続において、第3のトランジスタのドレインと第4のトランジスタのゲートの間にソース、ドレインが接続され、ゲートが第4のトランジスタのドレインに接続された第2導電型の第5のトランジスタを有するレベルシフト回路。

(もっと読む)

半導体装置及びその製造方法

【課題】歪みの高いキャリア移動領域における寄生抵抗及びエネルギー障壁を小さくするための半導体装置を提供する。

【解決手段】半導体基板1上にゲート絶縁膜7を介して形成されたゲート電極13bと、半導体基板1のうちゲート電極13bの下方に形成されるチャネル領域6cと、チャネル領域6cの両側方に形成され、第1炭素濃度で炭素を含み、第1リン濃度でリンを含む第1の炭化シリコン層23と、第1の炭化シリコン層23上にチャネル領域6cに接合して形成され、第1リン濃度より多い第2リン濃度でリンを含み、第1炭素濃度以下の第2炭素濃度で炭素を含む第2の炭化シリコン層24とを有する。

(もっと読む)

半導体素子及びその製造方法

【課題】回路基板に確実に実装可能で、且つ、加熱に起因して発生する応力が抑制可能な半導体素子を提供する。

【解決手段】半導体素子10において、複数の電極パッド13の上方に、中央部Aより中間部Bで、更に中間部Bより端部Cで膜厚が厚くなるように形成した絶縁部材15を設ける。各電極パッド13に接続するアンダーバンプメタル17は、それぞれ絶縁部材15から突出させ、その先端にそれぞれバンプ18を形成する。

(もっと読む)

DC/DCコンバータ及びDC/DCコンバータの制御方法

【課題】定常出力電圧の精度を向上させながら、出力電圧の変動に対する応答速度を向上させて定常出力電圧を安定化させ得るDC/DCコンバータを提供する。

【解決手段】出力電圧Voutと基準電圧Vrefとを比較する第一の比較器5と、第一の比較器の出力信号をトリガとして一定の時間幅のパルス信号を生成するパルス発生回路6と、パルス信号に基づいて開閉される第一のスイッチ回路1と、第一のスイッチ回路を介して供給される入力電圧Vinに基づいて出力電圧Voutを生成する出力電圧生成部2,3,4と、第一の比較器5の出力信号を遅延させて出力する遅延生成回路11と、出力電圧Voutと基準電圧Vrefとの電位差に基づいて遅延生成回路11の遅延時間を制御する誤差増幅器7とを備えた。

(もっと読む)

プロセッサ及び情報処理システム

【課題】比較的小さな回路規模で且つレジスタファイルの遅延を増大させることなく、SIMD演算の前処理としてのデータ並び替えを実行可能なプロセッサを提供する。

【解決手段】プロセッサは、SIMD演算を実行可能な演算器と、演算器に供給する演算対象のデータを格納するレジスタファイルと、レジスタファイルとは別個に設けられ、各データ列が複数個のデータ要素を含む整数n個のデータ列を列毎に書き込み、n個のデータ列の各々から同一位置のデータ要素を選択してn個のデータ要素として読み出し可能なバッファとを含み、バッファから読み出したn個のデータ要素を演算器にSIMD演算の対象として供給する。

(もっと読む)

1,071 - 1,080 / 2,507

[ Back to top ]