富士通セミコンダクター株式会社により出願された特許

1,501 - 1,510 / 2,507

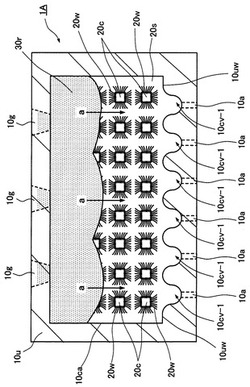

樹脂封止方法及び樹脂封止用金型

【課題】製造歩留まり、信頼性を向上させる半導体装置を製造する樹脂封止方法及び樹脂封止用金型を提供する。

【解決手段】半導体素子20cが搭載された支持基板20sを、下金型上に載置し、下金型と、下金型と衝合する上金型10uとを型締めし、金型の樹脂注入口10gから樹脂30rを注入し、樹脂注入口からエアベント孔10aの方向に樹脂を流動させ、上金型の内側壁10uwに樹脂を到達させて、半導体素子を樹脂により封止する。上金型の内側面は、キャビティ10ca内に於いて、被処理基板、半導体素子方向に突出する波形形状10cv−1を有している。これにより、半導体装置を、高い製造歩留まりで、高い信頼性を以て、製造することができる。

(もっと読む)

配線間不良箇所特定方法

【課題】配線の信頼性試験で検出された不良配線の短絡箇所を、ボルテージコントラスト法により、短時間に確実に特定できる方法を提供する。

【解決手段】多数の第1の並列配線領域が第1の接続領域で接続された一方の(櫛歯状)配線11と、多数の第2の並列配線領域が第2の接続領域で接続された他方の(櫛歯状)配線12とを、第1と第2の並列配線領域が対向する配置で、絶縁膜に埋め込まれた状態で形成し、第1の並列配線領域と第2の並列配線領域との間の絶縁膜の信頼性試験を行い、短絡を生じさせ、一方の(櫛歯状)配線11と他方の(櫛歯状)配線12のいずれか一方の接続領域を除去ないし断線させ、ボルテージコントラスト法の観察を行ない、並列配線領域間短絡箇所を特定する。

(もっと読む)

セルフタイミング回路を有する半導体メモリ

【課題】通常メモリセルの保持データの誤読み出しを確実に防止することが可能な半導体メモリを提供する。

【解決手段】半導体メモリのセルフタイミング回路において、ダミーワード線に接続され通常レイアウトユニットから構成されたセルフタイミング用ダミーメモリセルが連続して配置された第1のダミービット線と、ダミーワード線に接続され通常レイアウトユニットと点対称又は線対称の関係を有する対称レイアウトユニットから構成されたセルフタイミング用ダミーメモリセルが連続して配置された第2のダミービット線と、第1のダミービット線及び第2のダミービット線を入力し、そのうち電位の変化速度の遅い方のダミービット線の電位変化に基づいて、セルフタイミング信号を出力するタイミング制御回路とを備える。

(もっと読む)

電界効果型半導体装置

【課題】 電界効果型半導体装置に関し、従来の作製方法を大幅に変更することなく、サブスレッショルド電流によるoff時のリーク電流を抑制して、on−off比を高くする。

【解決手段】 ソース領域及び第1ドレイン領域の少なくとも一方が金属或いは多結晶半導体からなるとともに、前記金属或いは多結晶半導体と半導体チャネル層との間に形成されたトンネル絶縁膜を有する。

(もっと読む)

半導体装置とその製造方法

【課題】キャパシタを備えた半導体装置とその製造方法において、キャパシタの品質を向上させること。

【解決手段】第1の導電膜19、誘電体膜20、及び第2の導電膜21をこの順に形成する工程と、第2の導電膜21をパターニングして、複数の上部電極21aを形成する工程と、レジストパターン27の側面27bが後退するエッチング条件を用いて、該レジストパターン27をマスクにしながら誘電体膜20をエッチングし、キャパシタ誘電体膜20aを形成する工程と、第1の導電膜19をパターニングして下部電極19aを形成する工程と、上部電極19aの上の層間絶縁膜33にホール33aを形成する工程と、ホール33aに導体プラグ37を埋め込む工程とを有し、端部の上部電極21a上のホール37の形成予定領域が、側面27bが後退した後のレジストパターン27により覆われる半導体装置の製造方法による。

(もっと読む)

思考的品質改善システム

【課題】 思考的品質改善システムに関し、解析者の思考パターンに沿ったワークフローパターンを実現する。

【解決手段】 ワークフロー機能における、少なくとも集計、絞込み、分類を含むデータ加工エンジンの機能を汎用化しその組み合わせより、品質解析のデータの加工や処理を正規的に処理する。

(もっと読む)

OFDM復調装置およびOFDM復調方法

【課題】受信信号にスプリアスが混入している場合であっても受信品質の劣化が抑制されるOFDM復調装置を提供する。

【解決手段】FFT部23は、OFDM受信信号に対して複数回のバタフライ演算を実行することにより周波数領域信号を生成する。復調部24は、FFT部23により生成された周波数領域信号を復調する。FFT部23は、スプリアスを検出したときに、最後のバタフライ演算の結果に対して、検出されたスプリアスを除く信号成分の最大電力に基づいて各信号成分をスケーリングする。

(もっと読む)

半導体装置の製造装置及び半導体装置の製造方法

【課題】信頼性の高い半導体装置を効率良く製造できるようにする。

【解決手段】減圧されるチャンバ62と、チャンバ62内において、露出するレジスト膜49を有する半導体基板1を複数支持する基板ホルダ64と、基板ホルダ64の配置領域の外側に設けられ、チャンバ62内に酸素ガスを供給する供給孔72が複数箇所に形成されたガス供給管71と、チャンバ62内の流体を吸い込む排気孔が設けられた排気管74と、レジスト膜49をアッシングさせるための酸素ガスを活性化する高周波電源66と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】容易にコンタクト抵抗を低減することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に多結晶シリコン膜を形成し、その後、この多結晶シリコン膜の表面をエッチングする。そして、エッチングされた多結晶シリコン膜をシリサイド化して、シリサイド膜12を形成する。更に、シリサイド膜12に接するプラグ23s、23d及び23gを層間絶縁膜21内に形成する。

(もっと読む)

記憶装置、電子装置、および、データ管理方法

【課題】データ消去後の再書き込みが可能な記憶装置のデータを効率的に管理する。

【解決手段】管理サイズのデータの記憶領域に含まれる1以上の書き込みサイズの記憶領域に対応して保持され、それぞれの書き込みサイズの記憶領域にデータが書き込まれているか否かを示す割当情報を格納する割当情報格納部と、書き込みサイズの記憶領域を複数に分割した分割書き込みサイズの記憶領域に対応して保持され、それぞれの分割書き込みサイズの記憶領域のデータの有効性を含む分割使用情報を格納する分割使用情報格納部と、処理装置が記憶装置との間でデータを読み出しまたは書き込みするときのデータの格納先を識別する論理識別情報とデータが記憶装置内に格納されるときの格納位置との関係を示すアドレス情報を保持するアドレス情報格納部と、を備える。

(もっと読む)

1,501 - 1,510 / 2,507

[ Back to top ]