富士通セミコンダクター株式会社により出願された特許

171 - 180 / 2,507

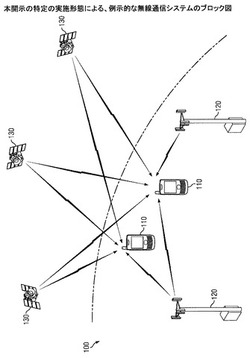

無線通信装置の電力制御のための方法及びシステム

【課題】 本開示は、無線通信装置の電力制御のための方法及びシステムを提供する。

【解決手段】 本開示によると、無線通信信号の電力レベルを追跡する方法は、無線通信要素の送信経路からアンテナへ送信された関連する無線通信信号の電力レベルを示すフィードバック信号を受信するステップを有する。当該方法は、前記無線通信信号に変換されるデジタル信号と関連する基準信号を受信するステップを更に有する。さらに、当該方法は、前記フィードバック信号の前記基準信号に対する利得を決定するステップ、前記決定した利得及び期待利得に基づき、利得誤差を決定するステップ、を有する。

(もっと読む)

パワーアンプ回路および回路装置

【課題】電源電圧が低下した場合も、出力信号の位相が変化しないパワーアンプ回路の実現。

【解決手段】電源VDDと、電源に接続されたMOSトランジスタTr,Trxと、MOSトランジスタのゲート・ドレイン間に接続された補償容量Cxgd,Cxgdxと、を有し、補償容量は、電源の電圧変化に応じて変化するMOSトランジスタのゲート・ドレイン間容量Cgd,Cgdxの変化を相殺するように、電源の電圧変化に応じて容量値が変化する特性を有するパワーアンプ回路。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系トランジスタを簡便な構造で適切に保護することができる半導体装置及びその製造方法を提供する。

【解決手段】ゲート電極110gと保護ダイオード用電極115pとが互いに接続されている。絶縁膜113は、所定値以上の電圧がゲート電極110gに印加された場合にリーク電流を保護ダイオード用電極115pと電子走行層104及び電子供給層103との間に流し、所定値は、HEMTがオン動作する電圧より高く、ゲート絶縁膜109gの耐圧よりも低い。

(もっと読む)

レイアウト方法及び半導体装置の製造方法

【課題】ダブルパターニングによるトランジスタの特性ばらつきを抑える。

【解決手段】並列に配置される複数のゲート電極パターン10〜15を交互に、ダブルパターニングの第1の露光工程で形成する第1のパターン及び第2の露光工程で形成する第2のパターンとして設定し(ステップS1)、第1のパターンと第2のパターンとを並列に接続したトランジスタ対を含む回路をレイアウトすることで(ステップS2)、ダブルパターニングによるトランジスタの特性ばらつきが抑えられる。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの動作方法

【課題】 電源電圧が変動することを防止しながら、電圧生成部による電源電圧の生成能力を最小限にし、半導体メモリの消費電力を削減する。

【解決手段】 第1電圧生成部は、メモリセルに接続される第1信号線を選択する第1選択部に供給する第1電源電圧を生成する。第2電圧生成部は、メモリセルに接続される第2信号線を選択するために、第1選択部が動作を開始した後に動作する第2選択部に供給する第2電源電圧を起動信号の活性化中に生成する。スイッチは、短絡信号の活性化中に、第1電源線と第2電源線とを短絡する。第1制御部は、アクセス要求に応答して、起動信号を活性化し、短絡信号の非活性化に応答して起動信号を非活性化する。第2制御部は、起動信号の活性化から所定時間後に短絡信号を活性化し、アクセス要求に基づくアクセス動作の完了後に、短絡信号を非活性化する。

(もっと読む)

プロセッサ、及び制御方法

【課題】低消費電流で被制御デバイスの間欠動作を制御する。

【解決手段】被制御デバイスから入力されるデータを処理する第1の動作モードと、前記被制御デバイスから入力されるデータを処理せず前記第1の動作モードより消費電流が小さい第2の動作モードとを有する処理部を有し、さらに、前記処理部が前記第2の動作モードのときにクロックをカウントするカウンタと、前記カウンタによる前記クロックのカウント値が基準値に達するごとに前記被制御デバイスを所定の時間動作させるための動作信号を出力する信号出力部と、前記カウント値が前記基準値に達するごとに前記基準値を増加させて前記信号出力部に設定する設定部とを含むタイマ部とを有するプロセッサによれば、低消費電流で被制御デバイスの間欠動作を制御できる。

(もっと読む)

電源装置

【課題】回路規模が小さい電源装置を提供する。

【解決手段】電源装置は,第1インダクタと,入力電源から第1インダクタへ供給される電流をスイッチングする第1スイッチング素子と,第1スイッチング素子を駆動する第1駆動制御回路と,第1インダクタから電流が出力される第1サブ出力端子とを有する第1サブ電源モジュールと,第2インダクタと,入力電源から第2インダクタへ供給される電流をスイッチングする第2スイッチング素子と,第2スイッチング素子を駆動する第2駆動制御回路と,第2インダクタから電流が出力される第2サブ出力端子とを有する第2サブ電源モジュールと,第1,第2サブ出力端子が接続された共通出力端子とを有し,第1スイッチング素子のオン動作は,共通出力端子の出力電圧が第1電圧より低いか否かに応じて制御され,第2スイッチング素子のオン動作は,出力電圧が第1電圧と異なる第2電圧より低いか否かに応じて制御される。

(もっと読む)

半導体記憶装置

【課題】データの読み出し速度を向上する。

【解決手段】半導体記憶装置1は、メモリセルアレー1aと、コラム線1bと、第1および第2のデータ線1d,1eと、データの読み出し時には、コラム線1bに第1および第2のデータ線1d,1eの一方を選択して接続し、データの書き込み時には、コラム線1bに第1および第2のデータ線1d,1eを接続するスイッチ1cと、第1および第2のデータ線1d,1eに接続された読み出し回路1fと、第1および第2のデータ線1d,1eに接続された書き込み回路1gと、を有する。

(もっと読む)

半導体メモリ、システムおよび半導体メモリの製造方法

【課題】 アドレス端子で受ける外部アドレスを用いて、リアルワード線を選択することなく、任意の冗長ワード線を選択する。

【解決手段】 半導体メモリは、複数のリアルワード線および複数の冗長ワード線を有するメモリブロックと、アドレス端子で受ける外部アドレスの一部である第1アドレスをデコードして第1デコード信号を出力し、テストモード中にデコード動作を禁止する第1デコーダと、通常動作モード中に、外部アドレスの別の一部である第2アドレスまたは不良の救済に使用する冗長ワード線を示す冗長アドレスをデコードし、テストモード中に第2アドレスをデコードし、第2デコード信号を出力する第2デコーダと、第1デコード信号および第2デコード信号に応じて、リアルワード線を選択する第1ドライバと、第2デコード信号に応じて、冗長ワード線を選択する第2ドライバとを有している。

(もっと読む)

半導体記憶装置

【課題】メモリセルトランジスタからのデータの読み出しを高速化する。

【解決手段】メモリセルアレイ121は、メモリセルトランジスタ131及びローカルビット線LBLを含む第1回路部と、ローカルビット線LBLをグローバルビット線GBLに接続してメモリセルトランジスタ131に対する書き込み及び読み出しを行う第2回路部を含む。この第2回路部の、グローバルビット線GBLの電圧が印加されるnMOSトランジスタ151,152,154等に、耐圧を電源電圧としたものを用い、読み出しの高速化を図る。書き込みは、グローバルビット線GBLに電源電圧以下の電圧を印加し、ソース線SLに電源電圧よりも高い電圧を印加することで行う。

(もっと読む)

171 - 180 / 2,507

[ Back to top ]