富士通セミコンダクター株式会社により出願された特許

181 - 190 / 2,507

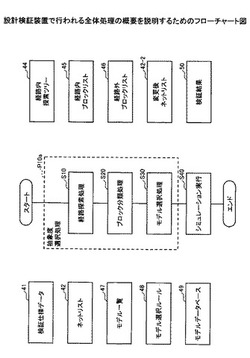

設計検証方法及びプログラム

【課題】 本発明の課題は、検証仕様に従った経路探索の結果を用いて、経路外のブロックの動作の抽象度を変更することにより高速にかつ適切にシミュレーションを行えるようにすること。

【解決手段】 上記課題は、コンピュータによって実行される設計検証方法であって、複数のブロックで構成される回路の検証に係る端子情報に基づいて、記憶部に格納されたネットリストを参照することによって、該ブロック間の接続関係に従って経路を探索し、前記ネットリスト内に記述される、前記探索された経路外のブロックの動作の抽象度を変更することを特徴とする設計検証方法により達成される。

(もっと読む)

画像処理装置

【課題】 画質の劣化を抑制しつつ、メモリのオーバーフローを低減する。

【解決手段】 画像処理装置は、映像データを符号化する符号化部と、符号化部で符号化された映像データを記憶する記憶部と、記憶部の空き容量と予め設定された閾値とを比較する監視部と、空き容量が閾値以下のとき、符号化対象のフレームに対応する映像データが符号化部で符号化される前に、符号化対象のフレームの画像サイズを縮小する画像縮小部とを有している。

(もっと読む)

欠陥検査装置および欠陥検査方法

【課題】欠陥検査工程における未検査を抑制すること。

【解決手段】ウエハを保持するステージ12と、前記ステージに保持されたウエハのアライメントを行なうアライメント部32と、アライメントされた前記ウエハ表面の欠陥を検査する検査部34と、前記アライメント部が前記アライメントを開始してから前記欠陥の検査が終了するまでの時間である検査時間が所定時間より短い場合、前記アライメント部に前記アライメントを再度行なわせ、前記検査部に前記欠陥を再度検査させる制御部36と、を具備する欠陥検査装置。

(もっと読む)

半導体装置の製造方法

【課題】DHF処理後に実施されるHPM処理またはAPM処理を、良好に行うことができる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、槽内で、シリコン基板を含むウエハを希フッ酸処理する工程と、槽内に水を導入して、槽内から希フッ酸を排出する工程と、槽内から希フッ酸が排出された後、温水の導入時点が、H2O2の導入時点と同時かH2O2の導入時点よりも遅くなるように、槽内に、H2O2と、上記水よりも温度の高い温水とを導入する工程とを有する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】高耐圧トランジスタ形成に適した半導体装置の新規な製造方法を提供する。

【解決手段】

半導体装置の製造方法は、シリコン基板に第1導電型第1領域と、第1領域に接する第2導電型第2領域を形成し、ゲート絶縁膜を形成し、第1領域と第2領域とに跨がるゲート電極を形成し、ゲート電極上から第2領域上に延在する絶縁膜を形成し、ゲート電極をマスクとし第2導電型不純物を注入してソース領域およびドレイン領域を形成し、ゲート電極および絶縁膜を覆って金属層を形成し熱処理を行って、ソース領域、ドレイン領域及びゲート電極にシリサイドを形成し、層間絶縁膜にソース領域、ドレイン領域、ゲート電極に達する第1、第2、第3コンタクトホール、及び絶縁膜に達する孔を形成し、第1〜第3コンタクトホール及び孔に導電材料を埋め込み、第1〜第3導電ビアと、孔の内部に配置された導電部材とを形成する。

(もっと読む)

半導体記憶装置

【課題】メモリセルトランジスタからのデータの読み出しを高速化する。

【解決手段】メモリセルアレイ121は、メモリセルトランジスタ131及びローカルビット線LBLを含む第1回路部と、ローカルビット線LBLをグローバルビット線GBLに接続してメモリセルトランジスタ131に対する書き込み及び読み出しを行う第2回路部を含む。この第2回路部の、グローバルビット線GBLの電圧が印加されるnMOSトランジスタ151,152,154等に、耐圧を電源電圧としたものを用い、読み出しの高速化を図る。書き込みは、グローバルビット線GBLに電源電圧以下の電圧を印加し、ソース線SLに電源電圧よりも高い電圧を印加することで行う。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

半導体装置

【課題】スキャンテストを可能にしながら内部データの漏洩及び改竄を防止する半導体装置を提供する。

【解決手段】複数のフリップフロップを有するユーザー回路と、テストモード時に、前記複数のフリップフロップを接続してスキャンチェーンを構成する接続経路とを有し、前記接続経路は、前記複数のフリップフロップのうちいずれかの前記フリップフロップの非反転出力値を論理演算して出力する論理演算回路、または、前記複数のフリップフロップのうちいずれかの前記フリップフロップの反転出力値を後段のフリップフロップに出力する反転値接続経路を有する。

(もっと読む)

キャリアの選択方法、及び、キャリア選択装置

【課題】

作業効率を向上できるキャリアの選択方法、及び、キャリア選択装置を提供する。

【解決手段】

キャリアの選択方法は、ウェハを格納するキャリアをコンピュータが選択するキャリアの選択方法であって、前記コンピュータは、前記ウェハに半導体素子を形成する製造条件又は製造実績に基づき、前記ウェハを格納するキャリアの使用時間を予測する予測工程と、前記ウェハを格納する前記キャリアの洗浄期限に基づき、前記キャリアの残使用時間を求める残使用時間演算工程と、前記残使用時間が前記使用時間よりも長いキャリアのうち、前記残使用時間と前記使用時間との差が所定時間以下のキャリアを前記ウェハの移載先として選択するキャリア選択工程とを実行する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造において基板の金属汚染を抑える。

【解決手段】半導体素子が設けられた基板の、半導体素子形成面とは反対側の裏面および端部に保護膜を形成する工程と、前記半導体素子形成面に設けられた金属含有膜を加工する工程と、前記金属含有膜の加工後に前記保護膜を除去する工程と、を含む半導体装置の製造方法。

(もっと読む)

181 - 190 / 2,507

[ Back to top ]