富士通セミコンダクター株式会社により出願された特許

11 - 20 / 2,507

半導体装置及び半導体装置の製造方法

【課題】半導体装置を薄型化する技術を提供する。

【解決手段】半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

(もっと読む)

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

半導体装置

【課題】メモリセルの動作を従来よりも高速化できる半導体装置を提供する。

【解決手段】フローティングゲートFGとコントロールゲートCG、第1導電型ソース13s及び第1導電型ドレイン13dを有する第1導電型MOSトランジスタ13と、前記フローティングゲートFGと前記コントロールゲートCG、第2導電型ソース14s及び第2導電型ドレイン14dを有する第2導電型MOSトランジスタ14と、前記第1導電型ドレイン13d及び前記第2導電型ドレイン14dに接続される第1のソース/ドレイン11bと、第2のソース/ドレイン11aと、ゲートを有する選択トランジスタ11と、前記第1導電型ソースに接続される第1電源線VpLと、前記第2導電型ソースに接続される第2電源線VnLと、前記選択トランジスタ11の第2のソース/ドレイン11aに接続されるビット線BLと、前記選択トランジスタ11のゲートに接続されるワード線WLと、を有する。

(もっと読む)

定電圧回路

【課題】出力電圧の急激な変動を生じさせることなく、出力トランジスタのバックゲートに供給する電圧を適切に制御できる定電圧回路を提供する。

【解決手段】出力電圧と基準電圧との差電圧を増幅する誤差増幅回路11と、誤差増幅回路の出力に基づいて出力電圧を制御する出力トランジスタ12とを有する定電圧回路にて、モニター用トランジスタ14によって検出されたリーク電流に比例した電圧を発振回路15A及びチャージポンプ回路16Aにより発生させて出力トランジスタのバックゲートに供給するようにして、出力トランジスタのバックゲート電圧をリニアに変化させて制御し、出力電圧の変動を抑制する。

(もっと読む)

バンドギャップ参照電源回路および非接触型デバイス

【課題】バンドギャップ参照電源回路の応答を速くすること。

【解決手段】温度係数が正の絶対温度比例電流を生成する絶対温度比例電流生成回路と、前記絶対温度比例電流のミラー電流を生成するミラー電流生成部と、前記ミラー電流に基づいて生成される温度係数が正の絶対温度比例電圧及び係数が負の相補的電圧から温度係数の絶対値が前記絶対温度比例電圧より小さいバンドギャップ参照電圧を生成するバンドギャップ参照電圧生成部とを有し、前記ミラー電流生成部と前記バンドギャップ参照電圧生成部の間の接続ノードから共通の出力ノードに接続され、当該出力ノードから前記バンドギャップ参照電圧を出力する複数のバンドギャップ参照電圧出力回路とを有し、前記複数のバンドギャップ参照電圧出力回路のうちの一部の回路は、前記ミラー電流生成部と前記接続ノードの間及びバンドギャップ参照電圧生成部と前記接続ノードの間それぞれに設けられた1及び第2のスイッチ回路を有すること。

(もっと読む)

半導体装置の製造方法

【課題】半導体素子等の複数の電子部品を備え、薄型化、小型化及び製造の低コスト化の要求に対応することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置100は、支持基板11と、前記支持基板11の一方の主面に搭載された第1の半導体素子21と、前記支持基板11と前記第1の半導体素子21との間に配置された電子部品31と、を具備し、前記支持基板11は、前記第1の半導体素子21から離間する方向に変形して形成される凹部Sを有し、前記電子部品31は、その厚さの少なくとも一部が前記凹部Sに収容されて搭載されてなることを特徴とする。

(もっと読む)

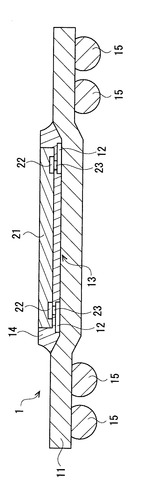

半導体装置及び半導体装置の製造方法

【課題】半導体装置の厚さ方向のサイズを縮小化する手段を提供する。

【解決手段】半導体装置1は、第一の半導体チップ11と、前記第一の半導体チップの電極形成面に形成された第一の導電体13と、第二の半導体チップ21と、前記第二の半導体チップの電極形成面に形成された第二の導電体22と、前記第二の半導体チップの電極形成面の、前記第二の導電体が形成されていない部分に形成された第三の導電体23と、前記第三の導電体に接続された外部電極15と、を備え、前記第一の半導体チップの電極形成面と前記第二の半導体チップの電極形成面とが向かい合うようにして、前記第一の半導体チップが前記第二の半導体チップの電極形成面に設置され、前記第一の導電体と前記第二の導電体とが接続されている。

(もっと読む)

不揮発性半導体記憶装置およびそのベリファイ制御方法

【課題】ベリファイに要する時間の短縮を図る。

【解決手段】ワード線WLとローカルビット線BLに接続された電気的に書き換え可能な複数のメモリセルMCを含むメモリセルアレイと、前記ローカルビット線に接続され前記各メモリセルのデータを反転してグローバルビット線GBLに出力する複数のローカルセンスアンプLSAと、前記複数のローカルセンスアンプの出力の論理和を演算するグローバルセンスアンプGBSAと、前記複数のローカルセンスアンプを動作させて該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第1ベリファイと,前記複数のローカルセンスアンプを停止させて,該各ローカルセンスアンプに接続された前記ローカルビット線と前記グローバルビット線を直結して該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第2ベリファイとを切り替えるアドレスデコーダと、を有する。

(もっと読む)

シミュレーション装置、シミュレーション方法、およびシミュレーションプログラム

【課題】ハードウェアとソフトウェアの協調動作のデバッグを効率的に行うこと。

【解決手段】シミュレーション装置100は、ソフトウェア101の実行中に、ハードウェアモデル102にアクセスする特定の関数が実行される場合、論理シミュレータ103側となるC−SVインターフェース104にて特定の関数の関数名を取得する。次に、C−SVインターフェース104は、関数名を記憶領域に格納する。また、論理シミュレータ103も、ハードウェアモデル102のシミュレーションの結果を記憶領域に格納する。波形ビューワ111は、記憶領域に格納されたシミュレーションの結果と関数名とを、時系列で対応付けて表示する。

(もっと読む)

半導体モジュール、半導体モジュールの製造方法及びカード

【課題】外観が良好な高品質のカードを提供する。

【解決手段】ICモジュール10がカード基材と一体化されてICカードが形成される。ICモジュール10は、モジュール基板11に設けられたICチップ12と、ICチップ12に電気的に接続されたアンテナ接続用端子11cと、モールド部14とを含む。アンテナ接続用端子11cは、ICモジュール10と一体化するカード基材に設けられるアンテナに、導電部材を用いて電気的に接続される。モールド部14は、チップ封止部14aと、アンテナ接続用端子11cに設けられたダム枠部14bとを有する。ダム枠部14bを設けることで、カード基材との一体化の際に用いられる導電部材の流出が抑えられ、カードの外観不良の発生が抑えられる。

(もっと読む)

11 - 20 / 2,507

[ Back to top ]