富士通セミコンダクター株式会社により出願された特許

2,001 - 2,010 / 2,507

電子装置

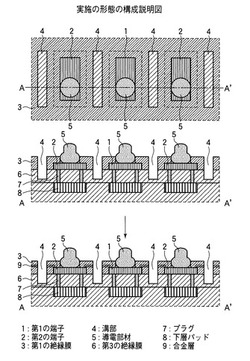

【課題】 電子装置に関し、隣接するパッド間のメタルショートを抑制する。

【解決手段】 電子部品と、前記電子部品上に形成される第1の端子および第2の端子と、前記電子部品上に形成され、前記第1の端子及び前記第2の端子が露出する開口を備えた第1の絶縁膜と、前記第1の端子及び第2の端子の少なくとも一方に接続され、前記第1の端子及び前記第2の端子とは異なる材料を含む導電部材と、前記第1の端子と前記第2の端子との間の前記第1の絶縁膜に形成される溝部とを備える。

(もっと読む)

情報処理システム及びファームウェア実行方法

【課題】本発明は、ファームウェアのダウンロードを高速に行う情報処理システムを提供することを目的とする。

【解決手段】情報処理システムは、制御CPUと、処理対象のデータを含む入力ストリームを受け取りメモリに転送するストリームインタフェースを含み、ストリームインタフェースによりファームウェアを含むストリームデータを受け取りメモリに格納するダウンロード処理を制御CPUの指示により実行すると共に、メモリに格納されたストリームデータを制御CPUが解析することによりファームウェアをメモリ空間に展開し、メモリ空間に展開されたファームウェアを制御CPUが実行することにより処理対象のデータに対する処理を実行することを特徴とする。

(もっと読む)

半導体装置のデータ作成方法、および電子線露光システム

【課題】露光データ作成の負担の増大を抑制し、少ない計算負荷で、電子線露光による形状が光露光で加工される形状に近似するような電子線用露光データを作成する。

【解決手段】本方法は、半導体装置の設計データから電子線露光に使用される電子線露光データを作成し、電子線露光データを基に電子線露光によって基板上に形成される電子線露光パターンの形状と半導体装置の設計データを基に光露光によって基板上に形成される光露光パターンの形状との相異部分を示す差分情報を抽出し、電子線露光パターンの形状と光露光パターンの形状との相異部分の寸法が所定の基準値内に収まったか否かを判定し、差分情報にしたがって、電子線露光データのパターンを形状変化させて形状変化露光データを取得し、電子線露光データを更新する更新ステップと、相異部分の寸法が所定の基準値内に収まっていないときに、差分抽出、判定、および更新を繰り返す。

(もっと読む)

情報処理装置、半導体集積回路装置及びブート方法

【課題】ブートプログラムとメインプログラムとが格納されたシリアルインタフェースの不揮発性メモリと、揮発性メモリとが接続される半導体集積回路装置であって、外部部品の増加を招くことがなく、かつ、設計期間の短縮化を図ることができ、かつ、ブートプログラムの改版時にレチクル費用が発生しないようにした半導体集積回路装置を提供する。

【解決手段】システムLSI2は、シリアルFlashメモリ3用のインタフェースであるブートローダ8を設け、シリアルFlashメモリ3からブートプログラムをリードし、該リードしたブートプログラムを実行してシリアルFlashメモリ3内のメインプログラムをSDRAM4にコピーする。

(もっと読む)

配線基板及び半導体装置

【課題】 配線基板及び半導体装置に関し、多層ビルドアップ基板等の配線基板に加わる応力によるフィルドスタックビアのビア破断を防止する。

【解決手段】 導体層と、前記導体層の表面に形成される第1の凹部と、前記導体層上に形成される第1の絶縁層と、前記第1の絶縁層に形成され、前記第1の凹部を露出させる第1の開口部と、前記第1の開口部内に配置され、少なくとも一部が前記第1の凹部内に埋め込まれる第1のフィルドビアと、前記第1の絶縁膜及び前記第1のフィルドビア上に形成される第2の絶縁層と、前記第2の絶縁層に形成され、前記第1のフィルドビアを露出させる第2の開口部と、前記第2の開口部内に配置され、前記第1のフィルドビアに接続される第2のフィルドビアとを備える。

(もっと読む)

電子部品収容テープ

【課題】 電子部品収容テープに関し、ガルウイング状のリード端子を有する電子部品の収容/テーピング/輸送/基板への実装段階において、電子部品の外形保護、リード端子の保護を図り、且つ、安全に取り出す。

【解決手段】 電子部品本体の収容部の周囲に、電子部品の端子と接する位置に配置される畝条突起部の形態を、電子部品本体の4つの隅部以外の位置において、その高さ或いは幅の少なくとも一方を電子部品の端子との接触面積を有為に低減する程度に不均一にする。

(もっと読む)

半導体装置の製造方法及び熱処理装置

【課題】 酸素濃度及びアルゴン濃度が制御され、且つ密閉された雰囲気下で、強誘電体膜の熱処理工程を実施することができる半導体装置の製造方法及び熱処理装置を提供する。

【解決手段】 部材が挿入でき、且つ減圧可能である熱処理室と、熱処理室に設けられた、熱処理室内への気体導入及び気体排気が可能である開口と、熱処理室内における気体の圧力を検出し、圧力に関する検出情報を出力する検出部と、熱処置室内の部材を加熱する加熱部と、開口による熱処理室内の気体排気を可能にする制御と、熱処理室内の密閉、開口による熱処理室内の気体導入、及び加熱部による部材の加熱を検出情報に基づいて行う制御と、を行う制御部と、を有する。

(もっと読む)

半導体装置

【課題】プロセス工程及び開発期間を減らし、サイズを小さくすることができる静電気放電保護回路を有する半導体装置を提供することを課題とする。

【解決手段】入出力パッド(101)と、電源電圧が供給される電源電圧ノード(VDE)と、基準電位が供給される基準電位ノード(GND)と、アノードが前記入出力パッドに接続され、カソードが第1のノードに接続される第1のダイオード(131)と、前記入出力パッド及び前記電源電圧ノードに接続され、前記入出力パッドに前記電源電圧より低い電圧が入力されると、前記第1のノードが前記電源電圧になるように制御する電位制御回路(103)と、前記入出力パッドに静電気が入力されると静電気オン信号を出力するトリガ回路(109)と、前記静電気オン信号が出力されると、前記第1のノード及び前記基準電位ノード間に静電気放電電流を流す静電気放電サージパス回路(108)とを有する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】半導体装置の配線層の信頼性を高める。

【解決手段】層間絶縁膜3に形成した配線溝4内に、バリアメタル膜5を介して、CuMnシード膜6及びCu膜7を有する配線部1を形成した後、SiH4とNH3のガスに曝し、その配線部1の表面にOを含有しないSiNの保護層8を形成する。この上にキャップ膜9を形成する。キャップ膜9の形成時には、配線部1のバリアメタル膜5との界面領域にはMnO層10が形成される一方、配線部1の上面には保護層8があることでMnの析出が抑制される。配線部1のMn含有量を高めても、配線部1とキャップ膜9との間にMnを含有するバリア性の低い層が形成されることがなく、エレクトロマイグレーション耐性及びストレスマイグレーション耐性の向上を図ることができる。

(もっと読む)

プロセッサ

【課題】 プロセッサにおいて中央処理回路を異常状態から所望の正常状態に復帰させる機能を簡易な回路構成により実現する。

【解決手段】 中央処理回路(140)は、条件付分岐命令に関して強制ジャンプの有効/無効を示すレジスタ(149)を有し、条件付分岐命令の実行時にレジスタ(149)が有効を示す状態であれば分岐条件が成立したものと判定する。レジスタ(149)は、タイマ回路(130)の割り込み要求の発行に伴って無効を示す状態から有効を示す状態に遷移する。メモリ回路(110)に格納されるプログラムは、条件付分岐命令を用いたループ処理に関して条件付分岐命令の分岐条件の成立がループ処理の終了条件となるように生成される。

(もっと読む)

2,001 - 2,010 / 2,507

[ Back to top ]