富士通セミコンダクター株式会社により出願された特許

201 - 210 / 2,507

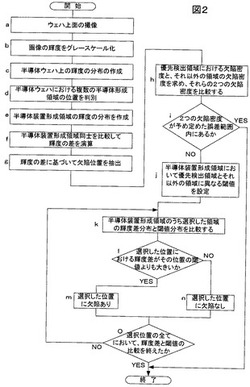

検査装置及び検査方法

【課題】画像から取得される欠陥から目的欠陥を抽出するための検査方法を提供する。

【解決手段】複数の検査対象領域の画像データを取得し、前記複数の検査対象領域のうち同じ構造を形成する領域同士の同じ位置の輝度を比較して輝度の差から輝度差分布を求め、前記複数の検査対象領域のそれぞれにおいて、優先的に検査をしたい優先検出領域の閾値がその他の領域の閾値よりも低くなるよう閾値分布を設定し、前記輝度差分布のうち前記閾値分布以上になる位置を目的欠陥発生位置と判定する、処理を有する。

(もっと読む)

半導体装置の製造方法

【課題】王水を用いることなくニッケルプラチナ膜の未反応部分を選択的に除去しうるとともに、プラチナの残滓が半導体基板上に付着するのを防止しうる半導体装置の製造方法を提供する。

【解決手段】シリコン基板10上に、ゲート電極16と、ゲート電極16の両側のシリコン基板10内に形成されたソース/ドレイン拡散層24とを有するMOSトランジスタ26を形成し、シリコン基板10上に、ゲート電極16及びソース/ドレイン拡散層24を覆うようにNiPt膜28を形成し、熱処理を行うことにより、NiPt膜28とソース/ドレイン拡散層24の上部とを反応させ、ソース/ドレイン拡散層24上に、Ni(Pt)Si膜34a、34bを形成し、過酸化水素を含む71℃以上の薬液を用いて、NiPt膜28のうちの未反応の部分を選択的に除去するとともに、Ni(Pt)Si膜34a、34bの表面に酸化膜を形成する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】安定に動作する半導体装置を提供する。

【解決手段】本明細書に開示する半導体装置は、基板11内に形成された第1導電型のウェル13と、ウェル13上にゲート絶縁膜17を介して配置されるゲート電極18と、ゲート電極18を挟んで基板11内に対向して配置される第2導電型のソース領域15及びドレイン領域16と、基板11内にソース領域15と隣接して配置され、ウェル1に電気的に接続される第1導電型のウェルタップ19と、ウェル13とウェルタップ19とに接し、ウェル13よりも不純物濃度が高く、第1導電型を有するポケット領域20と、を備える。

(もっと読む)

電子機器

【課題】スペクトラム拡散クロックに基づき動作する第1の回路ユニットとPLLクロックに基づき動作する第2の回路ユニットとの間で通信を行う場合,クロック乗り換え処理によるデータ通信のレイテンシを小さくし,単位時間当たりのデータ通信量の低下を防止する電子機器を提供する。

【解決手段】検出部5は,スペクトラム拡散クロックの周波数とPLLクロックの周波数との周波数差が第1の所定範囲内か否かを検出する。バスブリッジ部3は,周波数差が第1の所定範囲内の場合に,第1の回路ユニット1と第2の回路ユニット2との間で同期通信を実行し,周波数差が第1の所定範囲外の場合に,第1の回路ユニット1と第2の回路ユニット2との間で非同期通信を実行する。

(もっと読む)

検証方法及び検証プログラム

【課題】回路検証に用いるシナリオ等のプログラムを効率的に開発する。

【解決手段】コンピュータが、検証対象に対する命令を記述したシナリオ(S65)の所定記述部分の命令実行を制限する制限情報を含んだ設定制限リスト(S67)を用い、その内容を示すシナリオチェッカ(S69)を生成する。コンピュータは、検証対象のシミュレーション(S74)において、シナリオ(S65)の上記所定記述部分の命令実行時に、シナリオチェッカ(S69)を用いて当該命令が制限情報を含むか否かチェックし、その結果(S75)を出力する。

(もっと読む)

電源装置、制御回路、電子機器及び電源の制御方法

【課題】コイルのインダクタンス値の変動に伴って位相余裕が小さくなることを抑制できる電源装置を提供する。

【解決手段】DC−DCコンバータ1のコンバータ部2は、入力電圧Viが供給されるトランジスタT1と、トランジスタT1と出力電圧Voを出力する出力端子Poとの間に接続されたコイルL1とを有している。また、DC−DCコンバータ1の制御回路3は、参照電圧VR1にスロープを付加するコンデンサC3及びスイッチ回路SW1と、出力電圧Voに応じた帰還電圧VFBと上記スロープが付加された参照電圧VR1との比較結果に応じたタイミングでトランジスタT1をスイッチングする制御部とを有している。さらに、制御回路3は、コイルL1に流れるコイル電流ILを微分した結果に基づいて、参照電圧VR1のスロープのスロープ量を調整する検出回路40及び電流源21を有している。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

復調回路、復調方法および受信装置

【課題】受信性能を向上させることができる復調回路、復調方法および受信装置の提供を図る。

【解決手段】受信信号を復調した復調信号を用いて、硬判定処理を行う硬判定処理部71,74,77と、前記復調信号の遷移個所に対する割り当て範囲を決定し、ビットの尤度値を算出して軟判定処理を行う軟判定処理部72,75,78と、を有する。

(もっと読む)

真空ポンプの運転方法及び半導体装置の製造方法

【課題】反応生成物の付着を抑制し得る真空ポンプの運転方法及び半導体装置の製造方法を提供する。

【解決手段】吸気口30と排気口34とを有するケーシング22と、吸気口と排気口との間のケーシングの内部空間36内に設けられたロータ38と、ロータを回転させるモータ44とを有する真空ポンプ22の運転方法であって、加熱されたパージガスを、内部空間に達する孔46を介して内部空間内に導入しながら運転を行う。

(もっと読む)

受信回路、システム装置、及びタイミング調整方法

【課題】データを取り込むタイミングを調整すること。

【解決手段】メモリインタフェース回路12のマスク生成部37は、データ列DQと同期したストローブ信号DQS(内部ストローブ信号IRS)に基づいて、データ列DQを受け取る期間に応じた内部マスク信号CKMを生成する。DLL回路41は、レジスタ41aの設定値に応じて内部クロック信号CK2を遅延した内部クロック信号CKSを生成する。フリップフロップ回路33,34は、アンド回路38により内部マスク信号CKMと内部クロック信号CKSを合成した内部ストローブ信号CSTに応じて受信データ列RDQをラッチする。調整回路50は、DLL回路51,52の出力信号に基づいて、内部マスク信号CKMと内部ストローブ信号CSTの位相関係を検出し、レジスタ41aの設定値を更新して内部ストローブ信号CSTの位相を調整する。

(もっと読む)

201 - 210 / 2,507

[ Back to top ]