富士通セミコンダクター株式会社により出願された特許

2,401 - 2,410 / 2,507

基板識別方法及び基板識別装置

【課題】基板の識別を、塵埃を発生することなくかつ安価、簡単に行なう。

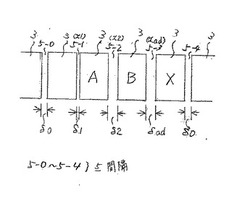

【解決手段】ステッパで基板に露光されたパターンの複数の所定位置xiの間隔δiを測定し識別情報として保存する。後に識別が必要になったとき、被識別基板の所定位置xiの間隔δiを測定し、保存された識別情報と一致する基板と識別される。他の方法として、所与の識別情報とずれ量Δiとの関係に基づき、所定位置xiの間隔δiにずれ量Δiを加えて露光する。後に識別が必要になったとき、所定位置xiの間隔δiのずれ量Δiを測定し、このずれ量Δiに対応する識別情報を識別情報とずれ量Δiとの関係から求め比較値とする。この比較値と一致する識別情報を有する基板として識別される。

(もっと読む)

トランスコード装置、トランスコーダ、デコーダおよびトランスコード方法

【課題】再エンコード(トランスコード)前のデコード画像にエラーが発生してもエラーの影響が低減されるトランスコード装置の実現。

【解決手段】第1の方式で符号化された画像データをデコードするデコーダ2と、デコーダから供給される画像データを、第2の方式で再エンコードするトランスコーダ3と、を備えるトランスコード装置であって、デコーダ2は、デコード時にデコードエラー量を算出して出力し、トランスコーダ3は、デコードエラー量および再エンコード時の情報に基づいて、再符号化した画像データをそのまま出力するか、スキップデータに置き換えて出力する。

(もっと読む)

半導体製造装置、半導体装置の製造方法、及びこれらに使用するシール部材

【課題】排気配管及び反応装置内に反応生成物が析出しにくい半導体製造装置を提供すること。

【解決手段】減圧雰囲気中で半導体基板の処理を行う反応装置70と、前記反応装置内のガスを排気する真空ポンプ80と、前記反応装置70と真空ポンプ80とを接続する排気管部とを有する半導体製造装置10において、前記配管部を外部から加熱する被覆加熱手段13と、シール部材15を内部から加熱するシール部材加熱手段と、排気配管11及びシール部材15の温度を検出する温度センサ14,16を設ける。温度コントローラ17及び18により、排気配管11とシール部材15の内面を反応生成物よりも高い温度であって、かつ等しい温度とする。これにより排気管内の温度が均一となり、反応生成物の析出を抑制できる。

(もっと読む)

半導体装置

【課題】複数の電源ブロックに分割した半導体装置にて、誤動作を引き起こし得る状態が発生した場合に、その発生を簡便かつ速やかに検出できるようにする。

【解決手段】異なる電源ブロックに配置され、クロックに同期して動作する第1及び第2の記憶回路と、一方の記憶回路の出力端子と他方の記憶回路の入力端子との間に接続される第1及び第2の遅延回路と、記憶回路の入力信号及び出力信号に基づいて誤動作が生じ得る状態であるか否かを判定し、判定結果をエラー検出信号として出力する判定回路とを備え、第1及び第2の記憶回路に異なる初期値を与えて、記憶回路間においてトグル状態で信号が送受信されているか否かをモニターすることにより、誤動作が生じ得る状態になったことを簡便かつ速やかに検出できるようにする。

(もっと読む)

ディスプレイ制御回路およびディスプレイ装置

【課題】簡易な構成で調停を行うことができる。

【解決手段】ディスプレイ制御回路1は、複数のマスタ2a、2bとの間でディスプレイに画像を表示する条件を規定した属性情報をやり取りする回路である。ディスプレイ制御回路1は、属性情報を格納するメモリ3と、マスタ2a、2bに対応して設けられ、マスタ2a、2bのメモリ3へのアクセス要求を受け付ける複数のチャネル4a、4bと、ハードウエアで構成され、各チャネル4a、4bが受け付けたアクセス要求を調停し、選択した1つのアクセス要求のメモリ3へのアクセスを許可する調停制御部5と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】ニッケル膜又はニッケル合金膜を用いてシリサイド化を行う場合において、シリサイド化されたソース/ドレイン拡散層のシート抵抗及びそのばらつきを低減するとともに、接合リーク電流を低減しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上10に、ゲート電極16とソース/ドレイン拡散層24とを有するトランジスタ26を形成する第1の工程と、半導体基板上に、ゲート電極及びソース/ドレイン拡散層を覆うように、ニッケル又はニッケル合金より成る金属膜28を、基板温度を220℃〜300℃とした状態で形成する第2の工程と、金属膜とソース/ドレイン拡散層の上部とを反応させ、ソース/ドレイン拡散層上に、ニッケルシリサイド又はニッケル合金シリサイドより成るシリサイド膜34bを形成する第3の工程とを有している。

(もっと読む)

半導体集積回路のレイアウト設計方法およびレイアウト設計プログラム

【課題】配線占有領域を削減し、冗長ビア配線ルール違反箇所を無くし又は削減することができるようにした半導体集積回路のレイアウト設計方法を提供する。

【解決手段】詳細配線(第1工程)で冗長ビア配線ルール違反が発生した場合、セルの向きを変更して冗長ビア配線ルール違反箇所を解消する配線修正を行うための準備(第2工程〜第12工程)を行い、その後、セルの向きを変更して配線修正を行い(第13〜第15工程)、経路更新を行う(第16工程)工程を用意する。

(もっと読む)

半導体装置およびその導体配線の接続検査方法

【課題】微細パターンを有する半導体デバイスの導体配線のインライン接続検査を、安価な装置で、効率良く実施することを目的とする。

【解決手段】接地(電源接続)電極パターンと非接地(フローティング)電極パターンを複数交互に配置し、接地電極(電源接続)パターンと非接地(フローティング)電極パターンそれぞれを2本以上相互接続し、各相互接続個所から延伸して電極パターンより幅の広い延伸配線を形成し、かつ接地電極パターンの延伸配線及び非接地電極パターンの延伸配線とが交互に配置された、延伸配線交互配置領域を形成する。この領域をSEM走査して、各延伸配線のSEM像明暗配列状態から、電極パターンの欠陥情報(オープン・ショートの判定、欠陥電極の位置など)を得る。

(もっと読む)

CANのエラー検出評価方法およびCAN通信装置

【課題】CANのエラー検出評価環境のコストの低減を図ること。CANのエラー検出評価環境の規模を小さくすること。

【解決手段】テストモード時に、被試験ノードと治具ノードを同一のCAN伝送路に接続し、被試験ノードと治具ノードとで、データフレームのID値およびDLC値を同じに設定する。被試験ノードのデータフレームのデータ領域に設定するデータ値のいずれかのビットのレベルをリセッシブとし、それに対応する治具ノードのデータフレームのビットのレベルをドミナントにする。このように設定されたデータフレームを被試験ノードおよび治具ノードからそれぞれCAN伝送路に送信すると、被試験ノード1がCAN伝送路へ送信するデータフレームのデータ値と、被試験ノード1がCAN伝送路から受信するデータフレームのデータ値が異なるので、ビットエラーが発生する。

(もっと読む)

インタフェース回路

【課題】最終製品に使用されている自社製の通信IPマクロであるインタフェース回路を自社製の通信IPマクロであると容易に確認することができるようにしたインタフェース回路を提供する。

【解決手段】SATAインタフェース回路29は、IPマクロ情報保持回路41と、セレクタ42と、特殊コマンド監視回路43とを含めて応答手段を構成し、ホストPC21から第1の特殊コマンドを受信したときは、CPU27にインタラプトを発行せず、IPマクロ情報保持回路41が保持するSATAインタフェース回路29のIPマクロ情報(IPマクロの種別、バージョン情報、コンフィギュレーション情報及び動作周波数)を応答データとしてホストPC21に自動送信する。

(もっと読む)

2,401 - 2,410 / 2,507

[ Back to top ]