富士通セミコンダクター株式会社により出願された特許

2,501 - 2,507 / 2,507

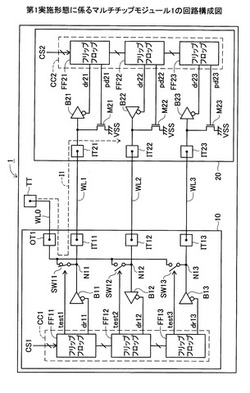

半導体装置および半導体装置モジュール

【課題】半導体装置間の内部結線の接続状態をより高精度に試験することが可能な半導体モジュールおよび半導体装置を提供すること。

【解決手段】試験対象となる配線の一端側にテスト端子TTを接続するスイッチSW11ないしSW13と、試験対象となる配線の他端側に接地電位VSSを与えるトランジスタM21ないしM23とを備える。よって、試験対象の配線の一端に電源電位VDDを与え、試験対象の配線の他端に接地電位VSSを与えることで、試験対象の配線を含む電流経路を形成することができるため、オープン故障を検出することができる。また、試験対象の配線に電源電位VDDを与え、試験対象外の配線に接地電位VSSを与えれば、試験対象の配線とそれ以外の配線との間における電位差を発生させることができるため、ショート故障を検出することができる。

(もっと読む)

半導体装置の製造方法

【課題】金属層の損傷を抑制した半導体装置の製造方法を提供すること。

【解決手段】Cu配線2上に酸化膜3を堆積する工程と、前記酸化膜3をドライエッチングして、前記Cu配線2に通達するビアホールHを形成する工程と、前記ビアホールH内にDIWを供給する工程と、前記DIWを供給した後に、前記ビアホールH内に燐酸アンモニウムを供給する工程と、前記燐酸アンモニウムを供給した後に、前記ビアホールH内に導電材料5を埋め込む工程とを含む。

(もっと読む)

デカップリングセル配置方法及びデカップリングセル配置装置

【課題】デカップリングセルの配置を短時間で網羅的に行うことができるデカップリングセル配置方法を提供すること。

【解決手段】セル配置装置は、タイミング解析結果から着目パスにおけるタイミングスラック量を、当該着目パスの電源ノイズに対するタイミング余裕度として抽出し、該タイミング余裕度をノイズ許容量に変換し、該ノイズ許容量と着目パスにおける電源ノイズ量とを比較し、該比較結果に基づいてその着目パスに対するデカップリングセルの配置の要否を判断するようにした。即ち、タイミング余裕度に基づき、電源ノイズ量を算出し、その電源ノイズ量とノイズ許容量とを比較してデカップリングセルの配置するようにした。

(もっと読む)

半導体装置及びその製造方法

【課題】金属半導体化合物からなるゲート電極を採用して十分な低抵抗化を図るも、煩瑣な構成・製造工程を付加することなく、容易且つ確実にゲート電極の閾値電圧の十分に広範囲な制御を可能とし、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体領域に例えばシリコン基板を用い、ゲート電極材料に多結晶シリコンを用いる場合、多結晶シリコン膜を炭素、窒素及び酸素のうちから選ばれた少なくとも1種である添加元素を含有するように形成して半導体層とした後、この半導体層上にNi,Co,Pd,Pt等の高融点金属膜を積層して熱処理してシリサイド化し、ゲート電極を形成する。

(もっと読む)

半導体可変容量素子及びその製造方法

【課題】蓄積モードMOS容量型の半導体可変容量素子において、高周波特性を低下することなく、反転バイアス時にゲート絶縁膜直下に形成される反転層に蓄積されたキャリアを効率よく引き抜くことができる半導体可変容量素子及びその製造方法を提供する。

【解決手段】半導体基板10の第1の領域に形成されたNウェル16と、半導体基板10上に形成された絶縁膜18と、Nウェル16上に絶縁膜18を介して形成されたゲート電極20nとを有する容量と、半導体基板10の第1の領域に隣接した第2の領域に形成された第2導電型のPウェル14とを有し、ゲート電極20nは、端部が第2の領域に延在し、Pウェル14上に絶縁膜18を介して形成されている。

(もっと読む)

半導体装置とその製造方法、及び分割露光用マスク

【課題】分割露光に起因した不良を早期に簡便に発見することが可能な半導体装置とその製造方法、及び露光用マスクを提供すること。

【解決手段】導電膜42の上にフォトレジスト43を塗布する工程と、第1、第2サブフィールドSF1、SF2が画定された露光用マスク20を用いて、該第1、第2サブフィールドSF1、SF2のそれぞれに分けて形成されたモニターパターン22の像同士が繋がるようにフォトレジスト43を分割露光する工程と、フォトレジスト43を現像してレジストパターン44にする工程と、レジストパターン44をマスクにして導電膜42をエッチングすることにより、モニターパターン22に対応した導電性モニターパターン42aを形成する工程と、導電性モニターパターン42aの抵抗値Rを測定し、半導体装置が不良になるかどうかを抵抗値Rに基づいて判断する工程とを有する半導体装置の製造方法による。

(もっと読む)

高耐圧MOSトランジスタの製造方法、及び高耐圧MOSトランジスタ

【課題】 マスク工程を簡略化しながらも、レイアウト面積を縮小した高耐圧MOSトランジスタ、高耐圧MOSトランジスタの製造方法を提供することを目的とする。

【解決手段】 基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に形成されたゲート電極と、ゲート電極の一方の側に位置する基板の内部に形成されたドレイン領域と、ゲート電極の他方の側に位置する基板の内部に形成されたソース領域と、ドレイン領域上に形成され、且つ不純物拡散領域を介してドレイン領域と電気的に接続された堆積型ドレイン層と、ゲート電極のソース領域側の側壁に形成された第1側壁スペーサを構成する絶縁膜と、ゲート電極の前記ドレイン側の側壁に形成され、堆積型ドレイン層側壁に接する第2側壁スペーサを構成する絶縁膜と、を有する。

(もっと読む)

2,501 - 2,507 / 2,507

[ Back to top ]