富士通セミコンダクター株式会社により出願された特許

21 - 30 / 2,507

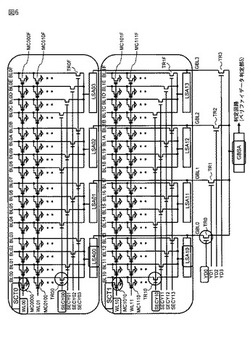

不揮発性半導体記憶装置およびそのベリファイ制御方法

【課題】ベリファイに要する時間の短縮を図る。

【解決手段】ワード線WLとローカルビット線BLに接続された電気的に書き換え可能な複数のメモリセルMCを含むメモリセルアレイと、前記ローカルビット線に接続され前記各メモリセルのデータを反転してグローバルビット線GBLに出力する複数のローカルセンスアンプLSAと、前記複数のローカルセンスアンプの出力の論理和を演算するグローバルセンスアンプGBSAと、前記複数のローカルセンスアンプを動作させて該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第1ベリファイと,前記複数のローカルセンスアンプを停止させて,該各ローカルセンスアンプに接続された前記ローカルビット線と前記グローバルビット線を直結して該複数のローカルセンスアンプに接続された複数のメモリセルのデータを同時にベリファイする第2ベリファイとを切り替えるアドレスデコーダと、を有する。

(もっと読む)

データ転送システム、データ転送方法、受信回路、及び受信方法

【課題】連続したデータの転送を可能とすること。

【解決手段】送信回路12は、データTDOを出力する毎に、ポール信号PLのレベルを反転する。受信回路13は、リードリクエスト信号REQに応答してポール信号を複数のタイミングで受け取るとともに、送信データTDOを複数のタイミングで受け取る。そして、受信回路13は、タイミングが異なる複数のポール信号に基づいて、受け取った複数のデータのうちの1つと等しい受信データRDOを出力する。

(もっと読む)

半導体装置の検査装置及び検査方法

【課題】半導体装置からのエミッションの検出を加熱しながら行う半導体装置の検査装置を提供する。

【解決手段】検査装置1は、半導体チップ2を載置する観察ステージ16を、半導体チップ2の基板材料と同じSiで製造し、半導体チップ2の裏面側に撮像素子35を配置した。半導体チップ2で発生した微弱な光は、半導体チップ2、観察ステージ16を透過して撮像素子35に入射する。観察ステージ16は、Siから製造されているので、ヒータ25によって簡単に加熱できる。また、観察ステージ16の上方には、プローブカード19及びLSIテスタ20が配置されており、半導体チップ2の回路のテストが可能である。

(もっと読む)

半導体素子の測定方法及びプローブカード

【課題】半導体素子の電気的な測定を複数回行なう場合であっても、正確に測定を行なうことができる半導体素子の測定方法を提供する。

【解決手段】半導体素子に形成された電極パッドにプローブを接触させて、前記半導体素子における電気的特性を測定する半導体素子の測定方法において、前記電極パッドに接触させた際に、先端部が前記電極パッドに対して第1の方向に動くプローブユニット61を前記電極パッドに接触させ測定を行なう第1の測定工程と、前記第1の測定工程の後、前記電極パッドに接触させた際に、先端部が前記電極パッドに対して第2の方向に動くプローブユニット62を前記電極パッドに接触させる第2の測定工程と、を有し、前記第1の方向と前記第2の方向とは異なる方向である。

(もっと読む)

半導体メモリ、半導体メモリの動作方法、システムおよび半導体メモリの製造方法

【課題】少ない数のコマンド端子を用いて、半導体メモリを効率よくアクセスする。

【解決手段】半導体メモリMEMは、選択信号に応じて選択される1つが動作し、複数の第1コマンド端子CMD0、CMD1にそれぞれ供給される複数の第1コマンド信号を受け、受けた第1コマンド信号を出力する複数の第1選択部SEL0、SEL1と、第1選択部の出力に接続され、第1コマンド端子の数より多く、少なくとも1つが第1選択部の複数に共通に接続され、第1選択部の1つから出力される第1コマンド信号を、第1同期信号SYNC1に応答して保持し、第2コマンド信号として出力する複数の保持部HLD0、HLD1、HLD2と、第2コマンド信号に応じた動作制御信号CNTを、第1同期信号に比べて発生頻度が低い第2同期信号SYNC2に応答して出力する動作制御部OPCと、動作制御信号に応じてアクセスされるメモリセルMCとを有している。

(もっと読む)

管理プログラム、管理方法、および管理装置

【課題】並列処理の効率化を図ること。

【解決手段】サーバSは、プロセスPの起動指定を受け付けると、実行中プロセスP群の中の子プロセスPについて、親プロセスPの並列処理数を取得する。そして、サーバSは、並列処理数が頭打ち並列処理数を超えている場合は、実行中プロセスPは親プロセスPの効率化に貢献していないと判断して、実行中プロセスPを停止する。これにより、サーバSは、親プロセスPの並列処理数を1つ減らして、並列処理数を適正化する。また、サーバSは、CPUリソースを使用可能にし、使用可能にしたCPUリソースを他のプロセスPの実行に使用して、CPUリソースを効率よく使用する。

(もっと読む)

画像処理装置、及び画像処理方法

【課題】立体動画像において復号エラーを精度よく修復する。

【解決手段】画像処理装置に、ピクチャ対のいずれかで復号エラーを検出する復号部と、エラーピクチャより過去に復号され、エラー対応箇所の周辺のブロックがエラーピクチャと近似するような近似ピクチャを含むピクチャ対におけるエラー対応箇所の視差をエラーピクチャとその対のピクチャにおけるエラー対応箇所の視差として推定する推定部と、エラーピクチャの対のピクチャにおけるエラー対応箇所から前記推定された推定視差分ずれた位置にあるブロックを、エラーブロックに適用して前記復号エラーを修復する修復部とを備え、復号エラーを精度よく修復する。

(もっと読む)

半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングにより半導体チップに分離する際、クラックやチッピングの発生を防ぐ。

【解決手段】電子回路が形成されている複数の半導体チップを作製するための半導体ウェハにおいて、切断される前の隣接する前記半導体チップの間には、スクライブ領域が設けられており、前記半導体チップは、ブレードにより前記スクライブ領域の一部を切断領域として除去することにより切断されて分離されるものであって、前記スクライブ領域には、前記半導体ウェハの状態において検査を行なうための検査用モニタ素子が形成されており、前記スクライブ領域の表面には、モニタ用電極パッドが設けられており、前記検査用モニタ素子と前記モニタ用電極パッドは、金属材料により形成されたモニタ用配線層及びモニタ用ビアにより接続されており、前記モニタ用配線層及び前記モニタ用ビアは、前記スクライブ領域内であって、前記切断領域の外側に形成されていることを特徴とする半導体ウェハにより上記課題を解決する。

(もっと読む)

ヒューズ素子読み出し回路

【課題】十分な読み出しマージンを確保し、ヒューズ素子のデータ読み出しの際に誤判定を防止することができるヒューズ素子読み出し回路を提供することを課題とする。

【解決手段】切断済みと未切断とで抵抗値が異なる第1のヒューズ素子(115)と、通常モードと試験モードとで異なる抵抗値を有する第1の抵抗回路(701,702)と、前記第1のヒューズ素子の抵抗値及び前記第1の抵抗回路の抵抗値に応じた読み出し電圧を出力する読み出し電圧出力回路(101)とを有することを特徴とするヒューズ素子読み出し回路が提供される。

(もっと読む)

エッチング装置

【課題】エッチング装置の透過窓の洗浄頻度を低減させる。

【解決手段】ICPエッチング装置1は、基板2のホルダ5が設けられた処理室3を有し、処理室3の上部には円筒形の透過窓11が取り付けられている。透過窓11の内周にはコーティング層23が形成されており、透過窓11の外側にはICPコイル25が配置されている。基板2のエッチング時には、ICPコイル25から電磁波が処理室3内のエッチングガスを励起させてプラズマを発生させる。プラズマ中のイオンなどは、基板2に到達して基板2上の薄膜をエッチングすると共に、コーティング層23をエッチングする。コーティング層23がエッチングされることで、基板2上の薄膜から放出される物質が透過窓11の内面に付着し難くなる。

(もっと読む)

21 - 30 / 2,507

[ Back to top ]