富士通セミコンダクター株式会社により出願された特許

901 - 910 / 2,507

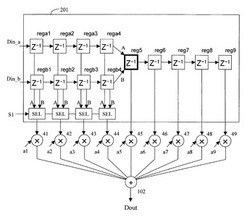

送信装置

【課題】OFDMシンボル間のデータ干渉を回避できるOFDM送信装置を提供することにある。

【解決手段】変調波を送信する送信装置において、複数の送信信号を逆フーリエ変換して互いに直交する周波数関係にある複数の搬送波信号を含む有効シンボルを生成し、有効シンボルの第1端から第1の期間の信号をガードインターバルとして有効シンボルの第1端と反対側の第2端に付加したOFDMシンボルを順次生成するOFDMシンボル生成部と、OFDMシンボルが有する複数のサンプリング点のデータ列を、規定のタップ数の第1のデータ列毎に順次畳込み演算する畳込みフィルタとを有し、畳込みフィルタは、前記有効シンボルの第1端のデータ列を含む前記第1のデータ列を畳込み演算する場合に、有効シンボルの第2端のデータ列を第1端のデータ列に周期的に付加した第1のデータ列を畳込み演算する送信装置。

(もっと読む)

パターン密度検証方法及びプログラム

【課題】チップ全体の密度検証においてマクロセル部分での設計規則違反の判定を出さないようにすること。

【解決手段】検証エリアの内側と外側に内側補助区画と外側補助区画とをそれぞれ設定し(ステップS19)、内側補助区画のパターン占有面積に外側補助区画のパターン占有面積を加味した検証エリアのパターン密度D2が密度基準を満たすか否かを判定する(ステップS20)。

(もっと読む)

周波数測定回路及びそれを有するPLLシンセサイザ

【課題】

被測定クロックの周期または周波数を高精度に計測する周波数計測回路を提供する。

【解決手段】

周波数測定回路は,被測定クロックの被測定エッジをカウントするカウンタと,基準クロックの基準エッジに応答して,前記カウンタのカウント値を記憶するカウンタラッチ回路と,直列に接続された複数の基本遅延回路を有し,前記被測定クロックを初段の前記基本遅延回路に入力して伝搬させる遅延回路と,前記基準エッジに応答して,前記遅延回路の複数の基本遅延回路の出力をそれぞれラッチする複数の遅延ラッチ回路と,前記遅延ラッチ回路がラッチした前記複数の基本遅延回路の出力に基づいて,前記被測定クロックの前記被測定エッジの前記遅延回路内での位置を検出するエッジ検出回路と,2つの基準エッジ間の前記カウント値と,前記2つの基準エッジでの前記第1のエッジ検出回路が検出する前記被測定エッジの位置情報とから,前記被測定クロックの周期または周波数を演算する演算器とを有する。

(もっと読む)

検証プロパティ開発支援方法及び検証プロパティ開発支援装置

【課題】低コストで容易に検証プロパティの信頼性を向上させることが可能な検証プロパティ開発支援方法及び検証プロパティ開発支援装置を提供することを目的とする。

【解決手段】検証プロパティの開発を支援する検証プロパティ開発支援方法であって、前記検証プロパティをグループ化するグループ設定手順と、同一グループ内の前記検証プロパティにおいて、各検証プロパティで検証される所定条件が同時期に不成立となるか否かを判定する判定手順と、を実行する。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に対する不純物の突き抜けを抑止する。

【課題を解決するための手段】半導体装置の製造方法は、基板上方に成膜した多結晶シリコンをエッチングして基板の第1領域上方に第1ゲート電極を形成し、基板の第2領域上方に第2ゲート電極を形成し、第1領域及び第1ゲート電極を覆う第1パターンを形成し、第2ゲート電極及び第1パターンをマスクにして第2領域に第1不純物を第1ドーズ量で注入して第2領域に第1エクステンション領域を形成し、第1ゲート電極、第1領域及び第2ゲート電極の上面を露出させた第2パターンを形成し、第1エクステンション領域を覆い、第1ゲート電極、第2ゲート電極及び第2パターンをマスクにして第1領域に第2不純物を第1ドーズ量よりも多いドーズ量で注入して第1領域に第2エクステンション領域を形成するとともに、第1ゲート電極及び第2ゲート電極の少なくとも上部をアモルファス化する。

(もっと読む)

半導体素子用収容器

【課題】 積み重ねた半導体素子用トレイ自体を相互に固定することを可能にし、半導体素子の飛散、トレイ枚数に関する制約などを生じさせるクリップ等の別個の固定手段を不要とする。

【解決手段】 トレイ10は、半導体素子40を収容するポケット13を有する。トレイ10は更に、上面側に第1の嵌合部15を有し、底面側に第2の嵌合部16を有する。複数のトレイ10を積み重ねるとき、下段のトレイと上段のトレイとを接触させながら相対的にスライドさせることにより、下段のトレイの第1の嵌合部15と上段のトレイの第2の嵌合部16とが嵌合し、上段のトレイと下段のトレイとが固定される。

(もっと読む)

半導体装置、及びその製造方法

【課題】基板の反りを抑制して半導体装置の信頼性の向上を図る。

【解決手段】樹脂材121と樹脂材122とを含む層120を備えた基板100と、基板100の主表面101の上方に搭載された半導体素子700と、基板100の主表面101の上方に、半導体素子700を覆って形成された封止樹脂層1100と、を有し、樹脂材122と封止樹脂層1100との熱膨張係数の差は、樹脂材121と封止樹脂層1100との熱膨張係数の差よりも小さく、半導体素子700の外縁703は、樹脂材122の上方に位置している。

(もっと読む)

半導体装置の製造方法

【課題】樹脂により囲まれる球状のはんだを良好に端子に接続するための半導体装置の製造方法を提供する。

【解決手段】一面に半導体素子が搭載されて樹脂封止された基板1のうち端子1bが露出する他面の上に、活性剤含有の熱硬化性樹脂膜8を形成する工程と、球状のはんだ9を熱硬化性樹脂膜8に押しつけて、端子1bに接触させる工程と、端子1bにはんだ9を押し当てた状態で、はんだ9に接触する領域の熱硬化性樹脂膜8に熱を加えて一部を半硬化する工程と、はんだ9を端子1bに押しつける力を解放する工程と、熱硬化性樹脂膜8の全体を加熱して、熱硬化性樹脂膜8の硬化率を上昇させるとともに、はんだ9を溶融して端子1bに接続する工程と、熱硬化性樹脂膜8の温度を下げるとともにはんだ9を硬化する工程とを含む。

(もっと読む)

半導体装置とその製造方法

【課題】

高温、長時間のアニールを必要とすることなく、低いオン抵抗を実現可能な高耐圧MOSトランジスタを含む半導体装置を提供する。

【解決手段】

半導体基板の高耐圧トランジスタ用第1導電型領域上にゲート電極を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第1のマスクをイオン注入マスクとして、ゲート電極を貫通する加速エネルギで第1導電型の不純物イオンを注入して、ソース領域で深く、ゲート電極下方で浅いチャネルドーズ領域を形成し、ゲート電極のドレイン側部分及びドレイン領域を覆う第2のマスク及びゲート電極をイオン注入マスクとして第2導電型の不純物をイオン注入してソースエクステンション領域を形成し、半導体装置を製造する。

(もっと読む)

有機ガス処理装置

【課題】小型で且つ運転が容易な有機ガス処理装置を提供すること。

【解決手段】紫外線を発生し、前記紫外線により光触媒に有機ガスを分解させる紫外線光源と、内壁が前記光触媒の皮膜で覆われ且つ前記紫外線を透す筒状体であって、前記紫外線光源を囲うように前記紫外線光源の長手方向に沿って配置され、且つ前記長手方向に延在する軸を中心に自転する複数の有機ガス光分解部と、複数の前記有機ガス光分解部を直列に連結して、前記有機ガス光分解部の連結構造体を形成する複数の連結管と、前記連結構造体の一端に設けられ、前記有機ガスを含むガスが流入する第1の開口部と、前記連結構造体の他端に設けられ、前記ガスが流出する第2の開口部とを有すること。

(もっと読む)

901 - 910 / 2,507

[ Back to top ]