エスケーハイニックス株式会社により出願された特許

21 - 30 / 122

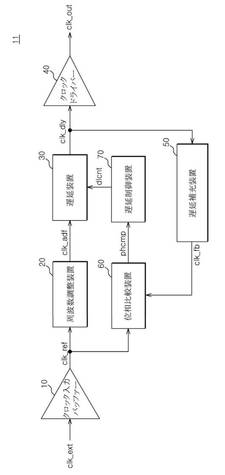

周波数調整装置及びそれを含むDLL回路

【課題】半導体集積回路の電磁干渉を減少させる周波数調整装置及びそれを含むDLL回路を提供する。

【解決手段】本発明の周波数調整装置は、基準クロックの周波数を複数の分周比に分周して複数のビットの周波数制御信号を生成する周波数制御信号生成部、及び前記複数のビットの周波数制御信号に応答して、入力される前記基準クロックの周波数を調整する周波数調整部とを含むことを特徴とする。

(もっと読む)

半導体装置

【課題】PVT変動に応じて動作駆動力を変更することが可能な、プリエンファシス動作をサポートするデータ出力回路を備える半導体装置を提供する。

【解決手段】インピーダンスコードPCODE<0:2>,NCODE<0:2>の変動に応じて値が調節されるプリエンファシスコードEM_PCODE<0:1>,EM_NCODE<0:1>を生成するコード生成部360と、出力データP_DATA,N_DATAを受信してデータ出力パッドDQに駆動し、インピーダンスコードに応じて駆動力が調節されるメイン駆動部311〜313,321〜323と、出力データを受信してデータ出力パッドに駆動し、プリエンファシスコードに応じて駆動力が調節される補助駆動部314〜315,324〜325とを備える。

(もっと読む)

揮発性メモリ装置のマルチレベルセルプログラム方法

【課題】頁バッファをプレーンの中央部に位置させ、上側メモリレジスタと下側メモリレジスタを区分させる不揮発性メモリ装置を提供する。

【解決手段】第1メモリセルグループと接続される第1レジスタ及び第2メモリセルグループと接続される第2レジスタを含む頁バッファが提供され、各メモリセルに対して下位ビットプログラムを完了する段階と、第1レジスタのデータラッチ部の第1ノードに上位ビットデータを設定する段階と、上位ビットプログラムを行う段階と、第1検証電圧以上にプログラムされた場合、第1ノードに第1データを設定する段階と、第2検証電圧以上にプログラムされた場合、第1ノードに第1データと相反したレベルの第2データを設定する段階と、第3検証電圧以上にプログラムされた場合、第1ノードに第1データを設定する段階と、第1ノードに設定されたデータにより上位ビットプログラムを繰り返す段階を含む。

(もっと読む)

デューティ比補正回路

【課題】入力される外部クロック信号の活性化エッジを用いてデューティ比を補正することができるデューティ比補正回路を提供する。

【解決手段】本発明のデューティ比補正回路は、第1の基準クロック信号及びリセット信号に応じて定義されるデューティ比の内部クロック信号を生成するデューティ調整手段と、第2の基準クロック信号及びフィードバックされる前記内部クロック信号に応答して前記リセット信号を生成するリセット信号生成手段とを備えることを特徴とする。

(もっと読む)

半導体集積回路

【課題】外部から印加された電圧のノイズを減少させて電圧を安定化させる半導体集積回路を提供する。

【解決手段】本発明は、電圧ノイズを減少させて電圧を安定化させる半導体集積回路において、第1電流が流れる第1内部回路と、第2電流が流れる第2内部回路と、前記第1電流のうちの一部と前記第2電流のうちの一部は第1接地パッドに流れ、残りの前記第1電流と残りの前記第2電流は第2接地パッドに流れるように構成された電圧安定化部とを含むことを特徴とする。

(もっと読む)

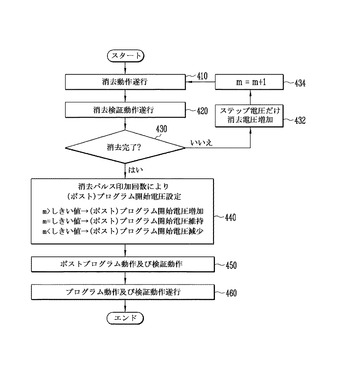

不揮発性メモリ装置のプログラム方法

【課題】 本発明の不揮発性メモリ装置のプログラム方法は、各セルのプログラム速度に応じてプログラム開始電圧を異なって設定する不揮発性メモリ装置のプログラム方法を提供することを目的としている。

【解決手段】 消去動作を行う段階と、前記消去動作が完了するまで消去パルス印加回数をカウントする段階と、前記カウントされた消去パルス印加回数としきい値を比較してプログラム開始電圧を設定する段階と、前記設定されたプログラム開始電圧に応じてプログラム動作を行う段階とを含む構成としたことを特徴とする。

【選択図】 図4  (もっと読む)

(もっと読む)

温度情報出力装置の温度情報出力方法

【課題】温度情報出力装置の面積を増やさなくとも動作可能な温度範囲を増やすことができる、温度情報出力装置の温度情報出力方法を提供する。

【解決手段】温度を感知し、当該温度に対応する第1の電圧VTEMPを出力するステップと、第1の電圧VTEMPと第2の電圧DACOUTとを比較するステップと、この比較結果に基づいて、デジタルコードDIGITAL_CODEを加減するステップと、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTを生成するステップとを含み、デジタルコードDIGITAL_CODEによって変化する第2の電圧DACOUTの変化幅が温度区間別に異なる。

(もっと読む)

半導体素子及びその製造方法

【課題】フラッシュメモリ素子の安全性及び信頼性を改善することができる半導体素子及びその製造方法を提供する。

【解決手段】第1方向に沿って延長された活性領域を含む半導体基板と、半導体基板の上部に第1方向に交差する第2方向に沿って形成されたセレクトラインと、セレクトラインの間の前記活性領域それぞれに形成されて第1不純物を含む接合領域と、セレクトラインの間の空間を埋め込む多層の酸化膜と、接合領域の下部に繋がれて半導体基板の活性領域に形成されて第2不純物を含む接合領域延長部と、多層の酸化膜のうち少なくともいずれか一層を貫通して接合領域及び接合領域延長部に接触されたコンタクトプラグと、を含む。

(もっと読む)

オンダイターミネーション制御装置

【課題】較正正確度が改善されたオンダイターミネーション制御装置を提供する。

【解決手段】オンダイターミネーション抵抗値を外部抵抗値と同一に調整するオンダイターミネーション制御部と、第1パルス信号の活性化時にオンダイターミネーション制御部の出力電圧から比較器のオフセット電圧値を検出してキャパシタに保存し、第2パルス信号の活性化時にオフセット電圧値を相殺した後、出力電圧と既に設定された基準電圧とを比較して出力するオフセット補償部と、第3パルス信号の活性化時にオフセット補償部の出力を一定時間保存するラッチと、ラッチの出力をカウントしてコード信号を増加又は減少させるカウンタとを含み、オフセット補償部は、第2パルス信号の活性化時に保存されたオフセット電圧値を相殺して基準電圧と比較し、ラッチ及びカウンタは、第2パルス信号の活性化区間内において活性化状態に制御される第3パルス信号に応じて活性化制御される。

(もっと読む)

集積回路チップ及びこれを含む送受信システム

【課題】 伝送チップ上でのデータピン配列と、伝送チップと受信チップとの間のライン配列とが互いに異なってもクロストークを防止できる技術を提供すること。

【解決手段】伝送チップと、受信チップと、前記伝送チップから前記受信チップにデータを伝送するための複数のラインとを備え、前記伝送チップは、前記複数のラインに伝送されるデータパターンと前記複数のラインの配列情報とに応じて、前記複数のライン上で発生するクロストーク防止動作を行うことを特徴とする。

(もっと読む)

21 - 30 / 122

[ Back to top ]