エスケーハイニックス株式会社により出願された特許

71 - 80 / 122

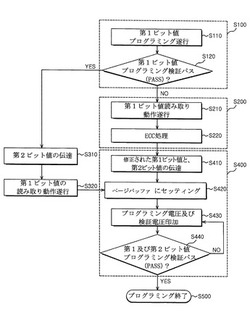

半導体システム及びデータプログラミング方法

【課題】電荷損失が発生してもデータプログラミング動作の信頼性を向上させることができるデータプログラミング方法及び半導体システムを提供する。

【解決手段】データプログラミング方法は、書き込みデータの第1ビット値がプログラミングされた複数のメモリセルの閾値電圧の分布が定められた第1電圧範囲を離脱したのかを判別する段階(S100)と、複数のメモリセルの閾値電圧の分布が前記第1電圧範囲を離脱した場合、エラー修正コードを通して前記第1ビット値を修正する段階(S200)と、修正された前記第1ビット値及び前記書き込みデータの第2ビット値を前記複数のメモリセルにプログラミングする段階(S400)とを含む。

(もっと読む)

リフレッシュ回路

【課題】所定レベルを維持するローアドレスが不要にラッチされないようにすることにより、リフレッシュ動作時に消費される電流を減少できるようにしたリフレッシュ回路を提供すること。

【解決手段】リフレッシュ期間で周期的に発生するパルスを含む第1のイネーブルパルス及び第1のローアドレスの全てのビットに対するカウントが終了する時点で発生するパルスを含む第2のイネーブルパルスを生成するイネーブルパルス生成部と、前記第1のイネーブルパルスに同期して、前記第1のローアドレスをラッチして第1のラッチアドレスを生成する第1のアドレスラッチと、前記第2のイネーブルパルスに同期して第2のローアドレスをラッチして第2のラッチアドレス及び第3のラッチアドレスを生成する第2のアドレスラッチと、を備えることを特徴とする。

(もっと読む)

半導体メモリチップ及びこれを用いるマルチチップパッケージ

【課題】マルチチップパッケージのパッケージングを容易にし、半導体メモリチップとマルチチップパッケージのパッドとを接続するボンディングによって伝送される信号のローディングを一定にすることができるようにした半導体メモリチップを提供すること。

【解決手段】第1のデータ信号と第1のストローブ信号と第1のマスク信号とが入力される第1のパッド部と、第1のモードでは、前記第1のデータ信号と前記第1のストローブ信号と前記第1のマスク信号とを第1の書き込み経路回路に伝達し、交換モードでは、前記第1のデータ信号と前記第1のストローブ信号と前記第1のマスク信号とを第2の書き込み経路回路に伝達する第1の選択伝達部と、を備えることを特徴とする。

(もっと読む)

半導体装置、チップIDの付与方法及びその設定方法

【課題】複数個のチップの各々が演算コードに対して直列的に所定の演算を行うことによって各チップに異なるチップIDを容易に付与する。また、条件によって演算コードまたは所定コードをチップIDとして付与することによって各チップに望みのチップIDを付与する。

【解決手段】第1チップ及び第2チップを含む半導体装置において、第1チップに設けられ、第1リペア信号により初期コードに所定の演算を行って第1演算コードを生成する第1演算部と、第2チップに設けられ、第2リペア信号により第1演算コードに所定の演算を行って第2演算コードを生成する第2演算部を含む。

(もっと読む)

埋め込みビットラインを備えた半導体装置の製造方法

【課題】埋め込みビットラインの抵抗を減少させることができる半導体装置の製造方法を提供すること。

【解決手段】本発明の半導体装置の製造方法は、基板201に活性領域203を分離するトレンチ202をエッチングにより形成するステップと、活性領域203の何れか1つの側壁の一部を露出させた開口部207を有する絶縁膜205を形成するステップと、絶縁膜205上にトレンチ202を部分的に埋め込み、開口部207を埋め込むようにシリコン膜パターン208Aを形成するステップと、シリコン膜パターン208A上に金属膜209を形成するステップと、金属膜209及びシリコン膜パターン208Aを反応させて、埋め込みビットラインとなる金属シリサイド膜211を形成するステップとを含む。

(もっと読む)

誘電体膜の形成方法、及びこれを用いる半導体素子のキャパシタの形成方法

【課題】誘電特性及び漏れ電流特性を向上させることのできる半導体素子の誘電体膜の形成方法及びキャパシタの形成方法を提供する。

【解決手段】誘電体膜は、原子層堆積法により、ウェーハ上に酸化ジルコニウム(ZrO2)及び酸化アルミニウム(Al2O3)で構成された誘電体膜を形成する方法であって、チャンバー内に、1つのZrと1つのAl原子とが1つの分子を構成しているソースガスを注入し、ウェーハ上に、ZrO2とAl2O3とからなる[ZrO2]x[Al2O3]y(ここで、x及びyは正数である)膜を形成するステップを繰り返すことにより、ZrO2とAl2O3とで構成された厚さ30Å〜500Åの誘電体膜を形成する。

(もっと読む)

半導体メモリ装置及びその動作方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】本発明の不揮発性メモリ装置の製造方法は、セル領域及び周辺回路領域を有する基板上に層間絶縁膜及びゲート電極膜が交互に積層されたゲート構造物を形成するステップと、前記セル領域の前記ゲート構造物を選択的にエッチングして、複数層の前記ゲート電極膜を一方向から分離させる第1トレンチを形成するステップと、前記周辺回路領域のコンタクト予定領域に対応する前記ゲート構造物を選択的にエッチングして、第2トレンチを形成するステップと、を含む。

(もっと読む)

モードレジスタセットを備える半導体メモリ装置

【課題】アドレスピンを追加せずに複数のMRSコマンドを生成することができるモードレジスタセットを備えた半導体メモリ装置を提供する。

【解決手段】データバッファ制御信号DQBUF_ENDBを生成する制御部230と、データバッファ制御信号DQBUF_ENDBに応じて、データパッドDQを介して入力される複数のMRSコードA<0:12>,BA<0:2>をバッファリングして出力するデータバッファ部250と、データバッファ部250から出力される複数のMRSコードA,BAをデータラインGIO,LIOを介して受信し、受信した複数のMRSコードA,BAを用いて複数のMRSコマンドNMRS_CMD<0:12>、EMRS_CMD<0:12>、EMRS2_CMD<0:12>、EMRS3_CMD<0:12>、TMRS_CMD<0:12>を生成する複数のMRSコマンド生成部290A〜290Eとを備える。

(もっと読む)

不揮発性メモリ装置及びその製造方法

【課題】不揮発性メモリ装置及びその製造方法を提供すること。

【解決手段】直列に接続した複数のメモリセルを含むメモリストリングと、前記メモリストリングの両端部にそれぞれ接続する第1及び第2選択トランジスタとを、含む不揮発性メモリ装置であって、前記メモリストリングが、第1半導体層145、及びメモリゲート絶縁膜を隔てて前記第1半導体層145と接する第2導電層125を含み、前記第1及び第2選択トランジスタが、それぞれ、前記第1半導体層145の一端及び他端と接続する第2及び第3半導体層165A、165Bを含み、前記第2導電層125が配置されない領域の前記第1半導体層145と接する第4半導体層165Cと、を含む。

(もっと読む)

ジルコニウム酸化膜を有する半導体素子のキャパシタ及びその製造方法

【課題】70nm以下の金属配線を有する次世代DRAMで要求される容量および良好な漏れ電流特性を確保できるキャパシタ及びその製造方法を提供する。

【解決手段】キャパシタ形成方法は、ストレージ電極65を形成するステップと、ストレージ電極65の表面をプラズマ窒化66A処理するステップと、該表面がプラズマ窒化66A処理されたストレージ電極65上にZrO2薄膜67を蒸着するステップと、ZrO2薄膜67の表面をプラズマ窒化処理して、表面が窒化66BされたZrO2薄膜を形成するステップと、窒化66Bされた前記ZrO2薄膜上にプレート電極68を形成するステップとを含む。

(もっと読む)

71 - 80 / 122

[ Back to top ]