モトローラ ソリューションズ インコーポレイテッドにより出願された特許

641 - 649 / 649

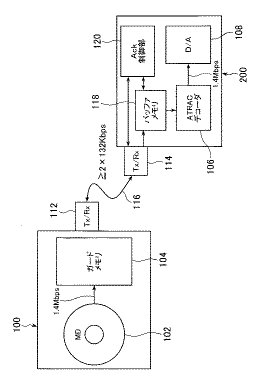

無線デジタルデータ通信システム

【課題】音楽データ等の一定頻度での継続的な再生が要求されるデータを無線により低消費電力かつ簡単な構成で伝送可能とする。

【解決手段】それぞれ送受信機を有する第1の通信ユニットおよび第2の通信ユニットの間で無線でデジタルデータを伝送する無線通信システムである。第2の通信ユニットは第1の通信ユニットから受信したデータを蓄積するバッファを備える。このバッファにおけるデータの蓄積度に応じて第1の通信ユニットから第2の通信ユニットに送信されるデータの通信速度を変化させる。あるいは、バッファに所定数以上のパケットが蓄積されると第1の通信ユニットはパケットの送信を一時停止し、前記バッファに蓄積されたパケット数が所定値以下になると再びパケットを送信する。

(もっと読む)

通信装置において回路モジュールを保護する方法

【課題】 通信装置においてSIMカードに電力を供給しても安全な時間を検出するための装置および方法を提供する。

【解決手段】 通信装置において回路モジュールを保護する方法は、まず、通信装置内に回路モジュールが存在するか否かを判断する段階を含む。次の段階は、通信装置に対する電源電圧を測定する。次の段階は、電源電圧を所定の閾値電圧と比較する。電源電圧が閾値より低い場合は、次の段階は通常の機能を電話機に与えて、比較段階に戻る。しかし、電源電圧が閾値より高い場合は、次の段階はSIMカードに対する接続を遮断し、通信装置の機能を制限する。

(もっと読む)

高速書込みリカバリを備えたメモリ装置および関連する書込みリカバリ方法

【課題】 メモリ装置において、最小のコラムピッチにより高速の書込みリカバリを可能にしかつ書込みデータ線に負荷が与えられた場合に遭遇する問題を避ける。

【解決手段】 電流検知スタティックランダムアクセスメモリ(SRAM)のようなメモリ10はビットライン負荷および2つの付加的なメカニズムによって高速の書込みリカバリを達成する。第1に、共有データライン上の余分の負荷252もアクティブになって書込みリカバリプロセスを早める。第2に、複数のコラム200,202,204が書込みリカバリの間に共通のデータライン接続され、それによって書込みサイクルの間に書き込まれるコラムが再び他のコラムに蓄積された電荷を使用して電荷共有により部分的にプリチャージできる。

(もっと読む)

マイクロストリップから懸垂ストリップ線路への集積移行構造とその製造方法

【課題】 整合レジストレーションの誤差に影響を受けないマイクロ波ハードウェアに適しており、電気的不連続性を最小限に抑えてインピーダンスの変形を行うマイクロストリップを懸垂ストリップ線路に移行する構造と、その製造方法とを提供する。

【解決手段】 マイクロストリップ14から懸垂ストリップ線路24への集積移行構造と、それを作成する方法とは、整合不良による電気的不連続性を最小限に抑え、その影響を受けずにマイクロストリップ14から懸垂ストリップ線路24伝送線路への移行を行う。導体10は一定の幅を有し、接地面36,38内の漸次的に先細りになる空隙44,42が、懸垂ストリップ線路24伝送媒体となる。漸次的に先細りになる空隙44,42は、インピーダンス変換を行い、製造誤差による移行中の不連続性を最小限に抑える。

(もっと読む)

データ処理システムにおける加算比較選択バタフライ演算およびその命令を実行する方法

【課題】 ビタービ・アルゴリズムをソフトウェア内で実行する演算時間を短くする方法を提供する。

【解決手段】 平行データ構造と専用のビタービ左シフト命令が、ソフトウェアのデータ処理システム20内に重畳符号化された信号を解読するために必要とされるクロック・サイクルの数を最小限に抑える。特に、データ構造とビタービ左シフト命令により、加算比較選択バタフライ演算を実行するために必要なクロック・サイクルの数が減る。加算比較選択バタフライ演算は、ビタービ解読アルゴリズムを実行する複数の命令内のループに含まれ、所定の回数だけ繰り返されて、トレリス図内の最良経路を選択する。

(もっと読む)

超小型高周波回路のための相互接続構造

【目的】 RF処理のためのフィルタ接続部分におけるクロストークを大幅に低減する改善されたリエントラントオフチップRF選択度構造を提供する。

【構成】 差動回路(402,415)、伝送ライン(423,424)およびオフチップフィルタ(422)が前記差動要素の全てと関連する寄生容量をバランスさせる構造で使用される。該構造は差動発生回路および受信回路を備えた基板(409)を含む。各々一定の特性インピーダンスを有し、かつ各々グランドに対しバランスした容量を有する、2つの差動伝送ラインが双方ともある距離の間接近した間隔にされ、前記回路を接近した間隔の終端パッド(403)に結合する。グランド面(412)が両方の伝送ラインの下で共有される。第1の基板(409)とリエントラントRF経路(406)を有する第2の基板(408)はフィルタまたは遅延線のようなRF機能を含む。

(もっと読む)

ダイヤモンド材を電子源に用いた陰極ルミネセンス・ディスプレイ

【目的】 陰極ルミネセンス層103,203に対し遠位に配置された透明なフェースプレート104,204上に配置された透明な導電層105,205上に配置されたダイヤモンド材の層106,206を有する電子エミッタを提供する。

【構成】 外部から付与される適切な信号の入力が、ダイヤモンド材層106,206からの電子の放出を誘発し、陰極ルミネセンス層103,203からの光子放出を実質的に励起する。

(もっと読む)

ダイヤモンドフイルム電子源を用いた電子素子

【目的】 0.05ミクロン代の小さな構造サイズを必要とせず、5x105V/cm程導電界のみを用いて、大量の電子を放出させることができる、電子放出電子素子を提供する。

【構成】 ダイヤモンド材料電子放出部(101)とアノード(102)とが双方とも支持基板(103)上に配置されており、それらの間に相互電極領域(130)を規定するようにした、電子素子。相互電極領域(130)を横切る電子の搬送は、ダイヤモンド材料電子放出部(101)の放出面(120)において、開始される。代替実施例では、実質的に対称的で、電子放出部(301)について軸方向にずれており、かつ相互電極領域(330)内にあるゲート電極(340)を用いて、変調能力を設けている。

(もっと読む)

ゲート電極の製造方法

【目的】 II−VI族およびIII−V族化合物半導体FETの中に金属ゲート電極18を製造する方法を提供する。

【構成】 本方法は、II−VI族またはIII−V族化合物半導体基板12を提供する段階およびその上にゲート電極18の第1部分16を形成する段階を含む。ハードマスク20は、ゲート電極18の第1部分16の上に形成し、平坦化誘電層22は基板12の表面上に形成し、ハードマスク20およびゲート電極18の第1部分16を含んでいる。その後ハードマスクを露出させて除去する。ついでゲート電極18の第2部分28を第1部分16の上に形成する。

(もっと読む)

641 - 649 / 649

[ Back to top ]