三星電子株式会社により出願された特許

1,011 - 1,020 / 8,520

半導体素子の製造方法

【課題】ピッティング不良が抑制され、簡単な工程を通じて形成することができる高性能の半導体素子の製造方法を提供する。

【解決手段】半導体基板にゲート電極を形成する段階と、ゲート電極に側壁スペーサを形成する段階と、側壁スペーサの両側の半導体基板を一部エッチングしてトレンチを形成する段階と、トレンチ内にSiGe混晶層を形成する段階と、SiGe混晶層上にシリコン層を形成する段階と、シリコン層の面の結晶方向に従って、エッチング率が異なるエッチング液を利用してシリコン層の一部をエッチチングすることによって111傾斜面を有するシリコンファセット(Si facet)を含むキャッピング層を形成する段階と、を有する。キャッピング層を含むことによって半導体素子でホールの移動度が高まる。キャッピング層内のピッティング不良が減少することによって半導体素子の特性が良好になる。

(もっと読む)

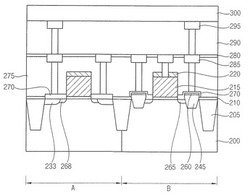

ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置

【課題】ガードリング構造を有する半導体デバイス、ディスプレイドライバ回路、及びディスプレイ装置を提供する。

【解決手段】本発明による半導体デバイスは、第1導電型の半導体基板と、半導体基板に既定の深さを有して形成された2以上の第2導電型の第1ウェル領域と、第2導電型の第1ウェル領域の内に既定の深さを有して形成された少なくとも一つの第1導電型の第2ウェル領域と、第1ウェル領域の間に位置し、第1ウェル領域と既定の間隔だけ離隔して既定の深さを有して形成された第2導電型のガードリング領域と、を含み、ガードリング領域は、システムグラウンド電圧に連結される。

(もっと読む)

携帯用端末機におけるメニュー実行方法及びその装置

【課題】携帯用端末機において、増加するアプリケーションサービスによって提供される複数の付加機能を迅速に実行するために速いメニュー実行を提供する方法及びその装置を提供する。

【解決手段】複数の分割された領域を有し、各分割された領域に対応するアイテムが形成されるアイテムリストをタッチスクリーン上にディスプレイするステップと、分割された領域内の第1の位置又は第1の位置と異なる第2の位置に対するユーザージェスチャを認識するステップと、認識されたユーザージェスチャの位置に対応して所定のメニューを実行するステップとを有し、タッチスクリーン上の分割された領域の第1の位置には分割された領域に形成されたアイテムに関連した第1のサービスを提供する第1のメニューが予め設定され、第2の位置には分割された領域に形成されたアイテムに関連した第1のサービスと異なる第2のサービスを提供する第2のメニューが予め設定される。

(もっと読む)

サーボトラックライター及びその動作方法

【課題】サーボパターンライト時に、スピンドルモータの外乱を減少させ、スピンドルモータによって発生するジッタを減少させることができるサーボトラックライター及びその動作方法を提供する。

【解決手段】サーボトラックライターの動作方法は、クロックパターン信号をヘッドディスクアセンブリーの磁気記録媒体にライトする段階と、磁気記録媒体にライトされたクロックパターン信号をリードし、該リードされたクロックパターン信号の周波数を分周する段階と、該分周された周波数を有するクロックパターン信号を、磁気記録媒体を回転させるスピンドルモータに供給する段階と、を有する。

(もっと読む)

半導体メモリ装置及びそれを含む半導体パッケージ

【課題】高性能及び低電力が要求される多様な装置及びシステムを支援できる、マルチチャネルインタフェース方式のワイド入出力を有する半導体メモリ装置及びそれを含む半導体パッケージを提供する。

【解決手段】本発明の一実施形態に係る半導体メモリ装置は、複数のメモリセルアレイを含む半導体ダイからなり、半導体ダイの中央部に形成される入出力バンプパッド部を含む。入出力バンプパッド部は、前記それぞれのメモリセルアレイを外部装置と独立的に接続するための複数のチャネルを提供する。マルチチャネル方式のワイド入出力インタフェースを通じて動作周波数の減少及びバンド幅の拡張を図ることによって、高性能の装置及びシステムを支援すると同時に電力消耗を減少させる。

(もっと読む)

ハイパーリンク選択方法及び装置

【課題】ハイパーリンク選択方法及び装置を提供する。

【解決手段】ウェブページでタッチ入力またはクリック入力が感知されれば、入力に対応する座標を獲得する段階と、座標近くに存在する少なくとも1つの候補ハイパーリンクを検索する段階と、少なくとも1つの候補ハイパーリンクが含まれた領域を拡大する段階と、少なくとも1つの候補ハイパーリンクを、他のハイパーリンクと区分されるように変更する段階と、を含むハイパーリンク選択方法及び装置である。

(もっと読む)

携帯端末でパケット・フィルタリングを通じて電力消耗を低減させるための装置及びその方法

【課題】携帯端末でパケット・フィルタリングを通じて電力消耗を低減させるための装置及びその方法を提供する。

【解決手段】スリープ・モードに進入したアプリケーション処理部が不要なパケットによってウェイク・アップすることを防止するために、モデム部でパケットをフィルタリングさせ、自身が必要とするパケットに対するリストをパケット確認部に提供するアプリケーション処理部と、アプリケーション処理部から提供されたリストに含まれたパケットのみをフィルタリングして、リストに含まれたパケットをアプリケーション処理部に提供するパケット確認部とを備えることを特徴とする。

(もっと読む)

セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧印加方法

【課題】内部高電源電圧を利用して希望の動作をうまく行える半導体メモリ装置を提供する。

【解決手段】セルフリフレッシュ動作モードで内部の高電源電圧を使用する半導体メモリ装置及びその高電源電圧の印加方法が開示される。

複数のメモリバンクからなるメモリセルアレイを具備した半導体メモリ装置を動作させるために高電源電圧を印加する方法は、半導体メモリ装置の動作モードによって区別され得る。セルフリフレッシュ動作と同一である特定動作モードで外部の高電源電圧を受ける必要なく、内部から生成された高電源電圧を受けてメモリバンク別、またはメモリバンクグループ別にセルフリフレッシュを行う方法によれば、高電源電圧発生器のパンピング効率低下の発生無し、動作に必要な高電源電圧が安定的に印加される。

(もっと読む)

半導体セル構造物、上記半導体セル構造物を含む半導体装置、及び上記半導体装置を含む半導体モジュール

【課題】所定の整列関係を有する単位セルを含む半導体セル構造物を提供すること。

【解決手段】単位セルは、活性領域14、18、24、28、ゲートパターン32、34、36、38、ダミーパターン42、44、46、48、及び導電パターン94を有する。ゲートパターン32、34、36、38は活性領域14、18、24、28と交差する。ダミーパターン42、44、46、48は単位セルを電気的に接続する。選択された単位セル内のダミーパターン42、44、46、48は、選択された単位セル内のゲートパターン32、34、36、38との間に対角的に配置される。導電パターン94はダミーパターン42、44、46、48と電気的に接続する。これにより、半導体セル構造物は、行及び列に沿って互い突出しない単位セルを有することができる。上述した半導体セル構造物は半導体装置及び半導体モジュールに配置される。

(もっと読む)

フレームレート制御方法及びそのための液晶表示装置

【課題】表現可能な全階調の中で上位階調のガンマ歪曲が除去できる第1のフレームレート制御方法を提供する。

【解決手段】フレームレート制御方法は、入力される2進nビットの階調値で構成されるRGBデータを、eビット(e≧n+1)に拡張し、連続する2d個のフレーム内に、拡張RGBデータの下位dビットを除いた上位(e−d)ビットが示す階調データとその直上位階調データの発生頻度が調整されるようにフレームデータを変換し、2d個のフレームデータの中で最初半分であるノーマルフレームと、各フレームの画素配置を垂直方向に変えて得られる残り半分のフレームであるプラスフレームとを、毎フレームごとに互いに交互に表示されるようにフレームデータを再配置することを、各単位画素ブロック内においてRGBデータの下位dビットを除いた上位(e−d)ビットが示す階調データとその直上位階調データの発生頻度が空間的に調整されるように配置する。

(もっと読む)

1,011 - 1,020 / 8,520

[ Back to top ]