三星電子株式会社により出願された特許

8,501 - 8,510 / 8,520

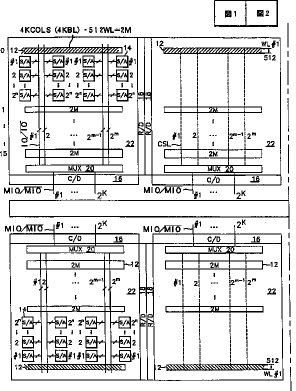

高帯域幅を可能とした半導体メモリ装置

【目的】 容易に高帯域幅が得られるチップアーキテクチャで構成した半導体メモリ装置を提供する。

【構成】 長方形状のメモリセルアレイのアレイ長手方向へワード線を配線すると共にその直交方向へビット線を配線し、そして、前記直交方向へ、データ入出力線(IO/バーIO)及びこのデータ入出力線とビット線との接続選択のための列選択線(CSL)を配線する。更に、データ入出力線を所定数ずつマルチプレクサ20を介してメインデータ入出力線(MIO/バーMIO)へ接続する。アレイ上ではデータ入出力線と列選択線の基本構成を繰り返し配線できるので集積性に優れ、高帯域幅を容易に実現できる。アクセスでは、長手方向へ配線したワード線方向へ単位アレイ12の活性化が行われ、各サブアレイ22の単位アレイ12に対しメインデータ入出力線数分のデータをアクセスできる。

(もっと読む)

電圧オンリセット回路

色補正方法及びその装置

【目的】 色空間を分割して該当領域別に色補正係数を算出して色補正する。

【構成】 画像デ−タを入力する工程と、入力されたデ−タの該当領域を判別してそれによる色補正係数を選択して出力する工程と、選択された色補正係数と入力デ−タを演算して色補正する工程と、色補正された画像デ−タを出力する工程を備なえ、精巧な色補正をを、従来のルックアップテ−ブル(LUT)を使用した色補正方式よりメモリを節約して速度を向上させて実現する。

(もっと読む)

半導体素子の製造方法

【目的】 水素化工程を改善した半導体素子の製造方法を提供する。

【構成】 本発明の半導体素子の製造方法は、基板1上にソース3、ドレイン4、活性層5、ゲート絶縁層6、ゲート7、絶縁層10、電極8および電極9を形成する第1工程と、前記第1工程で形成された層の上面にプラズマ窒化物層11を形成する第2工程と、プラズマ窒化物層11の上面にキャップ層12を形成する第3工程と、前記第3工程によりキャップ層12の形成されたトランジスタにプラズマ窒化物層11から発生する水素が拡散されて入るように熱処理する第4工程とを含む。水素拡散係数の低い材料からなるキャップ層12により、前記第4工程時に外部へ逃げる水素の量が少なくなり内部に拡散する水素の量が多くなるため水素化効果が増大する。

(もっと読む)

半導体装置の配線形成方法

半導体装置の配線形成方法

【目的】 収率および信頼性の高い半導体装置の配線形成方法を提供する。

【構成】 基板上に形成された下部構造物20上にAlを含む下部導電層21を形成し、下部導電層21上に形成された絶縁層22上にフォトレジストパターン23を形成する。フォトレジストパターン23を蝕刻マスクとする湿式蝕刻により絶縁層22を所定の厚さまで等方性蝕刻した後、残った絶縁層22をRIE方法によりテーパ蝕刻して直径が下部に行くほど小さくなるように開口部を形成する。続いて、下部導電層21が開口部により露出することを保障するために、フルオロカーボン系のガスと酸素との混合ガスを使用してオーバエッチングし、前記結果物をRIEスパッタリングする。フルオロカーボン系のガスを使用して下部導電層21上の絶縁層を蝕刻することにより、開口部を形成する時に生成するポリマー26や不揮発性の副産物などを除去する。

(もっと読む)

冷蔵庫の温度制御方法

直列通信ポートと光通信ポートの切換制御装置およびその駆動方法

【目的】 直列通信ポートと光通信ポートのいずれかを選択して使用できる切換制御装置とその駆動方法を得る。

【構成】 電源が印加されると、マイクロコントローラ38により切換スイッチSSから発生された切換信号が読出され、光通信ポートを使用する場合、光信号入出力端36へロー状態の出力信号IRPWRが、直列通信ポートを使用する場合、ハイ状態の出力信号IRPWRが出力され、マルチプレクサ32、35へチャネル選択信号が出力される。それにより、非同期通信部31と光信号入出力端36とにマルチプレクサ32、35を通じてデータ伝送チャネルが形成され、光信号伝送または直列データ伝送を行なえる待機状態になる。

(もっと読む)

自動輝度制限回路

【目的】 ブラウン管のホワイトバランスが合わなくなることを防止しうる自動輝度制限回路を提供することを目的とする。

【構成】 映像信号を増幅する増幅部20と、能動素子によって画面のコントラストを調整するコントラスト調整部20と、増幅部10及びコントラスト調整部20の出力を制御してブラウン管の映像信号レベル及びコントラストを自動的に調整する制御部30とよりなる。

(もっと読む)

半導体メモリ装置及びその製造方法

【目的】 半導体装置及びその製造方法を提供すること。

【構成】 セルアレイ領域と周辺回路領域から構成される半導体メモリ装置において、前記セルアレイ領域と周辺回路領域の間の境界領域に、前記セルアレイ領域を囲む形でその上部が除去された形のトンネルが形成される。

【効果】 従来半導体メモリ装置で問題となったセルアレイ領域と周辺回路領域の間の段差による導電層の信頼度低下を防止できるだけではなく、周辺回路領域の表面平坦化を同時に達成できる。

(もっと読む)

8,501 - 8,510 / 8,520

[ Back to top ]